Lab 6 - ECE 421L

Finally, the output of the gates:

Now that we know the output of the gates we can create the layout, which Cadence will check against these schematics. The NAND gate is simple as it contains 2 MOSFETS connected in series. The inputs are labeled "A" and "B" and the output is labeled "Y."

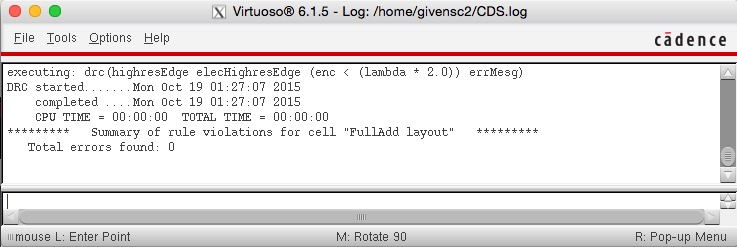

DRC, extract, and LVS the Layout:

The XOR gate is more complicated. All routing is done on the poly1 and metal1 layers. The metal2 layer is saved for later use.

Looking back, this design is flawed. The p-substrate that acts as the body for the NMOS is slightly resistive and the two NMOS located in the middle of the layout, not near the grounded ptap will likely have noise issues. But the layout passed DRC and LVS.

Below is a closeup of the inputs of the XOR gate. Notice they are attached to the body of the MOSFETs as depicted in the schematic.

And the output is between the source and drain of the set of 4 NMOSs and PMOSs.

Now to put it all together. Below is the schematic for the 2-bit Full Adder using the symbols created earlier:

And the symbol for the Full Adder:

Let's simulate the full adder using the symbol (and schematic) from above. Once again, vdd must be present or the circuit won't run properly.

Output:

Finally, based off of the Full Adder schematic, layout the circuit using the gate layouts created previously:

I tied the ground and vdd of all the NAND gates to their respective supply rails. I doubt this had anything to do with th LVS problem, as it still wouldn't pass LVS. The problem seemd to lie in the middle of the circuit. "cin" and "s" were routed incorrectly.

Success!