Lab 05 - EE 421L

parke179@unlv.nevada.edu

The library for this Lab05 can be downloaded from the zip file located in this directory

http://cmosedu.com/jbaker/courses/ee421L/f14/students/parke179/Lab05/other/

Direct download link

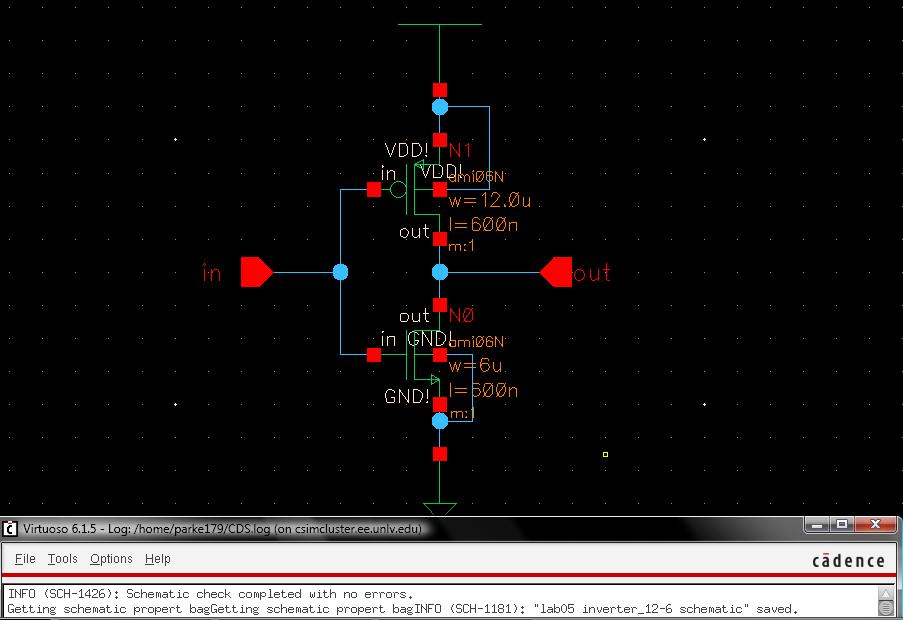

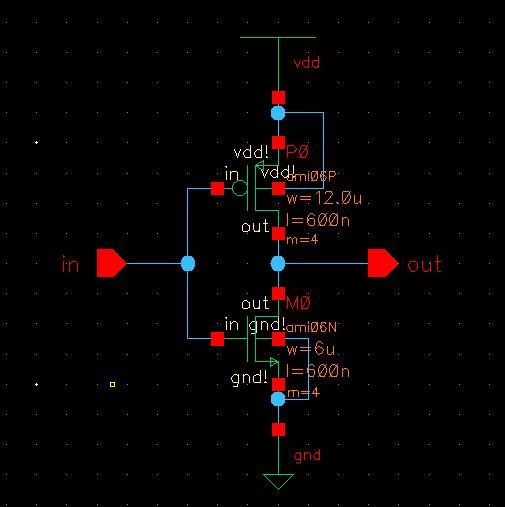

Part I: Design of a 12u/6u CMOS inverter

The first inverter design will use a PMOS with a width of 12u, and an NMOS with a width of 6u, and both have a length of 0.6u (in other words, the size of the inverter is 12u/6u).

Figure 1: Schematic of 12u/6u inverter

Note: A small mistake with the schematic in figure 1 is that I used the GND! and VDD! instances under the "basic" library, instead of the gnd! and vdd! instances under the NCSU_Analog_Parts library. An error won't become apparent until I try an LVS.

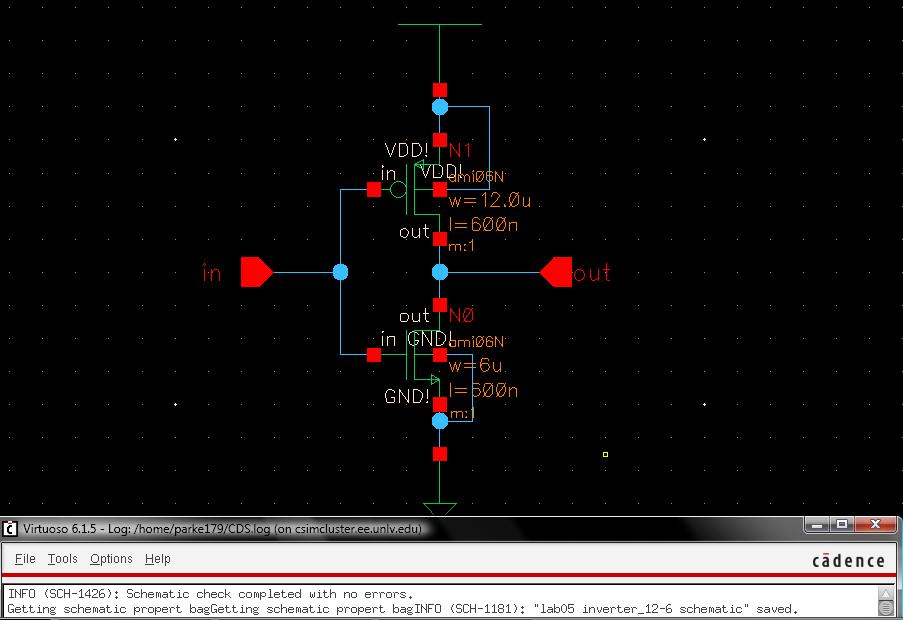

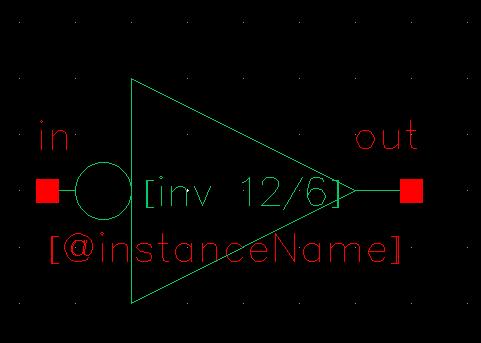

After a check and save, the schematic is exported as a symbol.

Figure 2: Symbol of 12u/6u inverter

Note: Figure 2 shows the symbol of the inverter, and there is yet another small mistake. The name "[inv 12/6]" is invalid because of the brackets, since a bracket must be followed by a special character such as "@." This error becomes apparent when the symbol is instantiated in the simulation cellview.

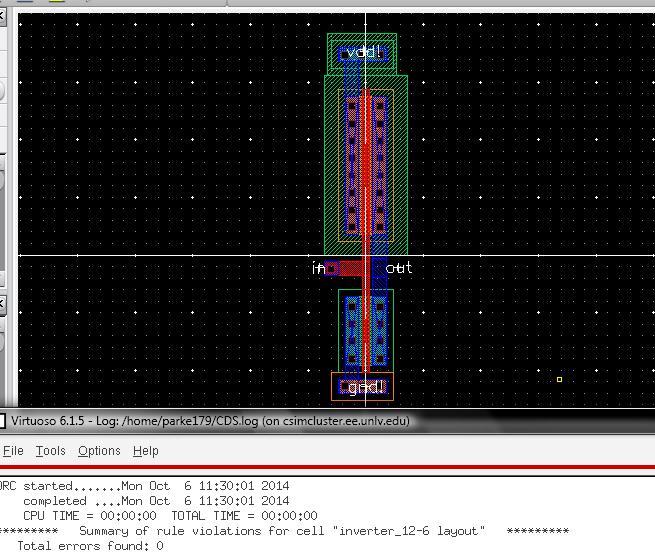

The next step is to layout the inverter. Using the DRC tool after each component is added is helpful to find errors early.

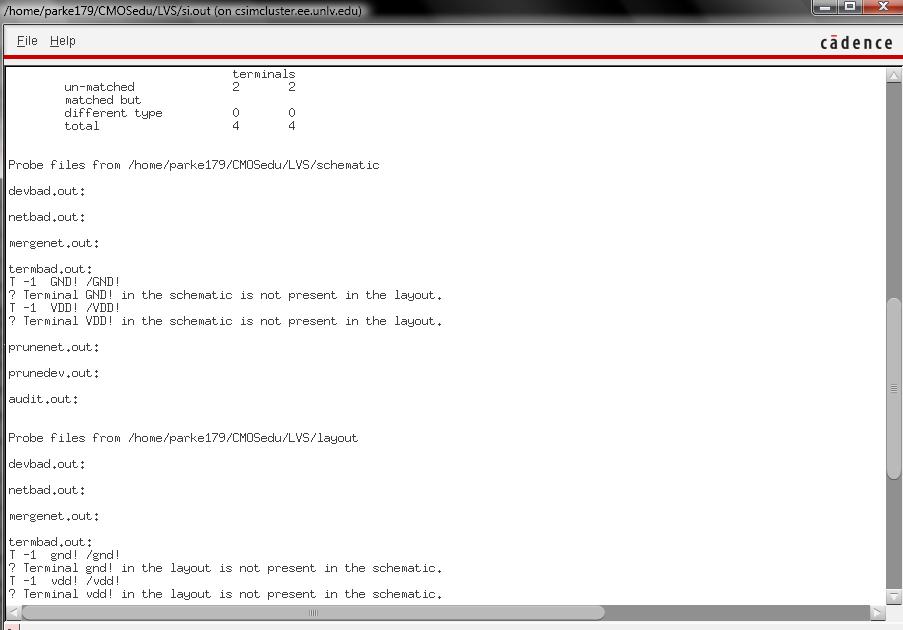

After the layout passes the DRC, the final step is to extract it and perform an LVS. The first time I ran this check I got an mismatch error for using the wrong gnd and vdd instances (see note under figure 1).

Figure 4: LVS error when using the wrong vdd and gnd instances

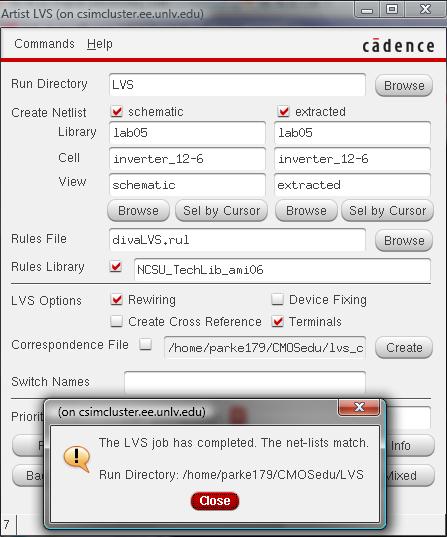

After using the proper gnd and vdd instance libraries in the schematic, the LVS passes.

Part II: Simulation of the 12u/6u CMOS inverter

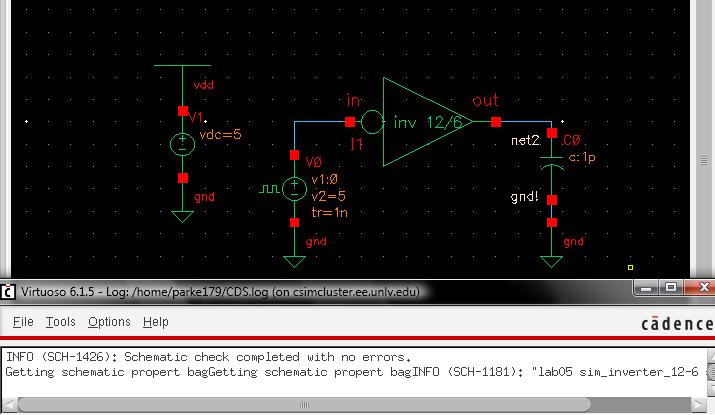

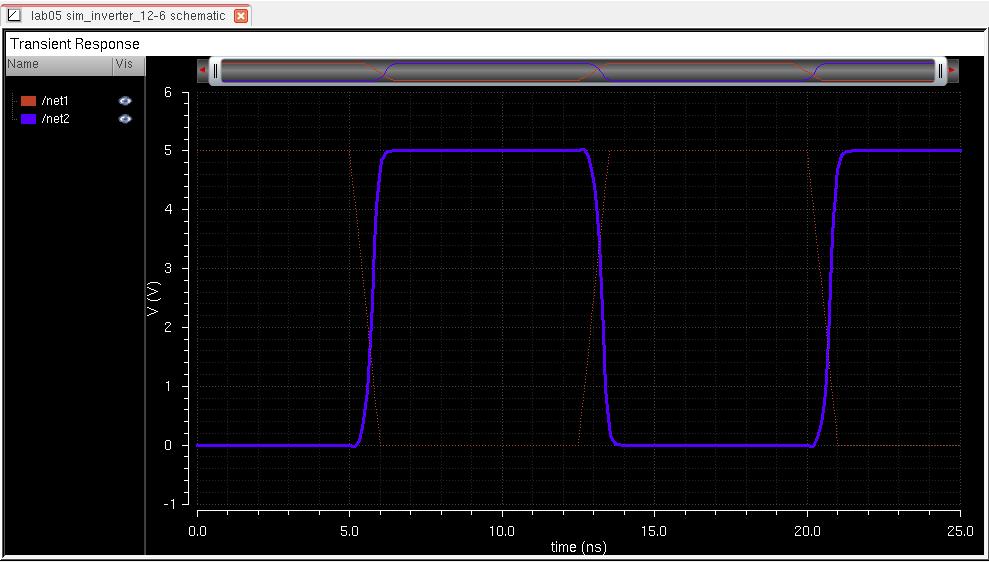

The simulation of the 12u/6u inverter will use a square wave input, and a capacitive load on the output.

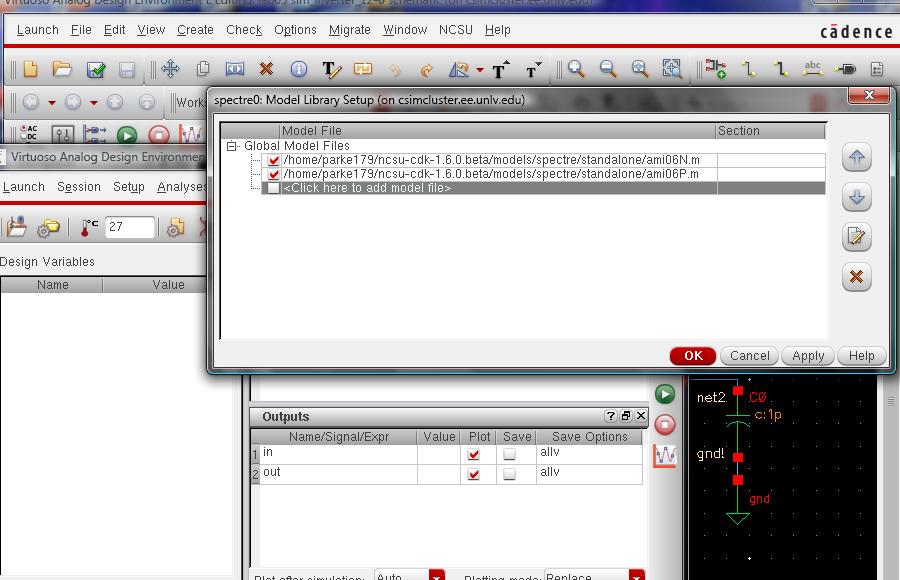

Be sure to set the Model Libraries if the simulation fails to complete.

A quick simulation shows that the circuit behaves correctly at 100f F.

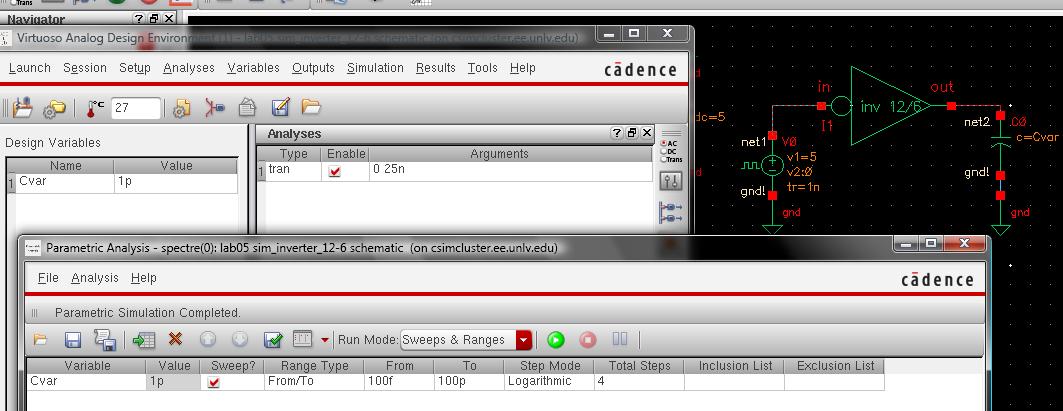

To simulate the circuit with Cload = to 100f, 1p, 10p, and 100p, I used a parametric analysis. I set the step mode to logarithmic to make it skip from 100f to 1p and etc.

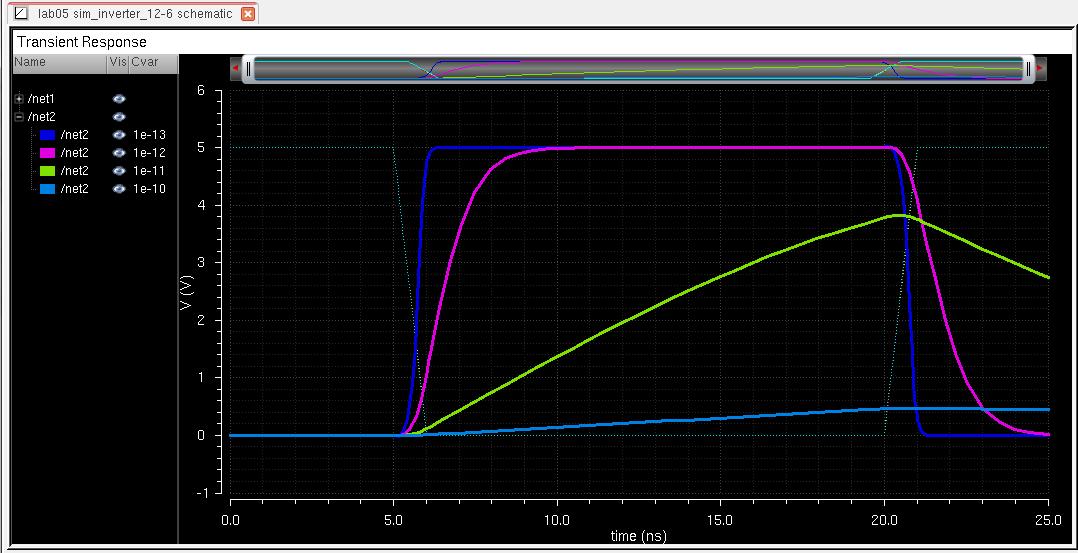

Figure 10: Parametric Analysis of 12u/6u inverter with varying Cload

Figure 10 shows the results of varying Cload from 100f (dark blue) to 100p (light blue). The rise time of the inverter greatly increases as Cload becomes larger. This is explained by the RC time constant increasing causes td (0.7RC) to increase.

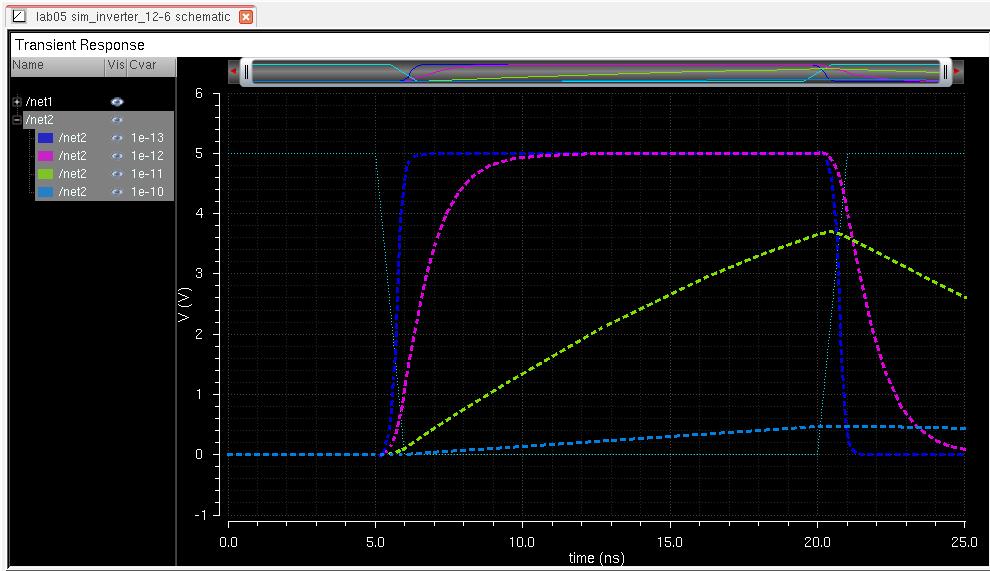

The simulation is rerun with UltraSim instead of spectre and the results are near identical.

Figure 10_Ultra: simulation using UltraSim instead of Spectre

Part III: Design and simulation of a 48u/24u CMOS inverter

Changing the size of the inverter and running a new simulation will be easy now that we have learned from our mistakes.

The size of this inverter will be 48u/24u and will be accomplished by setting the multiplier to 4.

The multiplier works by putting MOSFETs in series and combining them into a single MOSFET.

Figure 11: Schematic of the 48u/24u inverter

The only difference between this schematic (figure 11) and the one in figure 1 is the multipler is set to 4 instead of 1.

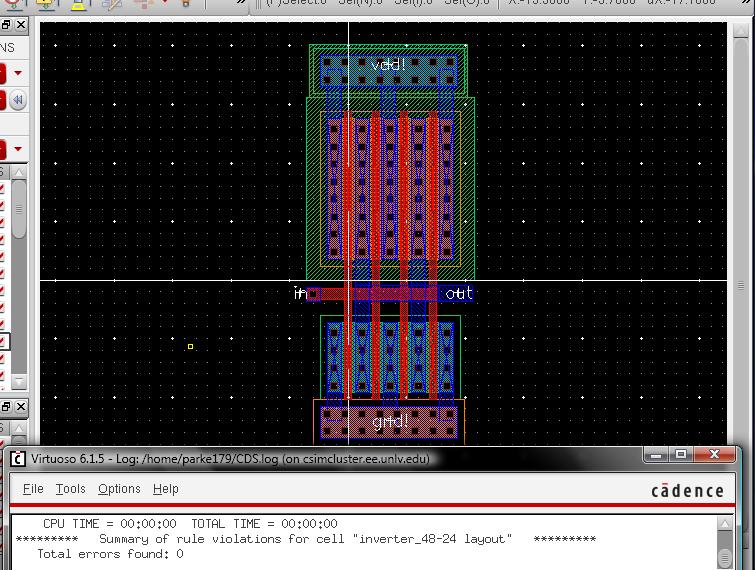

Similarly, the layout only requires M to be set and some adjustments made to accomidate the multiplier. Note that the S and D sides of the MOSFETs will alternate. The number of times poly crosses N-well or P-sub is equal to the number of PMOS's or NMOS's.

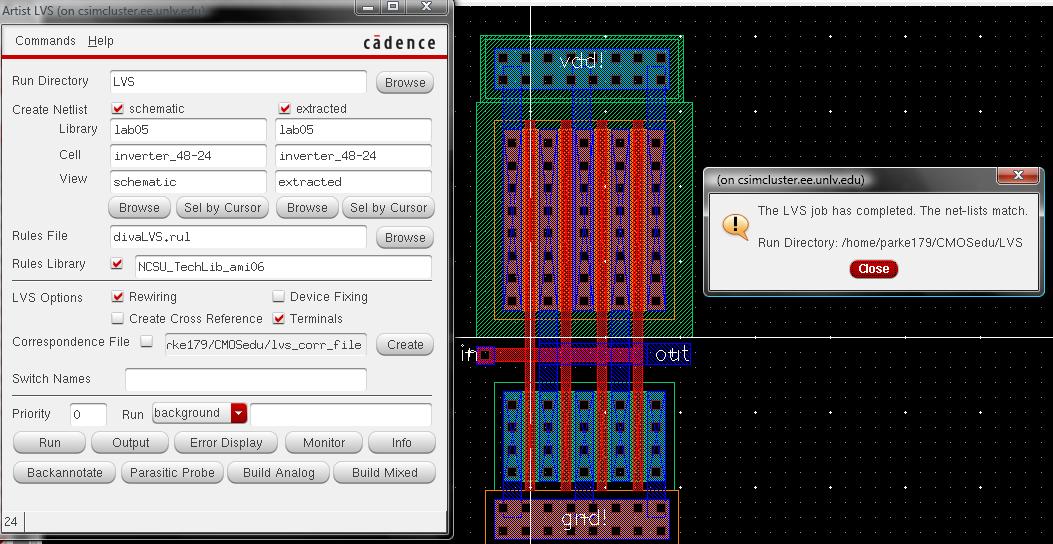

After the layout passes DRC, the next step is to extract it and perform an LVS.

After the LVS passes, we can simulate this inverter the same way that we simulated the previous one.

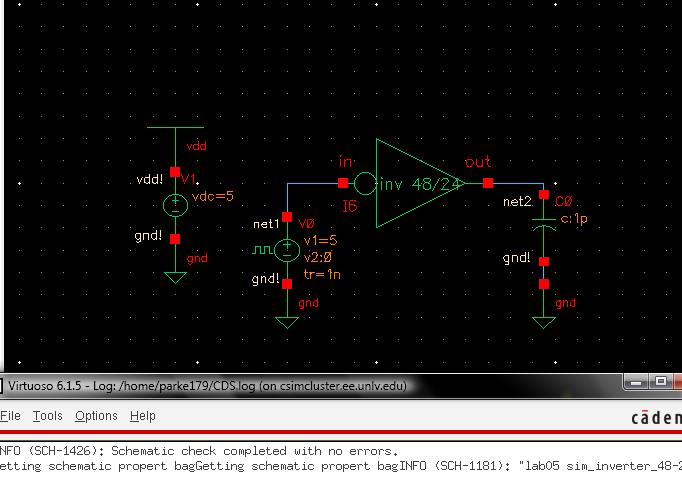

First, make update the schematic.

Then we can go straight to a parametric analysis by loading the session.

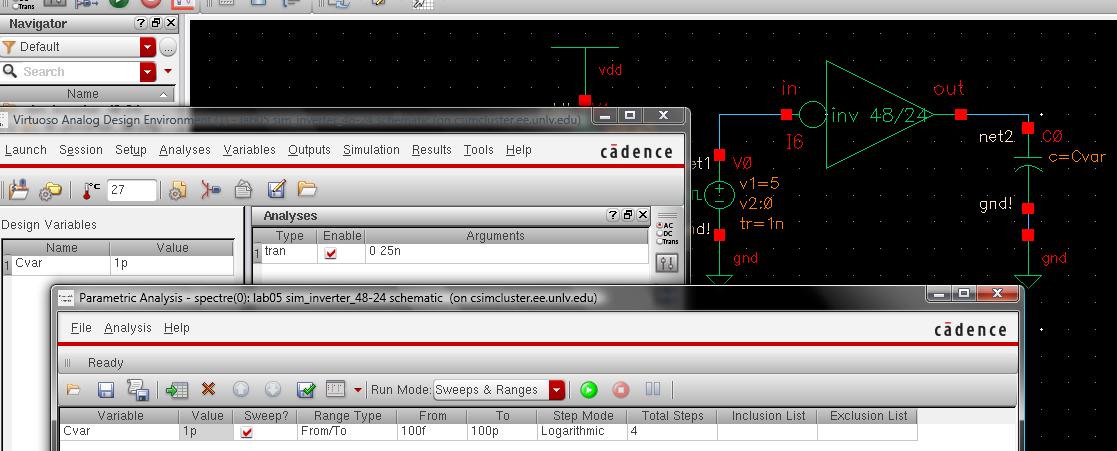

Figure 15: Setting up the simulation of the 48u/24u inverter

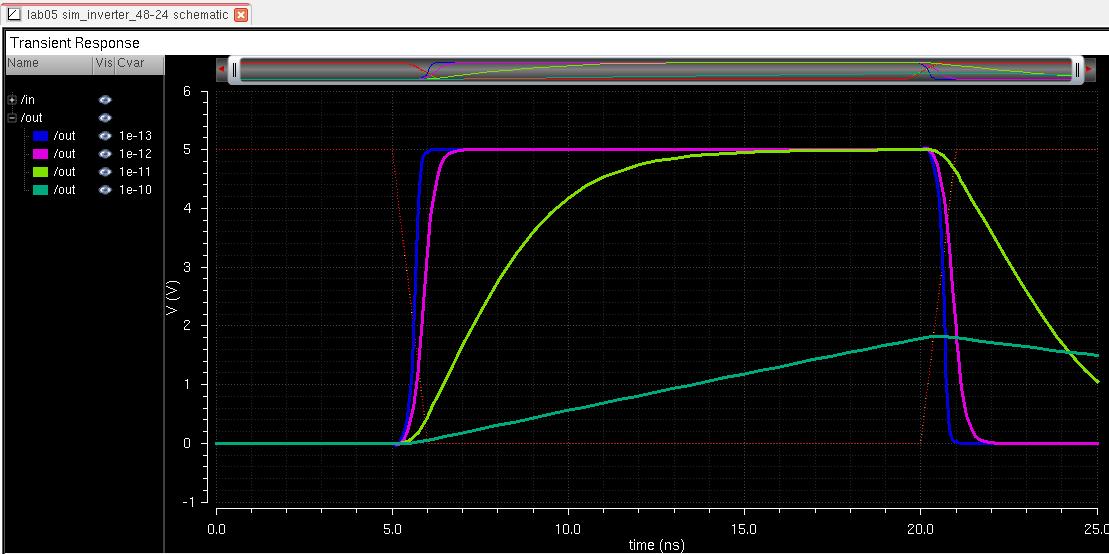

Figure 16: Spectre Analysis of the 48u/24u inverter

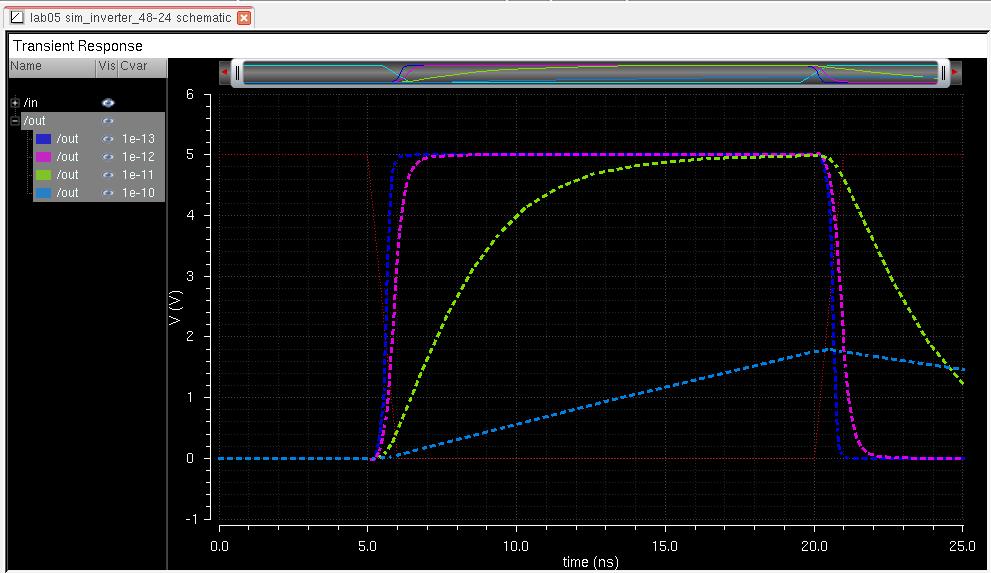

Figure 17: UltraSim analysis of the 48u/24u inverter

The two simulators, Spectre and UltraSim, have near identical results for this inverter as well.

Comparing the two different sized inverters, it appears that the larget inverter is less affected by a capicitor than the smaller inverter.

Creating backups

I use dropbox to backup all screenshots, project files, and html files. I do so by using the dropbox folder as my active work area to save to, and then dropbox automatically uploads changes to the files.

The library for this Lab05 can be downloaded from the zip file located in this directory

http://cmosedu.com/jbaker/courses/ee421L/f14/students/parke179/Lab05/other/

Direct download link