Lab 7 -

EE 421L

Authored

by Min Lan,

LANM2@UNLV.NEVADA.EDU

10/18/2013

Electric library: ML_ee421L_f13_lab7.jelib

Lab

description

In this lab, we will draft the schematics of 8-bit NAND, NOR, AND, and OR gates,

using buses. We will also draft MUXes, DEMUXes, Full Adder, and 8-Bit Adder; they

will be used in the ALU for the project. The layout for 8-Bit Adder will also be drafted.

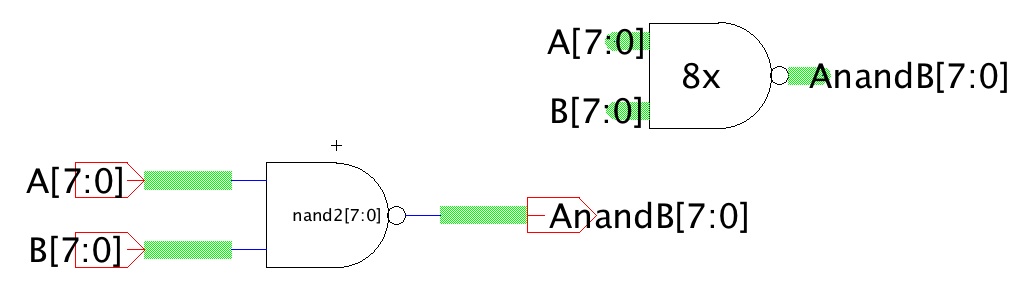

8-bit NAND gate array

Schematics

8-bit NOR gate array

Schematics

8-bit AND gate array

Schematics

8-bit OR gate array

Schematics

2-to-1 DEMUX

Schematics

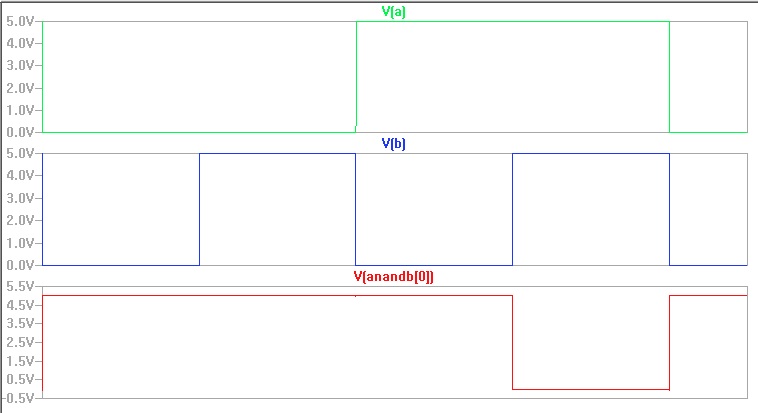

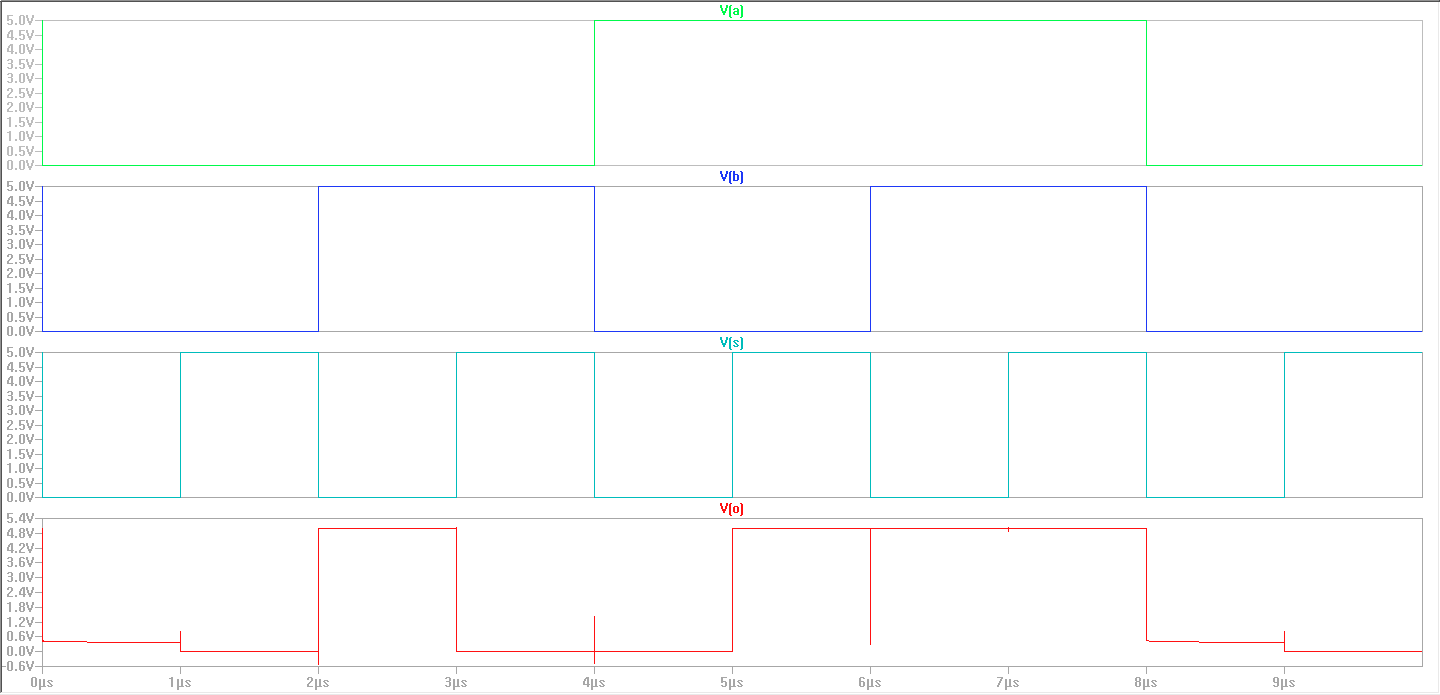

8-bit 2-to-1 DEMUX/MUX

Schematics

- Simulate with LTspice

- Simulate with IRSIM

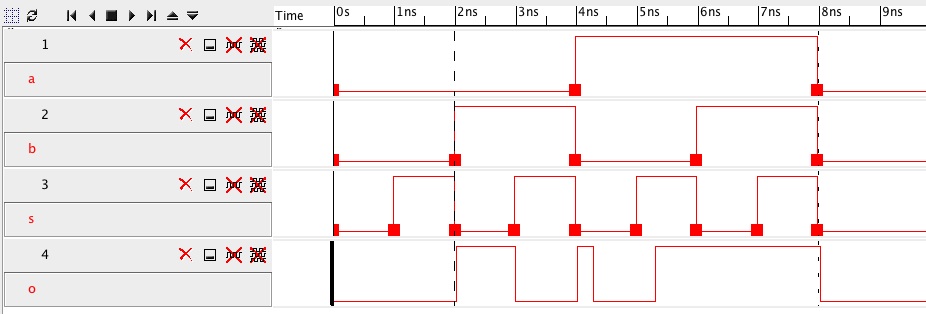

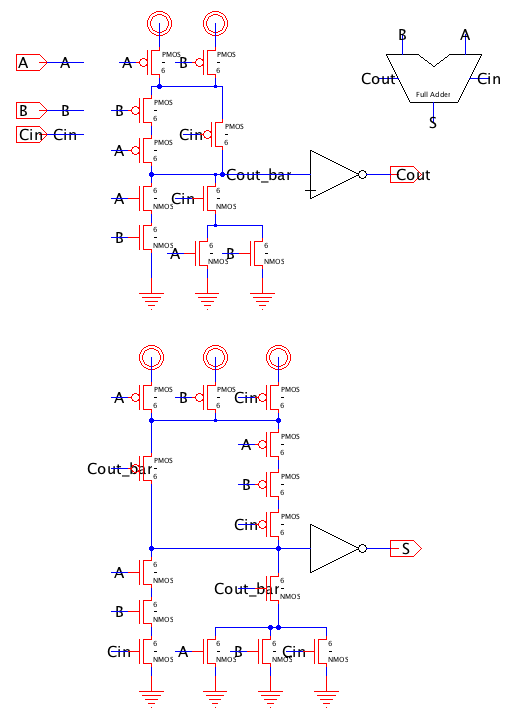

Full Adder

Schematics:

- Arc names are used to connect inputs for clean look

Layout:

- NCC, DRC, ERC checks:

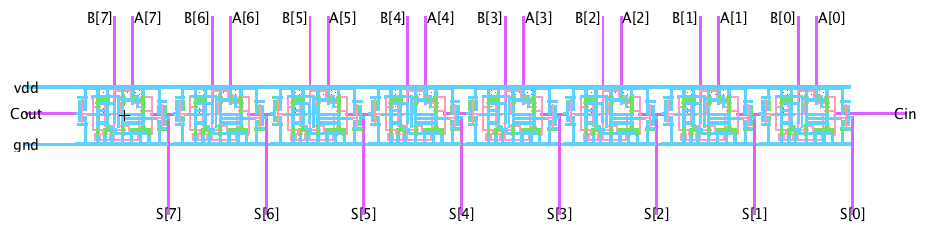

8-bit Adder (2)

Schematics:

Simulation with IRSIM:

- 5 + 3 = 8

- 2 + 7 = 9

Layout:

- Overview

- One Level Down

- DRC, NCC, ERC checks

Backup

Zip both your library file and your webpages and email to yourself.

Return to EE 421L Labs