# Digital Circuit Design

Developed by R. Jacob Baker University of Idaho

An IEEE/EAB Self-Study Course

Prepared for the Educational Activities Board of the Institute of Electrical and Electronics Engineers, Inc.

## **Digital Circuit Design**

Developed by R. Jacob Baker University of Idaho

Teasenautoethe dent and melao of reacon hert Networking the World™

> An IEEE/EAB Self-Study Course

٦

7

7

7

٦

Activities Board of the Electronics Engineers, Inc.

Prepared for the Educational

Institute of Electrical and compared to ease 2 particularly of the behalf

#### 1999 EDUCATIONAL ACTIVITIES BOARD (EAB)

Dr. Arthur W. Winston Vice President, Educational Activities

Prof. Jerry R. Yeargan Prof. David G. Daut Dr. Janie M. Fouke Mr. Robert D. Adams Mr. Pedro Ray Dr. Irving Engelson Dr. Bill D. Carroll Dr. Marion O. Hagler Mr. Richard S. Nichols Prof. John A. Orr Dr. Lyle D. Feisel Dr. Maurice Papo Dr. Raymond D. Findlay Mr. Michael Garretson Mr. Peter A Lewis

© 2000 by The Institute of Electrical and Electronics Engineers, Inc.

The author and publisher of this package have used their best efforts in preparing and collecting the materials. These efforts include the development, research, and test of the theories to determine their effectiveness. The editor and publisher make no warranty of any kind, expressed or implied with regard to the documents contained in this book.

All rights reserved. No part of this book may be reproduced, in any form nor may it be stored in a retrieval system or transmitted in any form, without written permission from the publisher.

Printed in the United States of America

ISBN 0-7803-4812-5

Editorial Production Supervision - Jill R. Bagley

Published by the Institute of Electrical and Electronics Engineers, Inc. 445 Hoes Lane, PO Box 1331, Piscataway, NJ 08855-1331.

http://www.ieee.org/organizations/eab/

## CONTENTS

| CMOS DIGITAL CIRCUIT DESIGN (COURSE INTRODUCTION) |                                    |  |

|---------------------------------------------------|------------------------------------|--|

| LESSON 1                                          | AN OVERVIEW OF CMOS CIRCUIT DESIGN |  |

| LESSON 2                                          | <b>Тне Well</b>                    |  |

| LESSON 3                                          | THE METAL LAYERS                   |  |

| LESSON 4                                          | THE ACTIVE AND POLY LAYERS         |  |

| LESSON 5                                          | THE MOSFET AS A CAPACITOR          |  |

| LESSON 6                                          | <b>The MOSFET</b> 13               |  |

| LESSON 7                                          | THE SHORT CHANNEL MOSFET15         |  |

| LESSON 8                                          | THE DIGITAL MODEL OF A MOSFET      |  |

| LESSON 9                                          | INVERTER OPERATION I               |  |

| LESSON 10                                         | INVERTER OPERATION II              |  |

| LESSON 11                                         | STATIC LOGIC GATES                 |  |

| LESSON 12                                         | THE TRANSMISSION GATE              |  |

| LESSON 13                                         | DYNAMIC CMOS LOGIC                 |  |

| LESSON 14                                         | <b>VLSI LAYOUT</b>                 |  |

| FINAL EXAMINATION                                 |                                    |  |

## SUMPLIMUS-

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L ROOM |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| The Mark Constant and the second state of the |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| Yes Proving Motorian MOSSEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

## **CMOS Digital Circuit Design**

#### A Self-Study Course

This course was designed around Chapters 1 - 6 and 10 - 15 of CMOS: Circuit Design, Layout, and Simulation, by Baker, Li and Boyce, IEEE Press, 1998. The goal of this self-study course is to provide information on custom CMOS (Complimentary Metal Oxide Semiconductor) digital circuit design with an emphasis on the physical implementation of integrated circuits (ICs).

#### Prerequisites

This course assumes the student has an electrical engineering background with fundamental knowledge in the areas of digital logic design, linear circuits, and basic electronics. No knowledge of integrated circuit design is assumed.

#### **Course Objectives**

After completing this course you should be able to:

- . Discuss the basic fabrication layers in a CMOS process.

- . Sketch a schematic from an integrated circuit layout.

- . Demonstrate an understanding of the origins of the unwanted parasitics in a CMOS IC.

- . Describe qualitatively how a MOSFET operates.

- . Design static and dynamic logic gates.

- Explain timing constraints in a CMOS IC.

- Size n- and p-channel MOSFETs for specific drive levels. ٠

#### Features of this course A. Review the objectives of the lessen and determine if they have been

This course includes:

- a study guide including learning objectives, reading assignments, and practice problems (with solutions).

- the course textbook. .

- a video tutorial for each lesson to help reinforce the concepts presented in the book and study I would like to take this opportunity to thank fill Bosley on Ourbarn Stelers ( if guide.

- a final exam which, upon completion, will lead to a certificate of achievement from the IEEE and 8 continuing education units (CEUs).

#### How to use this course

This course was developed assuming the reader would complete the lessons sequentially, that is, Lesson 1 followed by Lesson 2, etc. Similarly the lessons should be completed sequentially in the following order:

icon.

- 6. Review the practice problem solutions, designated by the

- Review the objectives of the lesson and determine if they have been met. If so proceed to the next lesson. If not review 2 through 5 above until the objectives are met.

After finishing Lesson 14 review the final exam instructions given in the final exam booklet. Information on taking and submitting the exam for grading/credit is given in this booklet.

#### Acknowledgments

I would like to take this opportunity to thank Jill Bagley and Barbara Stoler of the Educational Activities Department of the IEEE for their time, effort and encouragement in developing this course. Also, special thanks go to my wife Julie and children Kyri and Josh for their patience and encouragement while this course was being developed.

This county was developed menutive the new tormood our plate the lectrons requestedly, that its Lesson 1 follower to Leman 7, and himselp the resurce should be prepired sequentially in

## Lesson 1

## **AN OVERVIEW OF CMOS CIRCUIT DESIGN**

- Complimentary Metal Ocide Semiconductor (CMOS) is a manufacturable integrated circuit process consisting of a-channel and p-channel MOSFET's. CMOS is used in the fabrication of most processors and memory.

- CMOS integrated circuits are intricated in a wafer. The today is that up take dis when connected to a lead frame and excapationed in plastic. The layout view of an integrated circuit is the 'true view''' while the manuscription

### **Learning Objectives**

After completing this lesson you will be able to:

- Demonstrate an understanding of the course and its goals.

- Discuss what is meant by CMOS technology and why CMOS is popular for making integrated circuits.

- Explain what a die, wafer and leadframe are and how they are used in making a packaged integrated circuit.

- Determine the difference between layout and cross-sectional views of an integrated circuit.

## **Reading Assignment**

Read section 1.1 of the text. If you want to learn how to use the LASI (Layout System for Individuals, pronounced "Lazy") layout tools discussed in the book read all of Chapter 1 and download the layout tools from the address given in the text. This course will not discuss the use of LASI.

## Video Assignment

Watch the Lesson 1 tutorial on the video tape. These short tutorials are an important part of the course. Many of the final exam questions are based on the material presented in these tutorials.

- Complimentary Metal Oxide Semiconductor (CMOS) is a manufacturable integrated circuit process consisting of n-channel and p-channel MOSFETs. CMOS is used in the fabrication of most processors and memory.

- CMOS integrated circuits are fabricated in a wafer. The wafer is cut-up into die which are connected to a lead frame and encapsulated in plastic.

- The layout view of an integrated circuit is the "top view" while the cross-sectional view is the side view.

- Fing to bet down, with a ghitzake between the statement.

- Difference which is mound by CMOS tester longe and why CMOS is perioder for making intermed density.

- Explain-screen the solutional leads one set spit how they go used in endang a packager internet contait.

- Determine the differance between Labor and every second relation in meaning elements.

#### Fashing Assignment

Read an above (1) and members (4) when weath not care have be due (1) (5) (Laporat System for Intel calculation, the advected (1) (apply) (b) out starts device in the lifeth or device (1) on Chapter (1) and dependential that I went taxals invert the address gas on in the table. This colored will not descent the me of 1.4 kg.

Video Asstymment

We have been as a second could be to be realized and the second of the matter of the second of the second for the first second court and there are been and the matter of the term to the second secon

## Lesson 2 - THE WELL

Kay Paints

- The n-well is used for the ambing the body of p-channel MODER (s. in a resistor or as a diode when used with the p-schorate.

- The likeliness of any finitestate repairing the SS p use of short resistance with users of character carety in

## Learning Objectives

After completing this lesson you will be able to:

- Describe what an n-well is and how it is fabricated.

- · Lay out an n-well.

- · Discuss sheet resistance and how to calculate the value of an n-well resistor.

- Analyze how the n-well forms a diode with the substrate

- Determine the origins of depletion capacitance.

- Explain RC delay through an n-well.

## Reading Assignment

Read chapter 2 of the text. Also review the parameters related to the n-well, such as sheet resistance, given in Appendix A for the CN20 process.

Induced an Processor Problem Solutions Problem 2.4: The maintain, typical and reasoner values of estativity  $\theta$  for an event with a dickness of 3.000 is equal to  $\theta_{main}$  whereas (reas Appendix A. Table A.7.  $\theta$  is C(00, 7.500)and 0.000  $\Omega$  can

## Video Assignment

Watch the Lesson 2 tutorial on the video tape. Again, these videos are an important portion of the course and will cover material that will be on the final exam.

principal and an inclusion with the arm hand deniction and the arms that an

if \$2 > 1 Megazium the delay is given by

In the Particle of MRED and

## 713AA 3

## Key Points

- The n-well is used for the making the body of p-channel MOSFETs, as a resistor or as a diode when used with the p-substrate.

- The thickness of any fabricated layer in a CMOS process is constant. This fact leads to the use of sheet resistance with units of ohms/square to specify a resistance of a material.

- A parasitic depletion capacitance exists between any pn junction such as the junction between the p-substrate and the n-well.

- Because of the parasitic depletion capacitance an n-well resistor will exhibit delay, i.e. an input signal to one side of the resistor will take a finite amount of time to reach the other side of the resistor.

## **Practice Problems**

Complete problems 2.4, 2.5, 2.10 (without the SPICE simulation).

## **Practice Problem Solutions**

**Problem 2.4**: The minimum, typical and maximum values of resistivity  $\rho$  for an n-well with a thickness of 3  $\mu$ m is equal to  $R_{square} \cdot thickness$ . From Appendix A, Table A.7,  $\rho$  is 6,000, 7,500, and 9,000  $\Omega \cdot \mu$ m.

**Problem 2.5**:  $I_s = J_s \cdot L \cdot W = 10^{-8} A/m^2 \times 10^{-4} m \times 10^{-4} m = 10^{-16} A$ .

**Problem 2.10**: For a  $5\mu m \times 2000 \mu m$  n-well, the capacitance C is simply the product of the bottom area of the resistor with the zero bias depletion capacitance, or,

$C = 100 aF \times 5^2 \times 400 = 1 pF$

or if R = 1 Megaohm the delay is given by  $t_d = 0.35RC = 0.35 \times 1 \, pF \times 1 \, M\Omega = 350 \, ns$

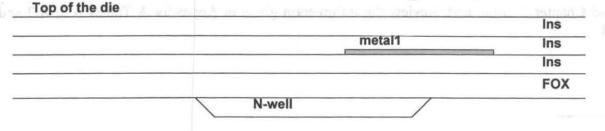

## Lesson 3 - THE METAL LAYERS

e of the CMDS inventon-well, metally via, exactly, and everybast should be understood.

## G.

#### Learning Objectives

After completing this lesson you will be able to:

- · Determine what the metal and via layers are and how they are laid out in a CMOS process.

- Discuss the parasitics associated with the metal layers.

- Explain electromigration and how to size metal wires.

- Analyze cross talk and ground bounce.

#### **Reading Assignment**

Read Chapter 3 in the text. Review the information given in Appendix A Tables A.3, A.7 and A.8.

A 2 Three bo

## Video Assignment

Watch the Lesson 3 tutorial on the video tape.

## Key Points

- The bonding pad is used to connect the chip to the lead frame.

- The metal layers are used to "wire" the integrated circuits together.

- There is a limit on the amount of current that can flow through a wire due to either the wire's sheet resistance or electromigration.

Problem 3.11: From Fig. P.(1) the area actives trained and would is 72 um while

- The parasitic resistance of a wire can cause "ground bounce".

- The parasitic capacitance associated with a wire can result in coupled "noise" on the wire.

- Use of the CMOS layers: n-well, metal1, via, metal2, and overglass should be understood.

## Practice Problem Solutions

Problem 3.2:

**Problem 3.6**: Considering only the plate capacitance, assume the area of metal1 and metal2 is A um<sup>2</sup>. The capacitance between metal1 and metal2, from App. A, is 38 aF/um<sup>2</sup>. The capacitance between metal1 and substrate is 26 aF/um<sup>2</sup>. The voltage change on metal1 =  $1V \times (38AaF/\mu m^2/(38A + 26A)aF/\mu m^2) = 0.594V$ .

**Problem 3.7**: Taking  $J_{al} = 1$  mA/um the maximum current = 5 um x 1mA/um = 5 mA. The limitation for the contacts = 5 mA/(0.4 mA/contact) = 12.5 =>> 13 contacts needed.

**Problem 3.11:** From Fig. P3.11 the area between metal1 and metal2 is 72 um while the perimeter is 36 um. The area between metal1 and substrate is 12 um x 18 um or 216 um and the perimeter is 60 um.  $C_{12} = (38 \times 6 \times 12 + 104 \times 36) \text{ aF} = 6.48 \text{ fF}, C_{1sub} = (26 \times 12 \times 18 + 82 \times 60) \text{ aF} = 10.536 \text{ fF}$ . The voltage change on metal1 is  $\Delta V_{metal1} = 5V \times C_{12}/(C_{12} + C_{1sub}) \approx 1.9V$

## Lesson 4 - THE ACTIVE AND POLY LAYERS

## Learning Objectives

After completing this lesson you will be able to:

- Discuss layers: n+, p+, contact, poly1.

- Lay out a MOSFET and a standard cell frame.

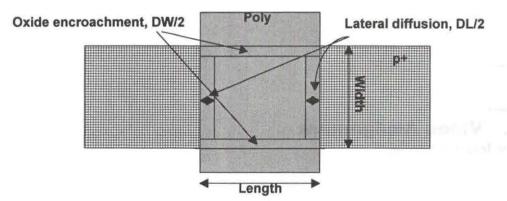

- Describe oxide encroachment and lateral diffusion.

- Explain why modern CMOS is termed a "self-aligned gate" process.

#### Reading Assignment

• Read Chapter 4 of the textbook and review Appendix A tables A.3, A.4, A.5, A.7 and A.8.

## Video Assignment

Watch the lesson 4 tutorial.

## Key Points

Metal1 must connect downwards to n+, p+ or poly. It cannot be connected directly to the n-well or the p-substrate.

Problem 4.5: See figure access. (a) From 2a 13104 modul pastro-tops for the p-chai MOSPET is intercedis. A. D.C. off) - 0.64424 des. (c) The lateral difference tops not affin

- A MOSFET is formed by laying out polysilicon (poly) over active (n+ or p+).

- A standard cell frame is used to route ground and power throughout the layout and to provide substrate and well tie-downs close to the areas where the MOSFETs are laid out.

• Lateral diffusion affects the length of a MOSFET while oxide-encroachment affects the width.

Practice Problems

Complete problems 4.4, 4.5, and 4.8.

#### **Practice Problem Solutions**

**Problem 4.4**: (a) From the BSIM model parameters for the p-channel MOSFET in Appendix A, the delta-width due to the oxide encroachment, DW (dw), is 0.162551 um. (b) The oxide encroachment does not affect the length of the MOSFET. From the following layout, the location of the oxide encroachment illustrates this clearly.

**Problem 4.5**: See figure above. (a) From the BSIM model parameters for the p-channel MOSFET in appendix A, DL (dl) = 0.84424 um. (b) The lateral diffusion does not affect the width of the MOSFET. From the above layout, the location of the lateral diffusion can illustrate this clearly.

**Problem 4.8**: cj of the n+ implant is  $1.0375 \times 10^{-4} \text{ F/m}^2$ , and cjsw is  $2.1694 \times 10^{-10} \text{ F/m}$ , from page 710 and also page 77, AD = 10 x 10 um2, PD = 4 x 10 um, therefore, the maximum capacitance, i.e. the zero bias depletion capacitance =  $1.0375 \times 10^{-4} \text{ F/m}^2 + 2.1694 \times 10^{-10} \text{ F/m} \times 40 \text{ um} = 10.375 \text{ fF} + 8.6776 \text{ fF} = 19.0526 \text{ fF}$ . This depletion capacitance will decrease if the n+ implant is held at a constant potential while the potential of the substrate is reduced.

The budy affect results in an increase in the threshold voluge of a MOSFET.

## Lesson 5 - THE MOSFET AS A CAPACITOR

#### Learning Objectives

After completing this lesson you should be able to:

- Explain the difference between strong inversion, weak inversion, and the depletion modes of MOSFET operation.

- Lay out a "natural" MOSFET capacitor.

- Discuss how the threshold voltage is derived.

Reading Assignment Read Sections 5.1 and 5.2 of the text.

Frablain S.4: When the MONFET is operating in the namunulation region, a large quarker of bilest and situated helow the gate oxide. There is no induced channel between the durin and source. Therefore, the expectative between gate and sourcestance is equil to the coorder transitioner. (6., -W-LD)/TC/C

### Video Assignment

Watch the Lesson 5 tutorial. This tutorial will cover information not contained in Chapter 5 of the book.

where N<sub>i</sub> is the number of acceptor atoms in the substrates at is the intrinsic currier concentration of silicon,

- Applying a potential greater than the MOSFET threshold voltage causes the surface at the oxide and semiconductor to "invert" forming a channel that connects the drain to the source of a MOSFET.

- When used correctly a MOSFET can make a very good capacitor.

- The body effect results in an increase in the threshold voltage of a MOSFET.

- A p-channel MOSFET can be laid out in its own well to eliminate body effect.

Complete problems 5.3, 5.4, 5.5, and 5.8.

#### **Practice Problem Solutions**

**Problem 5.3**: Since the MOSFET is operating in the strong inversion region a large amount of electrons are attracted under the gate and an induced channel is formed below the gate oxide. This channel connects the source and drain so the gate overlap of the source drain has no effect on the capacitance. The capacitance between the gate electrode and the source/drain is simply  $C_{ox} = C'_{ox} \cdot W \cdot L$

**Problem 5.4**: When the MOSFET is operating in the accumulation region, a large number of holes are attracted below the gate oxide. There is no induced channel between the drain and source. Therefore, the capacitance between gate and source/drain is equal to the overlap capacitance,  $(\varepsilon_{ox} \cdot W \cdot LD)/TOX$

**Problem 5.5**:  $C'_{ox} = \varepsilon_{ox}/TOX = (8.85 \times 3.97 \ aF/\mu m)/(400 \times 10^{-10} m) = 878 \ aF/\mu m^2$

**Problem 5.8**: The electrostatic potential at the oxide-semiconductor interface when  $V_{GS} = V_{THN}$  is:  $\phi_s = -\phi_F = \frac{kT}{q} \ln \frac{N_A}{n_i}$

where  $N_A$  is the number of acceptor atoms in the substrate,  $n_i$  is the intrinsic carrier concentration of silicon.

#### Key Points

- Applymp a potential power that the black IIT that hold vourge correct the surface or the exide and some conductor in "invert" forming a cheene, that corrects the deals to the source of a MONET T.

- When used correctly a MOCTOT CONTRACT a visor good constraint.

CMOS Digital Circuit Design

## Learning Objectives

After completing this lesson you will be able to:

- Determine the basic operation of an n-channel MOSFET. •

- Recognize how changing the gate-source or drain-source voltage of a MOSFET changes the MOSFETs drain current.

- Discuss channel length modulation; what it is and where it comes from. ٠

Read Section 5.3 and Appendix A of the text.

Video Assignment Watch the Lesson 6 tutorial.

- Key Points The inverted channel under the gate oxide has a sheet resistance that is a function of the applied  $V_{GS}$ .

- The MOSFET enters the saturation region when the charge in the channel becomes zero at . the channel-drain interface.

• Channel length modulation results from the electrical channel length changing with drain to source potential.

Practice Problems

Complete problems 5.13, 5.14, 5.15.

#### Practice Problem Solutions

**Problem 5.13**: Since every MOSFET shown in Fig. P5.13 has the same  $V_{DS}$ ,  $V_{GS}$ , KP, L and  $V_{THN}$ , the current flowing in each MOSFET is:

$$I_{Dn} = KP \cdot \mu_n \cdot \frac{W_n}{L} (V_{GS} - V_{THN})^2 \text{ or } I_{Dn} = KP \cdot \mu_n \cdot \frac{W_n}{L} \left[ (V_{GS} - V_{THN}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

or since  $I_{Dtotal} = I_{D1} + I_{D2} + ... + I_{dm}$

$$I_{Dtotal} = KP \cdot \mu_n \cdot \frac{W_1 + W_2 + \dots + W_n}{L} (V_{GS} - V_{THN})^2$$

and for the triode region

$$I_{Dn} = KP \cdot \mu_n \cdot \frac{W_1 + W_2 + \dots + W_n}{L} \left[ (V_{GS} - V_{THN}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

**Problem 5.14**: Calling the node connected to the drain of M1 and the source of M2 " $V_1$ " then  $V_{GS1} = V_G$  (the voltage on the gates assuming the source of M1 is grounded),  $V_{DS1} = V_1$ ,  $V_{GS2} = V_G - V_1$ ,  $V_{DS2} = V_D - V_1$  (where  $V_D$  is the voltage on the drain of M2 to ground). If M1 operates in the saturation region, then  $V_{DS1} \ge V_{GS1} - V_{THN}$ , i.e.  $V_1 \ge V_G - V_{THN}$ . For M2,  $V_{GS2} - V_{THN} = V_G - V_1 - V_{THN} \le 0$ . This means that M2 cannot conduct a current if M1 is operating in the saturation region so, therefore, M1 can either operate in either the cutoff region or the triode region but not the saturation region.

**Problem 5.15**: From Figure P5.14, we assume the most general case when both MOSFETs are operating in the triode region. We know from the previous problem that M1 can't operate in the saturation region. We can write:

$(I_D \times L1)/(KP \times W) = [(V_G - V_{THN})V_1 - V_1^2/2]$  and

$(I_D \times L2)/(KP \times W) = [(V_G - V_{THN} - V_1)(V_D - V_1) - (V_D - V_1)^2/2].$

Adding these two equations results in  $I_D \times (L_1 + L_2)/(KP \times W) = V_G V_D - V_{THN} V_D - V_D^2/2$  which can easily be put into the desired form, i.e.,  $I_D = [(KP \times W)/(L_1 + L_2)] \cdot [(V_G - V_{THN})V_D - V_D^2/2]$

## Lesson 7 - THE SHORT CHANNEL MOSFET

**Learning Objectives**

After completing this lesson you will be able to:

- Explain what short-channel effects are and their origins.

- Demonstrate an understanding of the concept of scaling MOSFETs.

- · Discuss "drive current" and how it is used to characterize modern CMOS devices.

## Reading Assignment

Read section 6.3 and review the information given on the CMOS14TB process in Appendix C.

**Problem 6.6**: From Fig. 6.5, at 10° years, reveal electron and build verticence an electronic weight of w<sub>eat</sub> and y<sub>low</sub> are approximately 10° and 9 x 10° converticence respectively. From Ea. (a. 27 de malality of the electronic is 100 cm<sup>2</sup>Vy and the mobility of the context of the states? Va

Printlen 6.11: This mobilizer whitney is shown to Argent

#### Video Assignment

Watch the Lesson 7 tutorial.

- Scaling is useful in CMOS design to reduce die size.

- As the channel length of a MOSFET is reduced the velocity of carriers traveling between the source and drain saturates causing the mobility of the carriers in the device to drop. This results in a reduction in current for a given gate to source voltage.

- The drain current is linearly related to the gate to source voltage in a short channel MOSFET.

Practice Problems

Complete problems 6.5, 6.6 and 6.11.

#### Practice Problem Solutions

Problem 6.5: The drive current of a short channel MOSFET is given by Eq. 6.4:

$$\begin{split} I_{drive} &= v_{sat} \times C'_{ox} \times (V_{GS} - V_{THN} - V_{DS,sat}) \\ C'_{ox} &= \varepsilon_{ox}/TOX = (8.85 \times 3.97 \ aF/\mu m)/(75 \times 10^{-10} m) = 4.685 \ fF/\mu m^2 \\ I_{drive} &= 10^7 \ cm/s \times 4.685 \ fF/\mu m^2 \times (2.5 - 0.5 - 1.5) \\ V &= 234 \ \mu A/\mu m \end{split}$$

For the long channel MOSFET described in Ch. 5 we assumed the mobility was a constant, i.e. not a function of  $V_{DS}$ . For short channel MOSFETs  $V_{DS,sat}$  is not directly dependent on  $V_{GS}$  and  $V_{THN}$ , but it is related to the carrier drift velocity. From Fig. 6.8 and Eq. 6.39  $V_{DS,sat}$  is dependent directly on the critical electrical field which causes the drift velocity to become  $v_{sat}$ .

**Problem 6.6**: From Fig. 6.8, at  $10^5$  V/cm, both electron and hole velocities are saturated where  $v_{nsat}$  and  $v_{psat}$  are approximately  $10^7$  and 9 x  $10^6$  cm/s respectively. From Eq. 6.39 the mobility of the electrons is  $100 \text{ cm}^2/\text{Vs}$  and the mobility of the holes is  $90 \text{ cm}^2/\text{Vs}$ .

Problem 6.11: This problems solution is shown in Appendix C.

## Lesson 8 - THE DIGITAL MODEL OF A MOSFET

Deadler polition 101, and 107 of sets 2010 dates of

After completing this lesson you will be able to:

Model the MOSFET for digital circuit design.

Read Chapter 10 of the text.

**Video Assignment**

Watch the Lesson 8 video tutorial.

- The MOSFET can be modeled by a switch in series with a resistor and two capacitors; one used for modeling the input capacitance of the MOSFET and one used for modeling the output capacitance.

- An n-channel MOSFET passes a logic high with a threshold voltage drop while a p-channel MOSFET passes a logic low with the addition of a threshold voltage.

- · Series connection of MOSFETs can be used to implement multiplexers.

## **Practice Problems**

Complete problems 10.1, and 10.7 (without SPICE simulations).

#### **Practice Problem Solutions**

Problem 10.1: For a 10um/2um MOSFET, the effective resistance of the NMOS is

$$R_n = 12 \, k\Omega \times \frac{2}{10} = 2.4 \, k\Omega$$

and for the PMOS,  $R_p = 36 k\Omega \times 0.2 = 7.2 k\Omega$ . The capacitance between the drain and ground is the same for both NMOS and PMOS (since they have the same width and length) and is equal to  $C_{ox} + 150$  fF or 166 fF. From Eq. 10.8 and 10.9, for NMOS,

$t_{PHL} = 2.4k \times 166f \approx 398 \, ps$ , and  $t_{HL} = 2 \times 2.4k \times 166 \, fF \approx 797 \, ps$

and for the PMOS,

$t_{PLH} = 7.2k \times 166f \approx 1.2ns$ , and  $t_{LH} = 2 \times 7.2k \times 166fF \approx 2.4 ns$

Problem 10.7: For a 3um/2um MOSFET, the effective resistance of the NMOS is

$$R_n = 12 \, k\Omega \times \frac{2}{3} = 8 \, k\Omega$$

and for the PMOS,  $R_p = 36 k\Omega \times 0.66 = 24 k\overline{\Omega}$ . The capacitance between the drain and ground is the same for both NMOS and PMOS (since they have the same width and length) and is equal to  $C_{ox} + 1$  pF or approximately 1pF total. From Eq. 10.8 and 10.9, for NMOS,

$t_{PHL} = 8k \times 1pF \approx 8 ns$ , and  $t_{HL} = 2 \times 8k \times 1pF \approx 16ns$

and for the PMOS,

$t_{PLH} = 24k \times 1pF \approx 24ns$ , and  $t_{LH} = 2 \times 24k \times 1pF \approx 48 ns$

(2) Set of the state of the second set of the set of the state of the state of the state of the plant of the state of t

## Lesson 9 - INVERTER OPERATION I

### Learning Objectives

After completing this lesson you will be able to:

- . Recognize the circuit topology of an inverter.

- Determine the operation of the inverter and how sizing the p- and n-channel MOSFETs affects the switching point voltage and speed of the inverter.

- Examine the layout of an inverter.

Read sections 11.1 - 11.3 of the text.

Example 11.1 (repeat) with VSP = 2.0 V: We are 1-write equilation

Video Assignment Watch the lesson 9 video tutorial.

## **Key Points**

- The maximum output voltage of a CMOS inverter is VDD while the minimum output voltage is ground. The switching point voltage lies somewhere between these boundaries and is set by the size of the MOSFETs.

- By changing the size of the MOSFETs we can change the "drive" or effective resistance of a MOSFET.

## Practice Problems

Complete problems 11.1 and 11.2 without SPICE simulations and repeat Example 11.3 with a switching point voltage of 2.0V.

#### **Practice Problem Solutions**

**Problem 11.1:** From Eq. 11.4 with  $V_{SP}$  approximately equal to  $V_{THN}$ ,  $\beta_n$  should be much larger than  $\beta_p$ . In a basic inverter, for both NMOS and PMOS, if the length of devices is the same and  $W_n = 400$  um and  $W_p = 3$  um then  $V_{SP} = (20V_{THN} + VDD - V_{THP})/(1 + 20) = 1.05$  V.

**Problem 11.2**: With W = 10 um and a load capacitance of 1 pF,  $C_{tot} = 1pF+(2 \times 10 \times 2 \times 800aF)=1.032pF$ .  $R_{n1} = 12k\Omega \times 2/10 = 2.4 k\Omega$ ,  $R_{p2} = 7.2 kW$ . The propagation delay times are  $t_{PHL} = 2.4k\Omega \times 1.032pF = 2.5ns$  and  $t_{PLH} = 7.2k\Omega \times 1.032pF = 7.43ns$

**Example 11.3 (repeat)** with VSP = 2.0 V: We can re-write equation 11.4 (with  $V_{THN} = 0.8$ , VDD = 5 and  $V_{THP} = 0.9$ ) so it reads

$$2 = \frac{\sqrt{\frac{\beta_n}{\beta_p}} \cdot 0.8 + 4.1}{1 + \sqrt{\frac{\beta_n}{\beta_p}}}$$

solving for the transconductance ratios yields,  $\beta_n/\beta_p \approx 3.0$ . Since KP<sub>n</sub> = 3KP<sub>p</sub> so setting  $W_n = W_p$ , and  $L_n = L_p$  yields the  $V_{SP} = 2V$ .

If Way Policy a subset is a subset of the construct of WED we conduct the subset of the subset of

## Lesson 10 - INVERTER OPERATION II

Practice Problems

Practice Problem Selations

Complete problems 11.5 (without simulations) and repeat examples 11.8 and 11.9 with ten increase in load expeditance to 50 pl

## Learning Objectives

After completing this lesson you will be able to:

- Design CMOS off-chip buffers.

- Lay out large MOSFETs.

- Recognize other inverter configurations.

Integrals),  $R = (122 \times 2/50 - 26k + 2/150) = 0.95k$ , and the output connectance is  $C = 2 \times 50 \times 80$ of  $r + 2 \times 150 \times 300$  af r = 320 (F = -32 pF. To drive 50 pF load equationate in  $r_1$  a time sing buffer, i.e. N = 2. Area = [50 pF/(0.32 × 3/2) of ] = 4.205. Using Eq. 11.25, the acing is

Read sections 11.4 and 11.5 in the text.

Example 11.5 (repeat) with  $\tau$  50 pF loads but  $\tau \tau \tau \tau = (8k + 8k) t0 nF - 800 m$

and add out of the desident entry submission

Watch the lesson 10 video tutorial.

## Key Points

- A buffer, made from a string of inverters, is used to isolate on-chip logic signals from large off-chip capacitances.

- Minimum delay through a buffer is sacrificed for smaller layout area in most practical buffer designs.

- Other inverter topologies can be used when a large number of inputs is needed or a tri-state output is required.

agentine Objectives

## 4.)(영어G ))의 '이크 V M - 0 이 # # #

### **Practice Problems**

Complete problems 11.5 (without simulations) and repeat examples 11.8 and 11.9 with an increase in load capacitance to 50 pF.

## **Practice Problem Solutions**

**Problem 11.5**: For the first inverter with size 150/50, the total resistance is (assuming 2 um length),  $R = (12k \times 2/50 + 36k \times 2/150) = 0.96k$ , and the output capacitance is  $C = 2 \times 50 \times 800$  aF + 2 x 150 x 800 aF = 320 fF = .32 pF. To drive 50 pF load capacitance, try a three stage buffer, i.e. N = 3. Area = [50 pF/(0.32 x 3/2)pF] = 4.705. Using Eq. 11.25, the delay is,

$t_{PHL} + t_{PLH} = 3 \times (.96k) \times (.32pF + 4.705 \times 0.48pF) = 7.426ns < 10ns$ using a two stage buffer, A = 10.206.  $t_{PHL} + t_{PLH} = 2 \times (.96k) \times (.32pF + 10.206 \times 0.48pF) = 10.02ns > 10ns$ therefore, a three stage buffer must be used.

**Example 11.8 (repeat)** with a 50 pF load:  $t_{PHL} + t_{PLH} = (8k + 8k)50pF = 800 ns$

#### Example 11.9 (repeat) with a 50 pF load:

If we try three stages the area factor is  $A = (50p/28.8f)^{1/3} = 12$  with a resulting delay of 3(16k) x (19.2f + 12 x 28.8f) = 17.5 ns > 15 ns. If we try five stages than  $A = (50p/28.8f)^{1/5} = 4.44$  with a resulting delay of 3(16k) x (19.2f + 4.44 x 28.8 f) = 7.06 ns.

Kinin Rosali

- A Millin multi fram is king of a surface, is used to indust much papit, showing integer official surveys, set.

- 4. Minimum datas, etc. spinolenter esservitores to secular lapore uno de most procuest funites designs.

- Other interver topologies the beared when a large number of materies recorded or a tri-state output is topologies.

## Lesson 11 - STATIC LOGIC GATES

b) (war = 8.594m) and (war = 500m)

## Learning Objectives

After completing this lesson you should be able to:

- Discuss the basic operation and topologies of CMOS static logic gates. .

- Recognize switching characteristics of CMOS static logic. .

- Design and operate CMOS complex logic gates.

(a) 学校(「Gaute 0, 10, n = 3×23((0,8)) + 3×3×8 + (0 + 0.35 - 24k×7.27) - (12×1,394) **Reading Assignment**

Read Chapter 12 in the course textbook.

Problem 12.6: Assuming minimum the MOSFETs nume 3 x 14k x 50f = 5.1 m while ton 18 1-2

Watch the lesson 11 video tutorial.

## **Key Points**

- Static gates are formed by complementary connections of series (parallel) NMOS with parallel (series) connections of PMOS.

- Large numbers of series connected MOSFETs can result in long propagation delays.

- Complex CMOS logic gates can be use to implement logic functions in a single gate that are not possible to implement NANDs and NORs alone.

Complete problems 12.3 (without simulations) and problem 12.6.

## **Practice Problem Solutions**

**Problem 12.3**: For an n-input NOR gate, we have:  $t_{PLH} = NR_p(C_{outp}/N + N \cdot C_{outn} + C_{load}) + 0.35R_pC_{inp}(N-1)^2$   $t_{PHL} = (R_n/N)(NC_{outn} + C_{outp}/N + C_{load})$ with minimum size MOSFETs,  $R_n = 8k\Omega$ ,  $R_p = 24k\Omega$ ,  $C_{outn} = C_{outp} = 4.8fF$ ,  $C_{inp} = 7.2fF$  for 3 inputs.

a) With  $C_{load} = 0$ ;  $t_{PLH} = 3 \times 24k(4.8/3 + 3 \times 4.8 + 0) + 0.35 \times 24k \times 7.2(3 - 1)^2 = 1.394ns$  $t_{PHL} = (8k/3)(3 \times 4.8 + 4.8/3 + 0) = 42.67ps$ b)  $t_{PLH} = 8.594ns$  and  $t_{PHL} = 309ps$

**Problem 12.6**: Assuming minimum size MOSFETs  $t_{PLH} = 3 \ge 24 \ge 50$  f = 3.6 ns while  $t_{PHL}$  is 1.2 ns.

- i. arge numbers of neries consensed in 161 KFs ecapterity in long encyclinitian delays.

- Complian CordSt legite datas dito ac ute to frigidation in tangle functions in a mingle gase that are not powerfile to enclosure NACEL and EPDIs al net.

## Lesson 12 - THE TRANSMISSION GATE

### Learning Objectives

After completing this lesson you will be able to:

- Discuss how a transmission gate (TG) operates. ٠

- Determine the design of logic elements, such as path selectors, using the TG. .

- Explain how a TG is used in an edge triggered flip flop. .

#### Video Assignment

Watch the lesson 12 video tutorial.

is on, allowing the O output to discume in the couple or show latch. When CLK nors his and T4 turn off and TMD sum on This renewes the D issue from the measur back and an print B to drive the output Q. The value of the D in an an prior to cleak group linch at pasta Key Points

- Using both an n-channel and p-channel switch in parallel will allow passing both a logic high (VDD) and a logic low (0 V).

- The TG can be used in path selector circuits and in a multiplexor/demultiplexor.

- Edge triggered flip-flops rely on the TG to gate input signals between master and slave latches.

#### Practice Problems

Complete problem 13.4 and describe how the edge triggered flip-flop shown in Figure 13.20 operates.

## **Practice Problem Solutions**

Problem 13.4: The sketch is shown below.

If  $C_{load} = 50$  fF the total delay is (assuming minimum size)

$t_d = 0.35 \times 2.5C_{ox} \times R_n \times N^2 + N \times R_n \times C_{load}$ = 0.35 \times 2.5 \times 800 af/\mumma \times 6\mum<sup>2</sup> \times 8k \times 9 + 3 \times 8k \times 50 fF = 1.5 ns

**Description of the operation of Fig. 13.20(b)**: This is a master/slave implementation of a D-FF. When CLK is a low T1 is on, allowing the D input to drive node B. Also when CLK is a low T4 is on, allowing the Q output to circulate in the output or slave latch. When CLK goes high T1 and T4 turn off and T2/T3 turn on. This removes the D input from the master latch and allows point B to drive the output Q. The value of the D input just prior to clock going high is passed to the Q output.

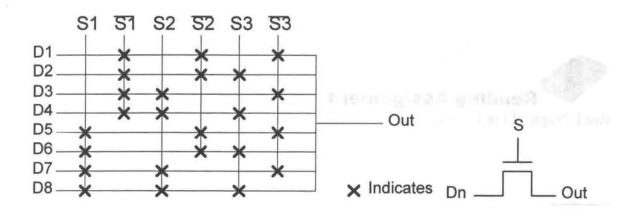

## Lesson 13 - DYNAMIC CMOS LOGIC

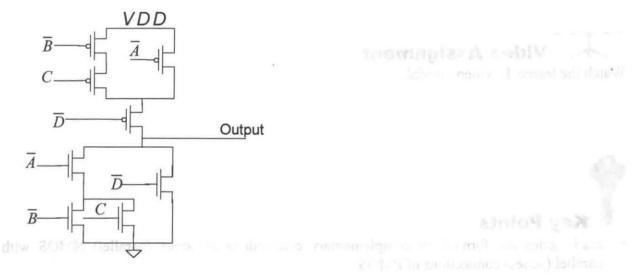

Complete probleme 14.5 and 14.6 (without simulation require.

## Learning Objectives

After completing this lesson you will be able to:

- Discuss the fundamentals of dynamic logic.

- Determine why a nonoverlapping clock is needed in some dynamic logic circuits.

- Recognize the different topologies for dynamic logic (e.g., clocked, PE, NP, etc.)

Video Assignment

Read Chapter 14 in the text.

## 7

Watch the lesson 13 video tutorial.

- Key Points

- Dynamic circuits utilize high-impedance (capacitive) nodes to store a charge corresponding to a logic level.

- High-impedance nodes are subject to charge leakage.

- · High-speed and very dense logic can be implemented using dynamic circuits.

Complete problems 14.5 and 14.6 (without simulation results.)

#### **Practice Problem Solutions**

**Problem 14.5**: Assuming minimum size devices are used (3um/2um) then the worst case  $t_{PHL}$  is:

$t_{PHL} \approx 3 \cdot R_n \times C_{load} = 3 \times 8k \times 50 \, fF = 1.2 \, ns$

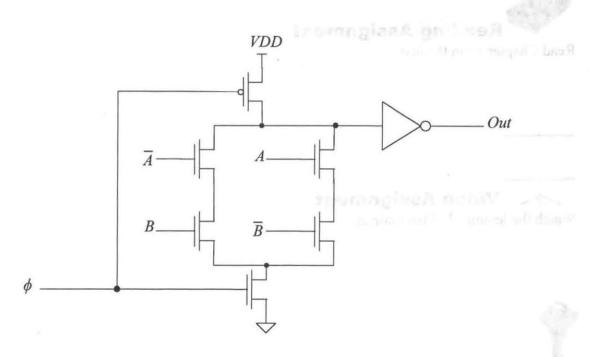

Problem 14.6: The schematic of the design is shown below.

#### Nev Points

- Dymamic e name dished 10,000 miph tariph tariph tariph in distance a dishe a dishe ta dishe taripa a tariph ta

- Epison per la place de servicie de se la presentação

- Hyperpetitional varies for the construction of an interval on the directory.

## Lesson 14 - VLSI LAYOUT

Practice Problems

Explain have connections would be made to the MULQDEMUX layout abown in Fig. F. (

## Learning Objectives

After completing this lesson you will be able to:

- Discuss the design of standard cells.

- Recognize example layouts of digital logic.

- Determine bussing considerations when laying out a chip.

come through the metally to a constant and then down to the net. Note, in order to weith design rule violations we might have to extend the arcassociated with the A lapor to the left in this frame.

Read chapter 15 of the textbook.

Video Assignment

Watch the lesson 14 video tutorial.

- Reducing die size increases the number of die on a wafer. The yield and profit increase with number of die/wafer.

- Utilizing standard cells can help speed up the time it takes to lay out a chip.

- Bussing can be an important concern when designing a large chip.

## Lessan 14 - VLSI LAYOUT

## **Practice Problems**

Explain how connections would be made to the MUX/DEMUX layout shown in Fig. 15.15.

### **Practice Problem Solutions**

The connections would be made using metall to the n+ active area through a contact. The active area can be thought of as a wire connection. The connection to the A input, for example, would come through the metall to a contact and then down to the n+. Note: in order to avoid design rule violations we might have to extend the n+ associated with the A input to the left in this figure.

V Video Assignment Wated the let on 14 video control

anvitosid@ hain esti

#### Key Foliats

- Reducing the constituents the netwice of the on a water. The visit and profit interests with interior chain-offic.

- Utilizing contact calls etc. help speed up the mere is mich to by set a stuff.

- Baising can be important advanta when defining a organistic

# Digital Circuit Design Final Examination

Lesson 1 - An overview of CMOS circuit design

#### FINAL EXAM DIRECTIONS

This examination covers the material presented in the Study Guide for "CMOS Digital Circuit Design." This exam is divided into sections which correspond to the Study Guide lessons. It consists of 100 multiple choice questions, each worth 1 point.

A passing grade of 70% is required to receive a Certificate of Achievement from the IEEE. Please take your time, read the questions carefully and then review your answers when you are finished. Record your answers on the perforated answer sheet at the end of the final exam.

This exam is open book, notes, and Study Guide (meaning you can use these as references while taking the exam). Complete and submit the Answer Sheet.

Completed answer sheets may be returned to the IEEE in one of the following ways:

By Mail - send to:

IEEE Education Department 445 Hoes Lane, PO Box 1331 Piscataway, NJ 08855-1331

By Fax - send to "Education" at 732-981-1686

or

A. The body of the p-channel MOSF

By E-mail - send your list of answers along with the appropriate contact information to: ssc-exam@ieee.org

Note: Unless otherwise stated, use the CN20 process parameters given in Appendix A of the text for the problems in this exam.

ions an inim been virus univer o Buranist ro

**GOOD LUCK!**

# Lesson 1 - An overview of CMOS circuit design

1. Which of the following is connected, via a bonding wire, to a lead frame?

A. a wafer

tarmed Latend 2014 2 and 30.0 years and an interesting harmes a structure of the second structure of the second and the second structure of the second

C. plastic encapsulation

D. probe card

2. Of the following, which occurs first?

A. cutting the wafer

B. encapsulating the die of the second of the second second

C. processing the bare wafer

of Land McMark

D. drawing layout

# Lesson 2 - The Well

3. The n-well is used mainly for:

A. The body of the p-channel MOSFETs

B. Making a bipolar transistor

C. As a substrate to make CMOS integrated circuits

D. Making a switch when used with the substrate

4. What is the resistance of an n-well resistor assuming the n-well's sheet resistance is 2,200 ohms per square if the resistor is 5 um wide and 200 um long?

| A. 44k                                                            |                              |

|-------------------------------------------------------------------|------------------------------|

| B. 100k                                                           | 80.2E_H                      |

| C. 250k                                                           |                              |

| D. 88k                                                            |                              |

| 5. Why is sheet resistance used in a CMOS process?                |                              |

| A. Because layout sheets are used to specify how the chip is asso | embled                       |

| D. Descurse all the lowers fabricated have a lower this lowers    |                              |

| B. Because all the layers fabricated have a known thickness.      | V.0.3                        |

| C. Because it is a technical term that may confuse the novice.    |                              |

| D. Because the field implant changes the resistance of the layout | C. The positive po-          |

|                                                                   |                              |

| 6. A depletion layer is formed between:                           | W. "The street lines is with |

| A. the n-well and the field oxide                                 |                              |

| B. the p-type substrate and the field oxide                       | A. a result                  |

|                                                                   | D. the field oxide           |

| C. the n-well and the p-substrate                                 |                              |

| D. the diode and the n-well                                       |                              |

|                                                                   |                              |

| 7. The depletion capacitance of a diode                           |                              |

| A. increases with increasing reverse bias across the diode        |                              |

| B. is not a function of the reverse bias across the diode         | H. Laying out a bonding      |

| C. decreases with increasing reverse bias across the diode        | S. A direct comes            |

| D. is not concern in a diode                                      |                              |

|                                                                   | C. Not mildleg and           |

Theometric directly to the usual

7

8. Estimate the delay through a 100k n-well resistor if the zero bias depletion capacitance between the n-well and substrate is 1 pF.

A. 3.5 ns B. 35 ns C. 100 ns

D. 700 ns

9. If the p-substrate of a wafer is held at ground potential the minimum voltage an n-well can be held at to avoid substrate injection is

A. -0.6 V

B. 0 V

C. The positive power supply voltage

D. -2 V

10. The n-well mask patterned on a reticle is used to pattern what on the wafer?

A. a resist

B. the field oxide

C. the substrate

D. the implant

#### Lesson 3 - The Metal Layers

11. Laying out a bonding pad without using the overglass layer would result in:

A. A direct connection to the metal layers.

B. Not making a connection to the bonding pad because of an insulating layer covering the boding pad.

C. Not making a connection between metal1 and metal2.

D. A connection directly to the n-well.

**Final Examination**

12. Metal1 is closer to the p-substrate so it:

A. is better for routing signals than is metal2.

B. has more resistance than other layers in a CMOS process.

C. has more capacitance to the substrate than does metal2.

D. has more relaxed design rules than does the other layers in a CMOS process.

13. Electromigration can cause erosion in a metal wire and lead to a wire breaking?

- A. True

- B. False

14. For a long length of metal used to transmit a signal, in general, the

- A. electromigration concerns generally set the minimum wire width.