# RESEARCH AND DESIGN OF LOW JITTER, WIDE LOCKING-RANGE ALL-DIGITAL

#### PHASE-LOCKED AND DELAY-LOCKED LOOPS

A Dissertation

Presented in Partial Fulfillment of the Requirements for the

Degree of Doctor of Philosophy

with a

Major in Electrical Engineering

in the

College of Graduate Studies

University of Idaho

by

Feng Lin

March 2000

Major Professor: Russel Jacob Baker, Ph.D.

#### AUTHORIZATION TO SUBMIT

#### **DISSERTATION**

This dissertation of Feng Lin, submitted for the degree of Doctor of Philosophy with a major in Electrical Engineering and titled "Research and Design of Low Jitter, Wide Locking-Range All-Digital Phase-Locked and Delay-Locked Loops," has been reviewed in final form. Permission, as indicated by the signatures and dates given below, is now granted to submit final copies to the College of Graduate Studies for approval.

| Major Professor               | Date                                  |  |

|-------------------------------|---------------------------------------|--|

|                               | R. Jacob Baker                        |  |

| Committee Members             | Date<br>Harry Li                      |  |

|                               | Harry Li                              |  |

|                               | Date                                  |  |

|                               | Richard Wells                         |  |

|                               | Date                                  |  |

|                               | James Frenzel                         |  |

|                               | Date                                  |  |

|                               | Larry Stauffer                        |  |

| Department                    |                                       |  |

| Administrator                 |                                       |  |

|                               | Dave Egolf                            |  |

| Discipline's                  |                                       |  |

| College Dean                  | Date<br>David E. Thompson             |  |

|                               | David E. Thompson                     |  |

| Final Approval and Acceptance | ee by the College of Graduate Studies |  |

|                               | Date                                  |  |

|                               | Charles R. Hatch                      |  |

|                               |                                       |  |

### **Abstract**

PHASE-LOCKED loops (PLLs) and delay-locked loops (DLLs) are often used in integrated circuits in order to compensate for clock distribution delays and to improve overall system timing. PLLs are also widely used in clock recovery and frequency synthesis. When compared to traditional implementations of PLLs and DLLs, an all-digital approach will be found more suitable for monolithic implementation on the same die with other digital circuits. A robust, process-independent performance is expected using all digital techniques.

In this dissertation, several aspects of phase-locked and delay-locked loops are investigated, including building blocks, loop dynamics, noise and jitter. General design criteria are summarized for the all-digital implementation with the comparison to the traditional approaches and popular charge-pump analog implementation.

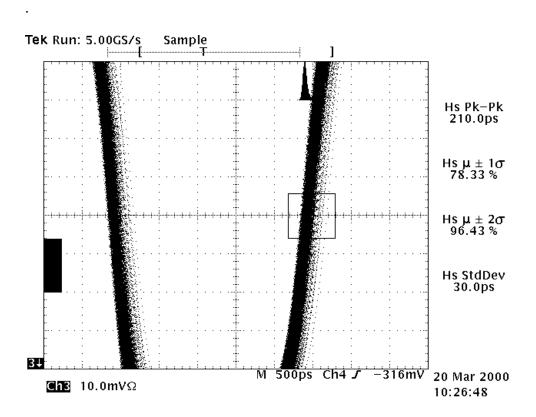

An all-digital phase-locked loop (ADPLL) using a proposed register-controlled oscillator (RCO) and all-digital phase frequency detector (PFD) is developed and fabricated using 0.18um CMOS technology. The two-loop architecture, hierarchy pull-in process and fine phase adjustment make this RCO-based ADPLL achieve less than 80-cycle lock time, 65MHz-385MHz lock range, 30ps RMS jitter and less than 2% duty cycle distortion when the reference clock is at 200MHz. This ADPLL also shows stable operation when power supply voltage is down to 1.4V, which gives more flexibility in low power applications without significant design modification.

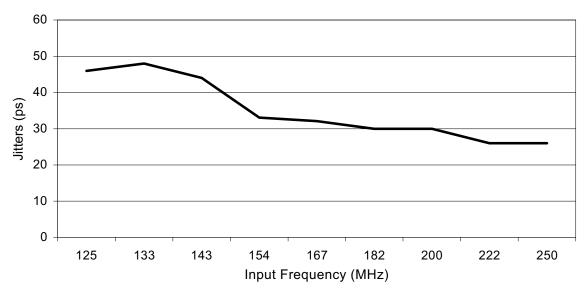

A register-controlled symmetrical DLL (RSDLL), targeted for clock synchronization and de-skewing in double-data rate synchronous DRAM, is implemented based on a symmetrical register-controlled delay line. This RSDLL was fabricated using 0.21µm CMOS technology and achieved 50ps RMS jitter when the operating frequency is in the range of 125MHz to 250MHz. This approach eliminates extra circuitry for duty cycle correction when using both rising and falling edges to latch data. Measurement results are presented to verify its robust operation under different voltage and temperature conditions.

### Acknowledgements

I'd like to thank my dissertation advisor Dr. Jacob Baker for his direction, encouragement in this work. Micron Technology Inc. (MTI) funded this project, manufactured the chip and provided measurement supports, which deserves my special thanks. I'd also like to thank Brent Keeth and Ron Harrison for their valuable discussion; Aaron Schoenfeld for his test setup; and Barbara Cobb, Jim Fabbri, Jeremy Gum, and Suzy Mcdonald for their layout support of this work.

During the course of this degree, my wife Hui has been very supportive and understanding. My mother Jingyi and father Chunxun deserve many thanks for their support and help.

### **Table of Contents**

| Abstract | <b>.</b> iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowl  | edgements v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Chapter  | 1 – Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter  | Acknowledgements       v         Chapter 1 – Introduction       1         Chapter 2 – Phase-Locked Loop Basics       7         2.1. Basic Operations of a PLL       7         2.2. Building Blocks of a PLL       9         2.2.1. Phase Detector       10         2.2.2. Loop Filter       18         2.2.3. Voltage-Controlled Oscillator (VCO)       20         2.3. System Analysis of a second-order PLL       24         2.4. A new candidate – Delay-Locked Loop       28         Chapter 3 – Loop Dynamics and Jitter       31         3.1. Tracking and Acquisition       31         3.1.1. Tracking       32         3.1.2. Acquisition       36         3.1.3. Aided Acquisition       40         3.2. Phase Noise and Jitter       41         3.2.1. Noisy Input – External Jitter       42 |

| 2.       | 1. Basic Operations of a PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.2      | 2. Building Blocks of a PLL 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | 2.2.1. Phase Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 2.2.2. Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 2.2.3. Voltage-Controlled Oscillator (VCO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2        | 3. System Analysis of a second-order PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.4      | 4. A new candidate – Delay-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter  | 3 – Loop Dynamics and Jitter 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.       | 1. Tracking and Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          | 3.1.1. Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          | 3.1.2. Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | 3.1.3. Aided Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3        | 2. Phase Noise and Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          | 3.2.1. Noisy Input – External Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 3.2.2. Noise in the Oscillator – Internal Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 4 – Charge-Pump and All-Digital Loops                          | 53   |

|------------------------------------------------------------------------|------|

| 4.1. Charge-Pump Phase-Locked Loops                                    | 53   |

| 4.1.1. Charge-Pump Basics                                              | 54   |

| 4.1.2. Self-Bias Techniques                                            | 59   |

| 4.1.3. Dead-zone                                                       | 61   |

| 4.1.4. Charge-sharing                                                  | 63   |

| 4.2. All-Digital Loops                                                 | 65   |

| 4.2.1. All-Digital Building Blocks                                     | 65   |

| 4.2.2. Design Criteria of All-Digital Loops                            | 71   |

| 4.2.3. Delay Interpolation                                             | 72   |

| Chapter 5 An All-Digital DLL using the Symmetrical Delay Line          | . 75 |

| 5.1. Synchronization in the Memory System                              | 75   |

| 5.2. Register-Controlled Symmetrical Delay Line (RSDL)                 | 77   |

| 5.3. An All-Digital DLL using the RSDL                                 | . 80 |

| 5.3.1. System Considerations                                           | 80   |

| 5.3.2. Circuits Design                                                 | 83   |

| 5.3.3. Experiment Results                                              | 86   |

| 5.4. Phase Shifter and Register-Controlled Oscillator                  | 89   |

| Chapter 6 – An All-Digital PLL based on Register-controlled Oscillator | 91   |

| 6.1. Design an All-Digital PLL                                         | 91   |

| 6.2. Two-Loop Register-Controlled Oscillator (RCO)                     | 92   |

| 6.2.1. Frequency Granularity of the RCO                                | 93   |

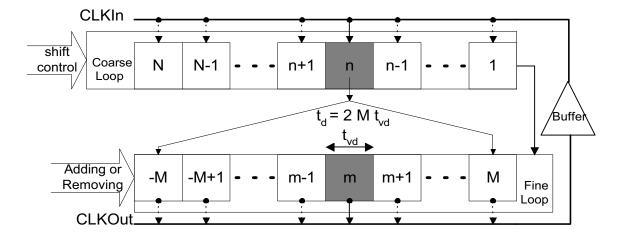

| 6.2.2. Two-Loop Architecture                                           | 96   |

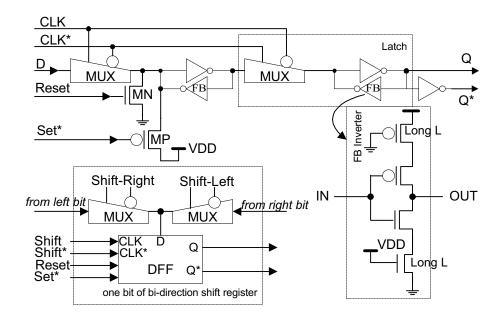

| 6.2.3. Circuit Design                          | , 99 |

|------------------------------------------------|------|

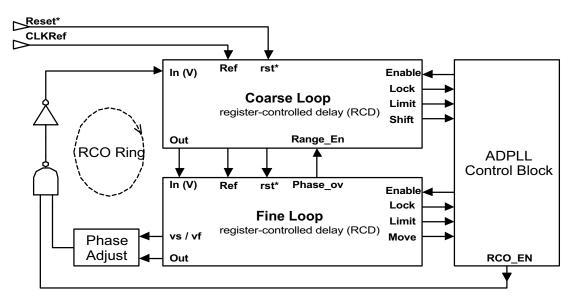

| 6.3. Design the RCO-Based ADPLL                | 100  |

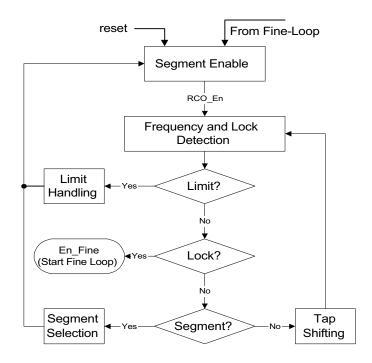

| 6.3.1. Hierarchy Pull-in                       | 102  |

| 6.3.2 Coarse Loop                              | 107  |

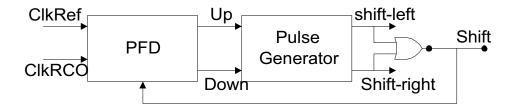

| 6.3.3. All-Digital PFD                         | 109  |

| 6.3.4. Fine Loop                               | 112  |

| 6.3.5. Locking Mechanism in the Fine Loop      | 116  |

| 6.4. Loop Dynamics of the RCO-Based ADPLL      | 119  |

| 6.4.1. Step-in Phase Response                  | 119  |

| 6.4.2. Step-in Frequency Response              | 120  |

| 6.4.3. Limit Handling                          | 123  |

| 6.4.4. Locking Characteristics with Variations | 125  |

| 6.5. Experimental Results                      | 128  |

| Chapter 7 – Conclusion                         | 134  |

| Bibliography                                   | 136  |

## **List of Tables**

| 1.1. | Comparisons between two different implementations of PLLs 4                                                                                                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

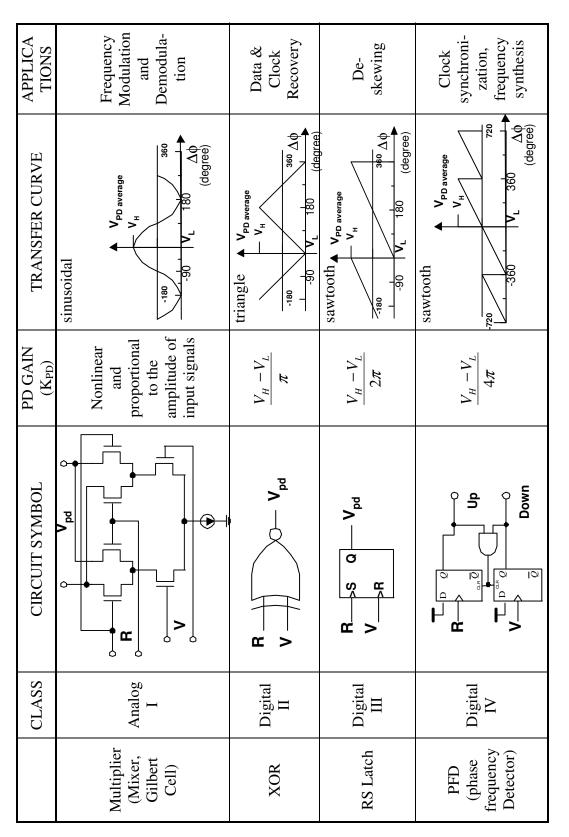

| 2.1. | Circuit symbols and transfer characteristics of different phase detectors based on applications                                                                                                              |

| 2.2. | Summary of lock characteristics of different phase detectors                                                                                                                                                 |

| 2.3. | Different loop parameters for the second-order system based on the various loop filters (Referring to Figure 2.10, $\tau_I = R_1 C$ , $\tau_2 = R_2 C$ ; $\Delta \omega$ refers to the input step frequency) |

| 3.1. | A gain factor according to different kinds of phase detectors                                                                                                                                                |

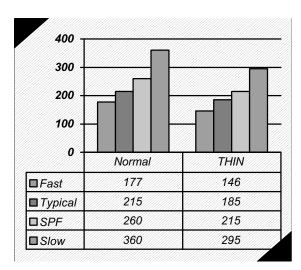

| 5.1. | Summary of the RSDLL test scribe characteristics                                                                                                                                                             |

| 6.1. | RCO lock range versus different parameters                                                                                                                                                                   |

| 6.2. | Summary of main features of the RCO-based ADPLL                                                                                                                                                              |

| 63   | Comparison between existing approaches and the RCO-based ADPLL 133                                                                                                                                           |

# **List of Figures**

| 1.2.  | Clock skew in an integrated circuit                                                                      |

|-------|----------------------------------------------------------------------------------------------------------|

| 2.1.  | Block Diagram of a basic PLL                                                                             |

| 2.2.  | PLL in lock (N=2 in this case)                                                                           |

| 2.3.  | Simplified Model of a Phase Detector 9                                                                   |

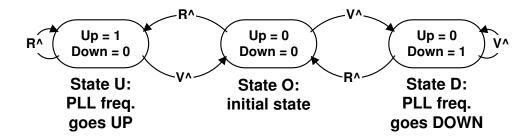

| 2.4.  | State diagram of a Phase Frequency Detector                                                              |

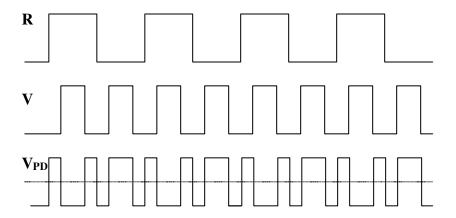

| 2.5.  | (a) XOR PD, the average over cycles is zero 13                                                           |

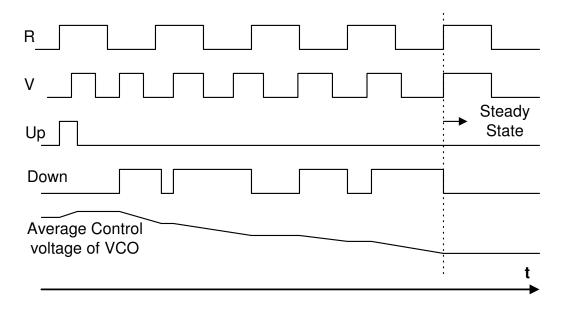

| 2.5.  | (b) PFD PD, a pull-in process is shown and steady state is achieved with both phase and frequency locked |

| 2.6.  | Hogge's self-correcting phase detector                                                                   |

| 2.7.  | Hogge's PD for the clock recovery circuit in lock                                                        |

| 2.8.  | Waveforms when the clock (V) lags the center of the data (R)                                             |

| 2.9.  | A sequential PD used for clock recovery without pattern noise                                            |

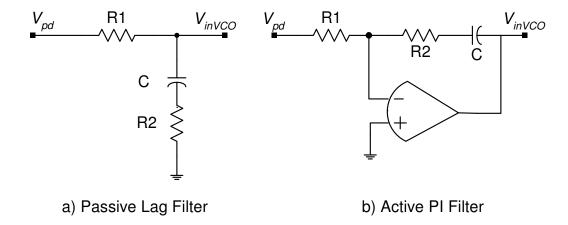

| 2.10. | Typical first-order loop filters with a zero                                                             |

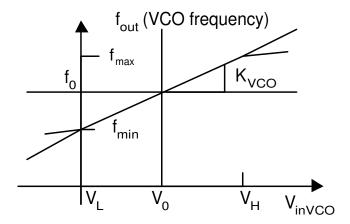

| 2.11. | VCO characteristics: frequency versus control voltage                                                    |

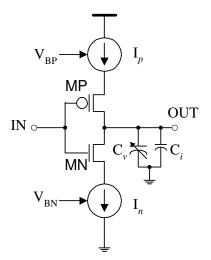

| 2.12. | Single stage of a simplified current-starved VCO                                                         |

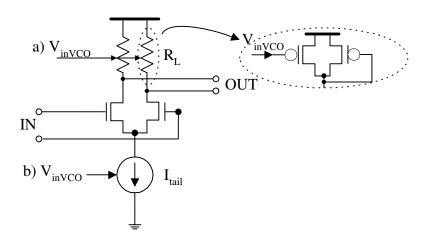

| 2.13. | Fully differential delay buffer [15]                                                                     |

| 2.14. | Linear model of second-order PLL system                                                                  |

| 2.15. | Magnitude plots of the PLL Phase Transfer Function (left) and Error Transfer Function (right)            |

| 2.16. | Block diagram of a DLL                                                                                   |

| 2.17. | Block diagram of the voltage-controlled delay line (VCDL)                                                                                  | 29 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

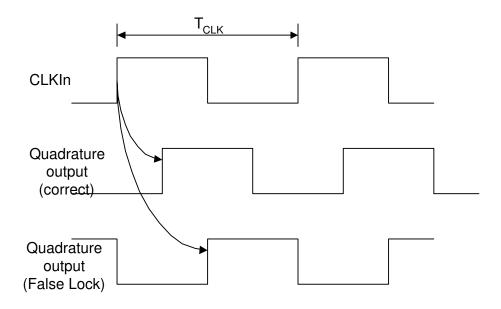

| 2.18. | False lock of a DLL (input clock and quadrature output are shown)                                                                          | 30 |

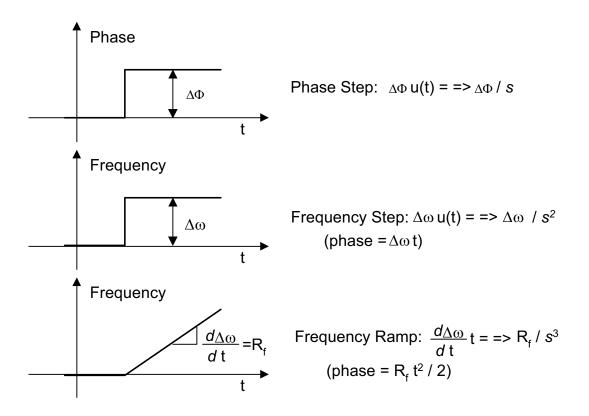

| 3.1.  | Three types of input variations: phase step, frequency step and frequency ramp with their time domain and frequency domain representations | 33 |

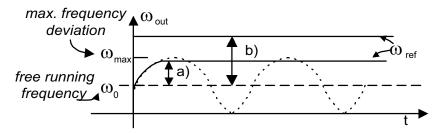

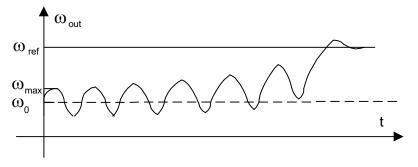

| 3.2.  | Processes of acquisition with the different frequency offset ( $\Delta\omega$ )                                                            | 37 |

| 3.3.  | Pull-in process                                                                                                                            | 38 |

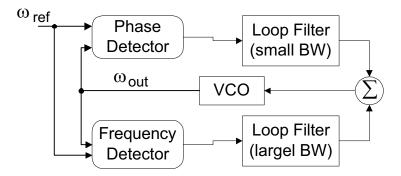

| 3.4.  | Two-loop architecture for the aided acquisition                                                                                            | 40 |

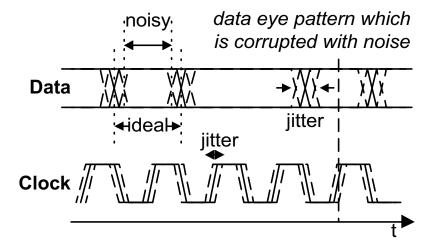

| 3.5.  | Timing jitter related to data and clock                                                                                                    | 42 |

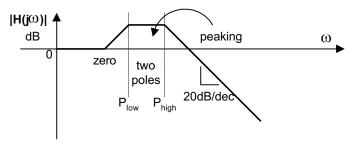

| 3.6.  | Jitter peaking for a typical second-order PLL                                                                                              | 45 |

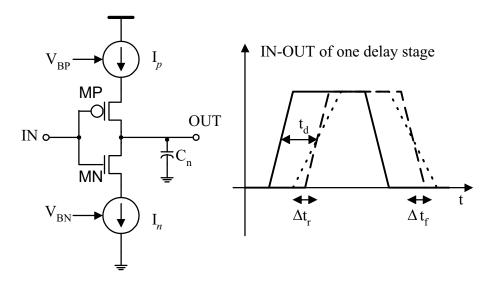

| 3.7.  | Timing error of one delay stage                                                                                                            | 48 |

| 4.1.  | A tri-state loop filter                                                                                                                    | 54 |

| 4.2.  | A charge-pump loop filter with the PFD                                                                                                     | 55 |

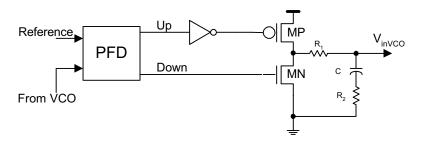

| 4.3.  | A typical charge-pump DLL                                                                                                                  | 57 |

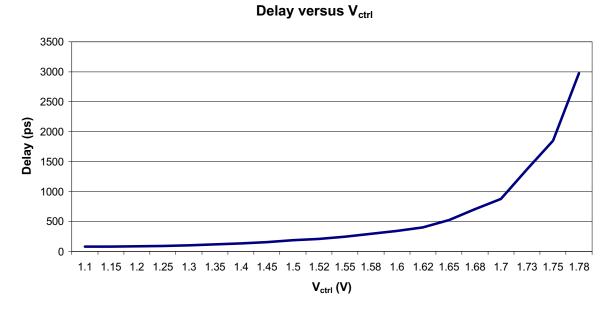

| 4.4.  | Delay versus control voltage of the VCDL                                                                                                   | 59 |

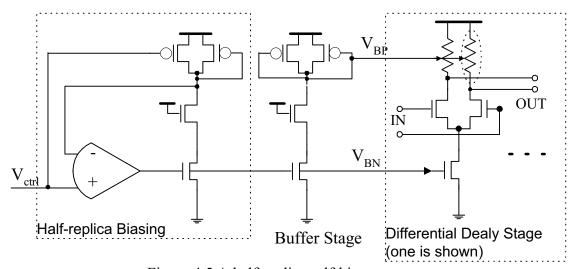

| 4.5.  | A half-replica self-bias generator                                                                                                         | 60 |

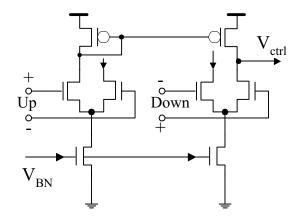

| 4.6.  | A differential charge-pump circuit                                                                                                         | 61 |

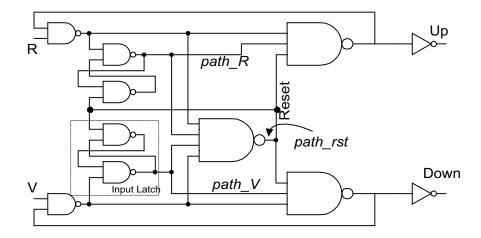

| 4.7.  | A CMOS Phase Frequency Detector                                                                                                            | 61 |

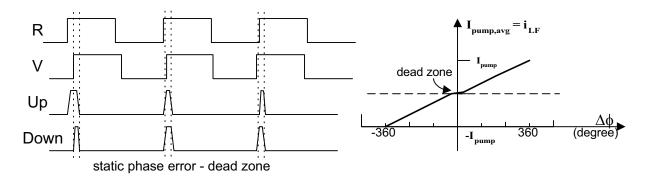

| 4.8.  | Dead zone in the charge-pump circuit                                                                                                       | 62 |

| 4.9.  | A charge-pump circuit using a pair of switches to eliminate the dead zone (Only the lower part is shown)                                   | 63 |

| 4.10. | Charge sharing and a possible solution                                                                                                     | 64 |

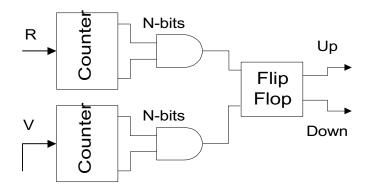

| 4.11. | A counter-based all-digital phase detector                                                                                                 | 65 |

| 4.12. | The "bang-bang" typed all-digital loops                                                                                                    | 67 |

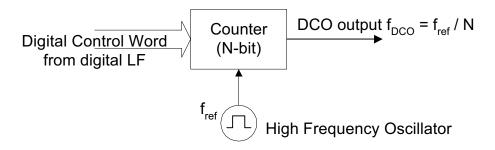

| 4.13. | A counter-based DCO                                                                                                                        | 68 |

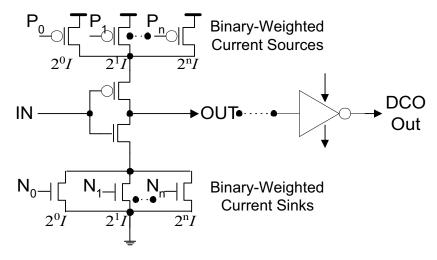

| 4.14. | A binary-weighted DCO                                                | 69 |

|-------|----------------------------------------------------------------------|----|

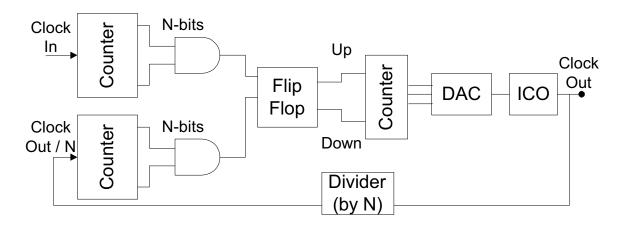

| 4.15. | A counter-based frequency-locked loop (FLL)                          | 69 |

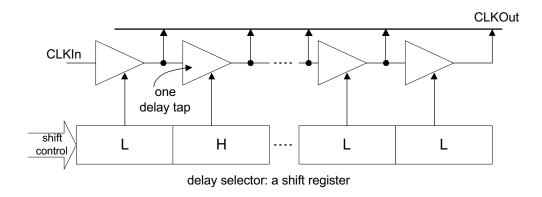

| 4.16. | The block diagram of a DCDL                                          | 70 |

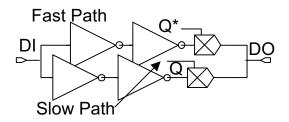

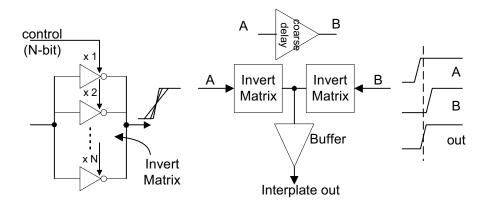

| 4.17. | One delay tap for the interpolation using fast and slow paths        | 73 |

| 4.18. | The register-controlled capacitors for the delay interpolation       | 74 |

| 4.19. | Delay interpolation by adjusting the driving                         | 74 |

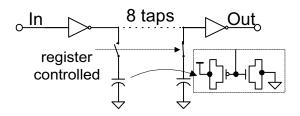

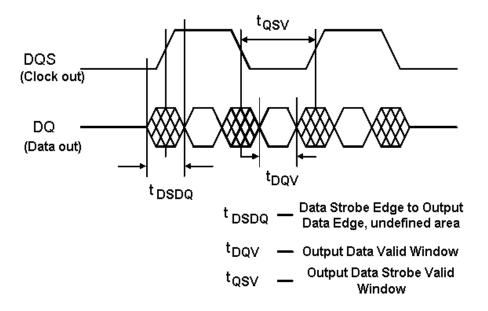

| 5.1.  | Data timing diagram for DDR DRAM                                     | 76 |

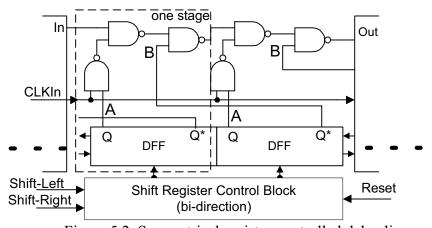

| 5.2.  | Symmetrical register-controlled delay line                           | 78 |

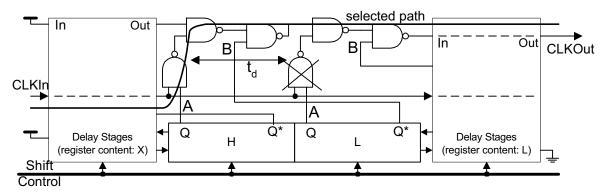

| 5.3.  | Delay Line and Shift Register                                        | 79 |

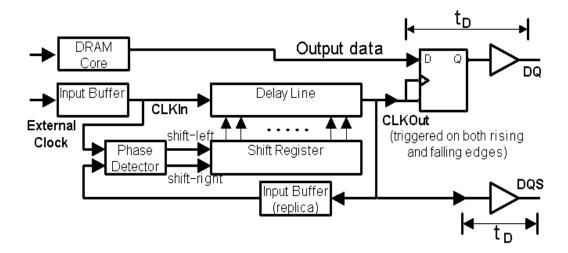

| 5.4.  | Block diagram of the RSDLL                                           | 81 |

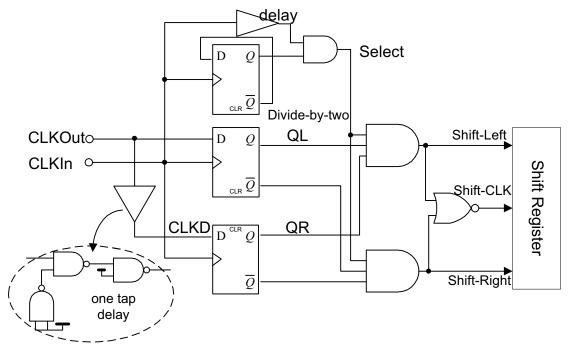

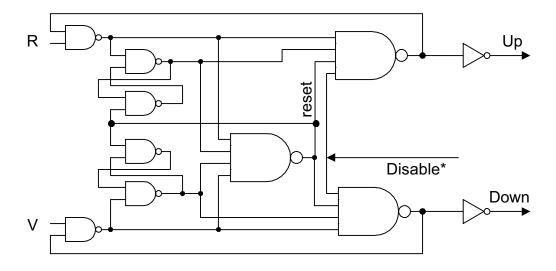

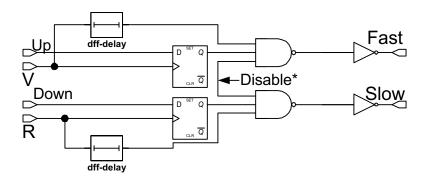

| 5.5.  | All-digital phase detector for the RSDLL                             | 84 |

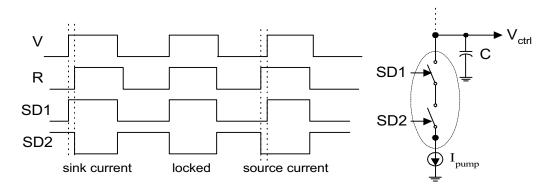

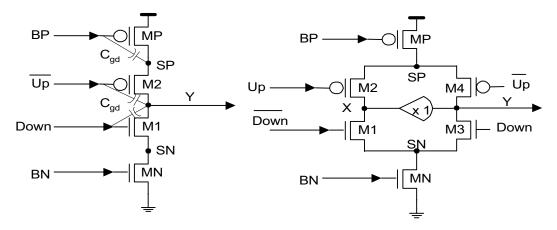

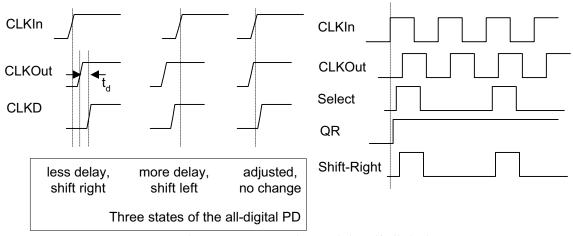

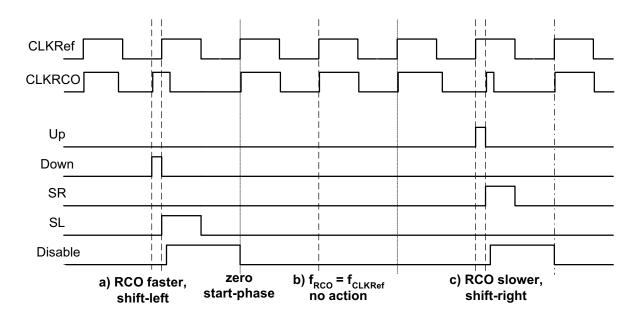

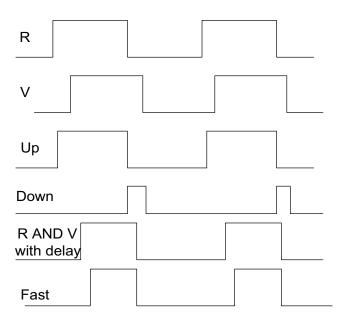

| 5.6.  | Operations of the all-digital PD                                     | 84 |

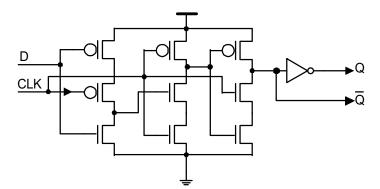

| 5.7.  | A dynamic D flip-flop with single-phase clock                        | 85 |

| 5.8.  | Measured RMS jitter versus input frequency                           | 86 |

| 5.9.  | Measured delay per stage versus VCC and temperature                  | 87 |

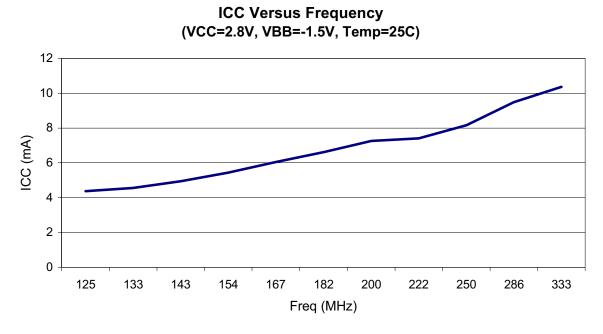

| 5.10. | Measured ICC (power supply current) versus input frequency           | 88 |

| 5.11. | Block diagram of the RDLL with in-phase and quadrature phase shifter | 89 |

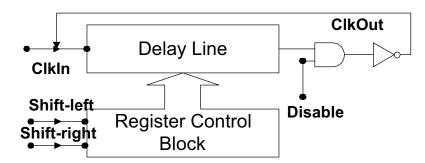

| 5.12. | Block diagram of a register-controlled oscillator (RCO)              | 90 |

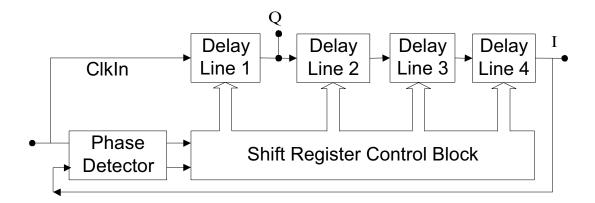

| 6.1.  | Single-loop register-controlled oscillator (RCO)                     | 94 |

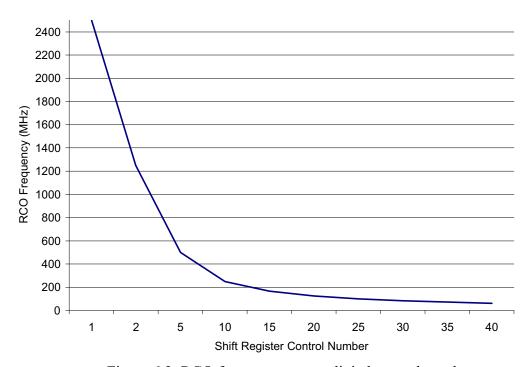

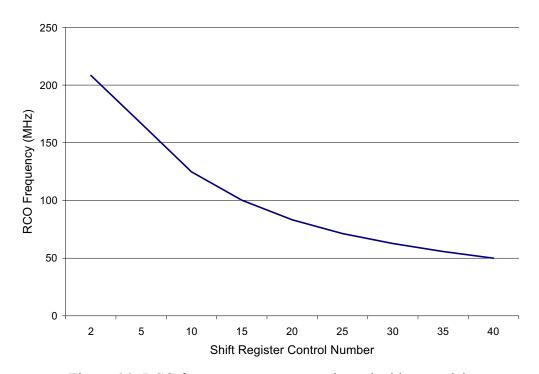

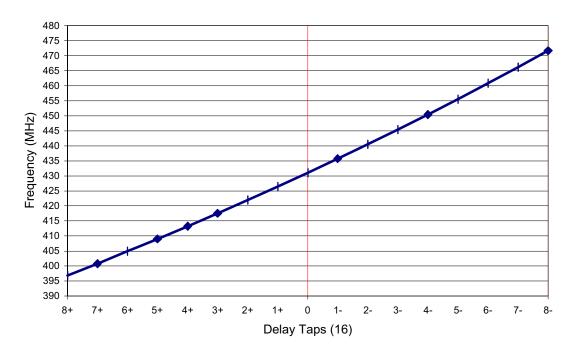

| 6.2.  | RCO frequency versus digital control number                          | 95 |

| 6.3.  | RCO frequency versus control word with extra delay                   | 96 |

| 6.4.  | Two-loop register-controlled oscillator                              | 97 |

| 6.5.  | DFF. FB inverter and one bit of the bi-direction shift register 1    | 00 |

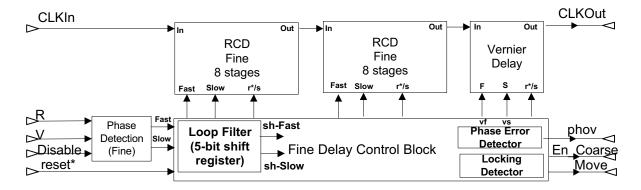

| 6.6.  | Block diagram of the two-loop RCO-based ADPLL                              |

|-------|----------------------------------------------------------------------------|

| 6.7.  | Block diagram of the Hierarchy Pull-in Process                             |

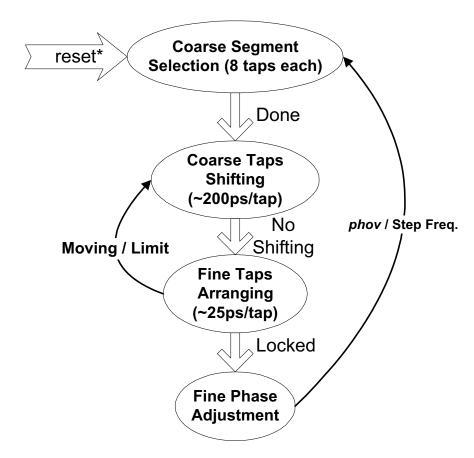

| 6.8.  | Searching algorithm used in the two-loop ADPLL                             |

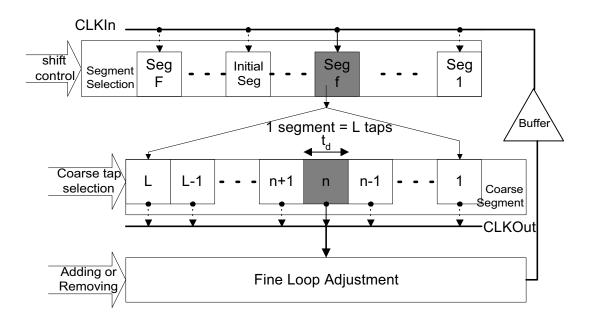

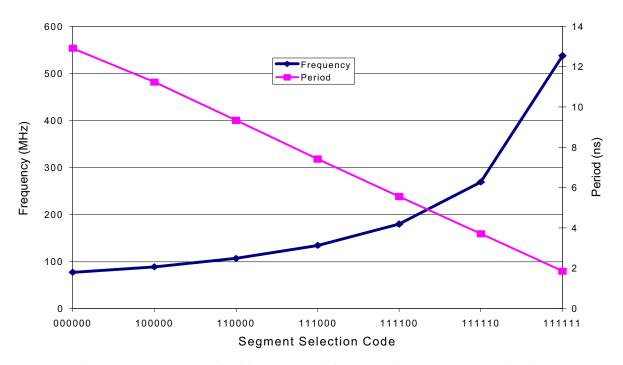

| 6.9.  | Frequency locking range of the coarse loop (segment selection) 105         |

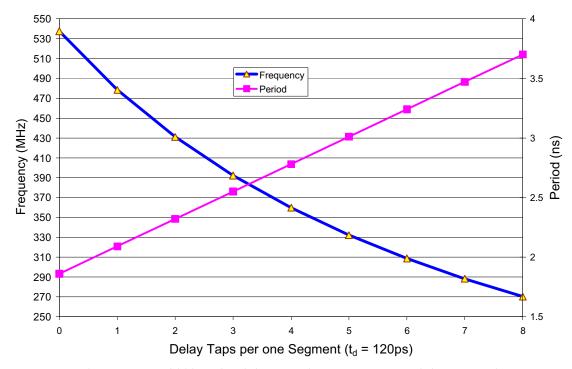

| 6.10. | Shifting the delay taps in one segment of the coarse loop                  |

| 6.11. | Enhance the ADPLL resolution – the fine loop adjustment                    |

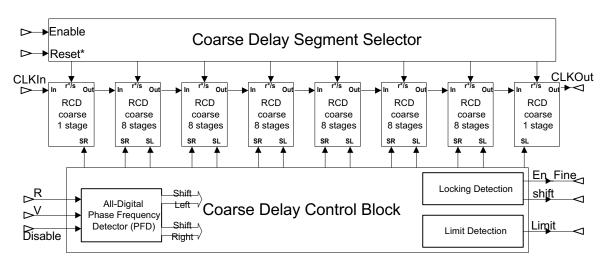

| 6.12. | Two-loop ADPLL: the coarse loop                                            |

| 6.13. | Block Diagram of the control logic of the coarse loop                      |

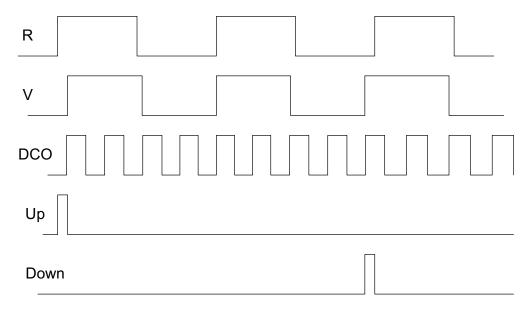

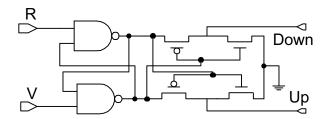

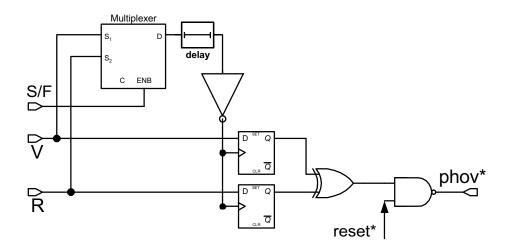

| 6.14. | An all-digital phase frequency detector (ADPFD)                            |

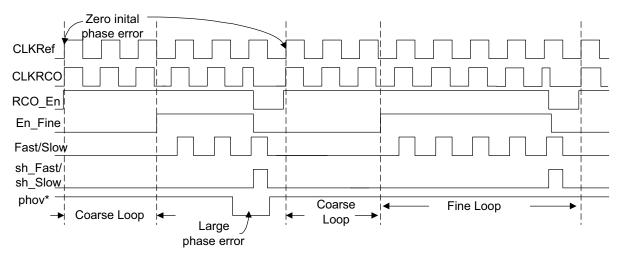

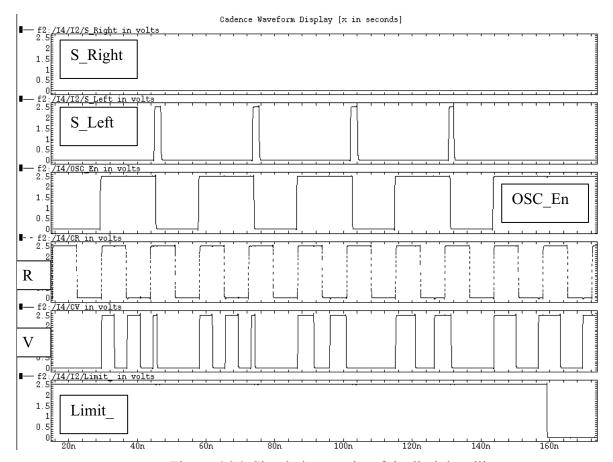

| 6.15. | The operations for the ADPFD and the coarse loop of the ADPLL              |

| 6.16. | A modified phase frequency detector                                        |

| 6.17. | Circuit diagram of the pulse generator                                     |

| 6.18. | Two-loop architecture: the fine loop                                       |

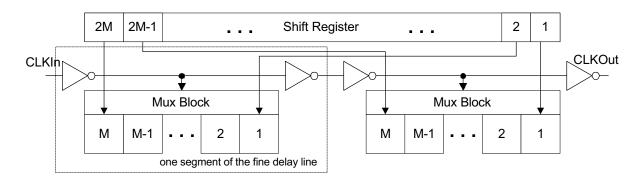

| 6.19. | Interleaved fine delay line with control blocks                            |

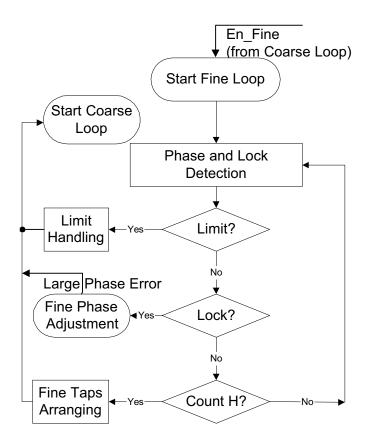

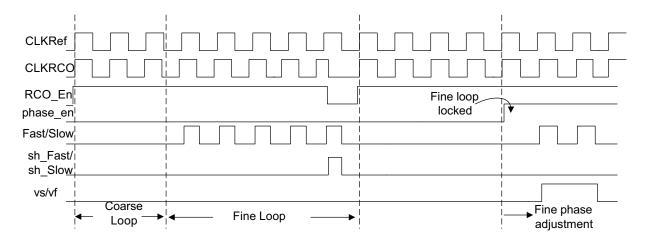

| 6.20. | Block diagram of the fine loop operations                                  |

| 6.21. | The two-way arbiter as part of the fine PD                                 |

| 6.22. | Operations of the fine PD                                                  |

| 6.23. | A variable phase error detector                                            |

| 6.24. | Locking characteristics of the fine loop                                   |

| 6.25. | Locking Mechanism: the fine phase adjustment                               |

| 6.26. | Simulation results of the limit handling                                   |

| 6.27. | Simulation results for the limit handling back to the normal operation 125 |

| 6.28. | Coarse delay per tap ( $2t_d$ in ps) under different conditions            |

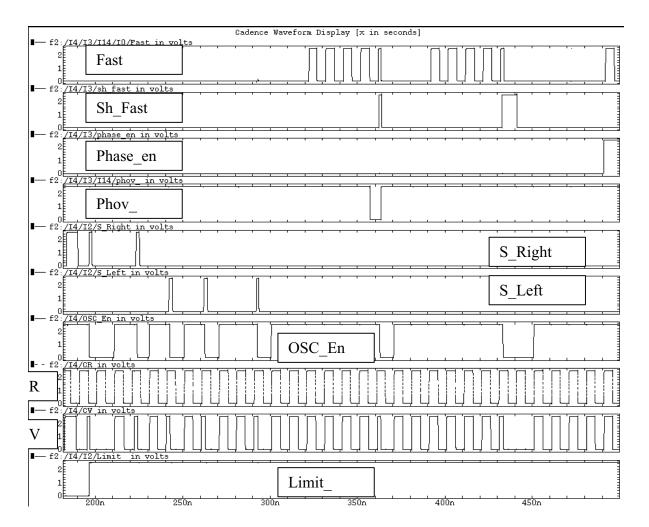

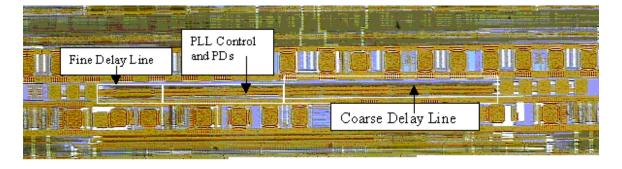

| 6.29. | ADPLL chip layout                                                                                             | 128 |

|-------|---------------------------------------------------------------------------------------------------------------|-----|

| 6.30. | Microphotograph of the RCO-base ADPLL                                                                         | 128 |

| 6.31. | Measured clock jitter (@200MHz, VCC=2.5V, room temperature)                                                   | 129 |

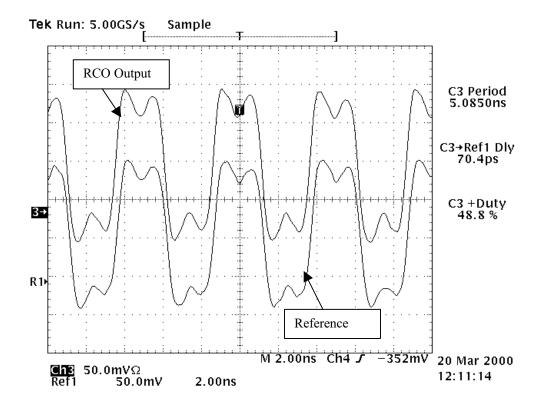

| 6.32. | Measured results when external clock is at 200MHz and VCC=2.5V                                                | 130 |

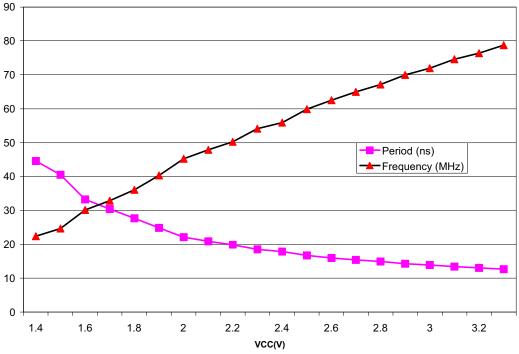

| 6.33. | Measured output clock period and frequency (lower end) when VCC is swept from 1.4V to 3.3V (room temperature) | 131 |

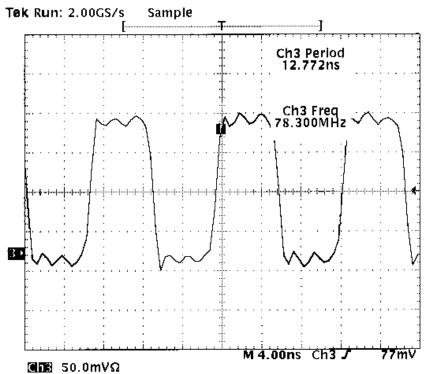

| 6.34. | Measured output clock (lower end) when VCC=3.3, 25C                                                           | 132 |

| 6.35. | Measured output clock (lower end) when VCC=1.4V, 25C                                                          | 132 |

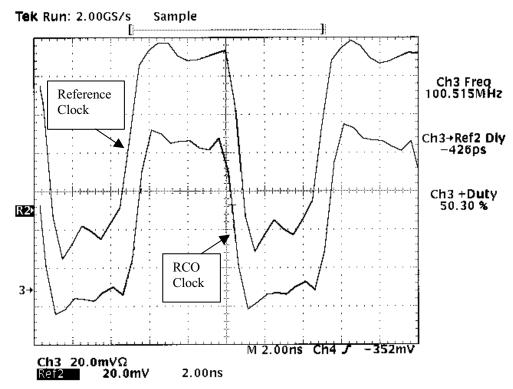

| 6.36. | Generated RCO clock versus internal reference clock @100MHz, VCC=2.5V, room temperature                       | 133 |

### Chapter 1

### **INTRODUCTION**

A Phase-Locked Loop (PLL) is a feedback system that causes an output signal to track a reference signal in phase and frequency. When both the frequency and phase of these signals are synchronized, the PLL is said to be in the locked condition. The phase difference between the output and reference is a known value when the loop is locked. Hence the name, "phase-locked loop". PLLs are found in a wide range of applications, including clock recovery, noise and jitter suppression in communications, clock synchronization in memory interface and high-performance microprocessors, and frequency synthesis for instrumentation and RF transceivers.

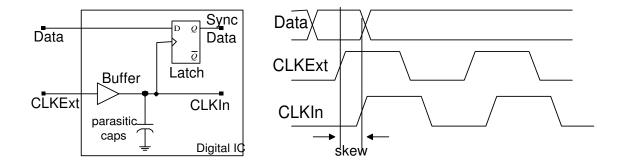

Another closely related circuit is the delay-locked loop (DLL), which is primarily used for clock synchronization and de-skewing. In high-speed synchronous systems clock skew can be a critical problem caused by clock buffers and propagation delay when the system clock enters a chip from a printed-circuit board (PCB), in Figure 1.1. The buffer is used to sharpen the clock edges and increase the drive capability needed because of the parasitics associated with the interconnect. In order to correctly latch the data and avoid setup / hold time violations of data latches, a PLL or DLL is needed to provide dynamic synchronization of the external (*CLKExt*) and internal (*CLKIn*) clocks, reduce the skew, and improve the system timing for on-chip and inter-chip operations.

Figure 1.1. Clock skew in an integrated circuit

The theory of phase-lock techniques has been investigated thoroughly by Gardner in [1]. Best, in [2], classified the PLL into four different categories based on different implementations: the linear PLL, classical digital PLL, all digital PLL and software PLL. With tabulated equations and handy software to demonstrate loop responses on different design parameters, this book is found useful for discrete implementations. A tutorial to integrated circuit (IC) related implementation [3] illustrated recent efforts to build phase-locked loops and clock recovery circuits monolithically. Current trends in PLL design techniques are trying to solve the following problems using state-of-the-art IC techniques:

- 1. Achieving robust operation.

- 2. Achieving wide locking range.

- 3. How to get better jitter performance?

Since the basic PLL system is at least a second-order system, its output is susceptible to power supply, process and temperature variations. Traditional phase-locked and delay-locked loops are implemented using analog and digital techniques with some off-chip components to achieve robust operation or tuning. Advances in very large scale integration (VLSI) technology have provided the capacity to implement PLLs and DLLs monolithically

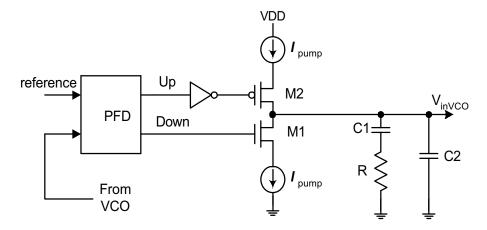

with high performance and low cost. Charge-pump PLLs [4] [5], appeared in the early 80s and used a phase-frequency detector to provide attractive tracking and locking performance. Since the tracking range is only limited by the voltage-controlled oscillator (VCO) and the static phase error is zero if mismatches and offsets are negligible, the charge-pump circuit is widely used in many implementations, [6] – [13], of phase-locked and delay-locked loops. Various methods have been proposed to improve the efficiency of charge-pump circuit. Since a higher-order system is inherent in charge-pump PLLs [4] [5], a robust charge-pump PLL design can be a challenge. One implementation proposed a self-bias technique to track the variations caused by process and temperature [15] at the cost of power supply sensitivity. A charge-pump PLL using a current-controlled oscillator is reported in [16], [32]. References [17] [18] analyzed low jitter implementations using charge-pump circuits. Charge-pump phase-locked and delay-locked loops may be considered as analog implementations.

On the other hand, all-digital implementations offer enhanced functionality and flexibility, greater simplicity, and good stability. Here, all digital means the entire system is built with digital components. All digital implementation is primary used in a DLL to provide accurate timing [21]-[27]. A counter-based all digital phase-locked loop (ADPLL) is analyzed in [2]. A digital-controlled oscillator (DCO) uses high frequency source to provide a reference. The operating range is limited by the high frequency reference. Another DCO-based ADPLL is reported in [19] [20]. As the feature size of modern VLSI technologies continue to shrink, fully integrated all-digital approaches will be more scalable and portable

in different processes and applications than its analog1 counterpart. Advantages and disadvantages of both approaches are listed in Table 1.1.

|                                                                  | ALL-DIGITAL PLL | ANALOG PLL      |

|------------------------------------------------------------------|-----------------|-----------------|

| Stability (relative)                                             | Good            | Poor            |

| Scalability                                                      | Good            | Poor            |

| System Order                                                     | ≤ 1             | ≥2              |

| Simplicity                                                       | Good            | Poor            |

| Drift in Power Management                                        | No Drift        | Drift           |

| Tuning                                                           | Discrete        | Continuous      |

| Lock Range                                                       | Limited         | Wide            |

| Immune to Variations in Process,<br>Temperature and Power Supply | Good            | Poor            |

| Area without passive elements                                    | Large           | Small           |

| Noise & Jitter                                                   | Predictive      | Design Oriented |

Table 1.1. Comparisons between two different implementations of PLLs

For a phase-locked loop, wide lock range and low jitter may not be achievable at the same time because, conventionally, the PLL is made narrow bandwidth to suppress the noise. In order to achieve wide lock range, aided frequency acquisition can be used to form a twoloop architecture, with the frequency tracking first, then phase locking [12], [19]. Aided acquisition can substantially increase the lock range. Another way to improve jitter performance is interpolation. The resolution of basic delay element used in the VCO or voltage-controlled delay line can be improved using interpolation [13], [17], [18], [24], [28], [31]. Jitter performance can also be improved by carefully examining the jitter associated with the phase-locked and delay-locked loops [14], [37]-[43].

Application oriented implementation results in different solutions. Besides widely used in the system timing, clock synchronization and clock generating, phase-locked or

the analog PLL mainly refers to Charge-Pump phase-locked loops (CPPLL).

delay-locked loops also have applications in disk drives, and clock / data recovery circuits [32]-[36]. Although complementary MOS (CMOS) implementations are relatively low cost and widely used in current integrated circuit design, in order to achieve high speed, BiCMOS, Bipolar and GaAs may be used to operate PLL in the GHz range [44]-[50].

The objective of the research presented in this dissertation is to develop low jitter, wide lock range phase-locked and delay-locked loops using all digital techniques. Both all digital PLLs and DLLs used in clock synchronization applications are examined in detail. The all digital PLL (ADPLL) implemented in this work can be used in frequency synthesis and clock recovery applications. In this research, an emphasis has also been placed on CMOS implementations.

Chapter 2 first reviews the basic operation involved in phase-locked and delay-locked loops and presents an overview of various building blocks and a linear approximation of second-order system analysis. Some design criteria of PLL and DLLs are explored in Chapter 3, including jitter analysis associated with oscillators. Some tradeoffs in gain, bandwidth, loop dynamics, lock range and lock time are also discussed in detail. Existing approaches, including conventional charge-pump PLL (analog PLL) and counter-based or DCO-based all digital implementations are examined in Chapter 4. Pros and Cons are summarized which lead to the proposed register-based solution presented in this dissertation.

Chapter 5 describes the architecture, circuit design, and implementation of a register-controlled symmetrical DLL (RSDLL) that is suitable for double-data rate (DDR) dynamic random access memory (DRAM). The measurement results verify robust operations and less sensitivity to variations in process, temperature and power supply with this all digital implementation. The simple register-controlled mechanism used in the RSDLL is further

explored in a proposed register-controlled oscillator (RCO), which is the main component used in the ADPLL. The RCO-based ADPLL is distinguished from the conventional voltage-controlled or digital-controlled oscillators. The two-loop architecture, specific lock-controlled mechanism and some techniques proposed to improve the resolution of this RCO-based ADPLL are discussed in Chapter 6 and applied to the design of ADPLL for deskewing and frequency synthesis applications. Some experimental results extracted from a test design provide the proof in silicon of the operation of the RCO-based ADPLL.

Chapter 7 summarizes the principal conclusions and contributions of this research.

Suggestions for further investigation are also offered in this chapter.

### **Chapter 2**

### **Phase-Locked Loop Basics**

### 2.1. Basic operation of a Phase-Locked Loop (PLL)

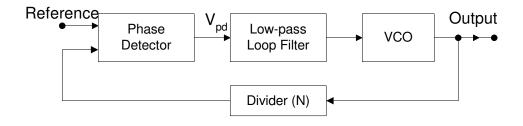

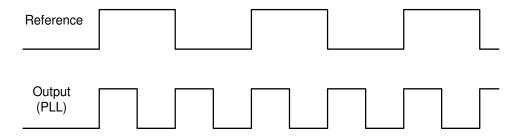

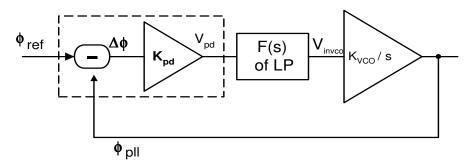

A basic PLL is a negative feedback system that consists of a phase detector, a low-pass loop filter and a voltage-controlled oscillator (VCO), as shown in Figure 2.1. A divide-by-N counter can be added in the feedback path to provide a frequency synthesis function. Figure 2.2 shows the waveforms of a reference signal and PLL output when the loop is in lock (using a divide-by-2 in the feedback path). The frequency of the PLL output signal is twice the reference with zero-phase difference (assuming N=2).

Figure 2.1. Block diagram of a basic PLL

Figure 2.2. PLL in lock (N=2 in this case)

The basic operations of a PLL can be divided into three steps. First, the phase detector (PD) catches the phase difference between two inputs and generates an error signal  $V_{pd}$  whose average value is linearly proportional to the phase difference. A Loop filter (LF) is then used to suppress the high-frequency components of the PD output, allowing the average value (DC or low-frequency) to control the VCO frequency. Finally, an oscillator generates an output signal whose frequency is a linear function of the control signal out of the LF. The generated signal is fed back to the input of the PD and another phase comparison is started until the phase difference achieves a fixed relationship (most commonly 0° or 90°, depending on the nature of the PD). Some important aspects of the basic PLL need discussion for further investigation:

- Phase is the interesting value in a PLL rather than the voltage and current in general feedback circuits. It can be changed to voltage or current during the different steps of the PLL operation.

- The loop is said to be locked if the phase difference is constant with time. In other words, the frequency is equal between the two compared signals.

- In general, a PLL exhibits non-linear locking behavior.

- A tiny frequency difference can accumulate fast and the phase error can grow significantly after several cycles.

- A finite time is required for the PLL output to respond to input changes.

- The PLL output is a periodic signal, while the reference could be periodic, frequency or phase modulated signals, or data (1s and 0s).

### 2.2. Building Blocks in a PLL

From the basic operation of a PLL, three important building blocks are needed to provide phase locking, namely a phase detector (PD), loop filter (LF) and oscillator. Some main features and various implementation methods for different applications are investigated in this section.

#### 2.2.1. Phase Detector

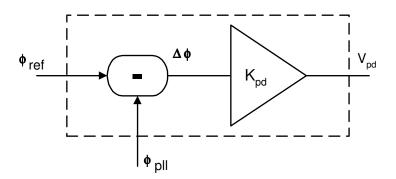

A simplified model of a phase detector (PD) is shown in Figure 2.3. The PD converts the input phase difference  $\Delta \phi$ , which is the subtraction of the reference phase  $(\phi_{ref})$  and PLL output phase  $(\phi_{pll})$ , to an output signal  $V_{pd}$  with a gain factor  $K_{pd}$ .

Figure 2.3. Simplified Model of a Phase Detector

The  $V_{pd}$  is an average value over cycles, which can be obtained using proper loop filters. A transfer characteristic curve can be derived from the relationship of input (phase) and average output (voltage or current). Since only the linear region, which refers to the steady state of a PLL, is a concern in deriving the PLL linear model, an equation can be used to illustrate such relationship with a gain factor  $K_{pd}$ , the slope of the PD linear transfer curve.

$$V_{\rm pd} = K_{\rm pd} \bullet \Delta \phi \tag{2.1}$$

Different types of PDs have their own transfer characteristics and are summarized in Table 2.1. The PD can be classified based on different applications and implementations. In Table 2.1, the two inputs, R and V refer to the reference (either data or clock) and PLL output respectively. The value  $V_{PD}$  stands for average output of the PD, and  $V_H$ ,  $V_L$  are the maximum and minimum average values of  $V_{PD}$  respectively. The average output of the PD can be a current when uses in the PD Class IV with a Charge-Pump circuit to generate proper control signal for the VCO.

In deriving the transfer function of the Class I PD, assume that  $R = A_R \cos(\omega_R t + \Delta \phi)$  and  $V = A_V \cos(\omega_V t)$ , then the output of this PD is the multiplication of R and V

$$V_{\text{pd, out}} = \mathbf{m} \cdot (\frac{\mathbf{A}_{R} \cdot \mathbf{A}_{V}}{2}) \cos[(\boldsymbol{\omega}_{R} + \boldsymbol{\omega}_{V}) \cdot t + \Delta \phi] + \mathbf{m} \cdot (\frac{\mathbf{A}_{R} \cdot \mathbf{A}_{V}}{2}) \cos[(\boldsymbol{\omega}_{R} - \boldsymbol{\omega}_{V}) \cdot t - \Delta \phi]$$

(2.2)

where m is a multiplication factor. When PLL is in lock or in the steady state,  $\omega_R = \omega_V$  and the integration over one period results in

$$V_{pd,average} = A \cdot \cos(\Delta \phi) = A \cdot \sin(\frac{\pi}{2} - \Delta \phi)$$

(2.3)

where A is a gain factor which is equal to  $m(A_RA_V/2)$  and dependent on the input amplitudes. Equation (2.3) shows that the slope of this PD is not constant. When the phase difference is small compared to  $\pi/2$ ,  $\sin(\pi/2-\Delta\phi)$  is approximately equal to  $(\pi/2-\Delta\phi)$  and  $K_{PD} \approx A$ . When large signals are used in the Class I PD, a similar transfer function can be derived as XOR PD, where  $K_{PD}$  is linear and independent of the signal amplitudes.

Table 2.1 Circuit symbols and transfer characteristics of different phase detectors based on applications

Class III and Class IV are edge-triggered phase comparison, which is sensitive to missing edges. For data recovery applications, these types of PDs may not be suitable without extra circuits to prevent false detection. Class IV PD can perform both phase and frequency detection (PFD) [51], which is powerful in many applications. The state diagram of this sequential detector is shown in Figure 2.4. Three possible states, O, D and U are embedded with this PFD, also known as classic 3-state PFD. The symbol 'A' indicates that rising edge of signal R or V is coming. After "Reset", the PFD goes to State O. With the memory of previous state, the PFD can generate proper Up / Down signals even if the frequencies of R and V are different and it will not lock on the harmonics. Another observation is when PFD-typed PLL is in lock, Up and Down are both low and no ripples generated by the loop filter. For XOR-based PLL, because R and V are 90 degree out of phase when in lock, ripples will be generated when the output of the PD passes through the loop filter and modulate the VCO output. Some design considerations of different PDs are summarized in Table 2.2. These features are mainly related to the steady state operation of a PLL, instead of transient or dynamic response.

Figure 2.4. State diagram of a Phase Frequency Detector

|                       | MULTIPLIER | XOR | RS-LATCH | PFD |

|-----------------------|------------|-----|----------|-----|

| Linear Range          | Small      | π   | 2π       | 4π  |

| Edge Sensitive        | No         | No  | Yes      | Yes |

| Duty Cycle Sensitive  | Yes        | Yes | No       | No  |

| Lock to Harmonics     | Yes        | Yes | Yes      | No  |

| Sequential (w/memory) | No         | No  | No       | Yes |

| Phase Detection       | Yes        | Yes | Yes      | Yes |

| Frequency Detection   | No         | No  | No       | Yes |

| Pattern Sensitive     | Yes        | Yes | No       | No  |

| Ripple out of LF      | Yes        | Yes | No       | No  |

| Locking Phase         | π/2        | π/2 | 0        | 0   |

Table 2.2 Summary of lock characteristics of different phase detectors

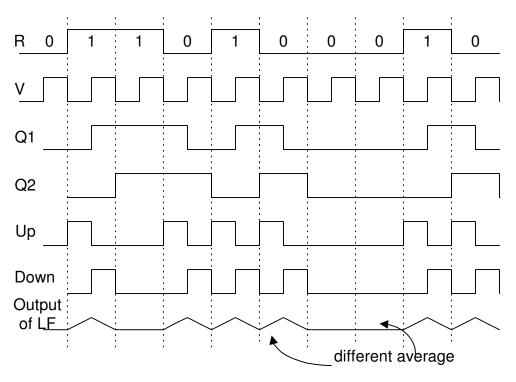

To illustrate some of the lock characteristics, assume the frequency of  $V(f_V)$  equal to 2 times the frequency of  $R(f_R)$ , and R is leading of V. The responses of different PDs are drawn in the Figure 2.5. From part (a), an XOR is used as the PD. For each cycle, the average value of PD output is equal to  $(V_H-V_L)/2$ , depending on what kind of power supply is used. In this case, the XOR-PD will declare locking! As a result, the XOR-PD typed PLL has some limitation on the oscillator, whose operating frequency has to be limited between  $0.5 f_R$  and  $2 f_R$ .

Figure 2.5 (a) XOR PD, the average over cycles is zero

In part (b), a PFD is used under the same situation. Although initially an Up is generated, over cycles, the Down is asserted more often than Up, and the average value used to control the VCO is decreased and the frequency of the VCO is decreased too to pull in the two different signals. When steady state is achieved, both Up and Down are logic LOW. Not only the phase, but also the frequency is locked when using the PFD. A charge-pump circuit is needed to convert Up/Down to a proper control voltage and will be discussed in Chapter 4. With finite delay associated with the reset path of the PFD (an AND gate and CLR-to-Q delay, referring to Table 2.1), a narrow pulse may be generated when changing the states (which is not shown in Figure 2.5 b). A static phase error may exist when a PFD is used.

Figure 2.5 (b) PFD PD, a pull-in process is shown and steady state is achieved with both phase and frequency locked.

Another issue is false edges and long strings of 1s or 0s, common for NRZ (not returning-to-zero) data, which are transmitted in data communications to bear the binary information. Another data pattern is "return-to-zero", in which the signal goes to zero

between consecutive data bits. Since the PFD is sensitive to the edges, it may not suitable for data / clock recovery.

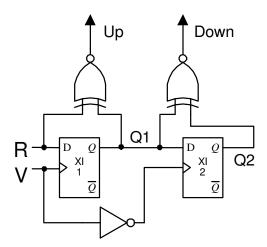

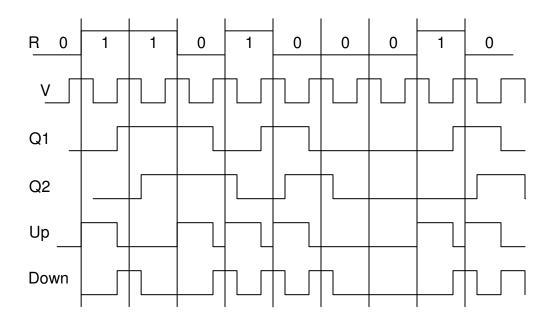

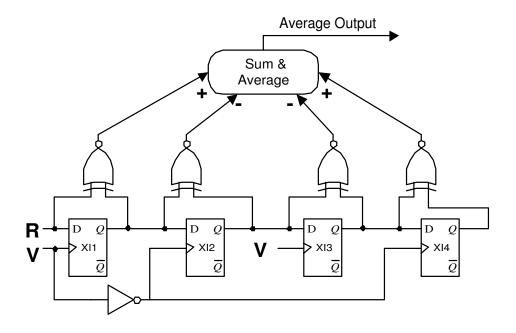

A sequential phase detector, Hogge's PD [52], shown in Figure 2.6, can be used as self-correcting clock recovery circuit. "Self-correcting" means that the clock signal can align to the center of the data bit independent of the data rate, temperature, or process variations. A "no-action" state is implemented in the event of missing data edges. A re-timed data (Q1) is fed into the flip-flop XI2, which is clocked by the complement of the generated clock V. Assume clock V has a 50% duty cycle and frequency is twice the data rate. The outputs of XI1 and XI2, Q1 and Q2, are half clock cycle delay from data input and Q1 respectively. The average value of the difference between XOR outputs, Up and Down over cycles will determine the trend in oscillator frequency, increasing, decreasing or staying the same.

Figure 2.6. Hogge's self-correcting phase detector

The timing diagrams for a Hogge's detector are shown in Figure 2.7. When in lock, the average of Up/Down over several cycles is zero. When the clock (V) lags the incoming data (R), shown in Figure 2.8, Up is high more often than Down and the average voltage out of the loop filter will increase, as well as the frequency of the oscillator. Unlike the 3-state

PFD, where *Up/Down* are both low when in lock, the Hogge's PD will still generate equal duration *Up* and *Down* signals, which results in ripple after integration via the LF. Another problem is sensitive to the input data density. The charge deposited on the LF is not equal dependent on the different data density, more average charge when 1s and 0s are alternative than a long string of 1s or 0s (Figure 2.7). This will cause a pattern jitter and modulate the VCO output.

Figure 2.7. Hogge's PD for the clock recovery circuit in lock

A possible solution to the pattern jitter is to center the ripple, shown in Figure 2.9 [34]. The effect is that no net charge will be deposited into the loop filter when the loop is in lock regardless what the data density is. In order to suppress the ripple, a high order pole (HOP) is needed in the LF to effectively get rid of the high-frequency components. This pole should be placed far away from the low frequency poles and have little effect on the low-frequency transfer functions [4].

Figure 2.8. Waveforms when the clock (V) lags the center of the data (R)

Figure 2.9. A sequential PD used for clock recovery without pattern noise

#### 2.2.2. Loop Filter

After investigating different phase detectors, the averaging or integrating part, a loop filter, need to be addressed. A Loop Filter (LF) is normally a low pass filter, which performs the integration of the PD output over cycles. From the previous section, the pulse width and duty cycle of the PD outputs contain the phase difference information. A LF can convert these digital signals into a continuous average value to control the VCO frequency. In the earlier implementations, the passive elements of a LF were put off-chip to save silicon space. Effort has been made to implement the LF on chip, especially for high-speed applications. The LF is the brain of the PLL, and different topologies of LFs and its parameters can greatly affect the loop dynamics (which will be discussed in Chapter 3).

Generally, first order low-pass loop filters are used in most PLL design, and one pole is included in the transfer function F(s) of the LF. A simple RC network can do this job with a transfer function of

$$F(s) = \frac{1}{1 + s \cdot RC} \tag{2.4}$$

In order to stabilize the operation, a zero is added in series with the capacitor (more on this in Section 2.3). Figure 2.10 shows two other typical loop filters: the passive lag filter (a) and the active PI (proportional + integral) filter (b) which include an op-amp. The transfer functions, F(s), are given by

$$F(s) = \frac{1 + s \cdot \tau_2}{1 + s \cdot (\tau_1 + \tau_2)} \qquad \dots \text{ a passive lag filter}$$

(2.5a)

$$F(s) = \frac{1 + s \cdot \tau_2}{s \cdot \tau_1} \qquad \dots \text{ an active PI filter} \qquad (2.5b)$$

where  $\tau_l = R_1C$ ,  $\tau_2 = R_2C$ . For the active PI filter, slow changes cause the LF to do normal integration. For fast changes, the *s* factor will be cancelled in Equation (2.5b), and the output of the LF is proportional to the input with a gain factor equal to  $R_2/R_1$ . Another approach uses a charge-pump type loop filter which will be discussed in Chapter 4. Compared to the basic RC low pass filter, these types of LFs with stabilized zero suffer the degradation of high-frequency suppression,  $R_2/(R_1+R_2)$  for passive lag LF or  $R_2/R_1$  for active PI filter. In general,  $R_1$  should be chosen at least 10 times larger than  $R_2$  for better high frequency performance. A common solution is to add a small capacitor in parallel with serial C and  $R_2$  to provide better suppression of high-frequency components. The drawback of this is making a higher order loop filter and all loop parameters need to be adjusted to prevent stability problems. When select the loop parameters, another consideration is the parasitics presented in the PLL, such as the output resistance of the PD, input resistance and capacitance of the VCO. The output resistance of the PD should be small compared to the  $R_1$ . The input resistance of VCO should be infinite and input capacitance is small compared to the LF.

Figure 2.10. Typical first-order loop filters with a zero

Though the LF can be integrated with the PD, with the purpose to generate proper control signal for the oscillator, the important feature of LF and potential effects for the overall loop characteristics will be pointed out in the following sections.

#### 2.2.3. Voltage-controlled oscillator

The last important building block of a basic PLL is the oscillator, which generates the required clock signal with a controlled frequency. If the signal out of the LF is a voltage, it is called voltage-controlled oscillator (VCO); a current-controlled oscillator (ICO) uses a current input to change its output frequency. If the frequency is a linear function of a control voltage  $V_{invco}$ , the VCO frequency ( $f_{out}$ ) can be given by

$$f_{out} = f_0 + K_{vco} V_{invco} \tag{2.6}$$

where the  $f_0$  is the free running frequency of the VCO, and  $K_{vco}$  is the gain factor. Figure 2.11 illustrates this relationship.

Figure 2.11. VCO characteristics: frequency versus control voltage

In Figure 2.11,  $f_{max}$  and  $f_{min}$  are the maximum and minimum frequencies that the VCO can achieve respectively.  $K_{VCO}$  is equal to the slope of the linear region. When the control voltage,  $V_{inVCO}$  is out of range, either greater than  $V_H$  or less than  $V_L$ , the curve is flatten out and the gain drops to zero. It results in slow loop response and possibly, large phase errors. The tuning range of the VCO, gain, and free running frequency ( $f_0$ ) are important design issues based on different applications and architectures of PLLs. Since we are interested in the output phase rather than frequency in a PLL system, and phase is the integration of the frequency in time domain, the transfer function of VCO is given by

$$\frac{\phi_{PLL}}{V_{inVCO}} = \frac{K_{VCO}}{s} \tag{2.7}$$

Unlike the PD, the VCO converts input control voltage ( $V_{inVCO}$ ) back to phase ( $\phi_{PLL}$ ). This will introduce another pole in the system transfer function, and make the basic PLL a second order system.

For the monolithic implementation, a basic LC tank used in the conventional oscillator is not suitable for wide operating range. A common topology using CMOS technology is the ring oscillator, which uses an odd number of inversions to make oscillations. Adjusting the delay of each ring cell according to the control signal can tune the frequency of this ring oscillator when used in a PLL. If the delay of each delay stage is  $t_d$  and N delay stages are used, the oscillating frequency ( $f_{osc}$ ) is equal to

$$f_{osc} = \frac{1}{2 \cdot N \cdot t_d} \tag{2.8}$$

where the factor of 2 in the denominator is due to both rising and falling edges of each delay stage contributing to the  $f_{osc}$ . From equation (2.8), two ways can be used to adjust the frequency:

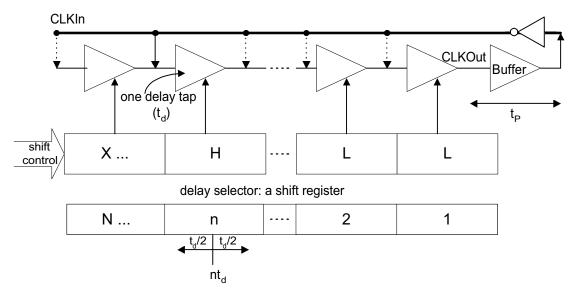

- *Method 1*: the effective number of delay stages -N

- *Method 2*: the delay per stage  $t_d$

For the first tuning method, one important thing is to keep the odd number of stages for a single-ended delay stage. If a basic inverter is used as a delay stage, two inverters need to be removed or added each time when using this approach. In order to achieve wide lock range, a large number of stages are required. This approach is suitable for an all-digital implementation since changing the number of delay stages can easily be accomplished by using a shift register, where the shifting control signals are generated by all-digital phase detector (more on this in Chapter 6). Because of discrete tuning by adding or removing delay stages, delay interpolation is needed to improve the resolution and achieve tight locking.

Another way to tune the oscillator frequency is by adjusting the delay per stage. This method is widely used in the different types of VCOs. A simplified current-starved VCO delay stage is shown in Figure 2.12.

- $V_{BP}$  and  $V_{BN}$  are bias voltages that control the current source and sink. The bias can be generated by  $V_{invco}$ .

- ullet C<sub>i</sub> is the intrinsic capacitance associated with the inverter MOSFET MP and MN (current stage and next stage).

- C<sub>v</sub> can be a voltage-controlled capacitor.

- The delay of this stage can be evaluated by the time used to charge or discharge load capacitance  $(C_v + C_i)$  by  $I_p$  or  $I_n$ .

Figure 2.12. Single stage of a simplified current-starved VCO

Varying the current  $I_p$  and  $I_n$ , or  $C_v$  can change the delay, thus the oscillating frequency. Turning is continuous in this case and easily achieved wide lock range without much area. Some potential problems with this approach are:

- 1. When the current is small, in order to achieve wide lock range, the slope of transition is sluggish, which is susceptible to noise and may cause excessive jitter of the output.

- For high-speed applications, the number of stages needs to be limited. For CMOS

ring oscillator, at least three stages are needed. In order to provide enough gain for

the oscillation, tradeoffs among gain, speed, and number of stages need to be

considered.

- 3. The mismatching may cause  $I_p \neq I_n$ , and duty cycle distortion in the output (which is unacceptable for XOR PD).

- 4. It is supply and substrate noise sensitive.

- 5. The gain of VCO is not constant under the variations of process and temperature, which may cause stability problem in a PLL system.

In order to improve the performance of a VCO, a fully differential delay buffer, shown in Figure 2.13, can be used to reject common-mode noise. The voltage –controlled resistors can be realized by the P-type MOSFET, which is biased on the triode region. Another way to adjust the delay is by changing the tail current. Matched layout is very important to get identical delay per stage. Since the fully differential approach uses crosspoint of the output and the complement of output, the signal swing doesn't need to be rail-to-rail, which may be suitable for low supply voltage applications. A level shifting circuit is needed to bring the voltage level back to the logic levels. Another benefit is negligible duty-cycle distortion. However, slow-transition problems are still related to this implementation.

When the input is out of range, the gain drops to zero and oscillations stop. In order to stabilize the operation under variations in process and temperature, self-biasing technologies are used, and discussed in Chapter 4. Noise issues with oscillators are investigated in Chapter 3.

Figure 2.13. Fully differential delay buffer [15]

## 2.3. System Analysis of a Second-Order PLL

When we put these three building blocks together and apply a linear approximation for the basic PLL system, a simple system model can be derived, and is shown in Figure 2.14. If the loop gain is  $K = K_{pd} K_{vco}$ , the product of the PD gain and VCO gain, the transfer function of the basic PLL system is

$$H(s) = \frac{\phi_{pll}}{\phi_{ref}} = \frac{K \cdot F(s)}{s + K \cdot F(s)}$$

(2.9)

where the F(s) is the transfer function of the LF given in section 2.2.2. If the divide-by-N is added in the feedback path, then the loop gain is  $K = K_{pd} K_{vco}/N$ . Without the LF ( $F(s) = K_L$ , just a gain factor), the PLL is a 1<sup>st</sup> order system, which is a model for all-digital implementation. The high loop gain also results in a wider bandwidth, which may not be suitable for some applications. With the first-order loop filter, the order of a basic PLL system is two because of the pole in the VCO.

Figure 2.14. Linear model of second-order PLL system

With the consideration of damping factor  $\zeta$  and natural frequency  $\omega_n$ , the general form of second-order system is

$$H(s) = \frac{\omega_n^2}{s^2 + 2\zeta \cdot \omega_n \cdot s + \omega_n^2}$$

(2.10)

Different topologies of the loop filter result in different  $\zeta$  and  $\omega_n$ , which is listed in the Table 2.3. From Table 2.3, we find that damping factor and natural frequency of the basic PLL system has a direct relationship with the loop gain (K) and LF parameters. For the basic RC filter, the  $\zeta$  and  $\omega_n$  have an inverse relationship with the loop gain. The added zero in the passive and active LFs will minimize this dependence and stabilize the loop operation. It's important to keep the loop gain constant to achieve ideal dynamic response of the PLL.

Another interesting point is the relationship between the static phase error ( $\Delta \phi$ ) and input phase ( $\phi_{ref}$ ). From Figure 2.13 and Equation (2.9), it's easy to derive the phase error transfer function  $H_e(s)$  which is given by

$$H_e(s) = \frac{\Delta \phi}{\phi_{ref}} = \frac{s}{s + K \cdot F(s)}$$

(2.11)

In the steady state, the PLL is locked with its transient dead. The steady state condition can be expressed by the static phase error,  $\phi_e(t\to\infty)$ . Assume  $\omega_{ref}=\omega_0$ , at t <0 and a frequency step  $\Delta\omega$  is applied at t = 0. The phase difference of the input is  $\Delta\omega$  u(t), where u(t) is a unit step function. In the frequency domain, it can be expressed as  $\Delta\omega/s^2$ . Using the final value theorem, the static phase error is given as follows:

$$\phi_e(t \to \infty) = \lim_{s \to 0} s \cdot H_e(s) \cdot \frac{\Delta \omega}{s^2}$$

(2.12)

The static phase error for the step in frequency based on different loop filters is listed on Table 2.3. Type<sup>1</sup> C filter has 0 static phase error if the op-amp is idea, where higher loop gain can suppress the static phase error for Type A and Type B filters. However, higher loop gain of Type A LF will degrade the damping factor and make the PLL unstable. That's the reason why basic RC filter is rarely found in practical PLL implementations.

If  $K >> \omega_n$  (high gain loop) for Type B and C filters, Equation (2.9) and (2.11) turn out to be

$$H(s) = \frac{\omega_n^2 + 2\zeta\omega_n \cdot s}{s^2 + 2\zeta \cdot \omega_n \cdot s + \omega_n^2}$$

(2.13)

$$H_e(s) = \frac{s^2}{s^2 + 2\zeta \cdot \omega_n \cdot s + \omega_n^2}$$

(2.14)

-

<sup>&</sup>lt;sup>1</sup> Here, the type of loop filter should not be confused with the type of PLL, which refers to the number of pure integrator (a pole at 0) included in the feedback system. A PLL with active PI filter is Type II.

|                     | TYPE | NATURAL<br>FREQUENCY               | DAMPING FACTOR                                                                    | STATIC PHASE<br>ERROR    |

|---------------------|------|------------------------------------|-----------------------------------------------------------------------------------|--------------------------|

| Basic RC<br>network | A    | $\sqrt{\frac{K}{RC}}$              | $\frac{1}{2} \cdot \sqrt{\frac{1}{K \cdot RC}}$                                   | $\frac{\Delta\omega}{K}$ |

| Passive lag filter  | В    | $\sqrt{\frac{K}{\tau_1 + \tau_2}}$ | $\frac{1}{2} \cdot \sqrt{\frac{K}{\tau_1 + \tau_2}} \cdot (\tau_2 + \frac{1}{K})$ | $\frac{\Delta\omega}{K}$ |

| Active PI filter    | С    | $\sqrt{rac{K}{	au_1}}$            | $\frac{	au_2}{2} \cdot \sqrt{rac{K}{	au_1}}$                                     | 0 (with idea op-amp)     |

Table 2.3. Different loop parameters for the second-order system based on the various loop filters (Referring to Figure 2.10,  $\tau_1 = R_1C$ ,  $\tau_2 = R_2C$ ;  $\Delta\omega$  refers to the input frequency step)

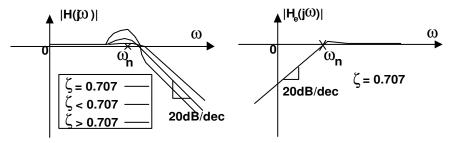

From equation (2.13), the phase transfer function of basic PLL system shows low-pass characteristics with bandwidth  $\omega_n$ . The  $\zeta$  determines the dynamic response of the second-order system, shown in the Figure 2.14 left. For  $\zeta > 1$ , the transfer function flattens out, and the dynamic response becomes sluggish (overdamped); for  $\zeta < 1$ , results in overshoot and oscillating. The optimal point may choose  $\zeta = 0.707$ . On the other hand, Equation (2.14) shows that phase error has high-pass transfer function, shown in Figure 2.15 right plot. In the low frequency range, the phase error is attenuated to be small, where in high frequency range (> $\omega_n$ ), large phase error can cause the PLL to lose tracking. A higher-order (> 2) system may be used to improve high-frequency attenuation, but this system may not be stable and may have some penalty in the settling time.

Figure 2.15. Magnitude Plots of the PLL Phase Transfer Function (left) and Error Transfer Function (right)

The steady state condition and linear approximation of a PLL system is the start point to understand a PLL operation. The transient response and loop dynamics will be investigated in Chapter 3. The challenges in design a PLL bring out a new candidate for clock synchronization: the delay-locked loop.

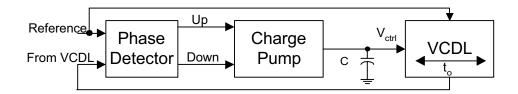

## 2.4. A new candidate -- Delay-locked loop (DLL)

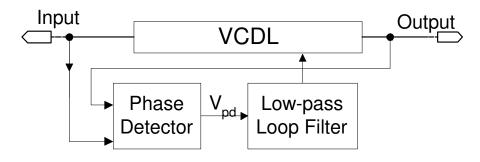

A delay-locked loop, shown in Figure 2.16, uses a voltage-controlled delay line (VCDL) to replace the VCO used in a PLL. The basic operation of DLL is to delay the input reference signal (clock) through a delay line to get a zero phase shift at the output (one period delay according to the input reference). The frequency of the input and output signals are same. The big difference between DLL and PLL is that VCDL doesn't generate a signal. This limits a DLL from being used in frequency synthesis applications. Another difference is no separated reference signal is needed in a DLL.

Figure 2.16. Block diagram of a DLL

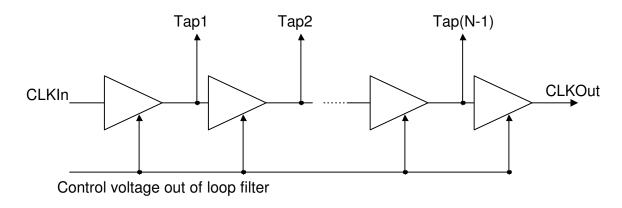

A (N-1)-tap of VCDL is shown in Figure 2.17. Suppose the input frequency is 400MHz ( $T_{clk} = 2.5ns$ ) and N=16. If the DLL is in the locked state (the rising edges of *CLKIn* and *CLKOut* occur at the same time), the VCDL can provide 16 different time-shifted taps of input clock signal, and each delay-per-tap is equal to 156ps. These equal spaced taps

can be used to provide optimum clock strobe for different DQ outputs in high-speed memory interface. It's also easy to get the quadrature signal out of Tap 4, which is shifted 90 degrees from *CLKIn*. Each delay buffer used in VCDL can be the same as was discussed in section 2.2.3. If mismatches between taps are negligible, the tap delay is independent of device parameters even in the presence of temperature and process variations.

Figure 2.17. Block diagram of the voltage-controlled delay line (VCDL)

DLLs have much more relaxed tradeoffs among gain, bandwidth and stability since it can be designed as a first-order system [15] [37], a simple capacitor for the loop filter. Noise injected into a DLL disappears at the end of the delay line, eliminating the noise recirculating occurring in an oscillator. A false lock should be avoided when the maximum delay of VCDL equals to the twice of input clock period. Figure 2.18 shows the relationship between the *CLKIn* and the quadrature clock output (for the previous example, the  $4^{th}$  tap). If the VCDL electrical length is  $2T_{CLK}$ , the quadrature output is  $T_{CLK}$  / 2 from *CLKIn* instead of  $T_{CLK}$  / 4.

Another way to implement DLL uses all-digital techniques and it can be designed as a 0<sup>th</sup>-order system, where no integration is taken place in such a system. The delay is changed using method one, i.e. changing the number of delay taps. The big benefit of all digital DLLs

is easy to scale for other processes and applications. The detail of this all digital implementation will be examined in Chapter 5.

Figure 2.18. False lock of a DLL (input clock and quadrature output are shown)

# Chapter 3

# **Loop Dynamics and Jitter**

## 3.1. Tracking and Acquisition

Since the basic PLL system is not a linear system, it can be difficult to analyze its transient

#### different conditions: