# DESIGN, FABRICATION AND TESTING OF MONOLITHIC LOW-POWER PASSIVE SIGMA-DELTA ANALOG-TO DIGITAL-CONVERTERS

by

Angsuman Roy

Bachelor of Science in Electrical Engineering

University of Nevada Las Vegas

2013

A thesis submitted in partial fulfillment of the requirements for the

Master of Science in Engineering – Electrical Engineering

Department of Electrical and Computer Engineering

Howard R. Hughes College of Engineering

The Graduate College

University of Nevada Las Vegas

November 2015

© Angsuman Roy 2015

All Rights Reserved

#### **ABSTRACT**

Analog-to-digital converters are critically important in electronic systems. The difficulty in meeting high performance parameters increases as integrated circuit design process technologies advance into the deep nanometer region. Sigma-delta analog-to-digital converters are an attractive option to fulfill many data converter requirements. These data converters offer high performance while relaxing requirements on the precision of components within an integrated circuit. Despite this, the active integrators found within sigma-delta analog-to-digital converters present two main challenges. These challenges are the power consumption of the active amplifier and achieving gain-bandwidth necessary for sigma-delta data converters in deep nanometer process technologies. Both of these challenges can be resolved through the replacement of active integrators with passive integrators at the expense of resolution.

Three passive sigma-delta topologies were examined and characterized in detail.

Two of these topologies were first-order and second-order noise shaping topologies. A new passive topology was developed which was determined to be optimal in resolution compared to the two traditional designs. This topology exhibits a first-order signal transfer function and a second-order noise transfer function. A method for increasing resolution of passive sigma-delta data converters despite inherent performance constraints was developed.

Three example circuits were designed, fabricated and tested using On Semiconductor's C5 500 nanometer CMOS process. These designs were optimized for low

power and utilized memory sense amplifiers as quantizing elements. The first circuit, using passive lumped on-chip elements for the noise shaping network achieved a power consumption of 100 micro-watts and an effective resolution of 8-bits. The second circuit replaced the lumped components with switched-capacitor elements and achieved a power consumption of 6.75 micro-watts and an effective resolution of 9.3 bits. The third circuit was designed as a case study for the application of the proposed topology to "K-delta-1-sigma" modulators. This circuit achieved a power consumption of 10 milli-watts and an effective resolution of 10 bits.

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor Dr. R. Jacob Baker for the extensive, untiring support provided to me as a student at UNLV. He has served not only as an academic advisor but as a role model for the rest of my life. I would like to thank my committee for all the guidance they have given to me over the years –Dr. Peter Stubberud, Dr. Yahia Baghzouz, and Dr. Evangelos Yfantis. My undergraduate research team consisting of Matthew Meza, Joey Yurgelon, Dane Gentry, Mario Verduzco, Michael Ghisilieri and Gerardo Gomez have been instrumental and critical to the completion of this research. I would like to thank Brandon Blackstone for providing the facility resources needed to complete this research as well as being a mentor to me. I would also like to thank Golf Nantanapramoth for providing electronic components at all hours of the night. Finally, I am grateful to my parents for providing a supportive environment that has facilitated my education. I am especially grateful for my father's encouragement in pursuing lifelong education.

# **Table of Contents**

| Abstract                                          | i   |

|---------------------------------------------------|-----|

| Acknowledgements                                  | iii |

| List of Figures                                   | vi  |

| List of Tables                                    | xii |

| Chapter 1 Introduction                            | 1   |

| Oversampling                                      | 3   |

| Noise-shaping                                     | 9   |

| Sigma-Delta Principles                            | 12  |

| Chapter 2 Passive Sigma-Delta Modulators          | 18  |

| Transfer Function Derivations                     | 18  |

| Simulated Comparison                              | 39  |

| Chapter 3 Discrete Component Level Implementation | 47  |

| Chapter 4 Continuous Time Sigma-Delta Modulators  | 53  |

| Circuit Design                                    | 53  |

| Measurements                                      | 66  |

| Chapter 5 Switched-Capacitor Sigma-Delta Modulators | 74  |

|-----------------------------------------------------|-----|

| Switched-Capacitor Basics                           | 74  |

| Circuit Design                                      | 77  |

| Measurements                                        | 87  |

| Chapter 6 Passive KD1S Modulators                   | 95  |

| Introduction to KD1S Modulators                     | 95  |

| Circuit Design                                      | 100 |

| Measurements                                        | 109 |

| Conclusion                                          | 115 |

| References                                          | 117 |

| Appendix A.4 Schematics and Layouts for Chapter 4   | 121 |

| Appendix A.5 Schematics and Layouts for Chapter 5   | 124 |

| Appendix A.6 Schematics and Layouts for Chapter 6   | 131 |

# List of Figures

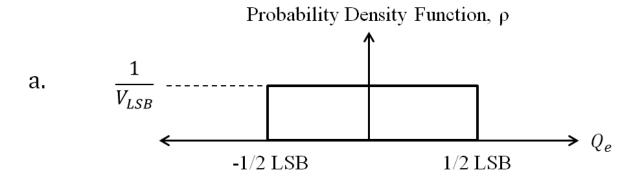

| Figure 1.1 (a) Probability density function and (b) quantization noise spectral density6     |

|----------------------------------------------------------------------------------------------|

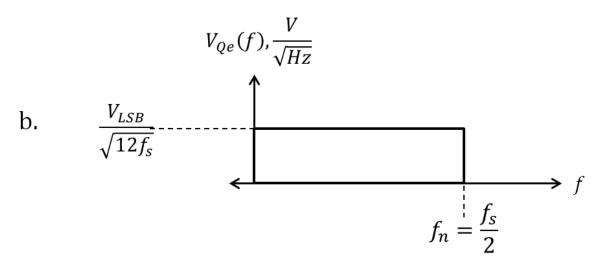

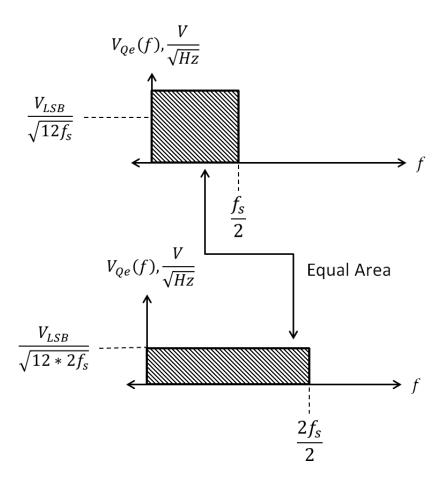

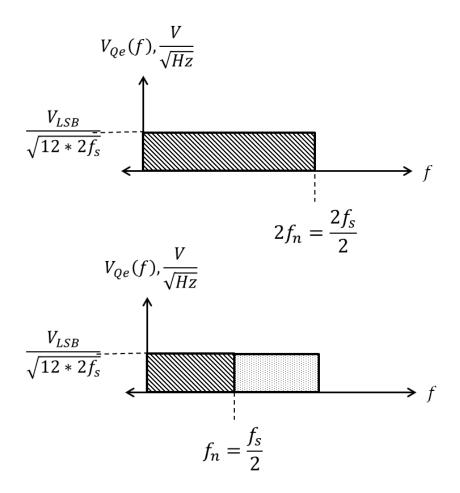

| Figure 1.2 – Effect of increasing sampling frequency on quantization noise spectral          |

| density7                                                                                     |

| Figure 1.3 – Bandlimiting an oversampled signal8                                             |

| Figure 1.4 – Comparison of quantization noise for (a) Nyquist rate, (b) simple oversampling  |

| and (c) noise-shaping11                                                                      |

| Figure 1.5 – Comparison of 1st and 2nd order noise-shaping12                                 |

| Figure 1.6 – System level block diagram13                                                    |

| Figure 1.7 – Comparator and integrator outputs14                                             |

| Figure 1.8 – Block diagram of feedback modulator16                                           |

| Figure 2.1 – Circuit (a) and block diagram and (b) schematic of 1st order passive            |

| sigma-delta modulator19                                                                      |

| Figure 2.2 – Schematic of 2nd order passive sigma-delta modulator22                          |

| Figure 2.3 – Schematic of modified 2nd order passive sigma-delta modulator24                 |

| Figure 2.4 – Block diagram of modified 2 <sup>nd</sup> order passive sigma-delta modulator25 |

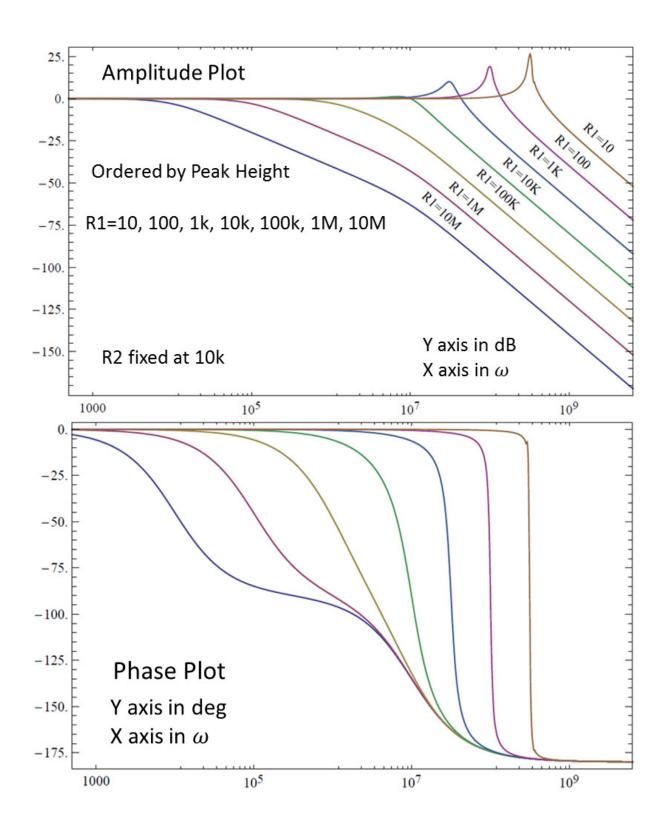

| Figure 2.5 – Bode plot of STF with fixed R1 and varying R2                           | 28 |

|--------------------------------------------------------------------------------------|----|

| Figure 2.6 – Bode plot of STF with fixed R2 and varying R1                           | 29 |

| Figure 2.7 – Bode plot of STF with R1 and R2 varying in opposite directions          | 30 |

| Figure 2.8 – Bode plot of NTF with fixed R1 and varying R2                           | 32 |

| Figure 2.9 – Bode plot of NTF with fixed R2 and varying R1                           | 33 |

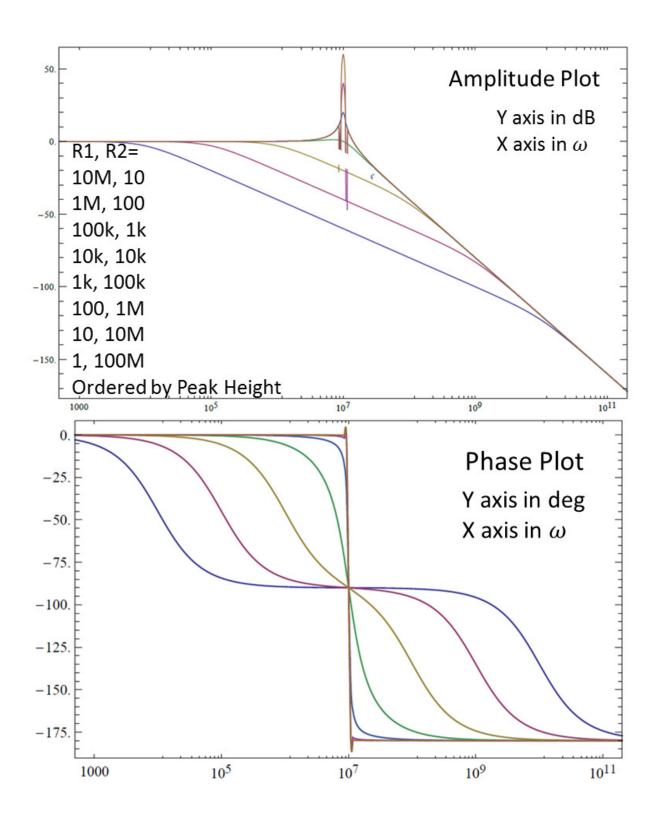

| Figure 2.10 – Bode plot of NTF with R1 and R2 varying in opposite directions         | 34 |

| Figure 2.11 – Bode plot of DTF with R1 fixed and R2 varying                          | 36 |

| Figure 2.12 – Bode plot of DTF with R2 fixed and R1 varying                          | 37 |

| Figure 2.13 – Bode plot of DTF with R1 and R2 varying in opposite directions         | 38 |

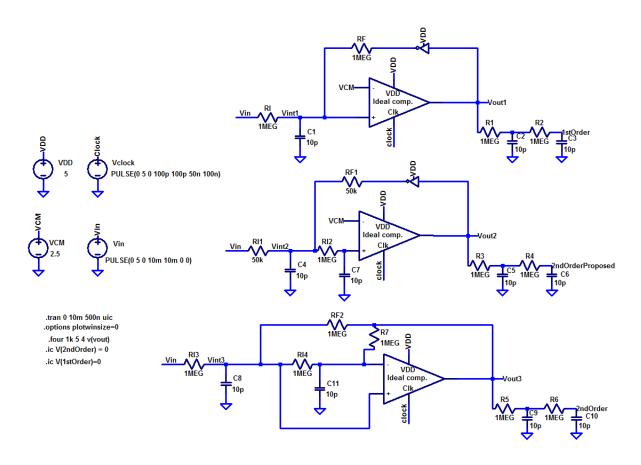

| Figure 2.14 — Simulation testbed for 1st and 2nd order passive modulators            | 39 |

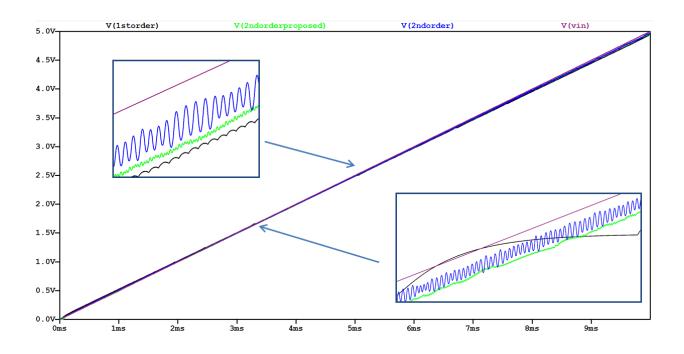

| Figure 2.15 – Transfer curves and zoomed insets                                      | 41 |

| Figure 2.16 – Transfer curves for equal area and zoomed inset with dead zones        | 43 |

| Figure 2.17 – Filtered output of each modulator with a 1 kHz input signal            | 44 |

| Figure 2.18 – FFT of each modulator's filtered output                                | 44 |

| Figure 2.19 – FFT of each modulator's digital output                                 | 46 |

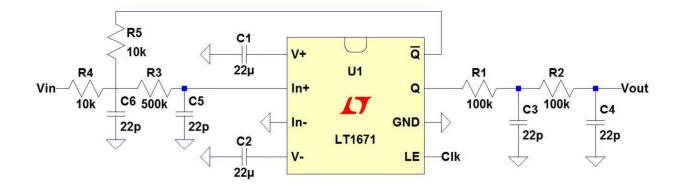

| Figure 3.1 – Schematic of LT1671 based $2^{nd}$ -order $\Sigma$ - $\Delta$ modulator | 48 |

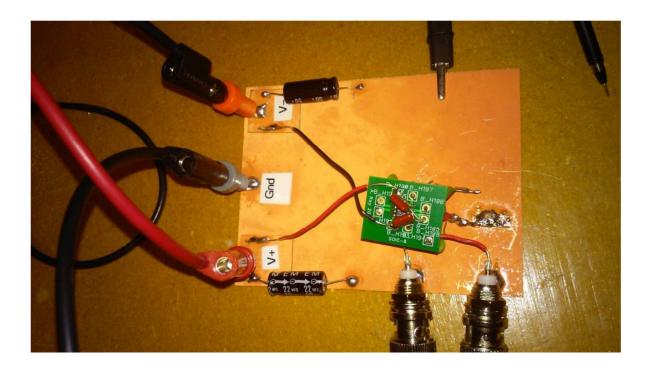

| Figure 3.2 – Top and bottom of circuit on SOIC-8 breakout board                      | 49 |

| Figure 3.3 – Set-up used for SNDR testing                                                  | 49 |

|--------------------------------------------------------------------------------------------|----|

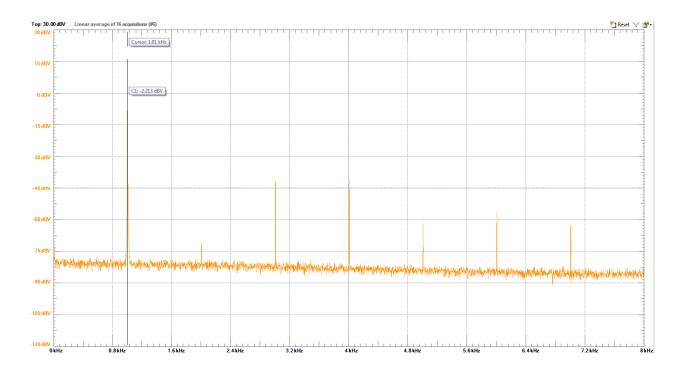

| Figure 3.4 – Example output spectrum                                                       | 50 |

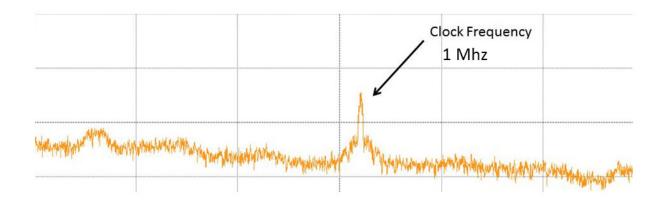

| Figure 3.5 – Remnant of 1 MHz clock frequency                                              | 51 |

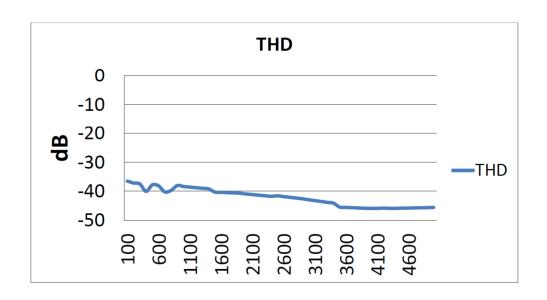

| Figure 3.5 – THD as a function of input frequency (Hz)                                     | 52 |

| Figure 3.6 – ENOB as a function of input frequency (Hz)                                    | 52 |

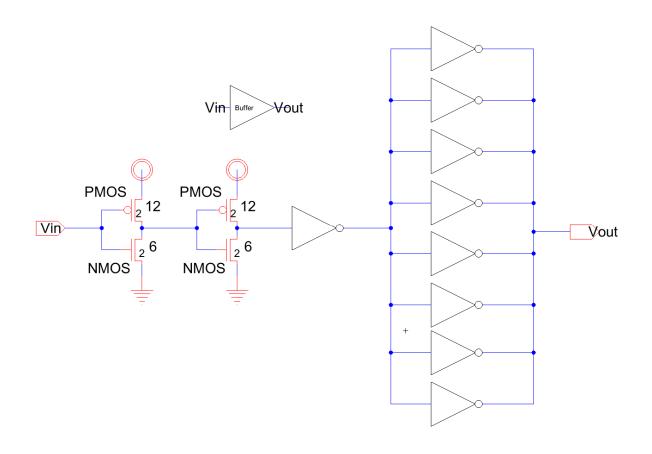

| Figure 4.1 – Basic schematic of continuous time sigma-delta modulator                      | 53 |

| Figure 4.2 – Layouts of passive components (not to scale)                                  | 55 |

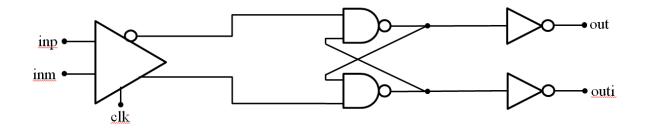

| Figure 4.3 – Block diagram of comparator                                                   | 56 |

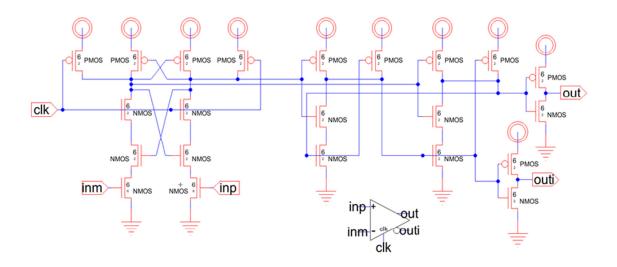

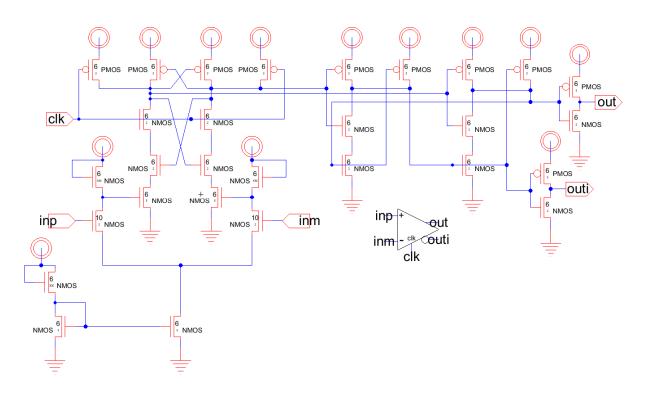

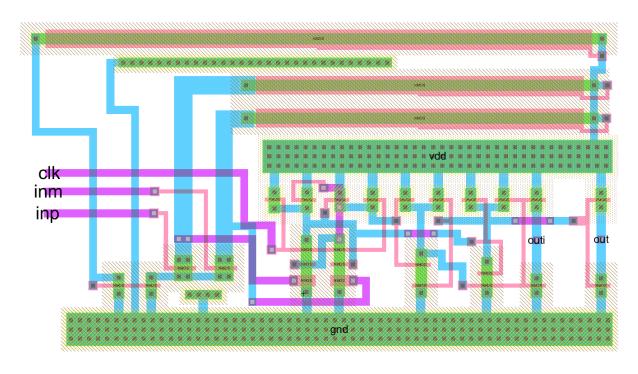

| Figure 4.4 – Sense amplifier schematic                                                     | 57 |

| Figure 4.5 – Inverter switching point                                                      | 58 |

| Figure 4.6 – Full schematic of comparator                                                  | 59 |

| Figure 4.7 – Comparator operation with $V_{inp}$ (green), $V_{inm}$ (red), $V_{out}$ (blue | ), |

| and V <sub>outi</sub> (teal)                                                               | 59 |

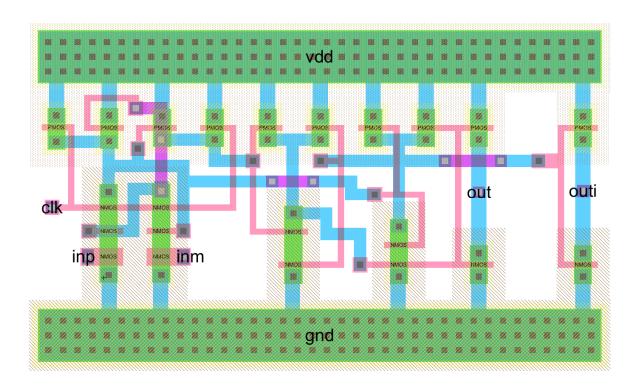

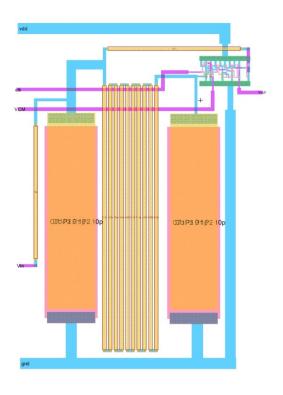

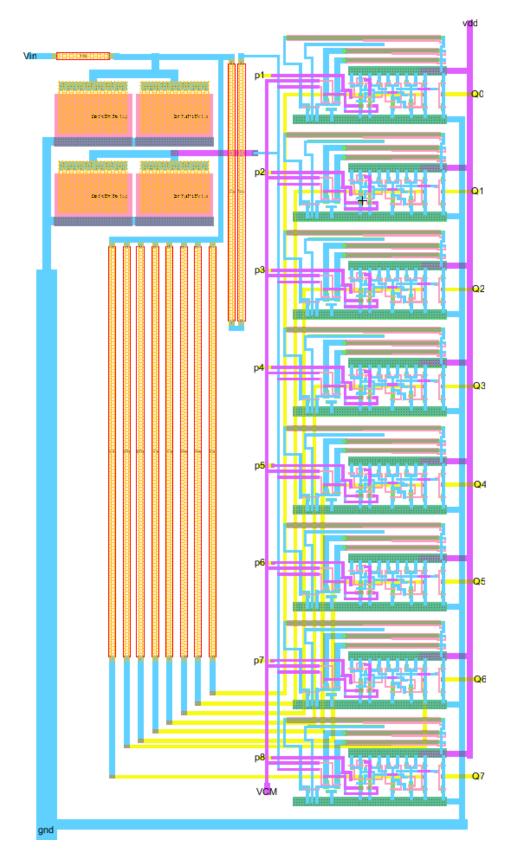

| Figure 4.8 – Comparator layout                                                             | 60 |

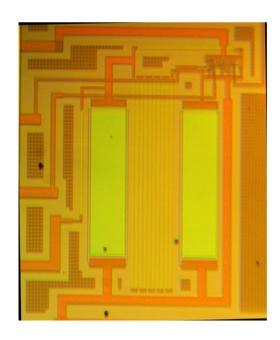

| Figure 4.9 – Complete modulator layout                                                     | 61 |

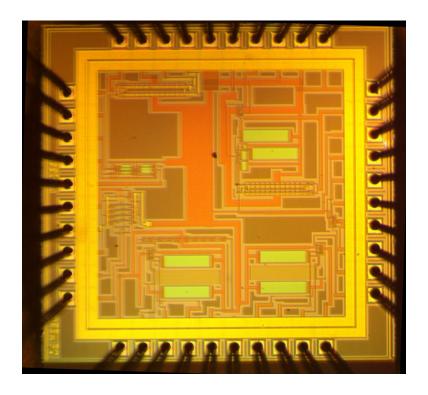

| Figure 4.10 – Micrograph of modulator                                                      | 61 |

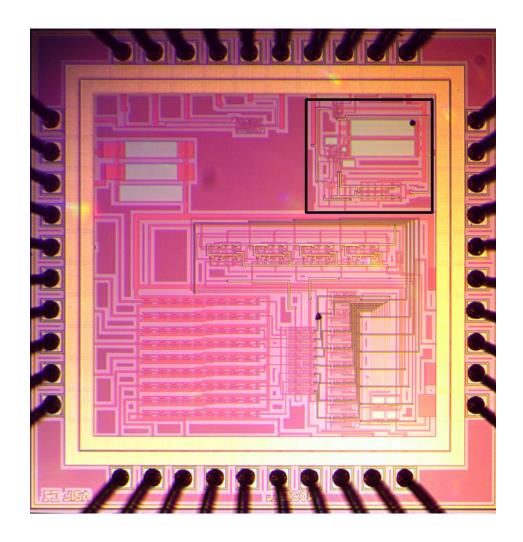

| Figure 4.11 – Micrograph of complete chip                                                  | 62 |

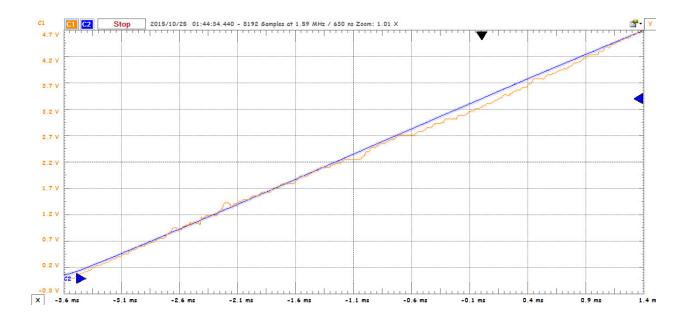

| Figure 4.12 – Input ramp (red) and 1-bit output (blue)                                 | 63 |

|----------------------------------------------------------------------------------------|----|

| Figure 4.13 – Filtered reconstructed output ramp compared to input ramp                | 64 |

| Figure 4.14 – Reconstructed output (blue) and input (red)                              | 65 |

| Figure 4.15 – FFT of modulator output with SNR bandwidth (red) and                     |    |

| out of band noise (blue)                                                               | 66 |

| Figure 4.16 – Simplified schematic of test set-up                                      | 67 |

| Figure 4.17 – "Deadbug" [17] test board (left) and PCB (right)                         | 67 |

| Figure 4.18 – Measured DC transfer function                                            | 68 |

| Figure 4.19 – Measured differential nonlinearity (DNL)                                 | 69 |

| Figure 4.20 – Measured total harmonic distortion (THD) and individual                  |    |

| components                                                                             | 71 |

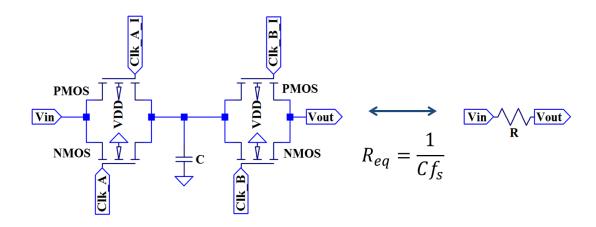

| Figure 5.1 – Structure of switched-capacitor resistor and its relationship to a lumped |    |

| resistor                                                                               | 75 |

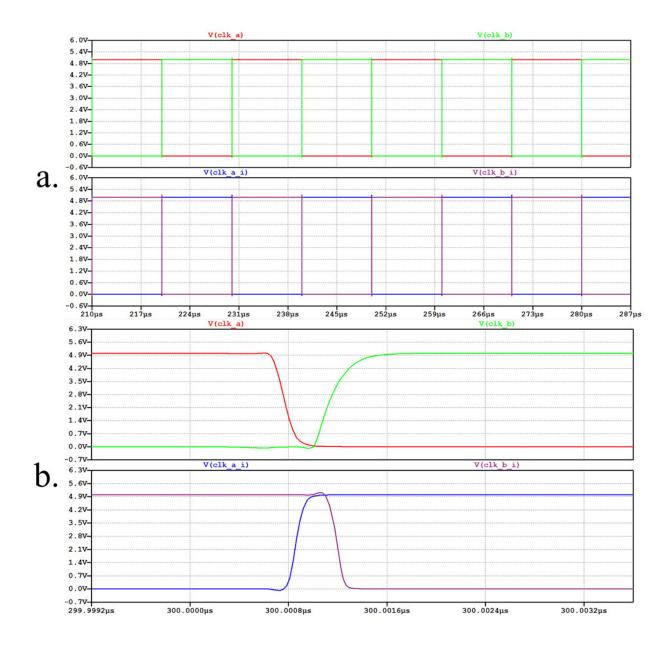

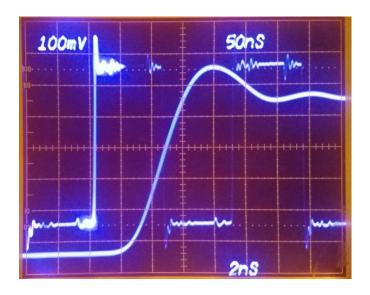

| Figure 5.2 – Clock Signals (a) and zoomed view of edges (b)                            | 76 |

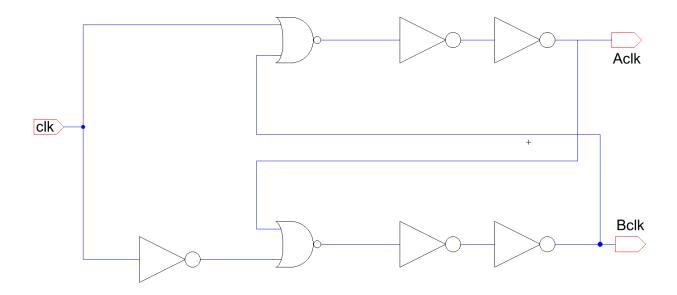

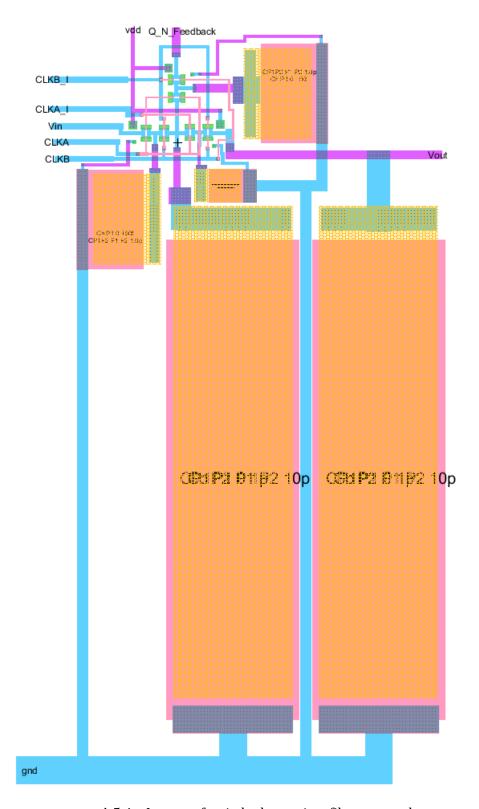

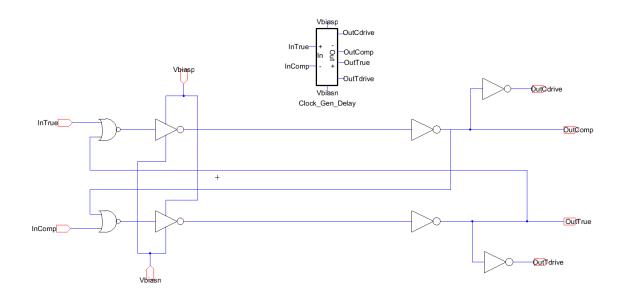

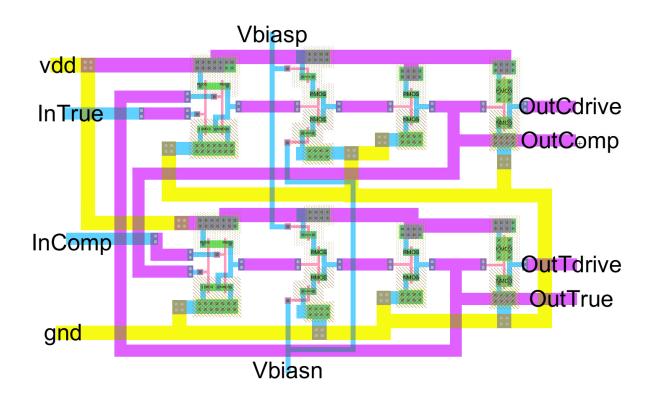

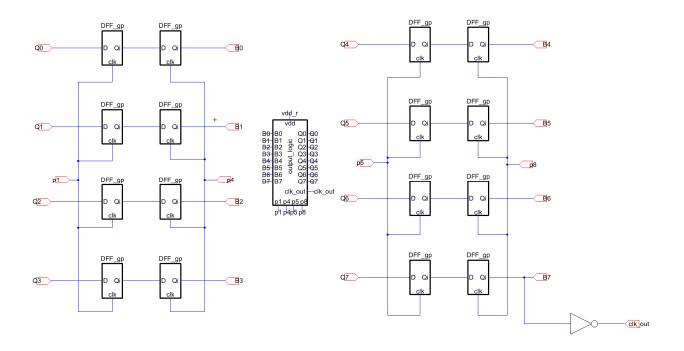

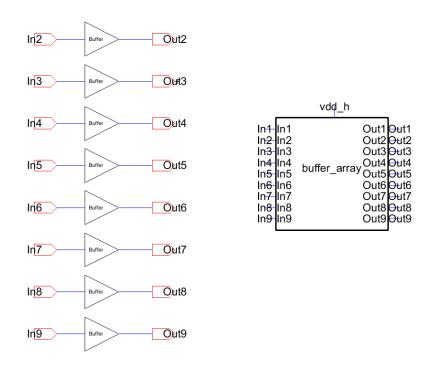

| Figure 5.3 – Logic-level schematic of NL clock generator                               | 78 |

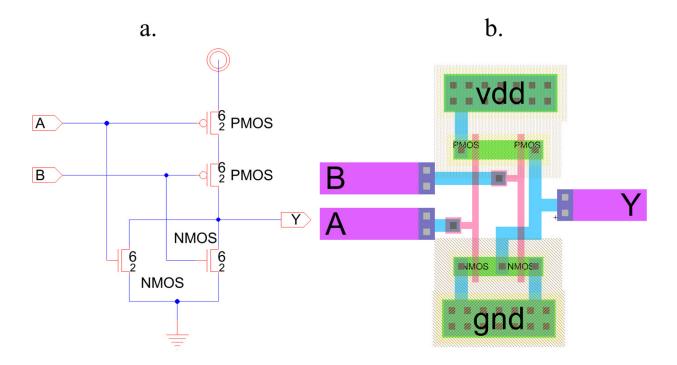

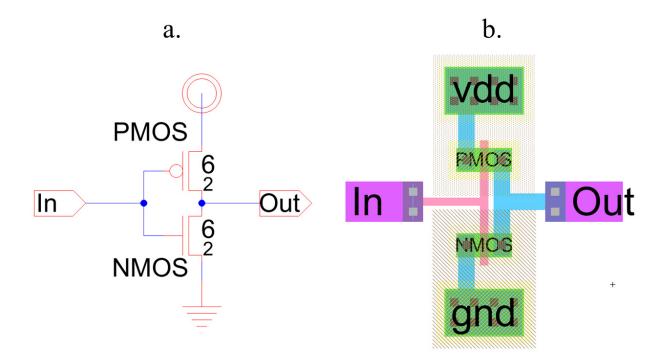

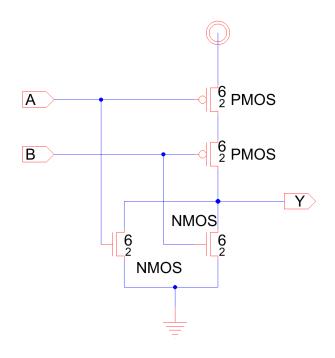

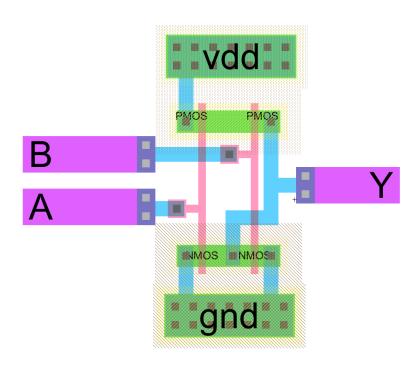

| Figure 5.4 – Schematic (a) and layout (b) views of NOR gate                            | 79 |

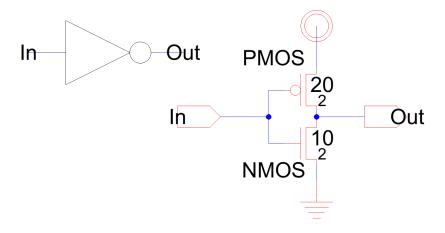

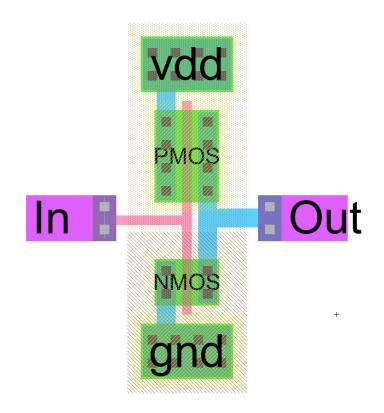

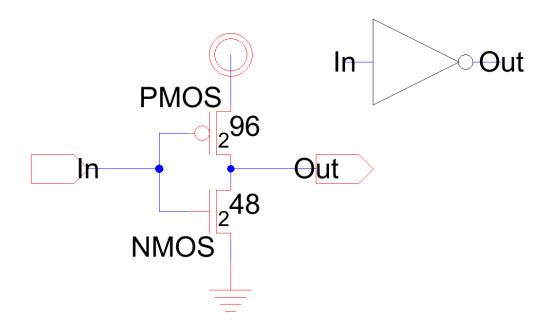

| Figure 5.5 – Schematic (a) and layout (b) views of inverter                            | 80 |

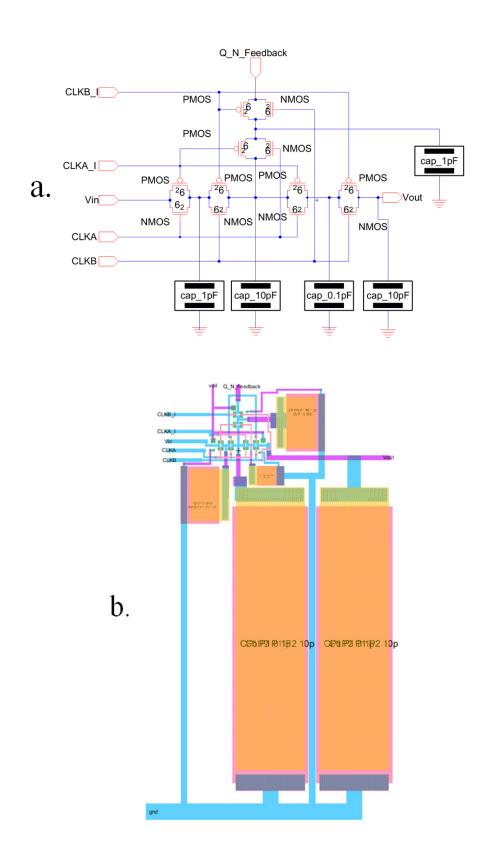

| Figure 5.6 – Schematic (a) and layout (b) of SC-resistor based passive filter                   |

|-------------------------------------------------------------------------------------------------|

| network81                                                                                       |

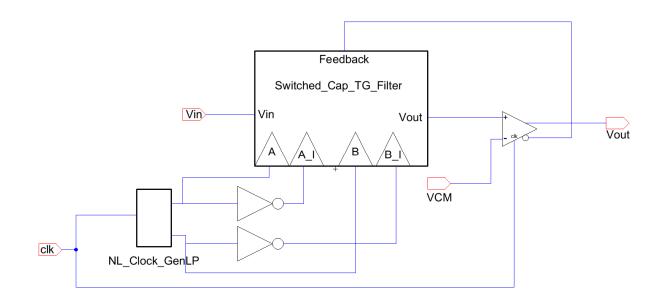

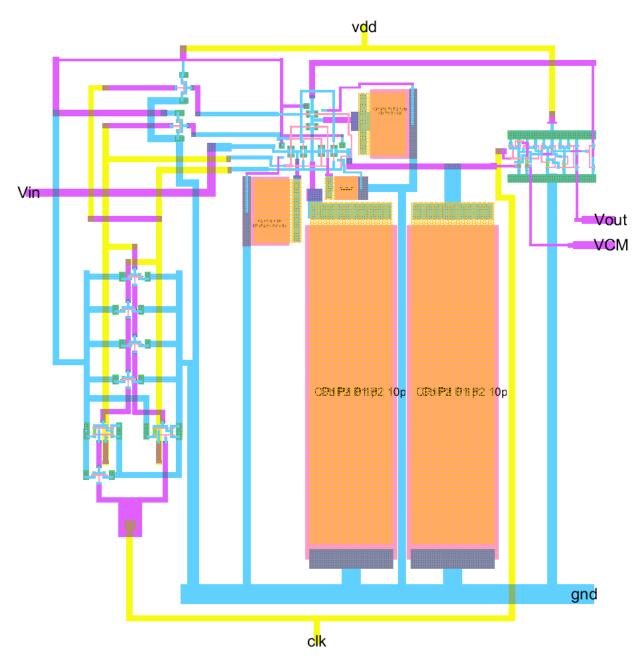

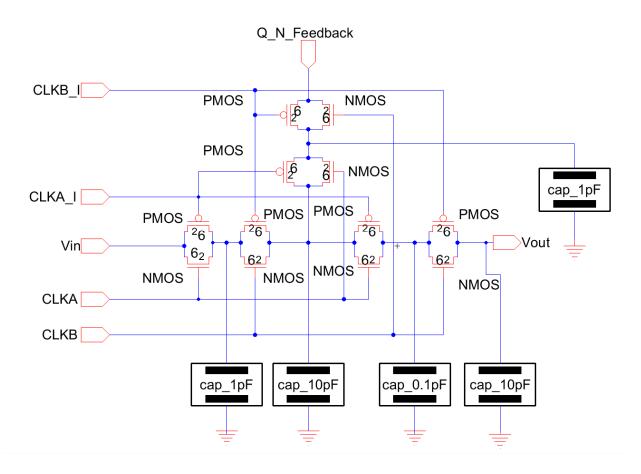

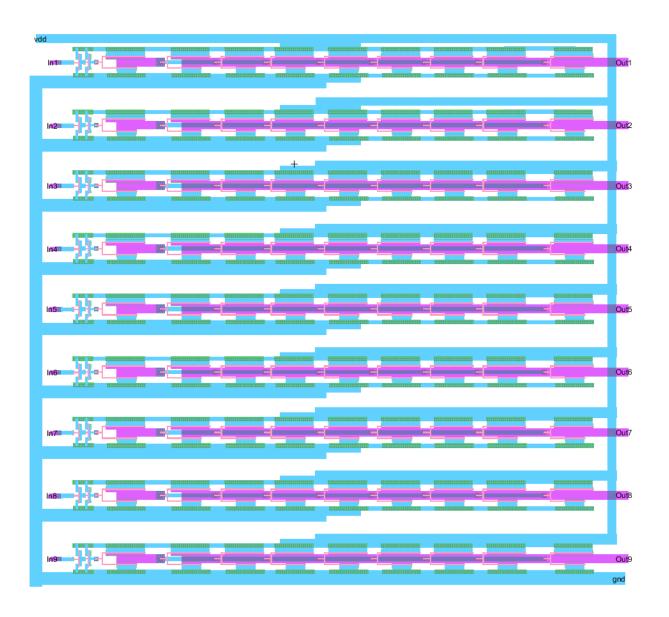

| Figure 5.7 – Complete schematic of SC-based sigma-delta modulator82                             |

| Figure 5.8 – Complete layout of SC-based sigma-delta modulator83                                |

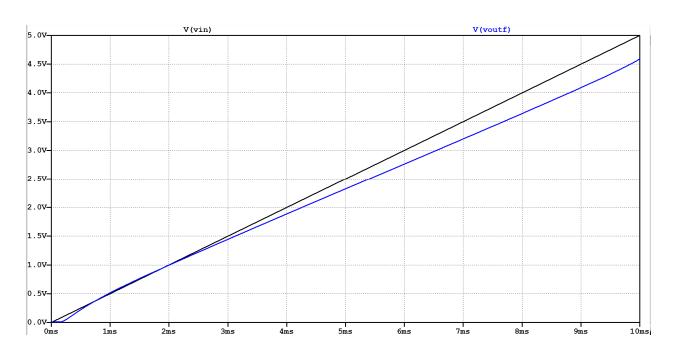

| Figure 5.9 – DC transfer curve of SC-sigma-delta modulator84                                    |

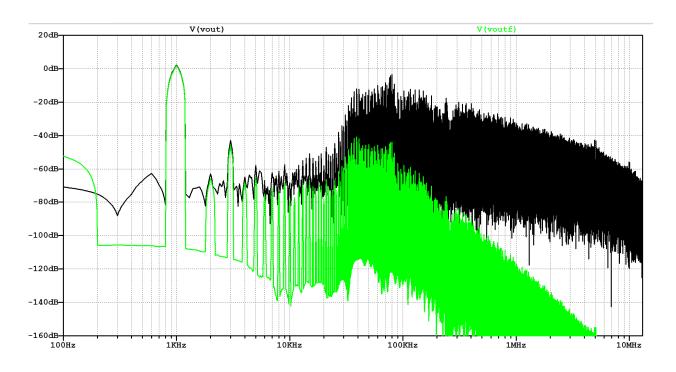

| Figure 5.10 – FFT of 1-bit output (Vout) and filtered output (Voutf)85                          |

| Figure 5.11 – Die photograph of complete chip with $\Sigma$ - $\Delta$ modulator in black box86 |

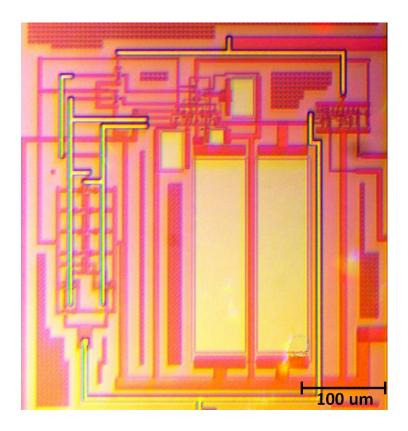

| Figure 5.12 – Zoomed view of SC sigma-delta modulator87                                         |

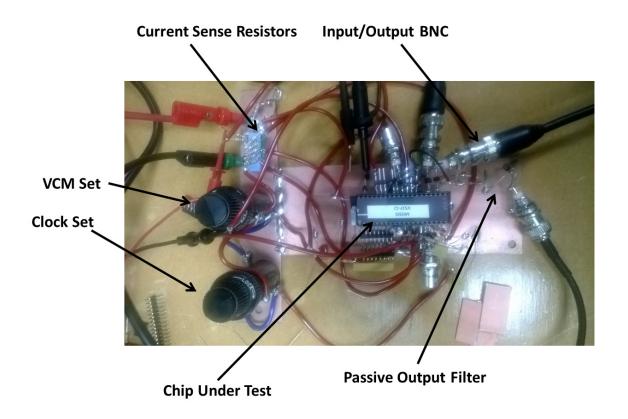

| Figure 5.13 – "Deadbug" test set-up89                                                           |

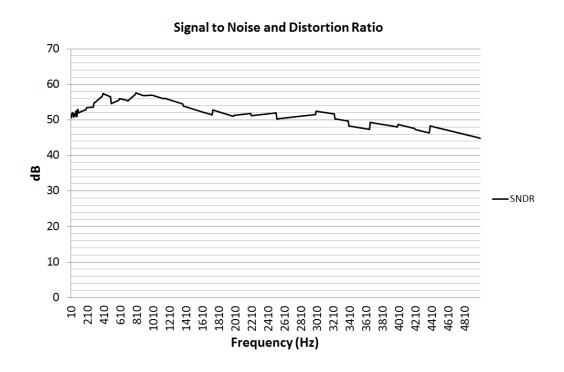

| Figure 5.14 – Measured SNDR91                                                                   |

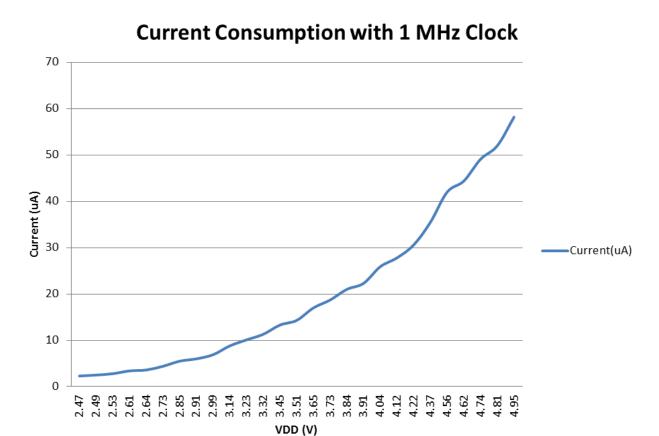

| Figure 5.14 – Measured current consumption as a function of VDD92                               |

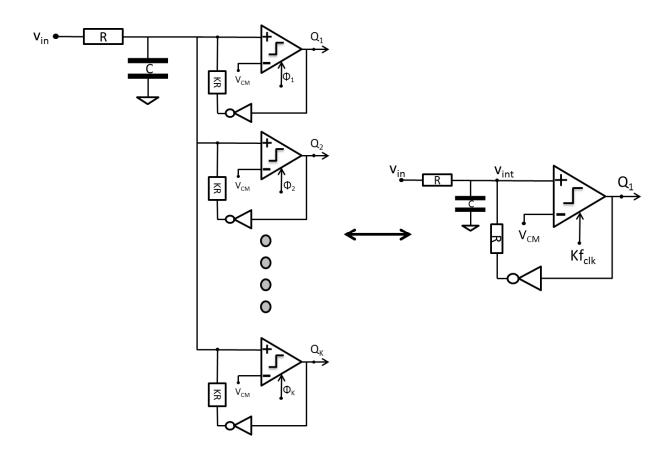

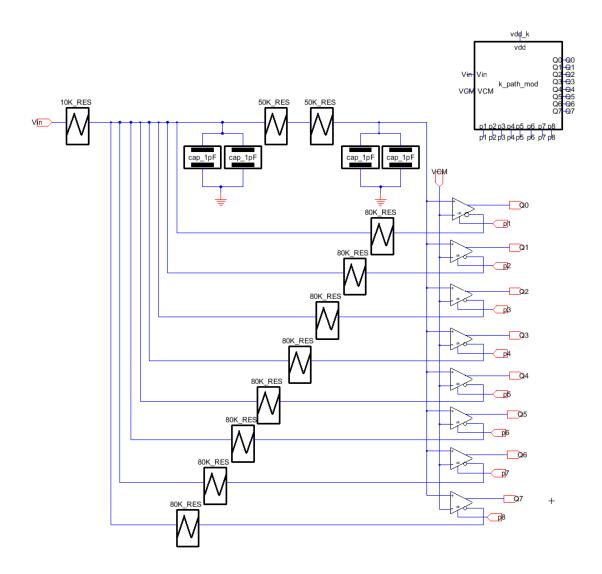

| Figure 6.1 – General structure of KD1S $\Sigma$ - $\Delta$ modulator and equivalent circuit97   |

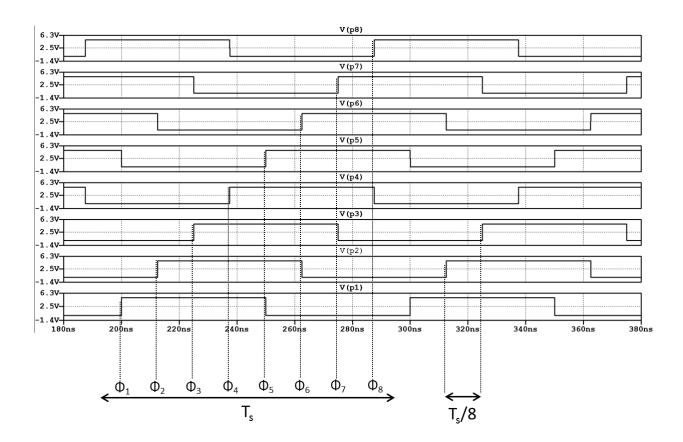

| Figure 6.2 – Example of clock phasing for an 8-path KD1S98                                      |

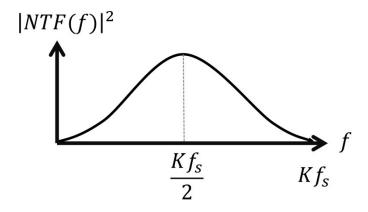

| Figure 6.3 – Theoretical noise transfer function of KD1S modulator99                            |

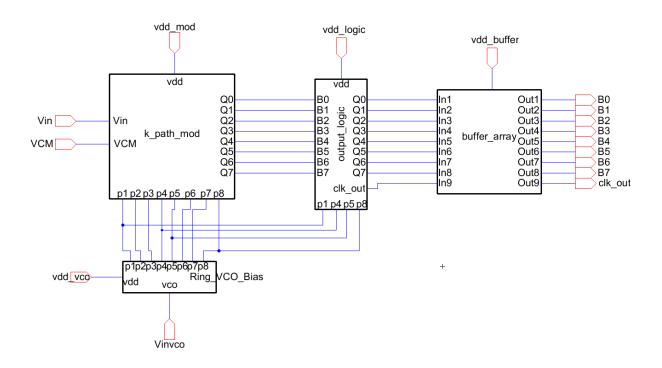

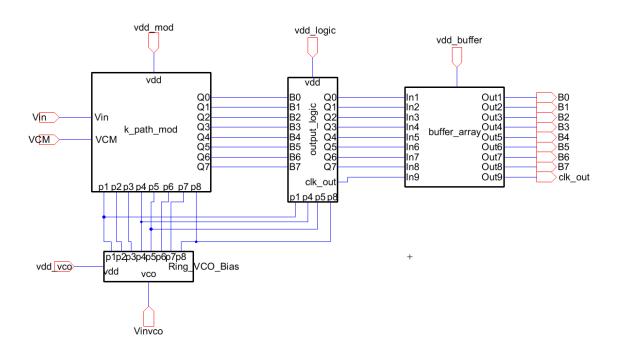

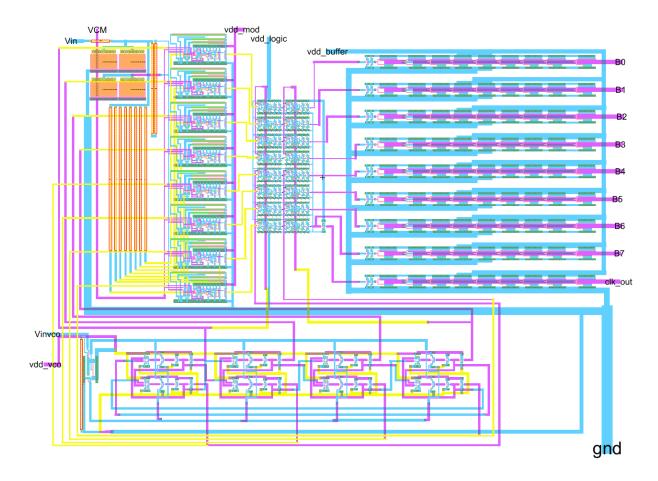

| Figure 6.4 – Block diagram of KD1S modulator100                                                 |

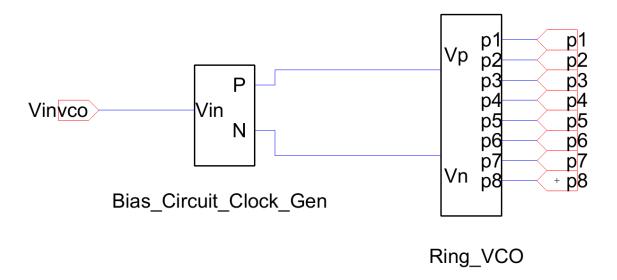

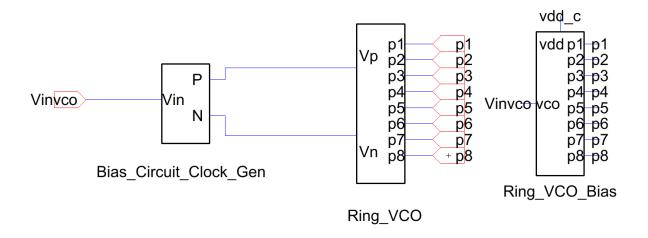

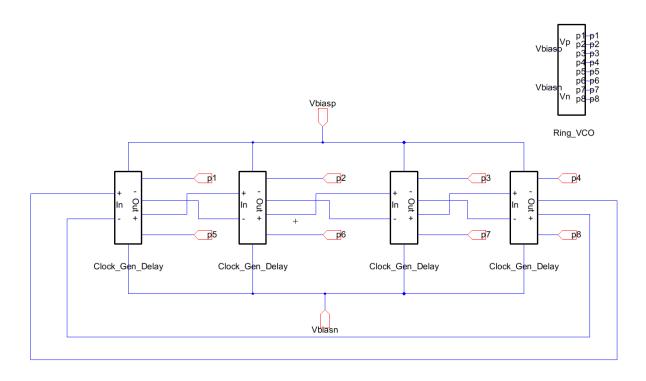

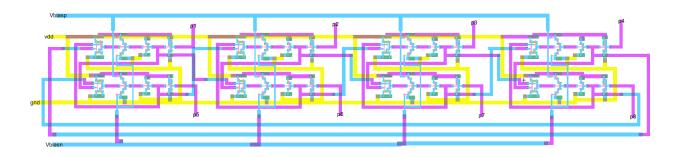

| Figure 6.5 – Block diagram of VCO101                                                            |

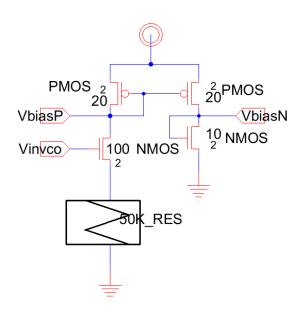

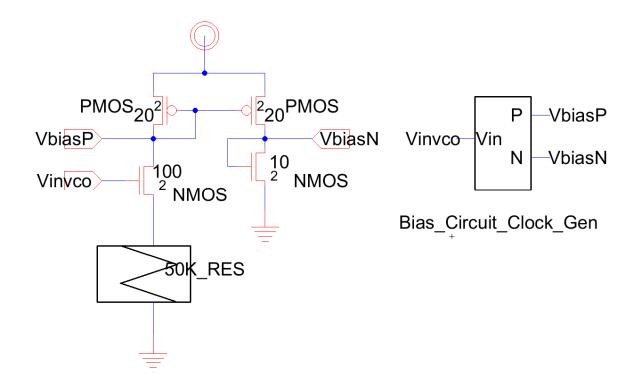

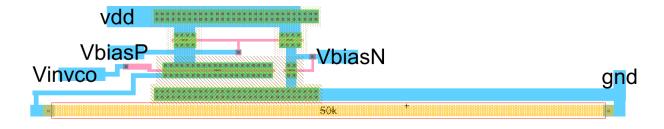

| Figure 6.6 – Bias circuit102                                                                    |

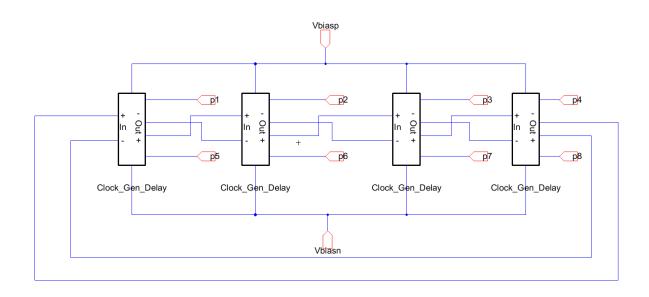

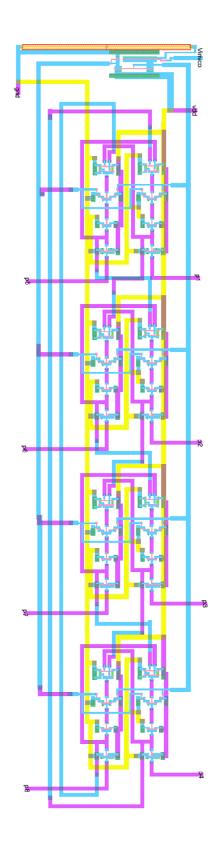

| Figure 6.7 – Ring oscillator comprised of differential delay units            | 102 |

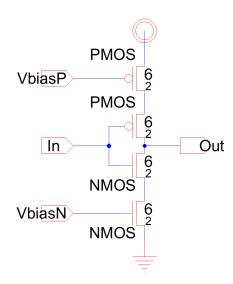

|-------------------------------------------------------------------------------|-----|

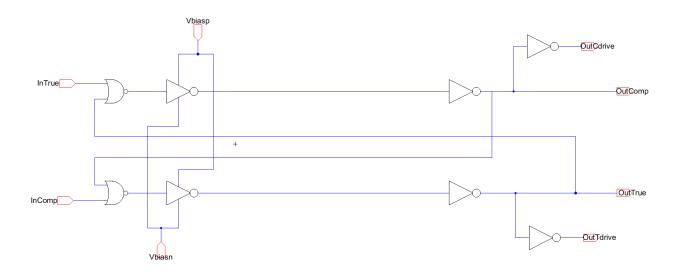

| Figure 6.8 – Schematic of individual delay unit                               | 103 |

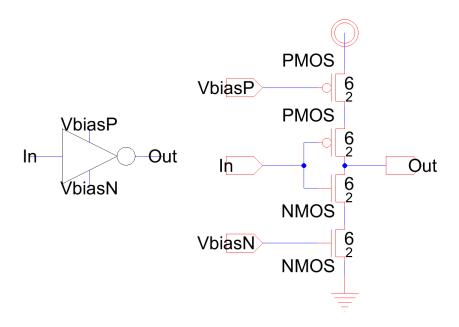

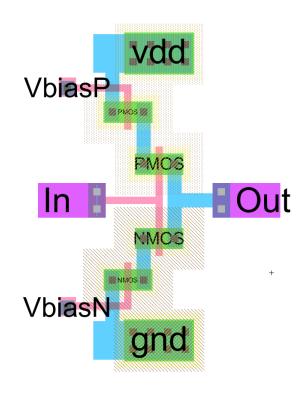

| Figure 6.9 – Schematic of current-starved inverter                            | 104 |

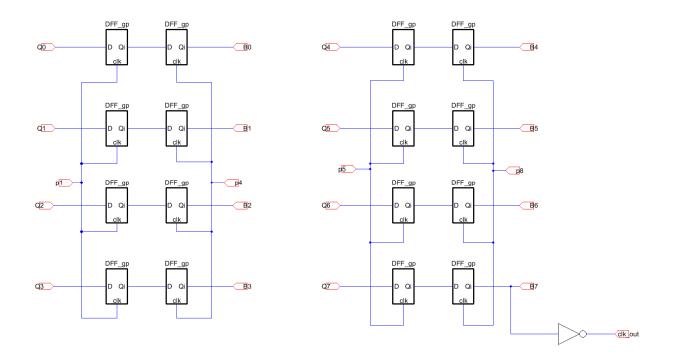

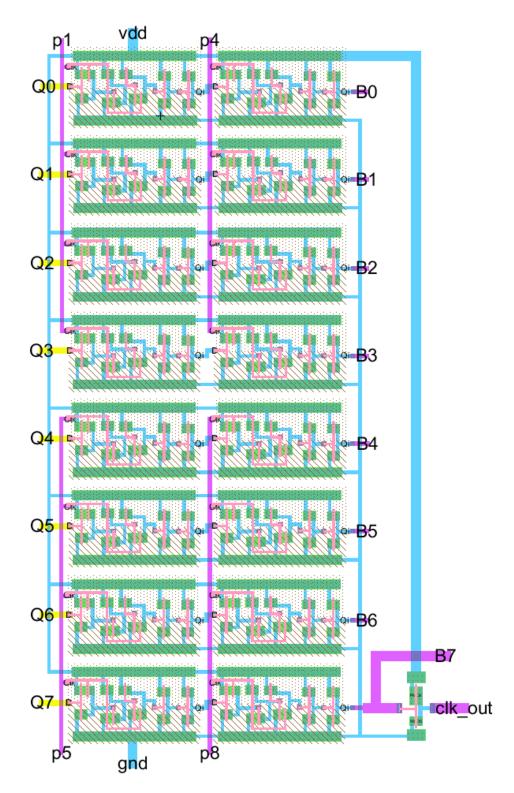

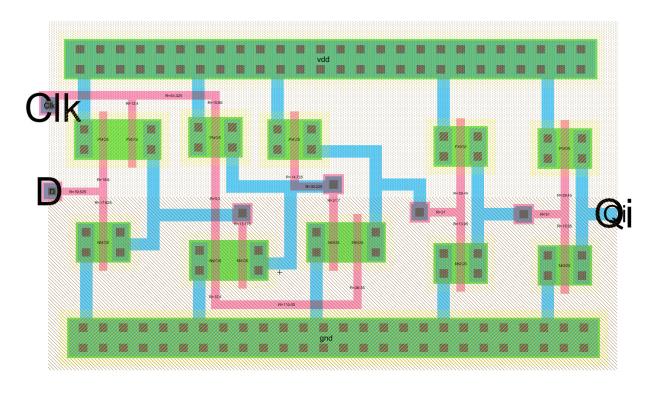

| Figure 6.10 – Schematic of 8-bit register                                     | 105 |

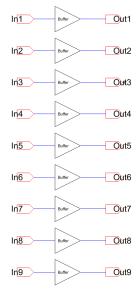

| Figure 6.11 – Output buffer                                                   | 105 |

| Figure 6.12 – Passive KD1S modulator                                          | 107 |

| Figure 6.13 – Schematic of comparator with pre-amplifier                      | 108 |

| Figure 6.14 – Verifying internal VCO frequency                                | 109 |

| Figure 6.15 – Verifying output buffer driving ability                         | 110 |

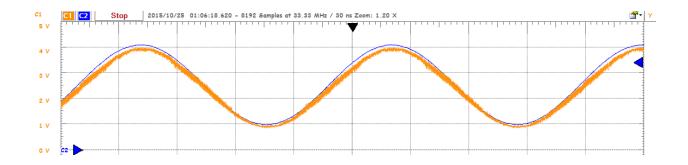

| Figure 6.16 – Input signal (blue) and filtered output (yellow)                | 111 |

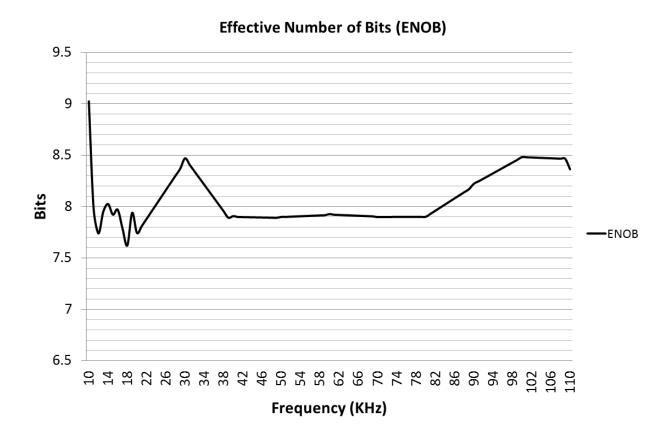

| Figure 6.17 – ENOB as function of input frequency                             | 111 |

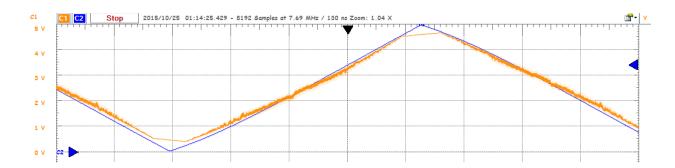

| Figure 6.18 – Input ramp signal (blue) and output (yellow)                    | 112 |

| Figure 6.19 – Input ramp signal (blue) and output (yellow) showing dead-zones | 113 |

| Figure 6.20 – Noise shaping with comb filtering                               | 11  |

# **List of Tables**

| Table 2.1 – Passive Components             | 42  |

|--------------------------------------------|-----|

| Table 2.2 –THD for each Topology           | 45  |

| Table 4.1 – Passive Component Values       | 54  |

| Table 4.2 – Summary of Measured Parameters | 73  |

| Table 5.1 Summary of Measured Parameters   | 93  |

| Table 5.3 Comparison to Other Works        | 94  |

| Table 6.1 Summary of Measured Parameters   | 114 |

# **Chapter 1 Introduction**

Analog to digital converters (ADC) are one of the most important types of electronic circuits today. They are found in any application where an analog signal needs to be converted into a digital value. Almost all quantifiable natural phenomena such as light and sound are analog in nature. However, most modern electronic components such as microcontrollers and processors require inputs in the form of digital values. The analog to digital converter bridges this divide. Due to the ubiquity of digital electronics, ADCs are found in almost all electronic circuits. There are many different topologies of ADC each with their strengths and weaknesses.

ADCs can be grouped into two broad categories, Nyquist-rate and oversampling. A Nyquist-rate ADC has the limitation that the maximum input signal frequency must be less than half the ADC's sample rate in order to prevent aliasing. Historically most ADCs have been Nyquist-rate ADCs. Topologies in this category include the flash ADC, the successive-approximation (SAR) ADC, pipeline ADCs and many others. These ADC topologies all suffer from the requirement that precision analog circuitry is needed to ensure accuracy. As semiconductor process technologies progress, it becomes increasingly difficult to fabricate precision analog components. Oversampling ADCs are not limited by Nyquist-rate sampling. The sampling rate is set higher than the maximum input frequency by some multiple. This increases the resolution through averaging. Any Nyquist-rate ADC can be run as an oversampled ADC to increase resolution at the expense of bandwidth assuming that

the analog input signal is busy [1]. However, the true benefits of oversampling become apparent when combined with noise-shaping to create the sigma-delta ( $\Sigma$ - $\Delta$ ) ADC.

The key benefit of oversampling is that an ADC can have a higher effective resolution than its nominal value. For example an 8-bit ADC can have an effective 10-bit resolution with 16X oversampling. The problem with using Nyquist-rate ADCs in this manner is that any Nyquist-rate ADC will have significant constraints on analog precision regardless of oversampling. If the concept of oversampling is extended to its most basic implementation, it becomes possible to theoretically realize any resolution with just a 1-bit ADC. There are many benefits to using a 1-bit ADC. Precision requirements are relaxed on components since there are only two states of operation and thus the ADC is inherently linear [2]. Power consumption is decreased since only a single active quantizing element is required. Integration into nano-CMOS processes is facilitated by the simplicity of the design. Combined with noise-shaping, a 1-bit oversampling ADC forms the heart of the sigma-delta ADC. Due to all these benefits,  $\Sigma$ - $\Delta$  ADCs have become the topology of choice for low-cost high resolution data converters.

Sigma-delta ADCs can be further categorized as active or passive. While all ADCs use active components, the term refers to the active integrator when applied to sigma-delta ADCs. Most  $\Sigma$ - $\Delta$  ADCs use an active amplifier configured as an integrator to perform the integration function. A passive  $\Sigma$ - $\Delta$  ADC replaces the active integrator with a capacitor. This reduces the linearity but also decreases power consumption. Usually 1st or 2nd order noise-shaping is used in passive  $\Sigma$ - $\Delta$  ADCs. It is generally not practical to realize passive  $\Sigma$ - $\Delta$  ADCs with higher order noise-shaping. As a result of their poor linearity, passive  $\Sigma$ - $\Delta$  ADCs

have not been extensively investigated and other ADC topologies, particularly SAR, have been used for low power applications. A passive  $\Sigma$ - $\Delta$  ADC is a viable alternative choice for applications where minimum power consumption is the highest priority. A novel passive  $2^{nd}$  order  $\Sigma$ - $\Delta$  has been developed that improves linearity while retaining low power consumption. This topology can be implemented in purely digital systems such as microcontrollers or FPGAs as well as integrated circuits.

## **Oversampling**

The concept of oversampling is fundamentally important to the function of sigmadelta ADCs. Simple oversampling can be applied to any data converter topology. For a given analog signal bandwidth, a minimum frequency of twice that bandwidth is required to digitize the signal without aliasing. This concept is described formally as the *Nyquist Criterion* which is mathematically given by

$$f_{sampling=2f_{MAX}} \tag{1.1}$$

Where  $f_{sampling}$  is the minimum sampling rate required to accurately digitize the analog signal without aliasing, and  $f_{MAX}$  is the bandwidth of the sampled signal. Oversampling involves running a data converter at a sampling rate that is higher than  $2f_{max}$ . For ease of signal processing and binary math operations usually this ratio is chosen to be a multiple of two. For example using a sampling rate of 32 MHz for a signal bandwidth of 1 MHz is oversampling by 16X. The required oversampling ratio (OSR) required to get n additional bits of precision is given by

$$OSR = 2^{2n} \tag{1.2}$$

Using this equation, if one desired to have 10-bit resolution from an 8-bit data converter, an OSR of 16X would be required. An important caveat to this is that this equation is valid only if the inherent linearity of the 8-bit data converter is at least equal to a 10-bit resolution. For a theoretical data converter perfect linearity is assumed. To understand why oversampling increases the resolution of an ADC, it is important to understand the concept of quantization noise.

Whenever an analog signal is sampled, there is an error between the quantized value and the actual value of the analog signal. This error as a function of time varies between -1/2 LSB and +1/2 LSB (least significant bit). The difference between the quantized value and the actual value gives rise to quantization noise. Quantization noise is white and its amplitude depends on the value of the LSB of the ADC [3]. The derivation of the frequency content of quantization noise starts by treating the quantization error,  $Q_e$ , as a random variable. The probability density function of this variable is plotted in Fig. 1.1a. The quantization error noise power is given by,

$$P_{Qe} = \int_{-\frac{1}{2}LSB}^{+\frac{1}{2}LSB} \rho * (Q_e) * dQ_e = \frac{V_{LSB}^2}{12}$$

(1.3)

The RMS quantization noise voltage is the square root of the quantization noise power and is given by,

$$V_{Qe,RMS} = \frac{V_{LSB}}{\sqrt{12}} \tag{1.4}$$

In order to get the spectral density function, the quantization noise power is set equal to the following integral,

$$\frac{V_{LSB}^2}{12} = 2 * \int_0^{\frac{fs}{2}} V_{Qe}^2(f) * df$$

(1.5)

The integral is multiplied by 2 to account for the power contributed by the negative frequencies of the spectrum. Solving this equation results in

$$V_{qe}(f) = \frac{V_{LSB}}{\sqrt{12*f_S}} \tag{1.6}$$

The key result from this equation is that the amplitude of the quantization noise is equal to  $\frac{V_{LSB}}{\sqrt{12*fs}}$  and is equally distributed to the Nyquist frequency of  $f_n=\frac{fs}{2}$ . This is illustrated in Fig. 1.1b.

Figure 1.1 – (a) Probability density function and (b) quantization noise spectral density.

The power of the RMS quantization noise,  $\frac{V_{LSB}}{\sqrt{12}}$ , depends on the amplitude of  $V_{LSB}$  which is constant for a given data converter resolution. Stated another way, the area under the function in Fig 1.1b is always the same regardless of the bandwidth. However, as the Nyquist frequency is increased, the amplitude of the quantization noise is proportionally reduced. This is illustrated in Fig. 1.2. It is important to note that in order for the integral to give the correct answer, a factor of two must be used to account for the negative frequencies as in Eq. 1.5. However intuitively it is clear that doubling the sampling frequency halves the amplitude of the quantization noise voltage. Clearly increasing the

sampling frequency alone does not reduce the quantization noise of an ADC. The spectrum also needs to be bandlimited with a filter in order to actually reduce the quantization noise.

Figure 1.2 – Effect of increasing sampling frequency on quantization noise spectral density.

After oversampling, the digital output signal needs to be filtered to bring the bandwidth back down to the original desired Nyquist rate. An example for 2X oversampling is shown in Fig. 1.3. After the signal is oversampled by 2X, an ideal low-pass filter is used to halve the quantization noise. In reality, this extent of noise reduction is not possible since an ideal low-pass filter is unrealizable. High-order analog filters are also difficult to realize,

therefore in practical data converters usually some type of high-order digital filter is used.

The quantization noise directly relates to the resolution of the data converter.

Figure 1.3 - Bandlimiting an oversampled signal.

The resolution of a data-converter is calculated from the signal-to-noise ratio (SNR). This is the effective resolution and not the nominal resolution. An ADC can be nominally described as an n-bit ADC if it outputs an n-bit word. However, this doesn't mean that the ADC can actually resolve a signal to that resolution. The term for the actual resolution of a data converter is effective number of bits (ENOB). The ideal SNR is given by

$$SNR_{ideal} = 20 * \log \frac{V_p/\sqrt{2}}{V_{LSB}/\sqrt{12}} = 20 * \log \frac{2^N\sqrt{12}}{2\sqrt{2}} = (6.02N + 1.76)dB$$

(1.7)

Where N is the number of bits and Vp is the maximum amplitude that can be applied to the ADC. Rewritten from Eq. 1.7, the effective number of bits is given by

$$N_{eff} = \frac{SNR - 1.76}{6.02} \tag{1.8}$$

The SNR can be either an ideal SNR, as is the case when assuming quantization noise only, or a measured SNR from actual test equipment. Generally, measured SNR can be quite lower than the theoretical ideal SNR.

Oversampling and band-limiting the signal increases SNR and thus the ENOB. For simple oversampling, Eq. 1.6 is modified to

$$V_{qe}(f) = \frac{V_{LSB}}{\sqrt{K*12*2*f_n}}$$

(1.9)

where K is the oversampling ratio and  $f_n$  is the Nyquist frequency or desired bandwidth of the input signal. The variable for sampling rate in Eq. 1.6 has been replaced with  $2 * f_n$  for clarity since the actual sampling rate is OSR-times higher.

## **Noise-shaping**

The problem with simple oversampling is that a very high oversampling ratio is required to get a significant increase in resolution. For example, a 1-bit ADC would need an OSR of  $2^{16}$  (65536) just to have an 8-bit resolution. For a 1 MHz bandwidth this would

require a sampling rate of 65 GHz, which is unfeasible. Instead, sigma-delta ADCs must combine noise-shaping with oversampling to get high resolutions. Noise-shaping is simply the use of a filter to shift quantization noise to frequencies outside the signal bandwidth of interest. This principle allows a sigma-delta ADC to achieve much higher resolution with a given OSR than otherwise possible.

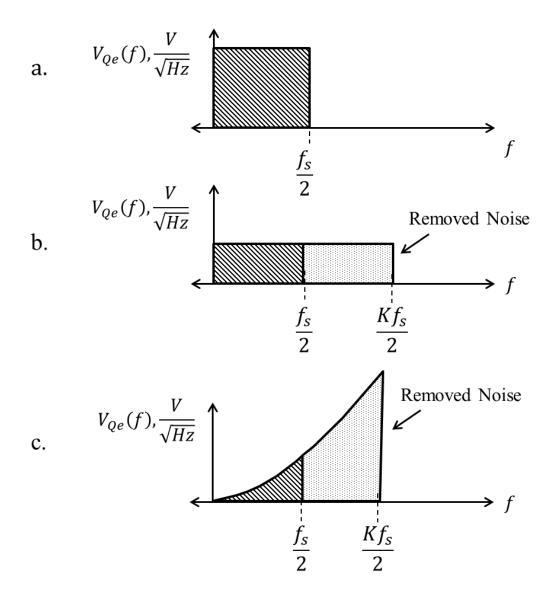

The RMS quantization noise  $V_{Qe,RMS}$  remains the same for a given sampling rate. However, with noise-shaping, the spectral density function shifts to higher frequencies. This is illustrated in Fig. 1.4c. For comparison, Fig 1.4a illustrates Nyquist rate sampling and Fig 1.4b illustrates simple oversampling. In all three cases, the total areas under the spectral density functions are the same, but the quantization noise in the bandwidth of interest in Figs 1.4b and 1.4c is reduced. In this case, the noise-shaping shown has a high-pass characteristic. The transfer function of this type of filter differentiates the quantization noise causing most of the energy to be concentrated at higher frequencies.

Figure 1.4 – Comparison of quantization noise for (a) Nyquist rate, (b) simple oversampling and (c) noise-shaping.

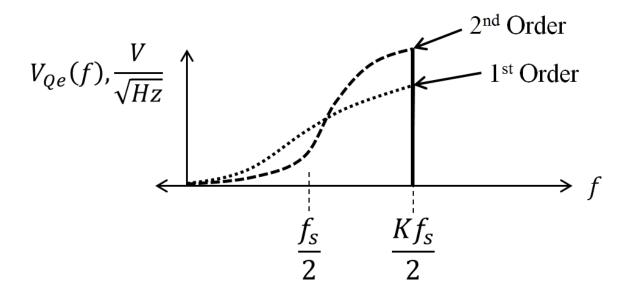

The shape of the spectral density curve is determined by the order of the noise-shaping. The simplest case is that of 1<sup>st</sup>-order noise-shaping which displays a 10dB per decade rise in the noise voltage amplitude until the oversampled Nyquist frequency,  $Kf_s/2$ . For passive sigma delta ADCs, noise-shaping is generally limited to 2<sup>nd</sup>-order. For active sigma-delta topologies stability issues come into play after 2<sup>nd</sup>-order, although 4<sup>th</sup> order

designs and beyond are now common [5]. A comparison of 1<sup>st</sup> and 2<sup>nd</sup> order noise-shaping is shown in Fig. 1.5. The quantization noise in the region of interest is lower for the 2<sup>nd</sup> order curve; however the trade-off is higher quantization noise at higher frequencies. Since all frequencies beyond the Nyquist frequency are filtered out, this noise does not matter.

Figure 1.5 – Comparison of 1st and 2nd order noise-shaping.

## Sigma Delta Principles

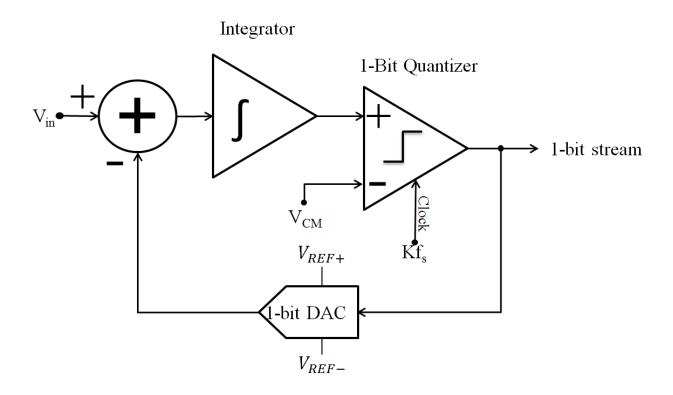

Sigma-delta ADCs are pervasive in almost all high resolution, low to medium speed data conversion applications. Despite this, many individuals find it difficult to understand the basic operation of sigma-delta ADCs. It is beneficial to examine the qualitative operation of a sigma-delta modulator before delving into detailed theory. A system-level block diagram of a sigma-delta modulator is shown in Fig. 1.6. There are four basic components to this diagram. These are a summing junction, an integrator, a 1-bit quantizer, and a 1-bit digital-to-analog converter (DAC). These components form a classical feedback

system, although there are additional caveats to treating a sigma-delta modulator as a linear system due to the fact that the quantizer and DAC are fundamentally nonlinear components [6]. The function of the summing block is to create an error signal, which is the difference between the input and output voltages. The integrator then sums these differences together. The 1-bit quantizer compares the integral of the error signal with a fixed reference voltage. The output of the quantizer is a "1" if the integral of the error signal is larger than the reference voltage. Otherwise the output is a "0". This bit-stream is a digital representation of the analog input. Understanding why this is a valid representation requires following an analog input signal through each block in the system.

Figure 1.6 – System level block diagram.

If a static analog signal (DC) is applied to the input of the sigma-delta modulator in Fig. 1.6, after a certain period of time, the average value of the bit-stream will represent the

value of the analog input. Before proceeding with how this occurs, some constraints for the system must be defined. The system has a maximum full scale input range ( $V_{REF+} - V_{REF-}$ ). In a practical circuit these are usually assumed to be the power supply rail voltage and ground. The common-mode voltage  $V_{CM}$  is generally set to be half of the full scale input range. For example, a circuit with a power supply voltage of 5V would have a 2.5V common-mode voltage. The signal swing for all components in the system is between 0V and 5V.

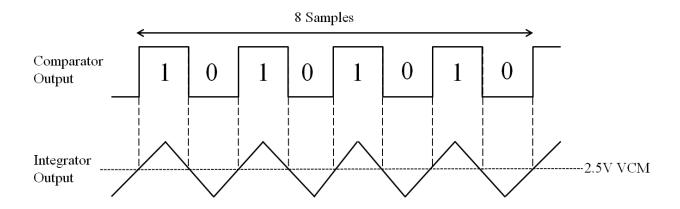

The seemingly random output of the sigma-delta modulator makes time domain analysis difficult. However if the data is averaged, then a meaningful result can be obtained. If an input of 2.5V is applied to the system in Fig. 1.6 with a 5V  $V_{REF+}$  and a 0V  $V_{REF-}$ , then the output of the sigma-delta modulator will have an equal amount of zeros and ones on average. This output waveform is shown in Fig 1.7. Each time the integrator output crosses 2.5V with a positive or negative slope, the comparator outputs either a one or zero respectively.

Figure 1.7 – Comparator and integrator outputs.

If 8 samples are averaged from the modulator output, then the average value is  $\frac{4}{8} = 0.5$ . Multiplying the average value by the full scale input value of 5 V does indeed result in the input voltage of 2.5 V. Had the input voltage been higher than 2.5 V, then there would be a correspondingly higher average value. Had the input voltage been lower, then there would be a lower average value. Simply stated, the average value of the output represents the input value. The resolution of the ADC can be increased by increasing the number of samples. This is simple averaging and for N-bits of resolution,  $2^N$  samples are required. The example in Fig. 1.7 has 3 bits of resolution. Obviously the number of samples becomes prohibitive for high resolutions because this example does not take noise-shaping into account. It is not productive to examine noise-shaping in the time domain and a frequency domain model is required.

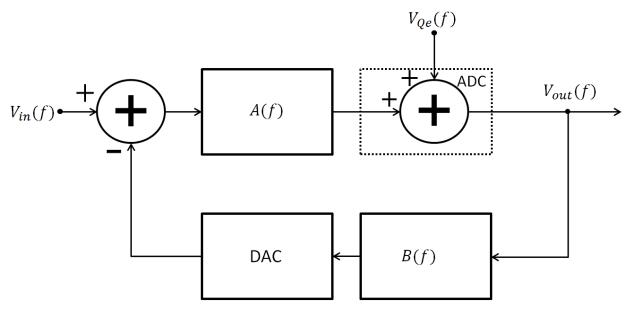

The sigma-delta modulator is in a broader category known as feedback modulators [7]. A block diagram of a feedback modulator is shown in Fig. 1.8. The summing junction on the left is where the feedback signal is subtracted from the input in order to create the error signal. The error signal is fed into an analog filter, A(f), before going into the next stage, an ADC. The ADC is fundamentally a nonlinear device but in order to use classical linear systems theory, it is instead modeled as a summing junction where the quantization noise is added to the input signal. The next stage is a digital filter, B(f), which filters the digital output before feeding it into the DAC which converts the signal back to analog.

Figure 1.8 - Block diagram of feedback modulator.

The sigma-delta topology simplifies this general feedback modulator diagram by setting B(f) to one. The ADC has a 1-bit resolution and is usually either a comparator or a D flip-flop (DFF). The 1-bit DAC is either an inverter or the complementary output from the ADC. With these simplifications the output can be given in terms of the input and quantization error as

$$v_{out}(f) = \frac{A(f)}{1 + A(f) * 1} * v_{in}(f) + \frac{1}{1 + A(f) * B(f)} * V_{Qe}(f)$$

(1.10)

The signal transfer function (STF) is the term multiplying  $v_{in}(f)$  and is written alone as

$$STF = \frac{A(f)}{1 + A(f) * 1}$$

(1.11)

The noise transfer function (NTF) is the term multiplying  $V_{Qe}(f)$  and is written alone as

$$NTF = \frac{1}{1 + A(f) * B(f)} \tag{1.12}$$

The forward path, A(f), is an integrator with a low-pass filter characteristic. The gain in the passband of the filter is large which results in an STF of nearly unity. Conversely, the NTF displays a high-pass characteristic and ideally approaches zero in the same region. This is how the quantization noise is reduced in the bandwidth of interest.

# **Chapter 2 Passive Sigma-Delta Modulators**

## **Transfer Function Derivations**

In order to approach the theoretical ideal performance for a sigma-delta modulator, an active integrator is typically employed for the integration function in the forward path. This uses active electronic amplifiers which generally have a quiescent current draw that is constant. The other components in a sigma-delta ADC only draw current when actively switching between high and low states. One way of reducing the power consumption of a sigma-delta modulator is to reduce the clock frequency. However this does not reduce the power consumption of the active integrator portion of the modulator and consequently the active integrator becomes responsible for a significant percentage of the total power consumption. Replacing the active integrator with a passive version can eliminate this portion of the power consumption at the expense of resolution. To examine why a passive integrator has reduced resolution requires a detailed analysis of a passive sigma-delta modulator.

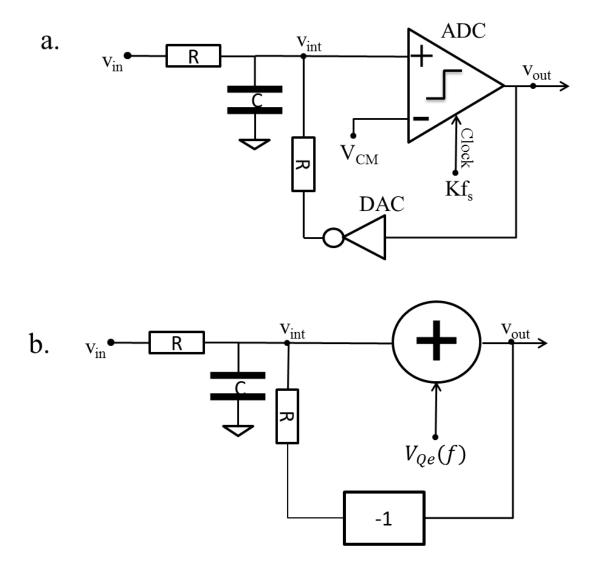

The simplest possible version of a sigma-delta modulator using ideal components is shown in Fig. 2.1A. The one bit ADC is a comparator and the one bit DAC is an inverter. The values of the resistors are the same in order to keep the gain of the circuit at unity. This schematic can be redrawn as the block diagram shown in Fig. 2.1B. The ADC is replaced with a summing junction where quantization noise is added. The DAC is replaced with a multiply by -1. The output of the modulator is given by

$$V_{oe}(f) + v_{int}(f) = v_{out}(f)$$

(2.1)

Where  $v_{int}$  is the voltage at the capacitor node. Next, nodal analysis can be used to rewrite  $v_{int}$  in terms of the currents flowing into the node. There are two currents flowing into this node, the current from the input and the feedback current. The feedback current has a negative polarity due to the inverter.

Figure 2.1 – Circuit (a) and block diagram and (b) schematic of 1st order passive sigma-delta modulator.

The sum of these two currents is given by,

$$i_{int} = \frac{v_{in} - v_{int}}{R} + \frac{-v_{out} - v_{int}}{R} \tag{2.2}$$

This current is then multiplied by the impedance of the capacitor to give a voltage,

$$v_{int} = \left(\frac{v_{in} - v_{int}}{R} + \frac{-v_{out} - v_{int}}{R}\right) * \frac{1}{j\omega C}$$

(2.3)

Substituting this into Eq. 2.1 results in

$$V_{Qe}(f) + \left(\frac{v_{in} - v_{int}}{R} + \frac{-v_{out} - v_{int}}{R}\right) * \frac{1}{j\omega C} = v_{out}(f)$$

(2.4)

The transfer function can be found by rearranging the terms

$$v_{in} - v_{out} - 2v_{int} + V_{oe} * J\omega RC = j\omega RC * v_{out}$$

(2.5)

$$v_{in} - 2v_{int} + V_{Qe} * J\omega RC = v_{out}(j\omega RC + 1)$$

(2.6)

This then yields,

$$v_{out} = \frac{1}{1 + j\omega_{RC}} v_{in} + \frac{j\omega_{RC}}{1 + j\omega_{RC}} V_{Qe} + \frac{-2*v_{int}}{1 + j\omega_{RC}}$$

(2.6)

Breaking down this equation gives the STF, NTF, and an extra noise/distortion term.

$$STF = \frac{1}{1 + j\omega RC} \tag{2.7}$$

$$NTF = \frac{j\omega RC}{1 + j\omega RC} \tag{2.8}$$

$$Distortion = \frac{-2*v_{int}}{1+j\omega RC}$$

(2.9)

It is clear from these equations that the STF displays a  $1^{\rm st}$  order low-pass filtering characteristic and the NTF displays a  $2^{\rm nd}$  order high-pass filtering characteristic. For a continuous time sigma-delta modulator there is an inherent anti-aliasing filter built in. The distortion term is the result of the voltage varying at the  $v_{int}$  node. With an active integrator this term is negligible because the amplifier attempts to keep the node voltage constant. The key limit to the resolution of a passive modulator is the distortion term. Deriving an equation for the resolution of a passive sigma delta modulator is difficult with the distortion term included. Instead, an equation for an ideal active sigma delta modulator is used with a constraint. The ideal SNR of a  $1^{\rm st}$  order sigma-delta modulator is given by

$$SNR_{ideal} = 20 \log \frac{V_p / \sqrt{2}}{V_{noise,RMS}} = 6.02N + 1.76 - 20 \log \frac{2\pi RC f_s}{\sqrt{12}} + 20 \log K^{3/2}$$

(2.10)

The derivation for this equation is found in [7]. For a passive modulator the time constant for RC needs to be significantly larger than the period of the sampling clock in order for this equation to be valid. If RC is set to  $4.4/T_s$ , then Eq. 2.10 becomes

$$SNR_{ideal} = 6.02N + 1.76 - 18.06 + 30\log K \tag{2.11}$$

Rewriting this equation in terms of the number of bits of increased resolution yields

$$N_{inc} = \frac{30\log K - 18.06}{6.02} \tag{2.12}$$

$$SNR_{ideal} = 6.02(N + N_{inc}) + 1.76$$

(2.13)

For every doubling of K beyond 4 there is a 1.5 bit increase in resolution which is 0.5 bits greater than with simple oversampling. In order to increase the ratio of resolution increase to oversampling, the order of the noise shaping should be increased to  $2^{nd}$  order.

A conventional passive 2<sup>nd</sup>-order sigma-delta modulator requires two feedback paths. The schematic of this circuit is shown in Fig. 2.2. This circuit has two feedback paths and does not have a set common mode voltage. Instead, the circuit acts to drive both capacitor nodes to the same value. A detailed description of this topology is found in [8].

Figure 2.2 – Schematic of 2nd order passive sigma-delta modulator.

The output equation of this circuit in terms of the input signal and quantization noise is given by,

$$v_{out}^{2} = \frac{1}{1 + (\omega RC)^{2}} \cdot v_{in}^{2} + \frac{(\omega RC)^{2}}{1 + (\omega RC)^{2}} \cdot \frac{v_{Qe}^{2}}{2} + \frac{2v_{1} + v_{2}}{1 + (\omega RC)^{2}}$$

(2.14)

The output is squared because of the way this  $2^{nd}$  order equation was solved. This form also preserves the standard form for the transfer functions which allows direct comparisons to be made to the  $1^{st}$ -order modulator. Breaking the equation down, the STF, NTF and distortion terms are given by

$$STF = \frac{1}{1 + (\omega RC)^2} \tag{2.15}$$

$$NTF = \frac{1}{2} * \frac{(\omega RC)^2}{1 + (\omega RC)^2}$$

(2.16)

$$Distortion = \frac{2v_1 + v_2}{1 + (\omega RC)^2} \tag{2.17}$$

Each transfer function is similar to that of the  $1^{st}$ -order sigma-delta modulator except that they are  $2^{nd}$ -order. A striking difference though is that the quantization noise power is cut in half. The ideal SNR can be solved as

$$SNR_{ideal} = 6.02N + 1.76 - 15.13 + 30 \log K$$

(2.18)

This equation verifies that the noise power is halved (3dB reduction) over the 1<sup>st</sup>-order modulator. In practice, a 2<sup>nd</sup>-order modulator offers a much higher performance increase than apparent from the ideal SNR equations. The reason for this is because of limitations and assumptions used in the linear model. Actual circuit simulations and measurements can show significantly different results although the general trends are still valid. This will become apparent in later chapters.

Performance can be significantly improved by using a modified passive  $2^{nd}$  order topology. This design simply adds an additional RC loop filter to the passive  $1^{st}$  order

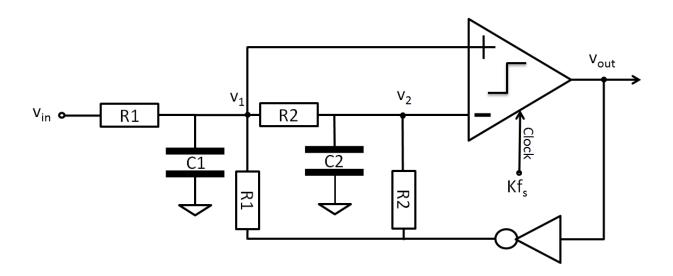

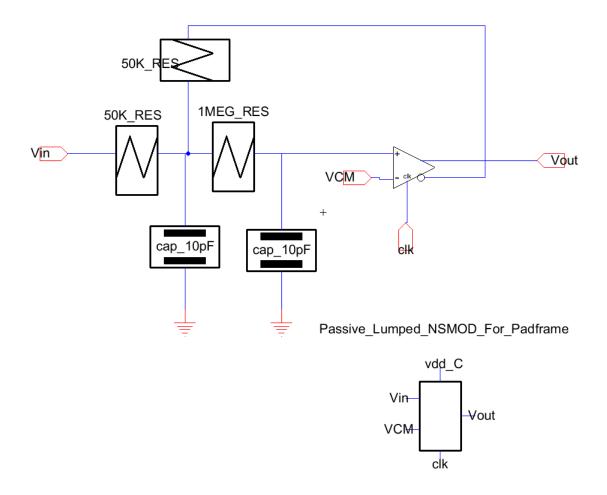

circuit. The schematic of the modified passive 2<sup>nd</sup> order circuit is shown in Fig. 2.3. On the surface, a big benefit of this is that there is just one feedback path and only two resistors need to be reasonably matched. Resistors R1 need to be matched but R2 can be a different value and not affect the gain of the circuit. Likewise, C1 and C2 do not need to be matched either. This allows a wide range of values that can be used in the circuit. Analyzing the transfer function and simulations show that performance is maximized when certain constraints are applied to component values.

Figure 2.3 – Schematic of modified 2nd order passive sigma-delta modulator.

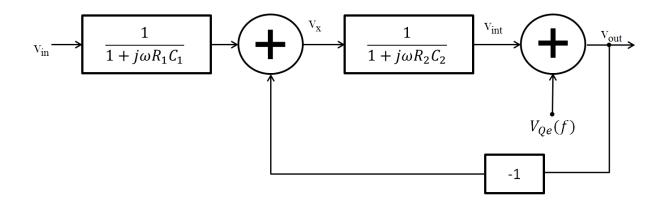

Due to the high number of variables, it is difficult to derive the transfer function of the modified 2<sup>nd</sup> order sigma-delta modulator. First the circuit needs to be converted into a block diagram as in Fig. 2.4. The RC filters have been replaced with their equivalent frequency domain transfer function. Although there is a system level diagram it can be convenient to use both schematics to derive the transfer function.

Figure 2.4 – Block diagram of modified 2<sup>nd</sup> order passive sigma-delta modulator.

Using nodal analysis the current flowing out of the summing junction at the  $\emph{v}_\emph{x}$  node is

$$\frac{v_{in} - v_x}{R_1} + \frac{-v_{out} - v_x}{R_1} = \frac{v_x}{1/j\omega C}$$

(2.19)

This can be rearranged as

$$\frac{v_{in}-2v_{x}-v_{out}}{R1} = v_{x} * j\omega C \tag{2.20}$$

Solving for  $v_x$

$$v_{x} = \frac{v_{in} - v_{out}}{R_{1} * j\omega C_{1} + 2} \tag{2.21}$$

The output voltage,  $v_{out}$  can be written in terms of

$$v_{out} = V_{Qe} + v_x * \frac{1}{1 + j\omega R_2 C_2}$$

(2.22)

Substituting  $v_{int1}$  results in

$$v_{out} = V_{Qe} + \left(\frac{v_{in} - v_{out}}{R_1 * i\omega C_1 + 2}\right) * \frac{1}{1 + i\omega R_2 C_2}$$

(2.23)

These equations can be solved using Mathematica to give  $v_{out}$  in terms of  $v_{in}$ ,  $V_{Qe}$ , and  $v_{int}$

$$v_{out} = \frac{1 + sR_2C_2}{1 + sR_2C_2 + sR_1C_1} \cdot v_{in} + \frac{s(sR_1C_1R_2C_2 + R_1C_1)}{1 + sR_1C_1 + s^2R_1C_1R_2C_2} \cdot V_{Qe} + \frac{1}{1 + sR_1C_1 + (1 + sR_2C_2)} \cdot v_{int}$$

(2.24)

The STF, NTF and DTF are

$$STF = \frac{1 + sR_2C_2}{1 + sR_2C_2 + sR_1C_1} \tag{2.25}$$

$$NTF = \frac{s(sR_1C_1R_2C_2 + R_1C_1)}{1 + sR_1C_1 + s^2R_1C_1R_2C_2}$$

(2.26)

$$DTF = \frac{1}{1 + sR_1C_1 + (1 + sR_2C_2)}$$

(2.27)

From examining the transfer functions a few things become apparent. The signal transfer function is 1<sup>st</sup> order meaning that input signals are filtered by a simple 10 dB per decade low-pass filter. The noise transfer function is indeed 2<sup>nd</sup> order which allows this topology to be classified as a 2<sup>nd</sup> order sigma delta modulator [9]. The distortion transfer function is also 1<sup>st</sup> order and is not multiplied by two like the first order and conventional second order topologies. This means that distortion should nominally be halved with the modified second order topology. The fact that there are 2 different RC filters allows a

significant range of choices. A design methodology needs to be developed to select optimal values for the passive components.

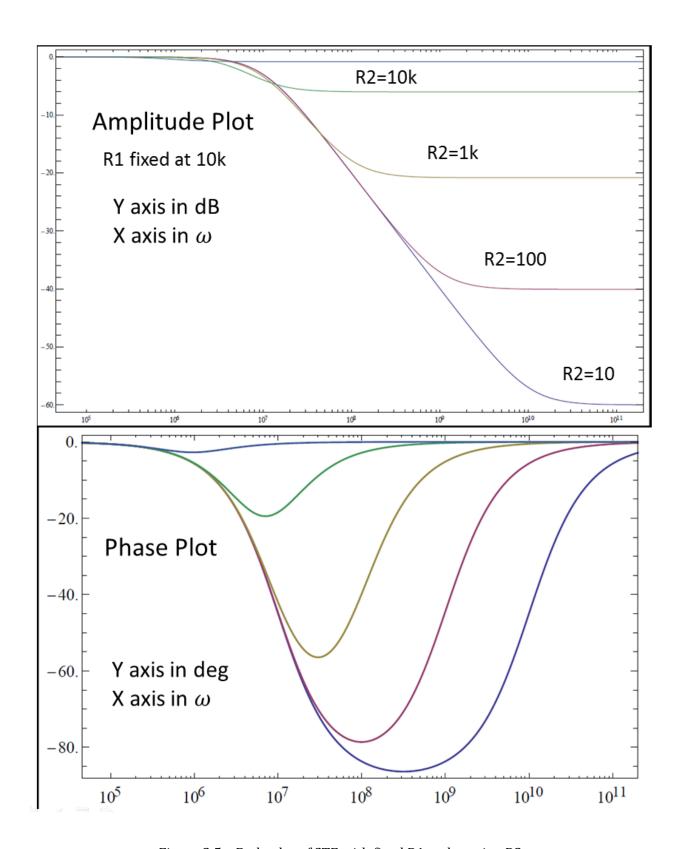

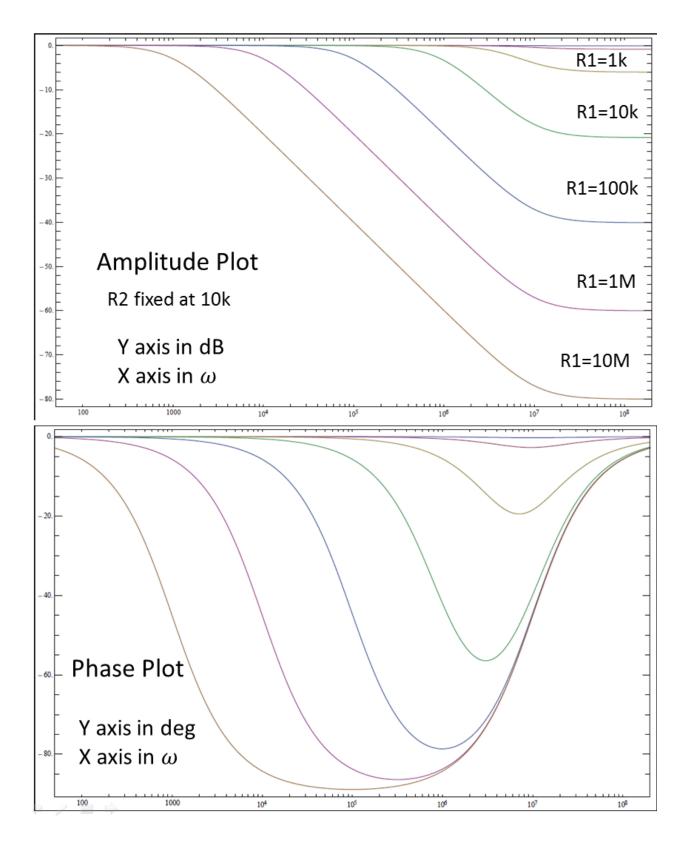

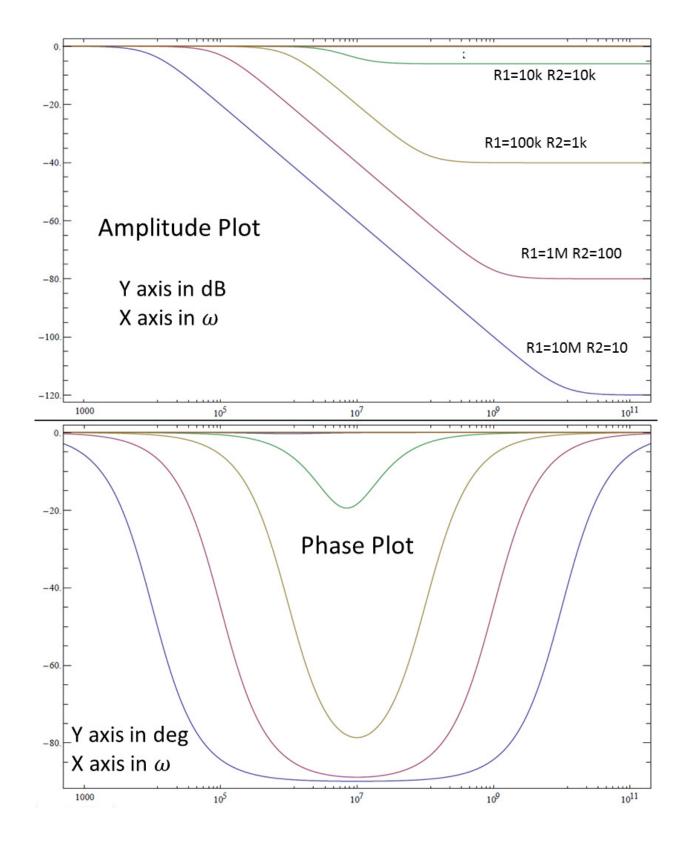

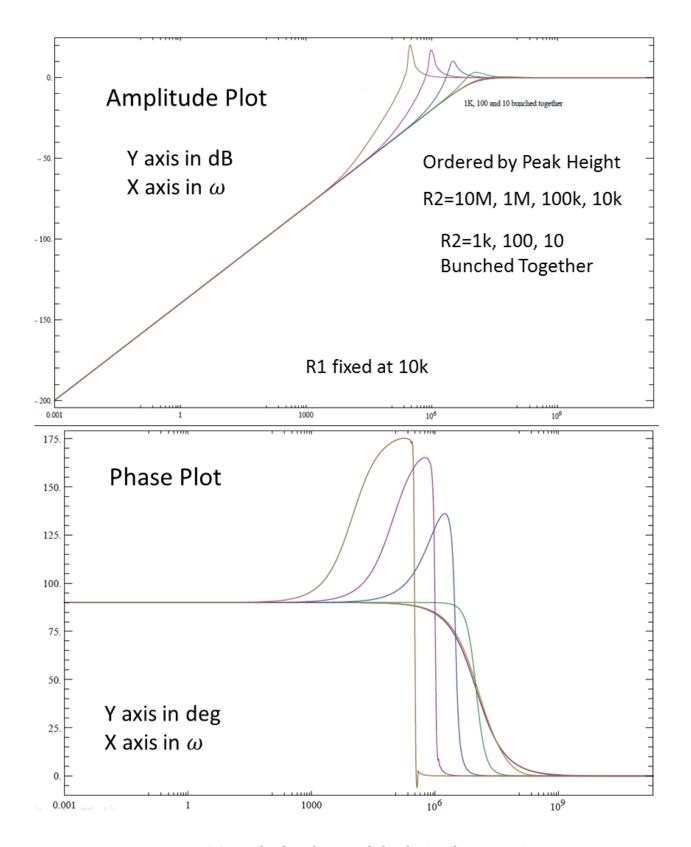

This can be done by plotting all the transfer functions and examining how they change with different component values. For example, R1 can be at a fixed value and R2 can be varied and the transfer function examined. This was done in Mathematica and the Bode plot of the signal transfer function is shown in Fig 2.5. The transfer function exhibits a 1<sup>st</sup> order roll off until reaching an amplitude value where it flattens out. For each decade decrease in R2 value, the amplitude where the curve flattens out is reduced by 20 dB. The corner frequency for the STF is not affected at all by varying R2. If R2 remains fixed and R1 is varied the resulting bode plot is as shown in Fig. 2.6. The corner frequency does indeed change when R1 is varied. The amplitude then flattens out at a certain frequency, indicating an all-pass characteristic. The phase plot confirms that there is indeed a form of all-pass behavior. If R1 and R2 are varied in opposite directions, then the amplitude and phase plots shown in Fig. 2.7 are the result. Again, the all-pass characteristic is visible. The STF plots will need to be taken into account when designing a modulator for a particular input signal range but they don't reveal much about the actual performance of this topology. For that, the NTF needs to be examined.

Figure 2.5 – Bode plot of STF with fixed R1 and varying R2.

Figure 2.6 – Bode plot of STF with fixed R2 and varying R1.

Figure 2.7 – Bode plot of STF with R1 and R2 varying in opposite directions.

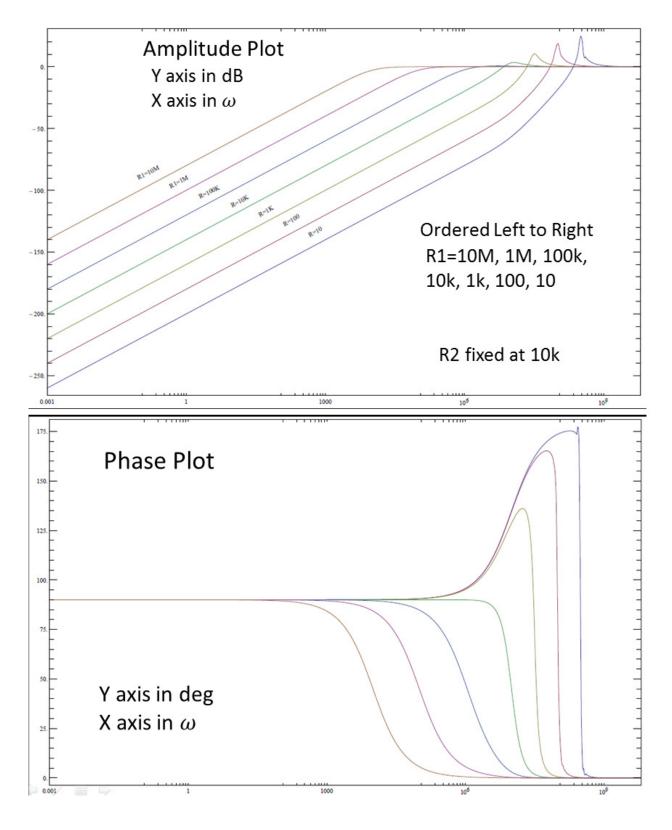

The next three figures, Fig. 2.8, Fig. 2.9 and Fig, 2.10 all illustrate what occurs to the NTF as the resistor values are varied. The method of judging these plots is by examining the amount of noise at the lower frequencies which are in the signal bandwidth of interest. In Fig. 2.8, R1 is held constant while R2 is varied. From this plot, it is apparent that there is some sort of resonant behavior occurring and that perhaps it is best to have the value of R2 maximized. However, the next plot in Fig. 2.9 seems to indicate that R1 should also be minimized. Finally, examining Fig. 2.10, it is apparent that the value of R1 should be as low as possible and the value of R2 should be as high as possible, given the constraint of desired signal bandwidth. The actual total noise power throughout the bandwidth is the same for all values. However, it appears that noise is shifted to a resonant peak which results in much lower quantization noise at lower frequencies of interest. This shifting of noise to a resonant peak is the mechanism by which this sigma-delta modulator topology achieves its higher resolution compared to standard passive designs.

Figure 2.8 – Bode plot of NTF with fixed R1 and varying R2.

Figure 2.9 – Bode plot of NTF with fixed R2 and varying R1.

Figure 2.10 – Bode plot of NTF with R1 and R2 varying in opposite directions.

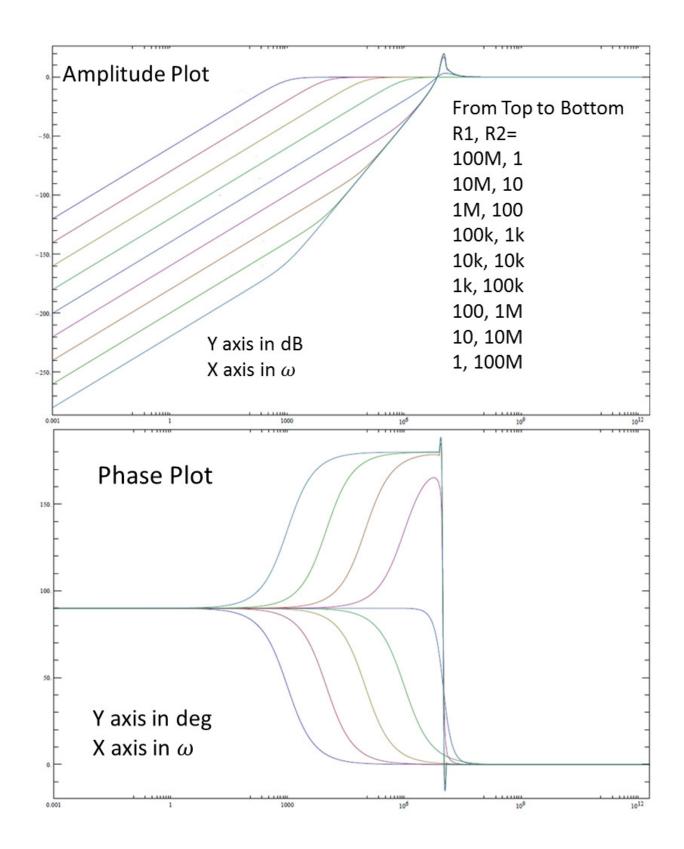

Finally, the bode plots of the remaining term in the output equation, the distortion term, needs to be examined. The next three figures, Fig 2.11, 2.12, and 2.13 show the effect of varying R1 and R2 on the distortion term bode plot. The overall behavior is that the distortion term rolls off with a 1<sup>st</sup>-order characteristic until a particular frequency where it rolls off with a 2<sup>nd</sup>-order characteristic. For some combinations, resonance causes a 2<sup>nd</sup> order roll-off without an initial 1<sup>st</sup> order roll-off. In Fig. 2.11, it is clear that increasing the value of R2 while keeping R1 fixed, causes an increase in the "Q" of the resonant peak while also shifting the resonant frequency lower. This is verified by examining the phase as well, with the sharpness in the transition to full phase inversion. In Fig 2.12, where R1 is varied and R2 is fixed, the same effect occurs for decreasing values of R1. The only difference is that the resonant frequency increases.

The condition in Fig. 2.11 is not desirable since it means that distortion increases within the signal bandwidth of interest. This appears to be contradictory to the conclusion drawn from examining the NTF – that R2 should be as high as possible. However, Fig 2.13 shows that indeed this conclusion is correct. When R1 has a low value and R2 has a high value, the distortion transfer function rolls off earlier with a 1st order characteristic and does not exhibit any resonance. The phase plot also confirms this, with a wide region of constant 90 degree phase shift.

Figure 2.11 – Bode plot of DTF with R1 fixed and R2 varying.

Figure 2.12 – Bode plot of DTF with R2 fixed and R1 varying.

Figure 2.13 – Bode plot of DTF with R1 and R2 varying in opposite directions.

## **Simulated Comparison**

Circuit level simulations are needed to verify that the transfer functions are indeed valid. In order to remove the effects of nonlinearities in circuit elements, ideal circuit components were used to isolate topology related effects. The ideal components used are those found in [cite] and are made up of SPICE switches, behavioral elements, and dependent sources. The components allow for ideal component level simulation in order to verify topological aspects of circuits without the nonlinearities of real components. The schematic used for simulation is displayed in Fig. 2.12.

Figure 2.14 — Simulation testbed for 1st and 2nd order passive modulators.

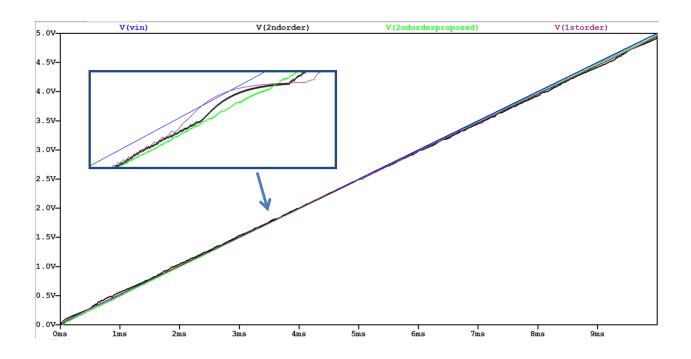

Each topology described in this chapter is compared side by side in this simulation. A 10 ms ramp signal is applied to each input and the output is filtered to create a transfer curve. The VDD is 5V, the VCM is 2.5V and the clock frequency is 10 MHz. Since ideal components are used any value can be used for VDD and VCM. These values were selected because they are commonly used for CMOS logic levels. All passive component values were adjusted such that each modulator had the same corner frequency of 16 KHz to allow for fair comparison.

The filtered outputs and their resulting transfer curves are shown in Fig. 2.13. At first glance, all the curves seem very close to each other and almost identical. However, upon closer inspection it is apparent that the "noise" that remains after filtering is different. In the left inset, it is clear that the proposed  $2^{nd}$  order topology has less noise than either the  $1^{st}$  or  $2^{nd}$  order designs. The inset on the right shows the biggest disadvantage of the  $1^{st}$  order modulator which is the presence of dead-zones. The output stops responding and a charging RC characteristic can be seen for the  $1^{st}$  order modulator.

When each design is compared with the same corner frequency, the proposed 2<sup>nd</sup> order modulator exhibits the best performance but only by a small margin. However, each design differs by the number of components and the space occupied by these components in a practical implementation. For a discrete board level implementation of a sigma-delta modulator (rare in practice) the board space and component cost considerations make the 1<sup>st</sup> order modulator attractive. The proposed 2<sup>nd</sup> order modulator offers an increase in performance with only two additional components. The traditional 2<sup>nd</sup> order design requires four which is not a good solution for board level implementations.

Figure 2.15 – Transfer curves and zoomed insets.

For IC implementations, layout area considerations are different. For example, resistors affect the layout area based on their value rather than quantity. It is in this area, where the proposed  $2^{nd}$  order design offers the greatest benefit. The passive component count for each design is shown in table 2.1. The layout areas for the  $1^{st}$  order and proposed  $2^{nd}$  order topologies are about the same. This is because the area for a  $50~k\Omega$  resistor is quite small compared to a  $1~M\Omega$  one. However, the proposed  $2^{nd}$  order design requires an additional 10~pF capacitor which has a layout area that's comparable to a  $1~M\Omega$  resistor. Therefore in the proposed  $2^{nd}$  order design, a  $1~M\Omega$  resistor is traded for a 10~pF capacitor which results in roughly the same area. The traditional  $2^{nd}$  order design has quite a large layout area requiring four  $1~M\Omega$  resistors and two 10~pF capacitors.

| Topology                       | Resistors |                                                | Capacit | tors  | Comments                            |

|--------------------------------|-----------|------------------------------------------------|---------|-------|-------------------------------------|

| 1 <sup>st</sup> Order          | 2         | 1 ΜΩ                                           | 1       | 10 pF | About equal to                      |

|                                |           |                                                |         |       | proposed 2 <sup>nd</sup> order      |

| Proposed 2 <sup>nd</sup> Order | 1         | 1 ΜΩ                                           | 2       | 10 pF | $50 \text{ k}\Omega$ layout area is |

|                                | 2         | 50 kΩ                                          |         |       | small compared to                   |

|                                |           | <u> </u>                                       |         |       | 1 ΜΩ                                |

| 2 <sup>nd</sup> Order          | 4         | 1 ΜΩ                                           | 2       | 10 pF | Largest passive                     |

|                                |           | <u>.                                      </u> |         |       | component area                      |

Table 2.1 – Passive Components

Taking layout area into consideration, an additional simulation was performed which reduced the value of the resistors in the traditional  $2^{nd}$  order modulator to  $250~k\Omega$  or one quarter their value used in the simulation in Fig. 2.13. The results in Fig. 2.14 show how performance differs between the modulators when adjusting for layout area considerations. Both the  $1^{st}$  and traditional  $2^{nd}$  order modulators show dead-zones in the inset in Fig. 2.14. Overall, when adjusted for area, the proposed  $2^{nd}$  order modulator offers the best performance.

Figure 2.16 – Transfer curves for equal area and zoomed inset with dead zones.

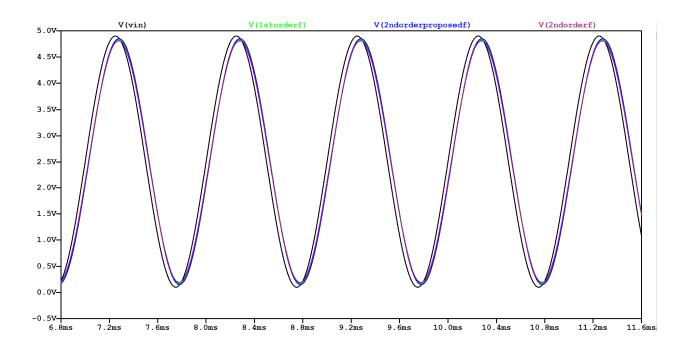

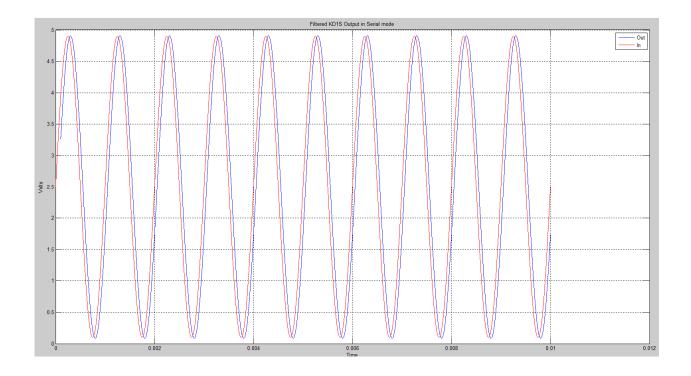

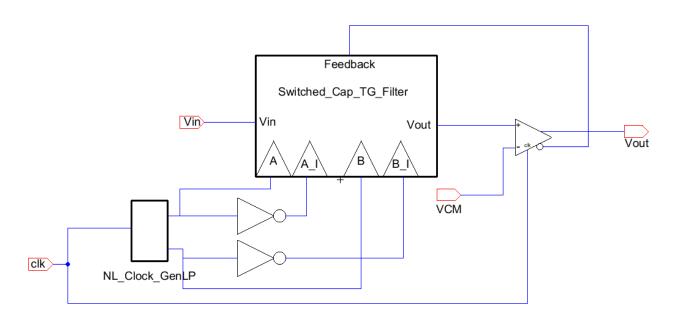

A transient analysis was performed in LTSpice with 20 cycles of a 1 KHz sine wave and the resulting FFT was used to compare the AC performance between modulators. These waveforms are shown in Fig. 2.14. The FFT of each modulator's filtered output is shown in Fig. 2.15. From this, it is clear that the 1st and proposed 2nd order modulators have less distortion components than the traditional 2nd order design. The ".four" function was used to compute the THD values and the results are shown in table 2.2. These results were obtained by calculating THD for the first five harmonics. The THD for the 1st order and proposed 2nd order modulators are almost identical although the 1st order is marginally worse. Since the results aren't conclusive, the simulations were repeated for an input frequency of 2 KHz. In this case the proposed 2nd order modulator clearly has the lowest distortion.

Figure 2.17 – Filtered output of each modulator with a 1 kHz input signal.

Figure 2.18 – FFT of each modulator's filtered output.

| Topology                          | Total Harmonic Distortion (THD) % |        |  |

|-----------------------------------|-----------------------------------|--------|--|

| 1st Order                         |                                   |        |  |

|                                   | Frequency                         | THD    |  |

|                                   | 1 KHz                             | 0.061% |  |

|                                   | 2 KHz                             | 0.052% |  |

| Proposed 2 <sup>nd</sup> Order    |                                   |        |  |

|                                   | Frequency                         | THD    |  |

|                                   | 1 KHz                             | 0.058% |  |

|                                   | 2 KHz                             | 0.041% |  |

| Traditional 2 <sup>nd</sup> Order |                                   |        |  |

|                                   | Frequency                         | THD    |  |

|                                   | 1 KHz                             | 0.46%  |  |

|                                   | 2 KHz                             | 0.35%  |  |

Table 2.2 –THD for each Topology

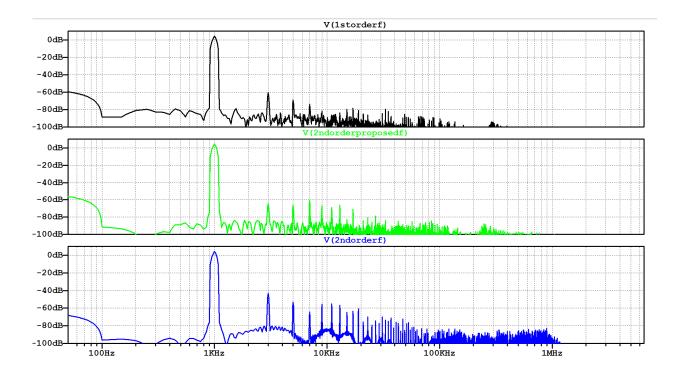

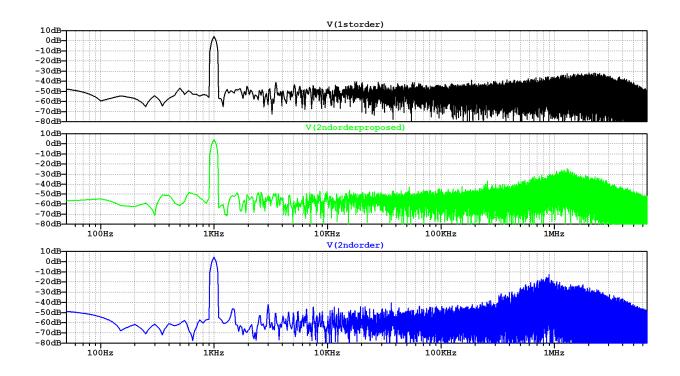

Finally, the FFT of the unfiltered digital output is shown in Fig. 2.16. It is important to examine this to see how the quantization noise is distributed amongst the frequencies. From this plot, it is clear that the noise-shaping for the  $2^{nd}$  order modulators is sharper than that of the  $1^{st}$  order modulator as expected. It is also clear that the noise floor for the proposed  $2^{nd}$  order modulator is the lowest of the three designs.

Figure 2.19 – FFT of each modulator's digital output.

Overall, it appears that the proposed  $2^{nd}$  order modulator topology is better than both the  $1^{st}$  order and traditional  $2^{nd}$  order topologies. This has been verified through the use of transfer functions which show better noise-shaping and lower quantization noise in the region of interest. Furthermore, SPICE simulations with ideal components show that the proposed  $2^{nd}$  order topology exhibits the best DC transfer linearity, lowest THD and lowest noise of all the presented designs.

## **Chapter 3 Discrete Component Level Implementation**

It is important to verify simulation results using ideal components by building an actual circuit and determining if the basic principles still hold true when translated into the real world. In order to do this, the passive modified 2<sup>nd</sup> order topology from chapter 2 was implemented using a discrete commercially available comparator and standard passive components. The results of this exercise demonstrate that the concept does indeed work in a real circuit and also that there is much room for improvement.

The schematic of the circuit is displayed in Fig. 3.1. This circuit is based around the LT1671 comparator made by Linear Technology [10]. This latched comparator is marketed as a low-power and high-speed device. In this application, the comparator was set up for dual supply operation, using +/- 5V power supplies. One advantage of this set-up is that no common-mode voltages need to be created since there is a ground reference. The passive network on the left of the LT1671 is the noise-shaping and feedback network. The passive network on the right of the chip is a simple 2<sup>nd</sup> order filter with a corner frequency of 72 KHz. The clock frequency was set to 1 MHz. This results in a very wide bandwidth and consequently a low OSR. A much lower corner frequency would likely be selected in a final implementation. The goal in this case was to examine the output harmonics clearly without attenuating them.

Figure 3.1 – Schematic of LT1671 based  $2^{nd}$ -order  $\Sigma$ - $\Delta$  modulator.

The circuit was built on an SOIC-8 breakout board with through-hole components directly soldered onto the pins. The top and bottom images of the circuit are shown in Fig. 3.2. Standard ¼ carbon film resistors were used. The capacitors were of film and NPO ceramic dielectric types. These capacitors have stable capacitances that do not vary with changes in applied voltage. It is worth noting that if ceramic capacitors are used in any sort of filtering application they must be of NPO type. Other ceramic dielectrics can introduce as much as 1% distortion into the signal. The completed circuit was mounted onto a copperclad board with proper decoupling capacitors at the power supply connections and BNC connectors for input/output signals. This is shown in Fig. 3.3 and is the set-up used to collect data for SNDR testing.

Figure 3.2 – Top and bottom of circuit on SOIC-8 breakout board.

Figure 3.3 – Set-up used for SNDR testing.

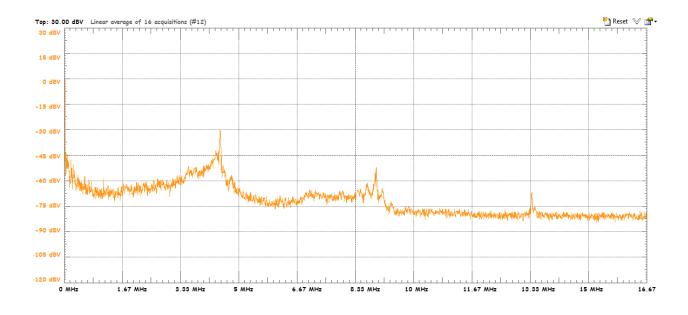

The complete set-up was tested using basic, student level test equipment. The regulated dual output power supply was set to +/- 5V. The input signal was set to be a 3.3V sine wave and came from a low distortion function generator. The output of the circuit was connected to a PC oscilloscope with 14-bits of vertical resolution and 10 MHz bandwidth [11]. This high resolution allows for meaningful SNDR testing. An example of an FFT spectrum is displayed in Fig. 3.4. For this plot, the input signal is 1 KHz and the total span of

the FFT is 8 KHz. The noise floor is at around -80 dB. The smoothness of the noise floor is due to averaging of 16 samples. Furthermore, coherent sampling was used to increase the spectral resolution of the FFT. This allows for an integer number of sinusoidal cycles within the sampling interval. Since the output filter is only  $2^{nd}$  order, there is still some energy at the 1 MHz clock frequency. This is shown in Fig. 3.5.

Figure 3.4 – Example output spectrum.

Figure 3.5 – Remnant of 1 MHz clock frequency.

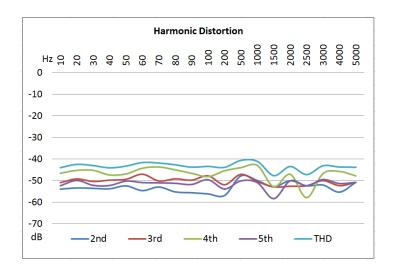

The SNDR was characterized by using THD. This is appropriate in this case because the distortion components are much higher than the noise power within the signal bandwidth. The THD was calculated by using the formula,

$$THD_f = \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2}}{V_1}$$

The levels of the first five harmonics were examined on the FFT and tabulated in Excel to make a THD plot. The THD as a function of frequency is shown in Fig. 3.6. The THD remains at less than 40 dB below the fundamental for most of the frequency range. The THD decreases with increasing frequency mainly due to the fact that the higher order harmonics are being attenuated as they approach the corner frequency of the 2<sup>nd</sup> order output filter. These THD levels are translated into ENOB in Fig. 3.7. The ENOB remains between 6 and 7 bits for most of the frequency range. While this is not good performance, it is important to note that no special precautions were taken in the implementation of this modulator. No matching was performed between components, no optimization of clock frequencies nor were output filters implemented.

Figure 3.5 – THD as a function of input frequency (Hz).

Figure 3.6 – ENOB as a function of input frequency (Hz).

## **Chapter 4 Continuous Time Sigma Delta Modulators**

## **Circuit Design**

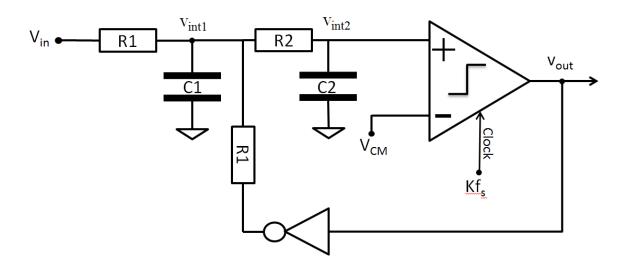

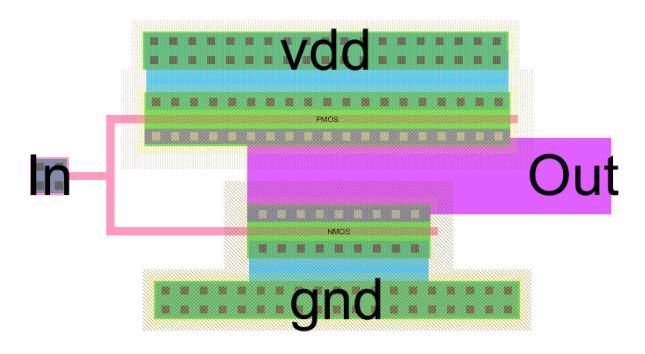

To verify the validity of theory and simulations, a physical implementation of the modified 2<sup>nd</sup> order passive sigma-delta topology is required. A simple continuous-time integrated circuit (IC) implementation on a mature CMOS process is a good starting point. The insights gained from such an exercise should scale well into modern CMOS processes. The C5 process by On Semiconductor is ideal for this application because of the high quality poly resistors and capacitors available which allow for the high resistance and capacitance values required by this topology [12]. The process also allows for the design of high quality analog components and digital logic at convenient 5V and 3.3V levels. A cell based methodology using the Electric VLSI software was used to design and layout the chip [13]. LTspice was used as the SPICE engine for both schematic and layout level simulation.

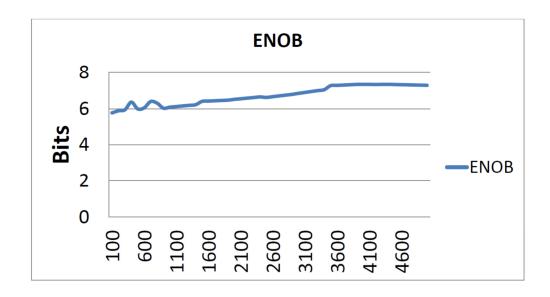

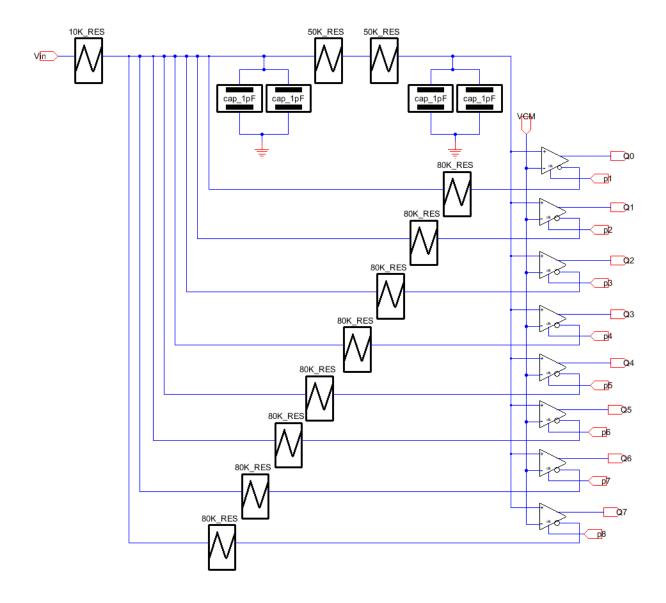

Figure 4.1 – Basic schematic of continuous time sigma-delta modulator.

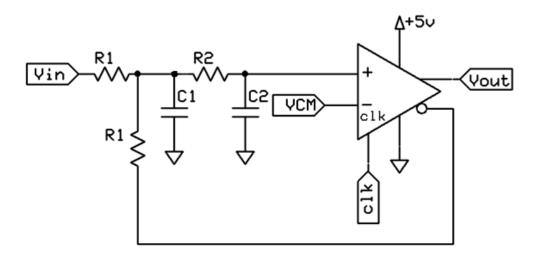

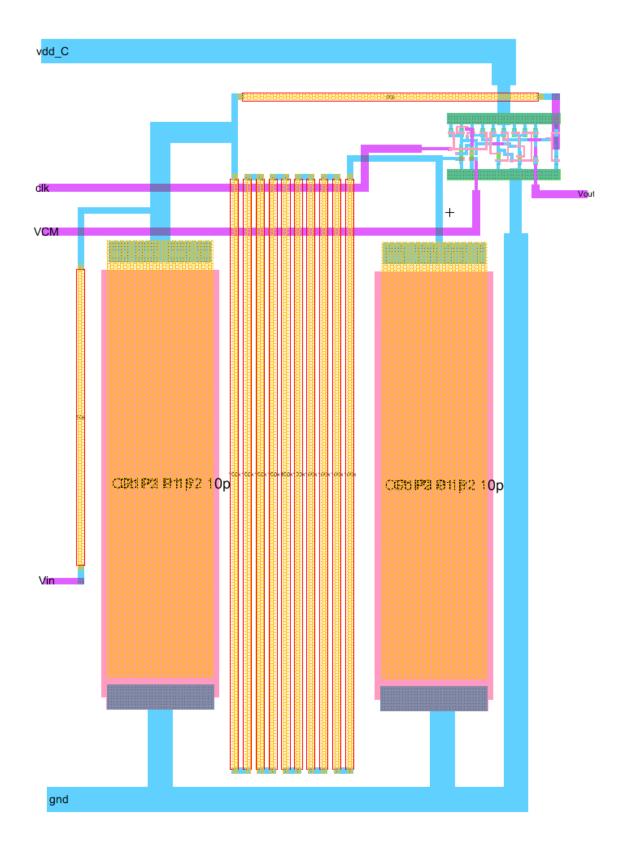

The basic schematic of the continuous-time sigma-delta modulator is shown in Fig. 4.1. The values of the passive components are given in Table 4.1. The resistors are created using the high-resistivity polysilicon in the C5 process. This high-resistivity treatment allows for high resistor values that are not possible using well resistors. The capacitors are formed using poly-poly capacitors available in the C5 process. Although the passive components are relatively large and take up most of the chip area, it is still practical to use them for an IC implementation. The layout views of the passive cells are shown in Fig. 4.2. These are not to scale and are intended to simply illustrate the components.

| Part  | Value | Layout Size     |

|-------|-------|-----------------|

| R1    | 50 kΩ | 162 um x 4.2 um |

| R2    | 1 ΜΩ  | 312 um x 63 um  |

| C1/C2 | 10 pF | 240 um x 60 um  |

Table 4.1 – Passive Component Values

Figure 4.2 – Layouts of passive components (not to scale).

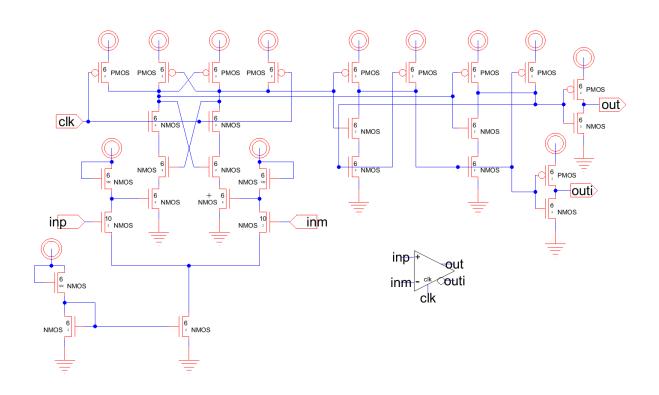

The most important part of the sigma-delta modulator is the clocked comparator. Much of the performance limitations are directly the result of the design of this component. For this application, a comparator needs to be decisive. This means that small input signals need to cause the output to swing either high or low without toggling back and forth until settling to one state. If the comparator was not decisive then glitches would ultimately reduce the resolution of the data converter. Although, it is worth noting that the sigmadelta topology inherently reduces the effect of these glitches since many samples are averaged together.

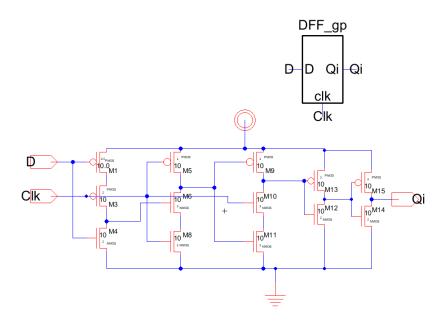

There are many comparator topologies that can be used in a sigma-delta modulator. For simplicity and low power, a memory sense amplifier with an SR latch and output inverters was selected as the comparator topology in this design. The block diagram of this circuit is shown in Fig. 4.3. The clocked comparator with differential outputs is on the left,

the S-R latch is in the middle and the output buffers are on the right. The S-R latch is used so that the output toggles only on the rising edge of the clock. The latch is comprised of two cross-coupled NAND gates. The output buffers are simple inverters.

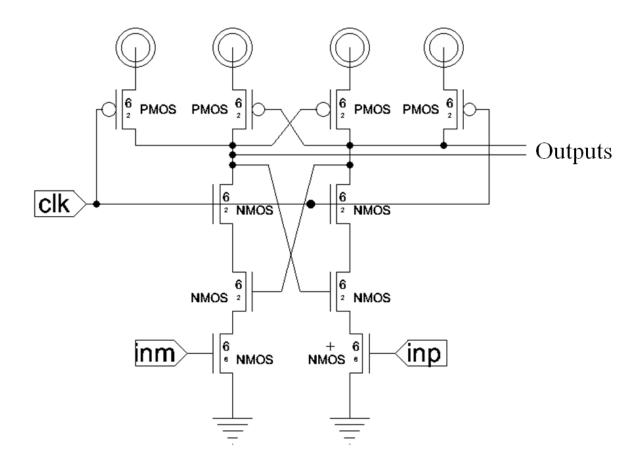

Figure 4.3 – Block diagram of comparator.

The memory sense amplifier uses a topology adapted from [14]. This type of amplifier is usually used for sensing in DRAM applications. As there may be hundreds of these amplifiers in a typical memory chip, reducing power consumption is very important. The low power consumption of this sense amplifier design is attractive in a passive sigmadelta modulator application. The schematic of the sense amplifier is shown in Fig. 4.4. The reason that this topology has low power consumption is due the use of long length MOSFETs operating in the triode region. These are the input MOSFETs in the bottom of the schematic. The long length MOSFETs reduce the contention current that flows to ground each time the clock switches state. Furthermore, the resistances of the long length MOSFETs isolate the inputs from the clock kickback noise. The operation of the circuit depends on the voltage imbalance of the inputs. Once the imbalance is sufficient, the input MOSFET with the higher input voltage pulls down the gate-source voltage ( $V_{gs}$ ) of the MOSFET above it. This causes that MOSFET to conduct resulting in the cross-coupled latch

to switch. A cross-coupled latch uses positive feedback to increase the gain and response time.

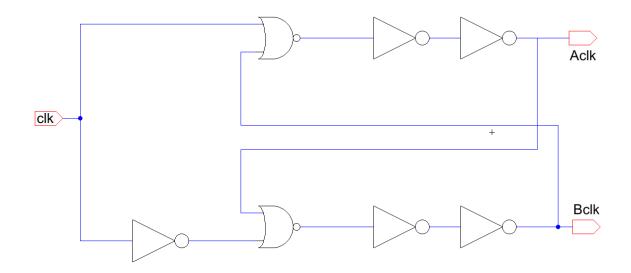

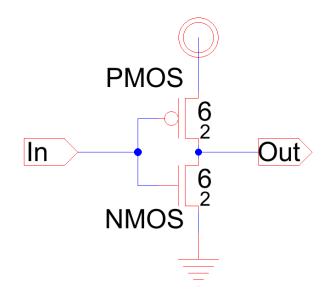

Figure 4.4 – Sense amplifier schematic.

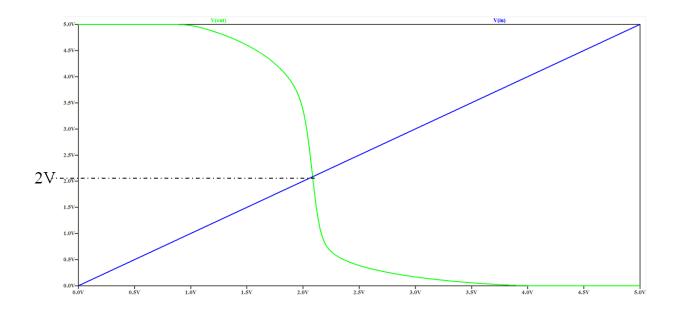

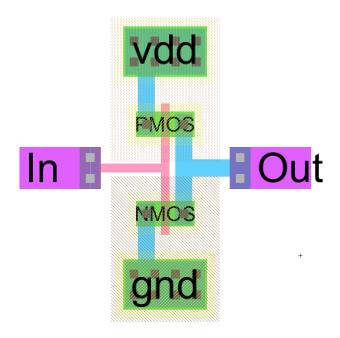

The remainder of the comparator design is made up of an S-R latch and output inverters. The S-R latch is made up of dual two-input NAND gates. The output inverters are made from identically sized PMOS and NMOS devices. All MOSFETs are minimum size in order to minimize power consumption. This does result in differing low to high  $(t_{PLH})$  and high to low  $(t_{PHL})$  transition points. The reason this occurs is because NMOS devices have about double the transconductance for a given size than PMOS devices. Generally, in most logic applications, the PMOS devices are twice the size of NMOS devices to result in equal

transconductance and therefore equal transition points. The switching point for the inverter is shown in Fig. 4.5.

Figure 4.5 – Inverter switching point.

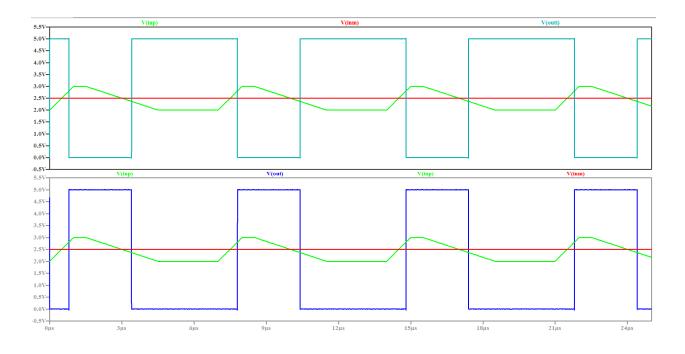

The full schematic of the comparator with a side by side comparison to its block diagram is shown in Fig. 4.6. Generally a common mode input of half the supply voltage is applied to the negative terminal of the comparator. When the voltage applied to the positive terminal exceeds that of the negative terminal, the output of the comparator switches high and the complementary output switches low. This is shown in Fig. 4.7. For this simulation the input signal is an arbitrary waveform to show that the comparator switches at the correct points. The complementary output is required to provide negative feedback and eliminates the need for an additional inverter and its associated delays in the feedback loop.

Figure 4.6 – Full schematic of comparator.

Figure 4.7 – Comparator operation with  $V_{inp}(green)$ ,  $V_{inm}(red)$ ,  $V_{out}(blue)$ , and  $V_{outi}(teal)$ .

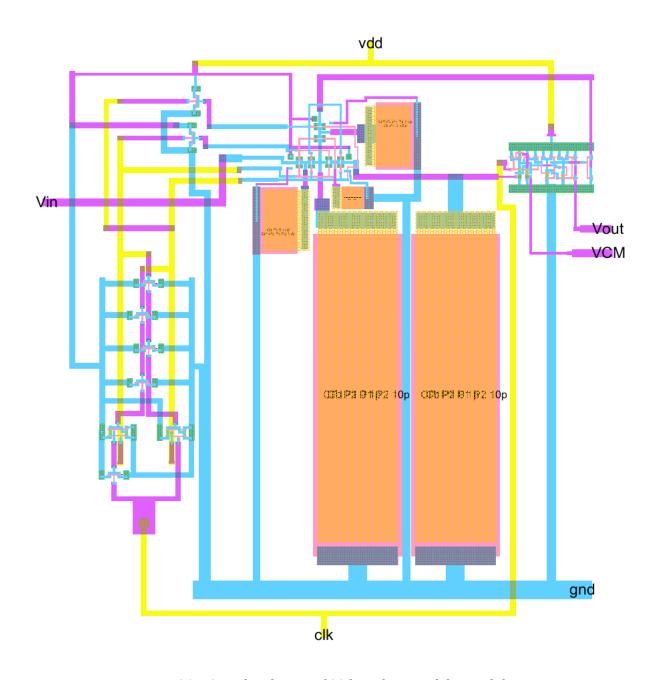

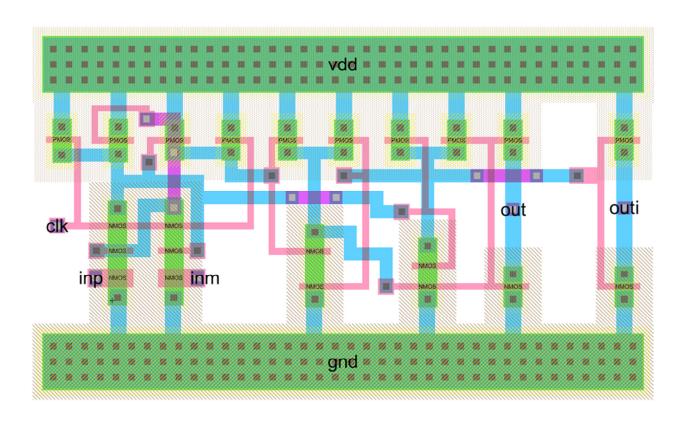

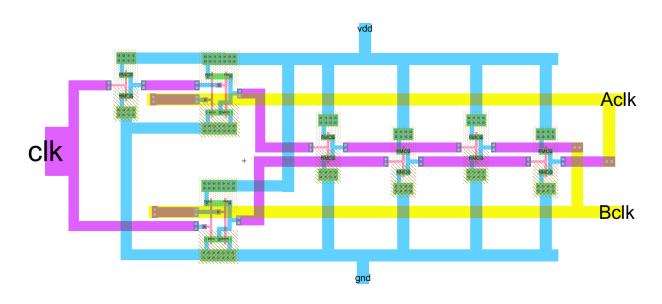

The layout of the comparator is carefully optimized to take up as little area as possible. Most component spacing is as close as possible while following C5 process design rules. The layout of the comparator is shown in Fig. 4.8. All MOSFETs are minimum size except for the input MOSFETs where the longer channel lengths are clearly visible. The size of the layout is 61.3 um by 37.6 um. This small size is critical because the passive components will occupy the majority of the space on the chip. A simulation of the layout with conservative RC modeling gives almost identical results to the schematic simulation. This means that parasitic effects from the layout are negligible. The full modulator layout is shown in Fig. 4.9. The total size of this layout is 400 um by 270 um. A micrograph of the modulator is shown in Fig. 4.10. This micrograph is a portion of a complete test chip which was fabricated with other test structures shown in Fig. 4.11.

Figure 4.8 – Comparator layout.

Figure 4.9 – Complete modulator layout.

Figure 4.10 – Micrograph of modulator.

Figure 4.11 – Micrograph of complete chip.

Simulations of the passive modified 2<sup>nd</sup> order sigma-delta modulator are needed to quantify its performance. Since a sigma-delta modulator operates by averaging a large number of samples, different types of testing must be done than other ADCs. Traditionally the linearity of Nyquist-rate ADCs are characterized with a plot of input voltage vs. output code. This is not possible with sigma-delta modulators since the output is 1-bit. Instead, a very slow ramp signal is applied to the input and averaged to create a linearity plot. A simulation of this sigma-delta modulator showing the input ramp signal and unfiltered 1-bit output is shown in Fig. 4.12. The input range of this design appears to be between 0.6V and 4.5V. Outside of this range, the output does not respond. At first glance, this can be attributed to the fact that the comparator design does not have a symmetrical input stage and thus fully rail to rail inputs. However, this is not the case since the comparator is used

with feedback which keeps the signal at the inputs around the common mode voltage which is well within the input range for the comparator. Rather this is due to the inability of the comparator to switch with input signal differences of below a few millivolts. This will be examined later and is a source for improvement with this design.

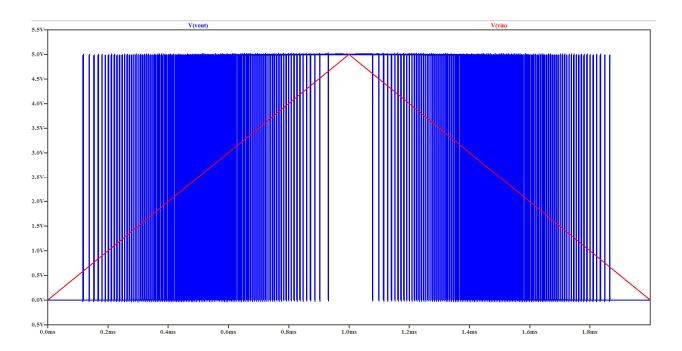

Figure 4.12 – Input ramp (red) and 1-bit output (blue).

Filtering the output results in a reconstructed ramp signal and reflects the linearity of the modulator. This output ramp is shown in Fig. 4.13 along with the input ramp signal. The perturbations along the slope of the output ramp are artifacts due to a non-ideal filter. A second order RC filter was used to create this plot. Using a higher order digital filter will remove these artifacts.

Figure 4.13 – Filtered reconstructed output ramp compared to input ramp.

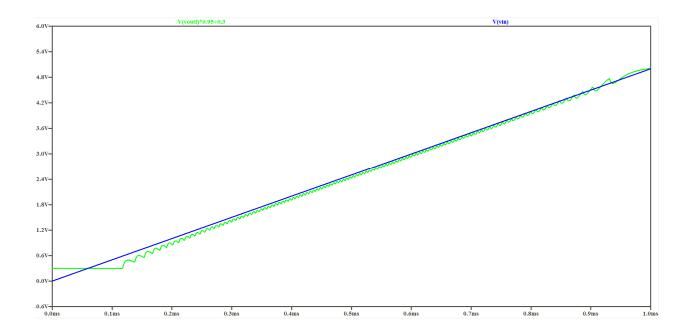

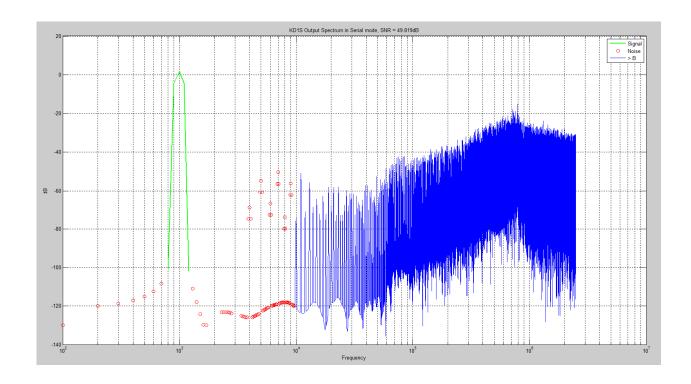

The mostly linear transfer function of this modulator indicates good AC performance as well. The small slope error that is visible in Fig 4.13 is due to the gain of the modulator not being exactly unity. While this is detrimental to DC input signals and results in a large error, it does not affect the linearity of AC signals. This is because AC linearity only depends on the slope of the transfer function being linear and is independent of gain. However, the gain error can be reduced through software trimming and calibration in the intended application of the ADC. A simulation of a reconstructed sine wave after passing through a digital sinc filter is shown in Fig. 4.14. The clock frequency for this simulation is 5 MHz, the input signal is 1 KHz and the OSR is set to 256. This results in a bandwidth of 10 KHz. The noise components within this 10 KHz bandwidth are added to the SNR. The FFT of the modulator output is shown in Fig. 4.15. The red portion of the spectrum is within the bandwidth that contributes to the SNR of 49.8 dB. The blue component represents out of band (OOB) noise. The MATLAB script was used to compute SNR removes the  $2^{nd}$  and  $3^{rd}$

harmonic distortion tones [15]. This is done to get an indication of the linearity of the modulator at lower input levels before distortion sets in at high output levels. Overall the simulation results indicate an ENOB of around 8 bits.

Figure 4.14 – Reconstructed output (blue) and input (red).

Figure 4.15 – FFT of modulator output with SNR bandwidth (red) and out of band noise (blue).

### **Measurements**

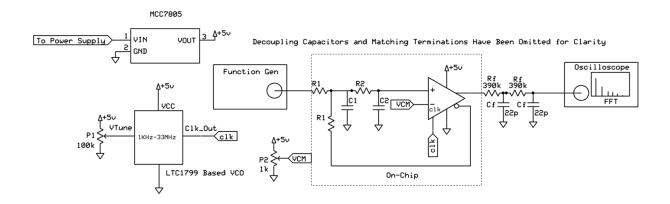

Ultimately, simulation results need to be validated with real world measurements to verify true circuit performance. For a low power IC this is difficult since optimization for low power reduces the ability to drive off chip loads. As a result the test set-up was carefully optimized to ensure that test data is meaningful and accurate. The test set-up is shown in Fig. 4.16. This set-up is used to measure the harmonic distortion of the filtered output signal using the oscilloscope's software FFT feature. This harmonic distortion measurement accurately reflects the SNDR of the modulator. The set-up can also measure current consumption of the modulator. A carefully constructed "deadbug" style breadboard was used to reduce the effect of parasitic capacitances. This circuit is shown in Fig. 4.17. There is an onboard clock generator, an LTC1799 which has a variable frequency output

between 1 KHz and 33 MHz [16]. A precision 25 turn potentiometer is used to adjust the frequency. All circuitry is properly bypassed with a combination of electrolytic, film and ceramic capacitors to ensure low source impedance at all frequencies.

Figure 4.16 – Simplified schematic of test set-up.

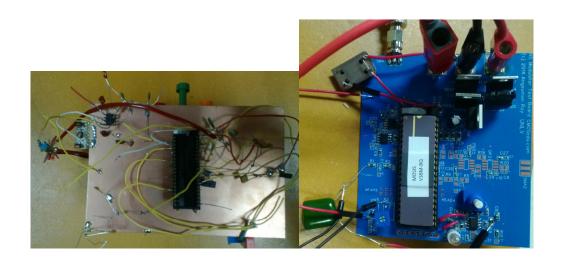

Figure 4.17 – "Deadbug" [17] test board (left) and PCB (right).

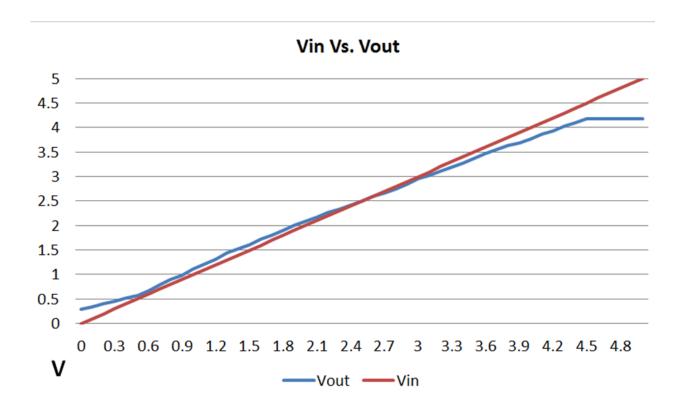

Using this test set-up and its variations, the DC transfer function, differential nonlinearity, power consumption and harmonic distortion were measured. The DC transfer function is shown in Fig. 4.18. For this set-up a stable variable voltage source was applied to the input and the resulting output voltage was measured. Both input and output voltages are measured using an Agilent  $34405A\ 5\ \frac{1}{2}$  digit multimeter. From the transfer function it is apparent the linear region falls between 0.6V and 4.5V. The applied input signal should be bounded within these limits for accurate conversion. A slight gain error is also apparent, but this should not be an issue after software calibration.

Figure 4.18 – Measured DC transfer function.

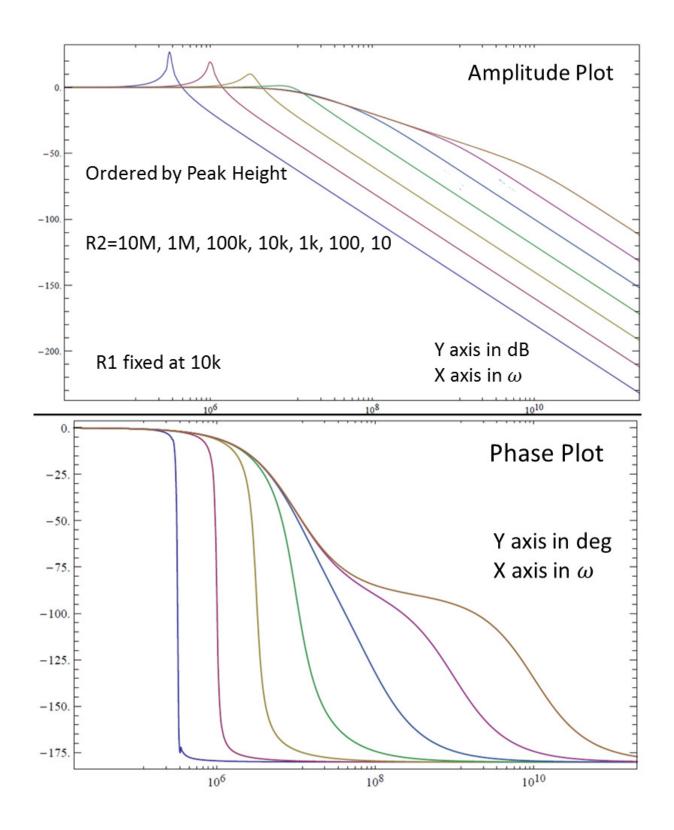

The differential nonlinearity (DNL) of the modulator can be obtained from the DC transfer function as done in Fig. 4.19. The units on the Y axis are percentages. The DNL is a measure of the change in linearity between each consecutive point on the DC transfer function. In essence, it can be viewed as a derivative of the DC transfer function.

Traditionally DNL is not used to characterize sigma delta ADCs because the output is not static. For this measurement, significant averaging is used which makes the output nearly static for each data point. Examining the DNL data, it is clear that the modulator is quite linear between 0.6 V and 4.5 V which is to be expected from the DC transfer function.

Between the 0.6 V and 4.5 V range, the DNL is kept within 0.4%. This indicates that the AC performance should be quite good.

# O.1 0.05 0 -0.05 -0.1 V 0 0.3 0.6 0.9 1.2 1.5 1.8 2.1 2.4 2.7 3 3.3 3.6 3.9 4.2 4.5 4.8 —Differential Nonlinearity

Figure 4.19 – Measured differential nonlinearity (DNL).