Photon counting circuit

test chip

Contributors

Angsuman Roy (angsumanroy@gmail.com)

Gonzalo

Arteaga (arteag1@unlv.nevada.edu)

David Santiago

(santid4@unlv.nevada.edu)

Bryan Kerstetter (bdkerstetter@gmail.com)

Jason Silic (jason.silic@unlv.edu)

Sachin P Namboodiri

(puruss1@unlv.nevada.edu)

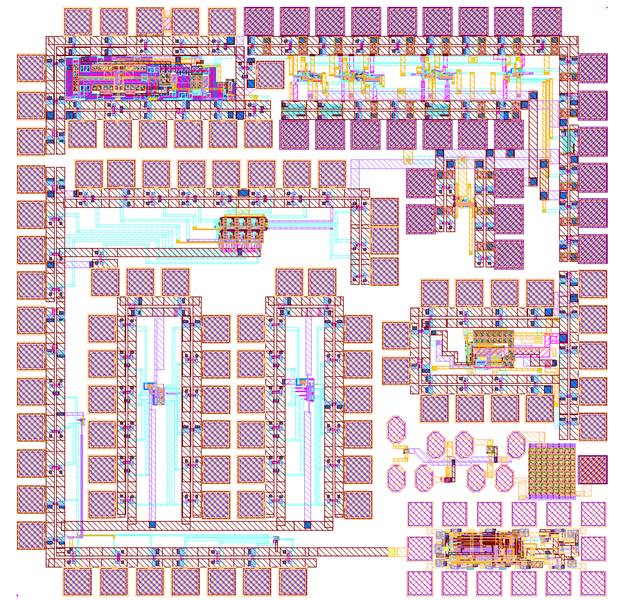

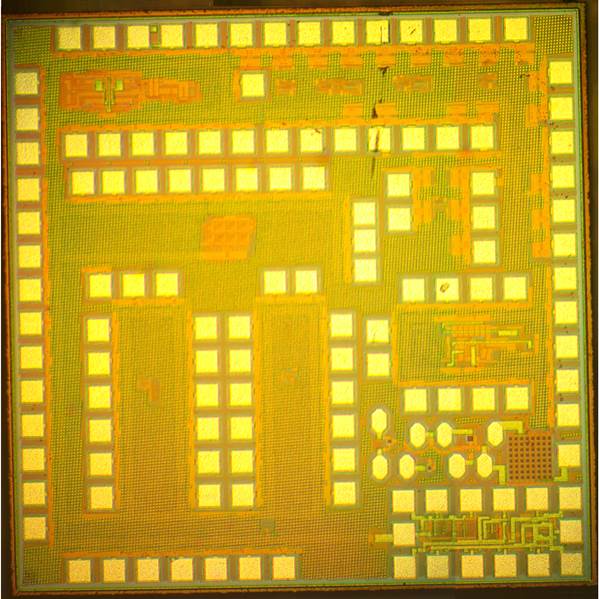

Chip Orgainization

This chip is

designed using Towerjazz’s 180nm SiGe

BiCMOS process and occupies an area of 2.5 mm x 2.5

mm. The chip was taped out on January 2020 and it comprises the following

circuits:

1)

Current mode photon counting circuits

Figure 1. Complete chip layout and photomicrograph