#### Forward

Dr. Baker:

The zipped filed I sent you is titled "Final Project" and has two different designs in it titled "Design 1" and "Design 2". I included both designs because my first design "Design 1" seems to have better overall performance, but I had spent so much time troubleshooting "Design 2" that I figured I would include it. I hope this clearly allows you to simulate my project without any difficulties, and I would like to thank you for yet another wonderful semester and learning

#### Introduction

The objective of this course project is to use On's C5 process to design a voltage follower using an op-amp that can operate with a VDD between 3V and 5V while driving a 10pF (max) and  $1k\Omega$  (min) load. The input voltage should be connected to the noninverting "+" input of the op-amp and the output voltage connected back to the inverting "-" input of the op-amp. Lastly, the design should meet the design constraints stated below.

## **Design Constraints**

- The error (difference) between the input signal and output signal should be < 0.1%

- Bandwidth of the follower should be > 100MHz

- Slew-rate with maximum load > 100V/microsecond

- Current draw from VDD should be less than 10mA under full load conditions

- Output swing should be 80% of VDD (e.g. 0.5V to 4.5V when VDD=5V or 0.12V to 2.88V when VDD=3V. The output swing doesn't have to be centered as these examples are, that is, 0.25V to 4.25V when VDD=5 V is fine too).

# **Table of Contents**

| Forward                           | 1  |

|-----------------------------------|----|

| Introduction                      | 1  |

| Design Constraints                | 1  |

| Table of Contents                 | 2  |

| Transconductance Matching         | 3  |

| NMOS Characterization             | б  |

| PMOS Characterization             | 13 |

| Table Summary of Characterization | 21 |

| Beta-Multiplier Reference (BMR)   | 22 |

| Voltage Follower: Design 1        | 23 |

| Voltage Follower: Design 2        |    |

| Voltage Follower: Design 3        |    |

| Table Summary of Design Results   | 47 |

| Conclusion                        | 48 |

| References                        | 49 |

#### **Transconductance Matching**

The purpose of this section is to use On's C5 process information in order to match the

transconductances of an NMOS and PMOS (gmn and gmp, respectively) based off their sizes. On's

C5 process Spice models detailed in C5\_models.txt are shown in Fig. 1.

\* BSIM3 models for AMI Semiconductor's C5 process Don't forget the .options scale=300nm if using drawn lengths and the MOSIS SUBM design rules \* 2<Ldrawn<500 10<wdrawn<10000 Vdd=5v \* Note minimum L is 0.6 um while minimum W is 3 um \* Change to level=49 when using HSPICE or SmartSpice = 8 = 1.39E-8 = 0.6696061 = 23.1023856 .MODEL NMOS NMOS ( +VERSION = 3.1 +XJ = 1.5E-7 LEVEL TOX VTH0 TNOM 27 = 1.7E17 NCH = 1.5E-7= 0.8351612 = -7.6841108 = 0 = 2.9047241 = 458.439679 = 1.6200205 +К1 +КЗВ K2 W0 = -0.0839158K3 NLX = 1E-8 1E-9 = 0= -0.134857 = 1.485499E-18 = 0.6103537 +DVT0W DVT1W DVT2W = 0 = 0 = 0.4302695 = 1E-13 = 1.643993E5 2.9047241 458.439679 1.629939E-11 DVT2 UB A0 +DVT0 +U0 DVT1 UA VSAT +UC = = 0.1194608 = -2.640681E-3 = 1.387108E3 +AGS +KETA В0 А1 = 2.674756E-6 = 8.219585E-5 B1 A2 5E-6 0.3564792 = 0.0299916 = 2.472348E-7 = 0 PRWG +RDSW PRWR = 0.0363981= 1.38/108E5 = 1 = 0 = 5.306586E-8 = 3.597605E-8 = -1.287163E-8 +WR WINT LINT +XL XW DWG NFACTOR = 0.8365585 CDSCD = 0+DWB +CIT +CDSCB VOFF = 0+DWB = 5.306586E-8 +CIT = 0 +CDSCB = 0 +DSUB = 0.2543458 +PDIBLC2 = 2.311743E-3 +PSCBE1 = 5.598623E8 VOFF = 0 CDSC = 2.4E-4 ETA0 = 0.0246738 PCLM = 2.5945188 PDIBLCB = -0.0272914 ETAB = -1.406123E-3 PDIBLC1 = -0.4282336 DROUT = 0.7283566  $\begin{array}{rcl} \text{PSCBE2} &= 5.461645\text{E}{-5}\\ \text{RSH} &= 81.8\\ \text{UTE} &= -1\\ \text{KT2} &= 0 \end{array}$ = 0 = 0 = 1 = -0.2501 = 5.4E-10 = 1E5 = 0 = 5.598623E = 0.01 = 8.621 = -2.58E-9 = -4.8E-19 +DELTA +PRT MOBMOD KT1 UA1 +KT1L UC1 WLN = -7.5E-11 = 1 = 0 AT +UB1 0 +WL +WWN = 1 WWL LL 0 +LLN = 1 = 0LW CAPMOD = 0 = 2 LWN XPART = 1 0.5 +LWL = 0.5 = 1E-9 = 0.4515044 = 0.1153991 = 0.1153991 = 133.285505 = 1.173187E-3 +CGDO +CJ +CJSW = 2E - 10= 2E - 10CGSO CGBO = 2E - 10= 0.99 = 0.1 = 0.1 = 0.0585501 = 2E-10 = 4.197772E-4 = 3.242724E-10 PB PBSW MJ MJSW +CJSWG +CF = 1.64E - 10PBSWG MJSWG = 0 PVTH0 PRDSW +PK2 = -0.0299638 = -0.0248758= 0) WKETA LKETA +AF = 1 KE = 8 = 1.39E-8 = -0.9214347 = 6.3063558 = 2.593997E-8 .MODEL PMOS PMOS ( LEVEL +VERSION = 3.1 +XJ = 1.5E-7 +K1 = 0.5553722 TNOM = 27 = 1.7E17 = 8.763328E-3 = 1.280703E-8 = 0 = 27тох VTH0 K3 NLX +XJ +K1 NCH K2 W0 +K3B = -0.6487362 W0 = 1.2807052-8 DVT1W = 0 DVT1 = 0.5480536 UA = 2.807115E-9 VSAT = 1.713601E5 B0 = 7.117912E-7 A1 = 4.77502E-5 PRWG = -0.0363908 WINT = 2.838038E-7 XW = 0 VOFF = -0.0558512 CDSC = 2.4E-4 ETA0 = 0.3251882 PCLM = 2.2409567 PDIBLCB = -0.0551797 PSCBE2 = 6.300848E-10 RSH = 101.6 UTE = -1 +DVT0W = 0 DVT1W DVT2W = 0 = 0 = 2.5131165 = 212.0166131 = -5.82128E-11 = 0.1328608 = -0.1186489 +DVT0 DVT2 +U0 +UC UB AO = 1E-21= 0.8430019 B1 A2 PRWB +AGS = 5E-6B1 = 5E-6 A2 = 0.3 PRWB = -1.016722E-5 LINT = 5.528807E-8 DWG = -1.606385E-8 NFACTOR = 0.9342488 CDSCD = 0 ETAP = -0.0580325 -3.674859E 2.837206E3 +KETA 674859E-3 +RDSW = +WR +XL = 1 ō = 2.266386E-8 = 0 +DWB +CIT +CDSCB CDSCD ETAB ŏ -0.0580325 = 0 = 1 = 3.355575E-= 6.44809E9 = 0.01 = 59.494 1.68E-9 =  $\begin{array}{l} \text{PDIBLC1} = 0.0411445 \\ \text{DROUT} = 0.2036901 \end{array}$ 1 3.355575E-3 +DSUB +PDIBLC2 +PSCBE1 **PVAG** = 0 +DELTA +PRT MOBMOD = 1 UTE KT2 KT1 -0.2942 = -1= 0 +KT11 UA1 = 4.5E-9= 0 = -1E-10 = 1 = 0 +UB1 -6.3E-18 UC1 WLN 1E3 0 AT = 0 +WL WW = +WWN +LLN = 1 WWL 11 = 0 LW CAPMOD LWN XPART = 1= 0.5 +LWL = 0 = 2 +CGD0 +CJ +CJSW +CJSWG = 0 = 2.9E-10 = 7.235528E-4 = 2.692786E-10 = 2.9E-10 = 0.9527355 = 0.99 CGBO MJ MJSW  $\begin{array}{l} = 0.3 \\ = 1E-9 \\ = 0.4955293 \\ = 0.2958392 \\ = 0.2958392 \end{array}$ CG50 PB PBSW = 6.4E - 11PBSWG = 0.99 MJSWG = 5.98016E-3 = 5.292165E-3 = 0) +CF = 0= 3.73981E-3 PVTH0 PRDSW = 14.8598424= -4.205905E-3+PK2 +AF WKETA LKETA KF 1

Fig. 1 – On's C5 Process Spice Models (C5\_models.txt)

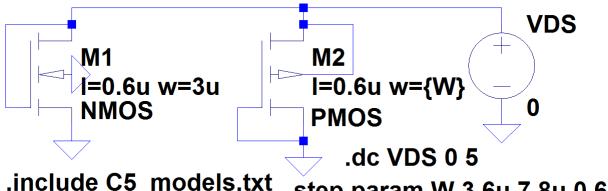

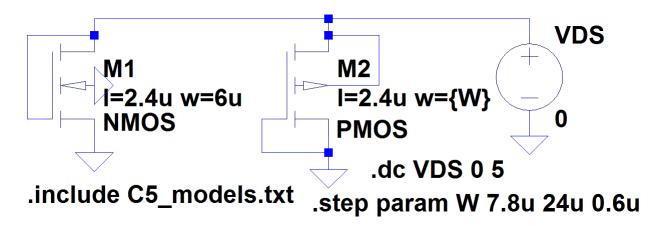

**Schem. 1** shows the NMOS and PMOS connected to one another (NMOS drain connected to PMOS source) for transconductance matching. Both the NMOS and PMOS are drain-gate connected to ensure they are each operating in saturation, and their bodies are connected to their sources (GND and VDD, respectively) to eliminate body effect. The size of the NMOS is chosen to be minimum length (Lmin=0.6um=600nm) and minimum width (Wmin=3um) based off On's C5 process information detailed in C5\_models.txt shown in **Fig. 1**.

Schem. 1 – Matching NMOS & PMOS Transconductances (g<sub>mn</sub> & g<sub>mp</sub>)

It is noted that "...we use 2-5 times minimum length for general design" and "...we use minimum length for high-speed design" (Baker, pg. 297). It is also important to know that "...using minimum channel lengths results in large mismatches between devices and low MOSFET output resistance" which results in "low gain and large input-referred offset voltages" (Baker, pg. 863). In addition, "...to minimize power and maximize speed, we will use minimum size devices (Baker, pg. 863). This information suggests we should not have started with minimum sizing for the NMOS since we are not designing for high speed since (bandwidth only needs to be greater than 100MHz) or minimized power, we do not want large mismatches between our NMOS and PMOS, and we do not want low MOSFET output resistance which will result in low gain and large input-referred offset voltages. However, we will use minimum sizing for the NMOS as a starting point and note that we can always come back and repeat the

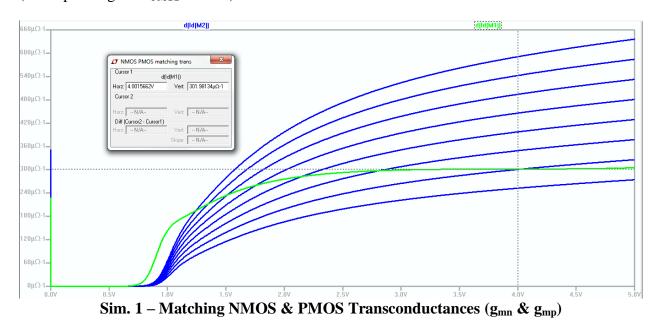

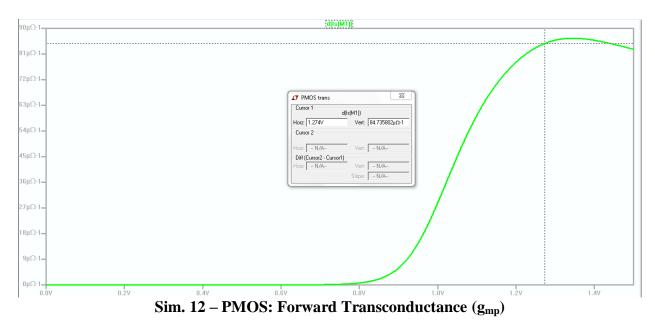

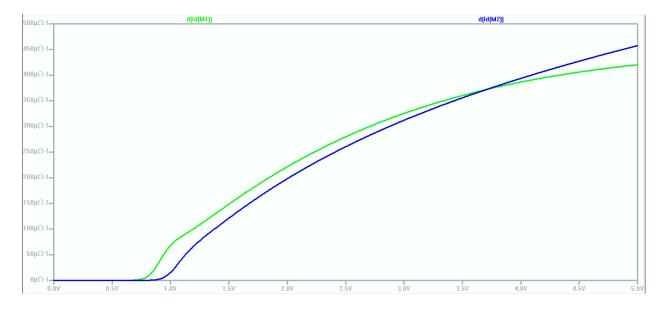

following process starting with a different sized NMOS. The PMOS in **Schem. 1** has the same length as the NMOS (Lmin=0.6um=600nm) for good matching, and its width is stepped to determine which width gives the closest PMOS transconductance ( $g_{mp}$ ) to the NMOS transconductance ( $g_{mn}$ ) as VDS=VSD=VGS=VSG=VDD is swept from 0V to 5V. **Sim. 1** shows the transconductances of the NMOS and PMOS ( $g_{mn}$  and  $g_{mp}$ , respectively) by plotting the derivative of their drain currents. See Eq. (9.57).

$$g_m = \left[\frac{\partial i_D}{\partial v_{GS}}\right]_{V_{GS} = \text{ constant}}^{I_D = \text{ constant}} = v_{sat} \cdot C'_{ox} \cdot W$$

(9.57)

By averaging the area (over 0V to 5V) of the various PMOS transconductance curves (corresponding to the various PMOS widths), it can be seen that the third curve from the bottom (corresponding to  $W_{PMOS}$ =4.8um) best matches the NMOS transconductance curve.

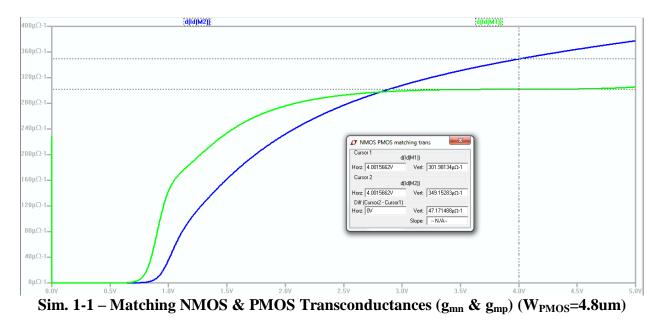

Sim. 1-1 shows the PMOS transconductance  $(g_{mp}=349uA/V)$  for  $W_{PMOS}=4.8um$  and NMOS transconductance  $(g_{mn}=302uA/V)$  for VDS=VSD=VDD=4V. This result simply shows the NMOS and PMOS transconductances  $(g_{mn} \text{ and } g_{mp}, \text{ respectively})$  are relatively closely matched for the specified sizes.

## **NMOS Characterization**

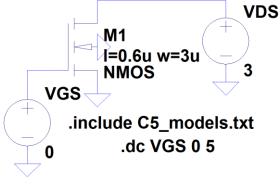

The purpose of this section is to sweep VGS in order to determine threshold voltage (Vthn), bias current (Ibiasn), and bias voltage (Vbiasn=VGS) to then determine output resistance ( $r_{on}$ ), transconductance ( $g_{mn}$ ), and transition frequency ( $f_T$ ) for the NMOS. **Schem. 2** shows the NMOS (3um/0.6um) with VDS=3V in order to characterize the NMOS on the lower end of VDD.

Schem. 2 – NMOS: VGS Sweep

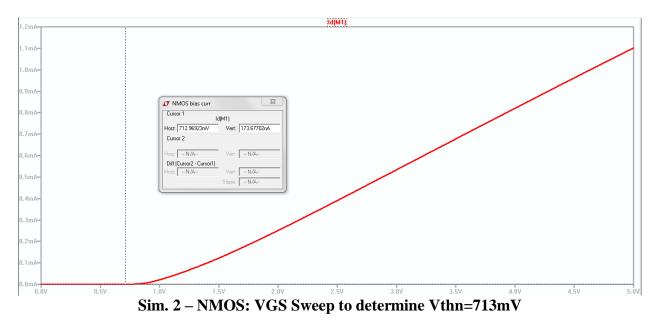

Sweeping VGS from 0V to 5V results in **Sim. 2** which shows VGS=Vthn=713mV. This is the voltage in which the NMOS turns on.

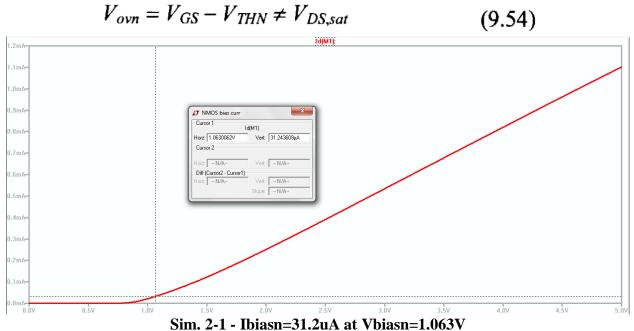

Referring to Eq. (9.54) and noting "... For general analog design, we set the overdrive voltage to 5% of VDD. For high-speed design, we might set the overdrive voltage to 10% of VDD or larger" (Baker, pg. 863), we can estimate Vovn=7%(VDD)=7%(5V)=350mV and can calculate VGS=Vovn+Vthn=(350+713)mV=1.063V. **Sim. 2-1** shows Ibiasn=31.2uA at Vbiasn=VGS =1.063V.

7 17 17 . 17

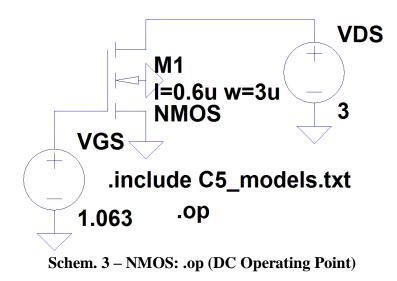

Schem. 3 shows the NMOS with VGS=Vbiasn=1.063V and VDS=3V, and Sim. 3 shows various DC operating point values from the Spice error log including Vthn=699mV,  $g_{mn}$ =174uA/V,  $r_{on}$ =1/Gds=1/(2.48x10<sup>-6</sup>)=403,226\Omega, and VDS,sat (here Vovn)=242mV.

| 🗸 SPI         | ∠▼ SPICE Error Log: C:\Users\ |  |  |  |

|---------------|-------------------------------|--|--|--|

| Vth:          | 6.99e-01                      |  |  |  |

| Vdsa          | t: 2.42e-01                   |  |  |  |

| Gm:           | 1.74e-04                      |  |  |  |

| Gds:          | 2.48e-06                      |  |  |  |

| Sim. 3 – NMOS | S: .op (DC Operating Point)   |  |  |  |

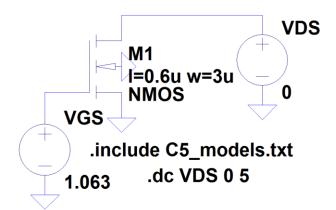

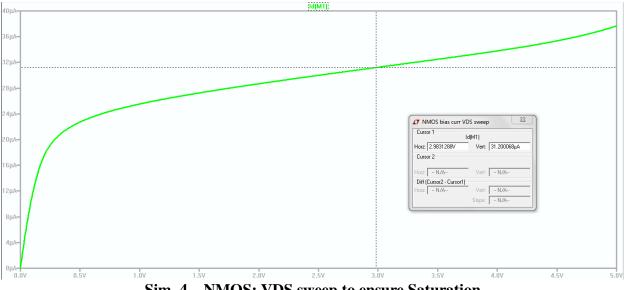

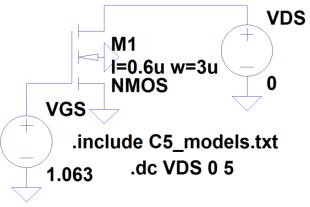

In order to ensure the NMOS is in saturation when Ibiasn=31.2uA at Vbiasn=1.063V, **Schem. 4** shows VDS being swept from 0V to 5V with VGS=1.063V. **Sim. 4** shows the NMOS is, in fact,

in saturation when Ibiasn=31.2uA and gives VDS=2.98V.

Schem. 4 – NMOS: VDS sweep to ensure Saturation

Sim. 4 - NMOS: VDS sweep to ensure Saturation

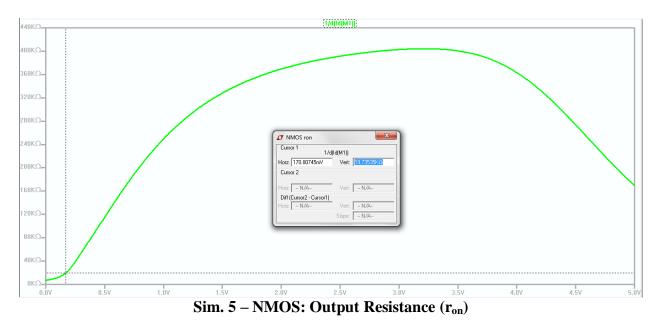

In order to determine the output resistance (r<sub>on</sub>) of the NMOS, **Schem.** 5 shows VDS being swept from 0V to 5V with VGS=1.063V. Sim. 5 shows the output resistance  $(r_{on})$  plotted as the reciprocal of the derivative of the drain current (1/deriv(I<sub>D</sub>)). VDS,sat (here Vovn) is approximated as the voltage where the output resistance begins to increase. This results in VDS,sat=170.8mV (approx.) and gives  $r_{on}=19.74k\Omega$ .

Schem. 5 – NMOS: Output Resistance (ron)

Table 1 shows values for  $r_{\text{on}}$  at varying voltages of VDS

| VDS=0V          | $r_{on}=7.2k\Omega$   |

|-----------------|-----------------------|

| VDS,sat=170.8mV | $r_{on}=19.7k\Omega$  |

| VDS=3 V         | $r_{on}=402.7k\Omega$ |

| VDS=4 V         | $r_{on}=363.0k\Omega$ |

| VDS=5 V         | $r_{on}=170.2k\Omega$ |

| Table 1 – r <sub>on</sub> for various values of VI | Table 1 | – r <sub>on</sub> for | various | values | of | VDS |

|----------------------------------------------------|---------|-----------------------|---------|--------|----|-----|

|----------------------------------------------------|---------|-----------------------|---------|--------|----|-----|

Lambda can be calculated as  $\lambda_n = 1/(r_{on}*I_D) = 1/(r_{on}*Ibiasn)$  using  $r_{on} = 402.7k\Omega$  @ VDS=3V from

**Sim. 5** and using Ibiasn=31.2uA  $\rightarrow$ :

$$\circ \lambda_n = 1/(r_{on}*I_D) = 1/(r_{on}*Ibiasn) = 1/((402.7k\Omega)*(31.2uA)) = 0.0796V^{-1}$$

$$\circ \lambda_n = 0.0796 V^{-1}$$

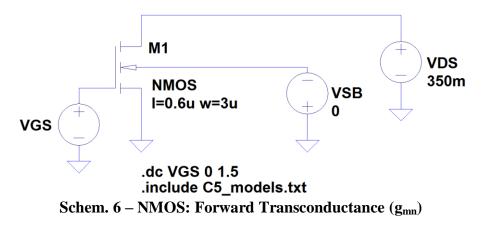

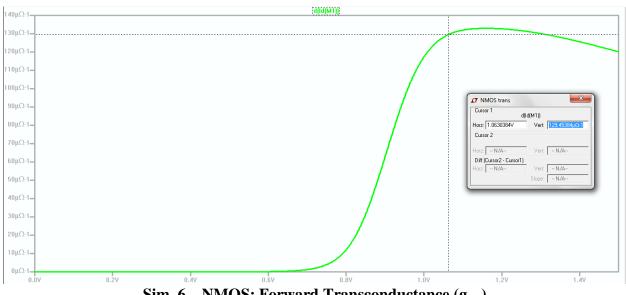

Determining the forward transconductance  $(g_{mn})$  of the NMOS is modeled in **Schem. 6** in which

VDS=VDS,sat(= Vovn)=350mV and VGS is swept from 0V to 1.5V in order to show a clear

plot.

Sim. 6 shows the transconductance  $(g_{mn})$  plotted as the derivative of the drain current  $(deriv(I_D))$ and gives  $g_{mn}=129.5uA/V$  at VGS=1.063V. It should be noted that "...g<sub>mn</sub> does change with VGS, unlike what was indicated in Eq. (9.57). This is because the saturation velocity isn't exactly constant and depends on both VGS and VDS" (Baker, pg. 298-299). The gain can then be calculated using  $r_{on}$ =402.7k $\Omega$  @ VDS=3V from Sim. 5 and using g<sub>mn</sub>=129.5uA/V at VGS=1.063V from **Sim. 6.**

$Gain=g_{mn}r_{on}=(129.5uA/V)*(402.7k\Omega)=52V/V$ ۲

Gain=52V/V •

Sim. 6 – NMOS: Forward Transconductance (g<sub>mn</sub>)

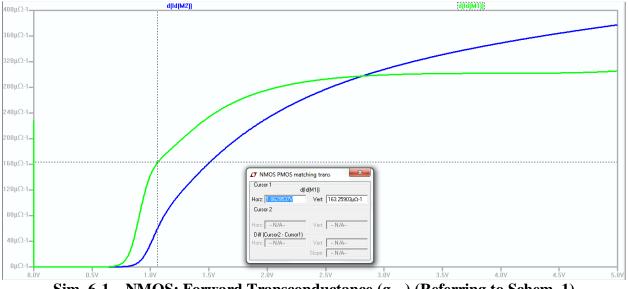

Additionally, Schem. 1 can be referred to for Sim. 6-1 which shows g<sub>mn</sub>=163.3uA/V for

VDS=VGS=Vbiasn=1.063V.

Sim. 6-1 – NMOS: Forward Transconductance (g<sub>nn</sub>) (Referring to Schem. 1)

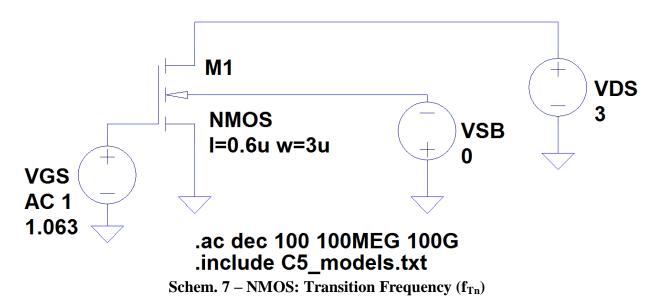

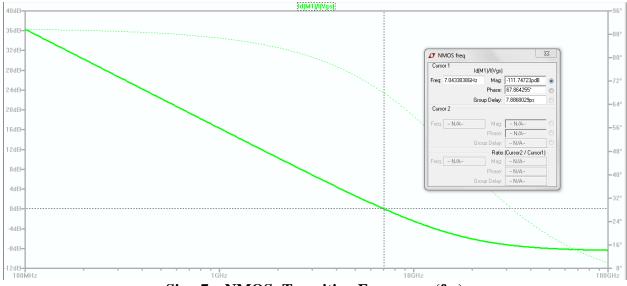

Determining the transition frequency  $(f_{Tn})$  of the NMOS is modeled in Schem. 7 in which VDS=VDS,sat(= Vovn)=350mV, VGS=1.063(AC 1), and an ac simulation is swept from 100MHz to 100GHz in order to show a clear plot.

The transition frequency  $(f_{Tn})$  is determined in Sim. 7 by plotting the drain current divided by the current through VGS ( $I_D/I_{VGS}$ ) which gives  $f_{Tn}=f_{un}=7.04$ GHz at 0dB.

Sim. 7 – NMOS: Transition Frequency (f<sub>Tn</sub>)

## **PMOS Characterization**

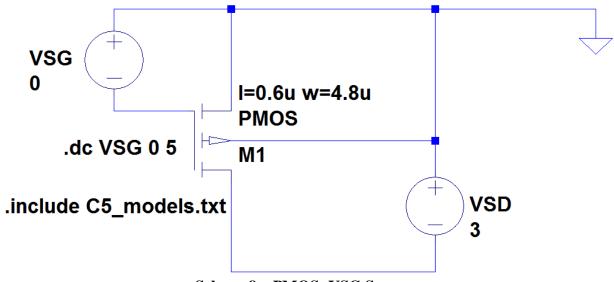

The purpose of this section is to sweep VSG in order to determine threshold voltage (Vthp) and bias voltage (Vbiasp=VSG) based on the NMOS bias current (Ibiasn=Ibiasp=31.2uA) to then determine output resistance ( $r_{op}$ ), transconductance ( $g_{mp}$ ), and transition frequency ( $f_T$ ) for the PMOS. **Schem. 8** shows the PMOS (4.8um/0.6um) with VSD=3V in order to characterize the PMOS on the lower end of VDD.

Schem. 8 – PMOS: VSG Sweep

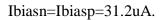

Sweeping VSG from 0V to 5V results in **Sim. 8** which shows VSG=Vthp=807mV (the voltage in which the PMOS turns on) as well as the voltage VSG=Vbiasp=1.274V at

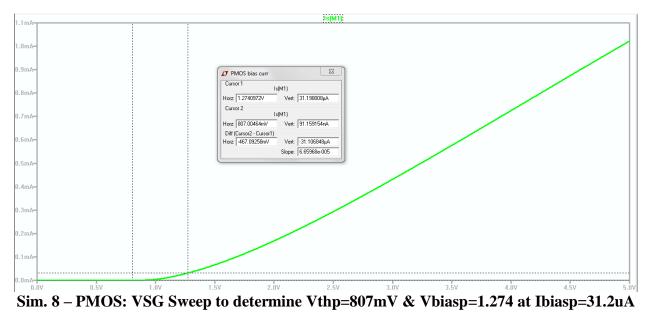

Schem. 9 shows the PMOS with VSG=Vbiasp=1.274V and VSD=3V, and Sim. 9 shows various

DC operating point values from the Spice error log including Vthp=886mV,  $g_{mp}$ =134uA/V,

$r_{op}=1/Gds=1/(3.43x10^{-6})=291,545\Omega$ , and VSD,sat=329mV.

Schem. 9 – PMOS: .op (DC Operating Point)

| ✓ SPICE                                 | SPICE Error Log: C:\Users\ |  |  |

|-----------------------------------------|----------------------------|--|--|

| Vth:                                    | -8.86e-01                  |  |  |

| Vdsat:                                  | -3.29e-01                  |  |  |

| Gm:                                     | 1.34e-04                   |  |  |

| Gds:                                    | 3.43e-06                   |  |  |

| Sim. 9 – PMOS: .op (DC Operating Point) |                            |  |  |

$\mathbf{Sim} \cdot \mathbf{y} = \mathbf{I} \cdot \mathbf{WOS} \cdot \mathbf{op} \left( \mathbf{DC} \cdot \mathbf{Operating I} \cdot \mathbf{Omt} \right)$

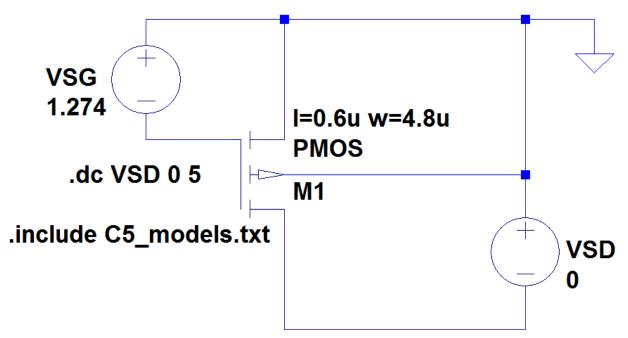

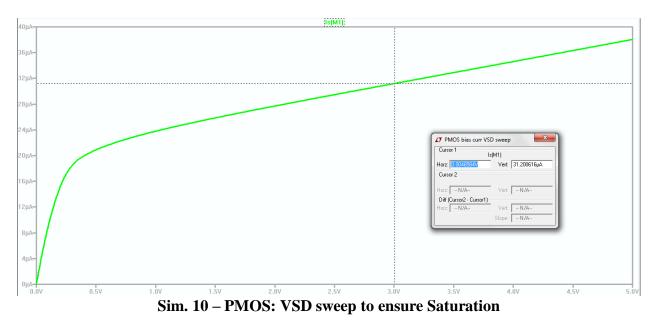

In order to ensure the PMOS is in saturation when Ibiasp=31.2uA at Vbiasp=1.274V, **Schem. 10** shows VSD being swept from 0V to 5V with VSG=1.274V. **Sim. 10** shows the PMOS is, in fact, in saturation when Ibiasp=31.2uA and gives VSD=3.005V.

Schem. 10 - PMOS: VSD sweep to ensure Saturation

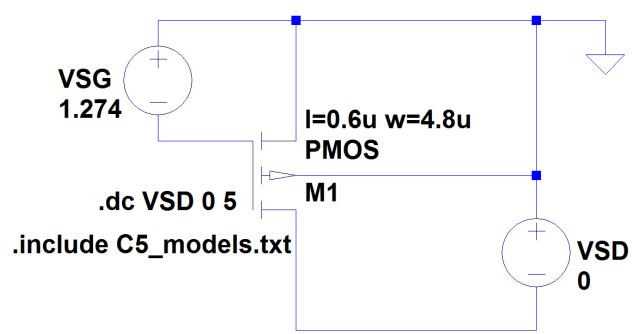

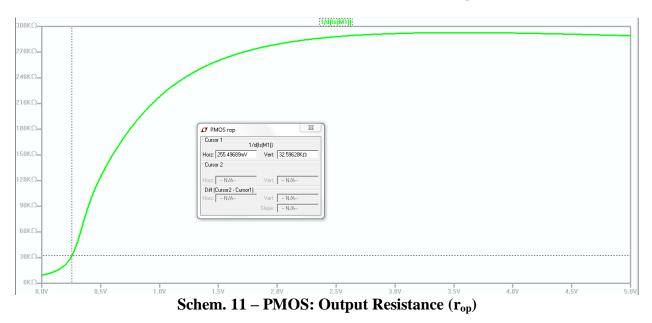

In order to determine the output resistance  $(r_{op})$  of the PMOS, **Schem. 11** shows VSD being swept from 0V to 5V with VSG=1.274V. **Sim. 11** shows the output resistance  $(r_{op})$  plotted as the reciprocal of the derivative of the drain current (1/deriv(I<sub>D</sub>)). VSD,sat is approximated as the voltage where the output resistance begins to increase. This results in VSD,sat=255.5mV (approx.) and gives  $r_{op}=32.6k\Omega$ .

Schem. 11 – PMOS: Output Resistance (r<sub>op</sub>)

**Table 2** shows values for rop at varying voltages of VSD

| VSD=0V          | $r_{op}=9.5k\Omega$   |

|-----------------|-----------------------|

| VSD,sat=255.5mV | $r_{op}=32.6k\Omega$  |

| VSD=3 V         | $r_{op}=291.7k\Omega$ |

| VSD=4 V         | $r_{op}=292.3k\Omega$ |

| VSD=5 V         | $r_{op}=289.0k\Omega$ |

Table  $2 - r_{op}$  for various values of VSD

Lambda can be calculated as  $\lambda_p = 1/(r_{op}*I_D) = 1/(r_{op}*Ibiasp)$  using  $r_{op} = 291.7 \text{k}\Omega$  @ VSD=3V from Sim. 11 and using Ibiasp=31.2uA  $\rightarrow$ :

$$\lambda_{p} = 1/(r_{op}*I_{D}) = 1/(r_{op}*I_{D}) = 1/((291.7k\Omega)*(31.2uA)) = 0.1099 V^{-1}$$

$$\circ \lambda_{p} = 0.1099 V^{-1}$$

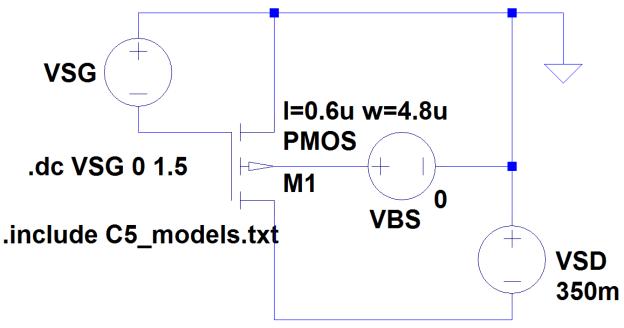

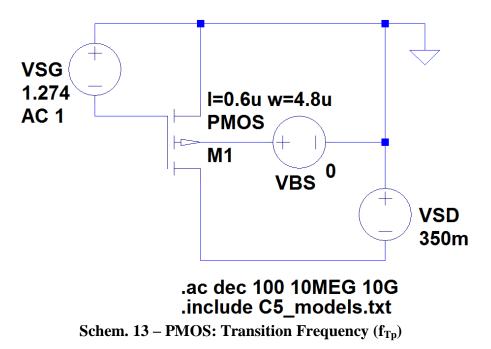

Determining the forward transconductance  $(g_{mp})$  of the PMOS is modeled in **Schem. 12** in which VSD=VSD,sat=350mV and VSG is swept from 0V to 1.5V in order to show a clear plot.

Schem. 12 – PMOS: Forward Transconductance (g<sub>mp</sub>)

Sim. 12 shows the transconductance  $(g_{mp})$  plotted as the derivative of the drain current (deriv(I<sub>D</sub>)) and gives  $g_{mp}=84.7$ uA/V at VGS=1.274V. The gain can then be calculated using  $r_{op}=291.7$ k $\Omega$  @ VSD=3V from Sim. 11 and using  $g_{mp}=84.7$ uA/V at VSG=1.274V from Sim. 12.

- $Gain=g_{mp}r_{op}=(84.7 \text{uA/V})*(291.7 \text{k}\Omega)=24.7 \text{V/V}$

- Gain=24.7V/V

Additionally, Schem. 1 can be referred to for Sim. 12-1 which shows  $g_{mp}=118.5uA/V$  for

VDS=VSD=VSG=Vbiasp=1.274V for W<sub>PMOS</sub>=4.8u.

Sim. 12-1 – PMOS: Forward Transconductance (g<sub>mp</sub>) (Referring to Schem. 1)

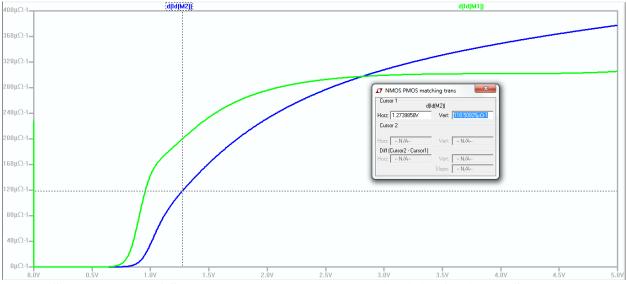

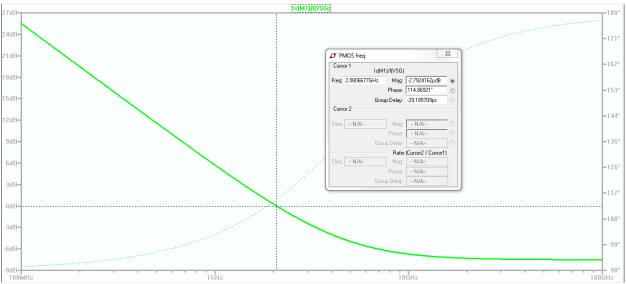

Determining the transition frequency  $(f_{Tp})$  of the PMOS is modeled in **Schem. 13** in which VSD=VSD,sat=350mV, VSG=1.274(AC 1), and an ac simulation is swept from 10MHz to 10GHz in order to show a clear plot.

The transition frequency  $(f_{Tp})$  is determined in Sim. 13 by plotting the drain current divided by

the current through VSG ( $I_D/I_{VSG}$ ) which gives  $f_{Tp}=f_{un}=2.08GHz$  at 0dB.

Sim. 13 – PMOS: Transition Frequency (f<sub>Tp</sub>)

# **Table Summary of Characterization**

| On's C5 Process MOSFET Parameters                                                 |                                                            |                                                                          |                                                                                      |

|-----------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| VDD=3V to 5V (VDD=3V Used) and a scale factor of 1um (scale= $1 \times 10^{-6}$ ) |                                                            |                                                                          |                                                                                      |

| Parameter                                                                         | NMOS                                                       | PMOS                                                                     | Comments                                                                             |

| Bias Current, I <sub>D</sub>                                                      | 31.2uA (=Ibiasn)                                           | 31.2uA (=Ibiasp)                                                         | Approximate, see <b>Sim.</b><br><b>2-1</b>                                           |

| W/L                                                                               | 3/0.6 (Min. length,<br>Min. width)                         | 4.8/0.6 (Min. length)                                                    | PMOS width based on Sim. 1                                                           |

| VDS,sat &<br>VSD,sat                                                              | *350mV (Vovn calc.)<br>*242mV ( <b>Sim. 3</b> )            | 329mV ( <b>Sim. 9</b> )                                                  |                                                                                      |

| VGS & VSG                                                                         | *1.063V (=Vbiasn)<br>(Calc. based on Vovn<br>& Vthn)       | *1.274V (=Vbiasp)<br>( <b>Sim. 8</b> – based on<br>Ibiasp=Ibiasn & Vthp) | No Body Effect                                                                       |

| Vthn & Vthp                                                                       | *713mV ( <b>Sim. 2</b> )<br>*699mV ( <b>Sim. 3</b> )       | *807mV ( <b>Sim. 8</b> )<br>*886mV ( <b>Sim. 9</b> )                     | Approx. & .op values                                                                 |

| g <sub>mn</sub> & g <sub>mp</sub>                                                 | *174uA/V ( <b>Sim. 3</b> )<br>*129.5uA/V ( <b>Sim. 6</b> ) | *134uA/V ( <b>Sim. 9</b> )<br>*84.7uA/V ( <b>Sim. 12</b> )               | Similar values for different sim's                                                   |

|                                                                                   | *163.3uA/V ( <b>Sim. 6-1</b> )                             | *118.5uA/V ( <b>Sim. 12-1</b> )                                          |                                                                                      |

| r <sub>on</sub> & r <sub>op</sub>                                                 | *403.2kΩ ( <b>Sim. 3</b> )                                 | *291.6kΩ ( <b>Sim. 9</b> )                                               | Similar values for different sim's                                                   |

|                                                                                   | *402.7kΩ (Refer to<br><b>Sim. 5 &amp; Table 1</b> )        | *291.7kΩ (Refer to <b>Sim.</b><br><b>11 &amp; Table 2</b> )              |                                                                                      |

| Gain:<br>g <sub>mn</sub> r <sub>on</sub> & g <sub>mp</sub> r <sub>op</sub>        | 52V/V                                                      | 24.7V/V                                                                  | <pre>!!Open circuit gain!! See calc. before Sim. 6 &amp; Sim. 12, respectively</pre> |

| $\lambda_n \& \lambda_p$                                                          | $0.0796V^{-1}$                                             | $0.1099 \mathrm{V}^{-1}$                                                 | See calculation after<br>Table 1 & Table 2                                           |

| f <sub>Tn</sub> & f <sub>Tn</sub>                                                 | 7.04GHz                                                    | 2.08GHz                                                                  | See Sim. 7 & Sim. 13                                                                 |

Table 3 was generated using the information captured from the previous simulations.

| Table 3 - | On's C5 | Process | MOSFET | Parameters |

|-----------|---------|---------|--------|------------|

|-----------|---------|---------|--------|------------|

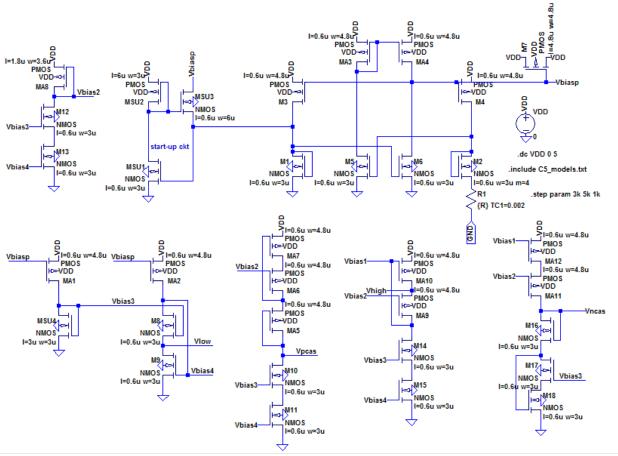

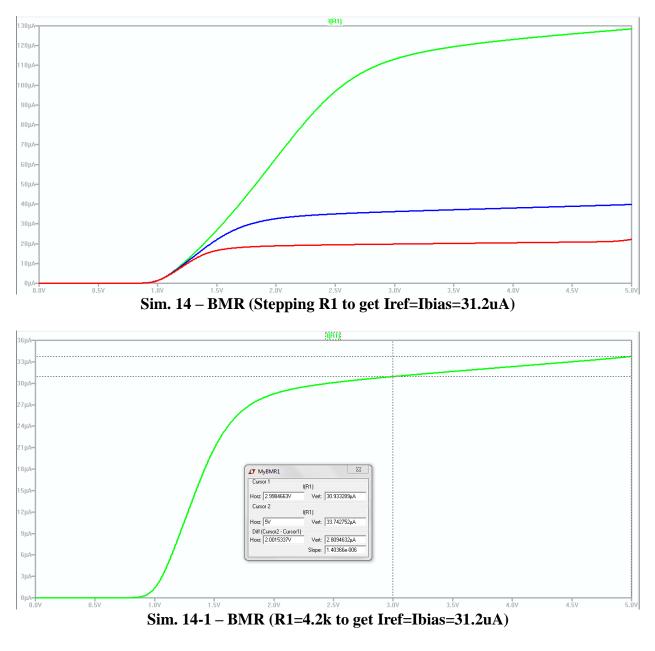

### Beta-Multiplier Reference (BMR)

The Beta-Multiplier Reference (BMR) in Fig. 20.47 of the CMOSedu book was used to generate the BMR shown in **Schem. 14.** Except for a few different sized devices, all the NMOS are 3u/0.6u and the PMOS are 4.8u/0.6u. The PMOS in the startup circuit (MSU2) is meant to operate as a large resistor, so its length is greatly increased in order to prevent MSU3 from turning on, preventing Vbiasp from stealing current from Vbiasn. **Schem. 14** shows the resistor (R1) being stepped for different values in order to determine which resistor value results in Iref=Ibiasn=Ibiasp=31.2uA. **Sim. 14** shows R1=4.2k sets Iref=Ibiasn=Ibiasp=31.2uA.

Schem. 14 – BMR (Stepping R1 to get Iref=Ibias=31.2uA)

## **Voltage Follower: Design 1**

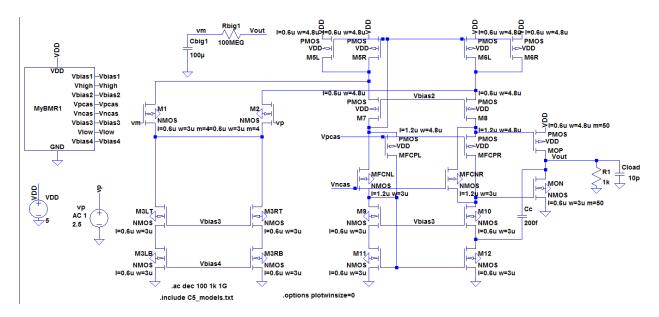

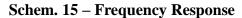

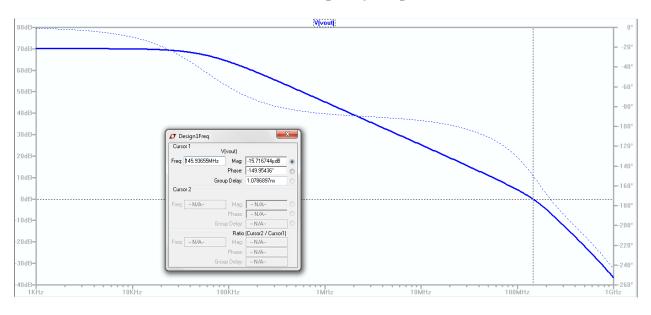

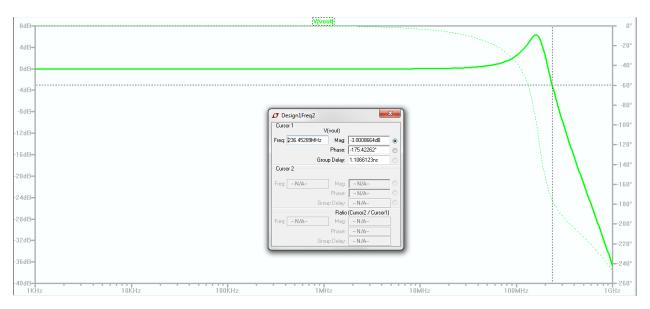

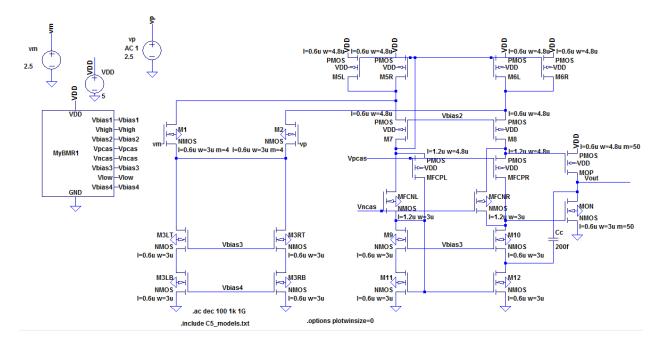

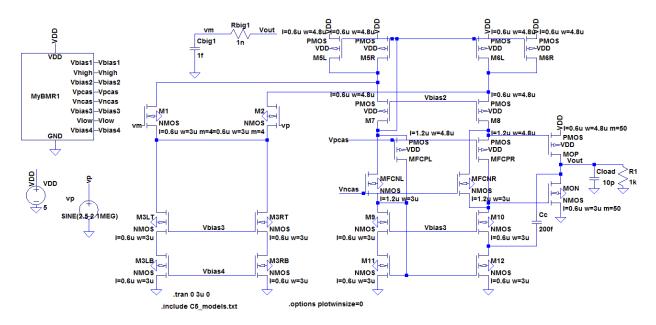

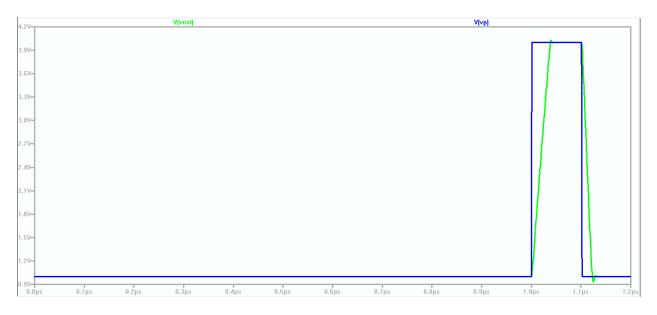

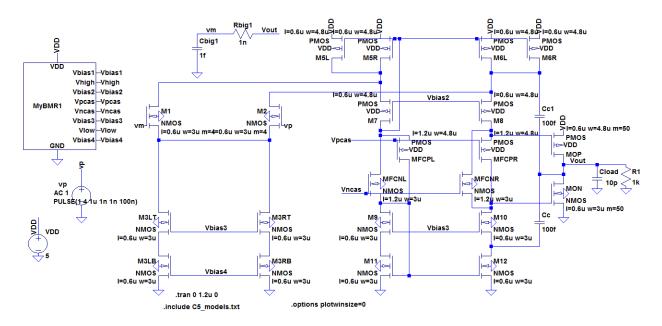

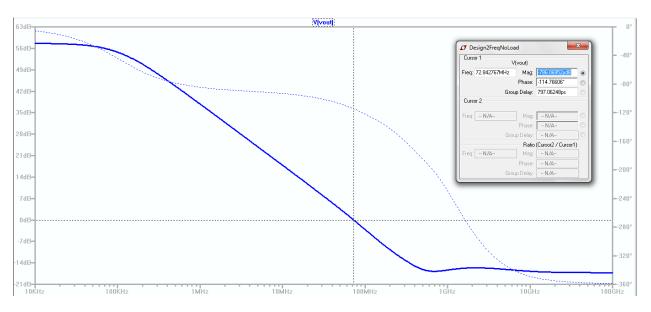

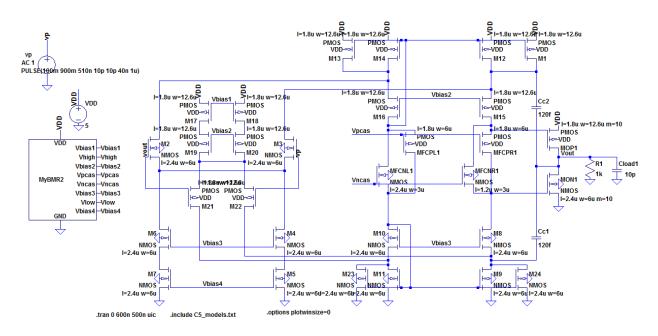

The op-amp design in Fig. 20.44 from the CMOSedu book was used as a starting point for the design of the voltage follower for Design 1. Except for a few different sized devices, all the NMOS are 3u/0.6u and the PMOS are 4.8u/0.6u. **Sim. 15** corresponding to **Schem. 15** shows the unity gain frequency at 0dB and gives  $f_{un}=145.9$ MHz.

Gentry, Dane 24 EE 420: Final Project – Spring 2016

Sim. 15 – Frequency Response (f<sub>un</sub>=145.9MHz)

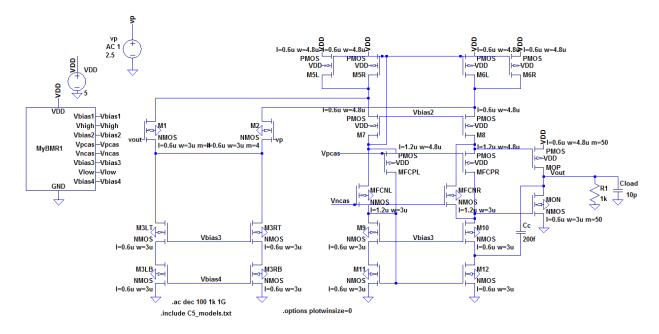

Sim. 16 – Frequency Response

Sim. 17 – Frequency Response

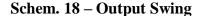

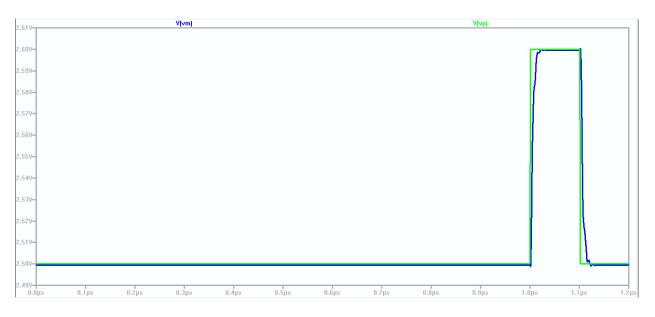

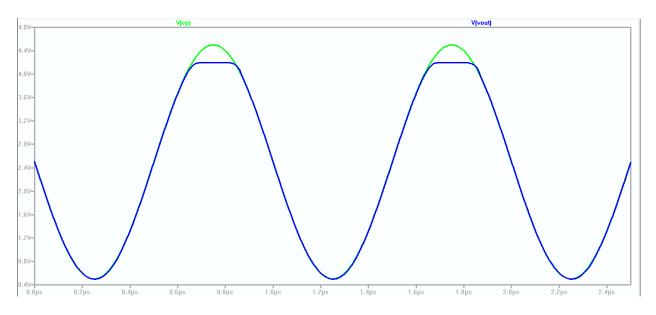

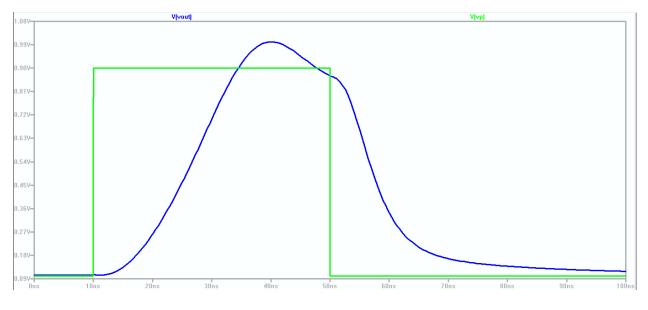

Schem. 18 and the corresponding Sim. 18 show the output swing of voltage follower for Design 1. The output closely follows the input, but there is unwanted clipping on the bottom swing of the output.

Gentry, Dane 27 EE 420: Final Project – Spring 2016

Sim. 18 – Output Swing

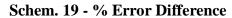

Schem. 19 and Sim. 19 shows a pulse input and the corresponding output. This is used to calculate the percent error difference as ((Vin-Vout)/(Vin+Vout))\*100. The percent error difference for Design 1 can then be calculated from Sim. 19 as ((4.0014-4)/(4.0014+4))\*100 = 0.012%.

$$\Rightarrow$$

% Error = 0.012%.

Gentry, Dane 28 EE 420: Final Project – Spring 2016

Sim. 19 - % Error Difference = 0.012%

Gentry, Dane 29 EE 420: Final Project – Spring 2016

Sim. 20 % - Error Difference

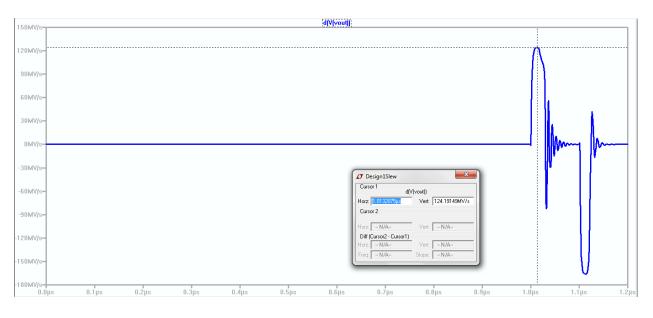

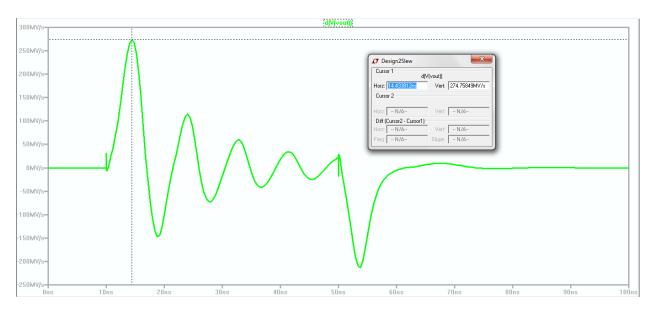

**Schem. 21** and **Sim. 21** show the slew rate of the output by plotting the derivative of the output voltage (deriv(vout)). **Sim. 21** shows the slew rate for Design 1 is 124.2MV/s=124.2V/us.

Gentry, Dane 30 EE 420: Final Project – Spring 2016

Schem. 21 – Slew Rate

Sim. 21 - Slew Rate=124.2MV/s=124.2V/us

Sim. Design 1 .op shows the total current draw from VDD for Design 1 as I(VDD)=2.55mA.

|           | e\Documents\DLG\Schoo | I\Spring 2016\EE 420\P |

|-----------|-----------------------|------------------------|

| Is(M51):  | 2.001e-005            | device_current         |

| Id(M61):  | -2.00334e-005         | device_current         |

| Ig(M61):  | 0                     | device_current         |

| Ib(M61):  | 6.6136e-013           | device_current         |

| Is(M61):  | 2.00334e-005          | device_current         |

| Id(M6r):  | -2.00334e-005         | device_current         |

| Ig(M6r):  | 0                     | device_current         |

| Ib(M6r):  | 6.6136e-013           | device current         |

| Is(M6r):  | 2.00334e-005          | device current         |

| I(Cc1):   | 3.34898e-025          | device current         |

| I(Cbig1): | 9.99661e-028          | device current         |

| I(Cc):    | 4.69478e-026          | device current         |

| I(Cload): | 9.99661e-024          | device current         |

| I(R1):    | 0.000999661           | device current         |

| I(Rbig1): | -1.11022e-007         | device_current         |

| I(Vp):    | 0                     | device_current         |

| I (Vdd):  | -0.0025461            | device current         |

|           |                       | -                      |

Sim. Design 1 .op – Total Current Draw from VDD

### Voltage Follower: Design 2

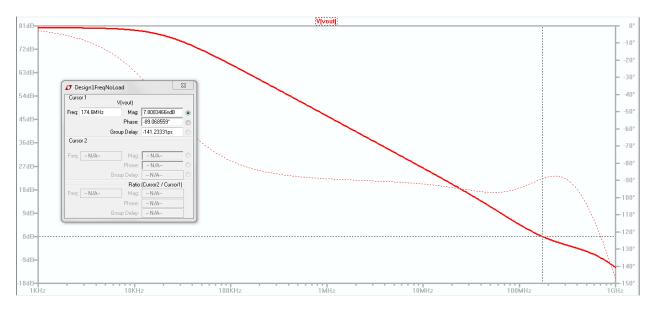

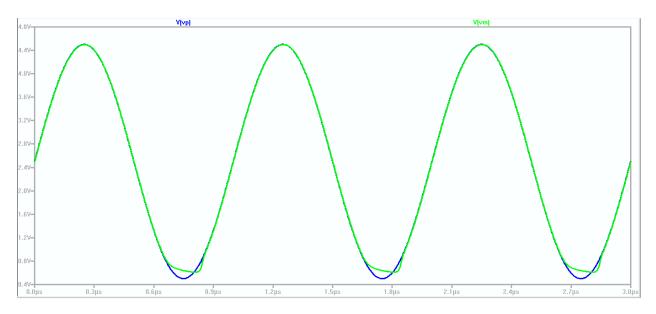

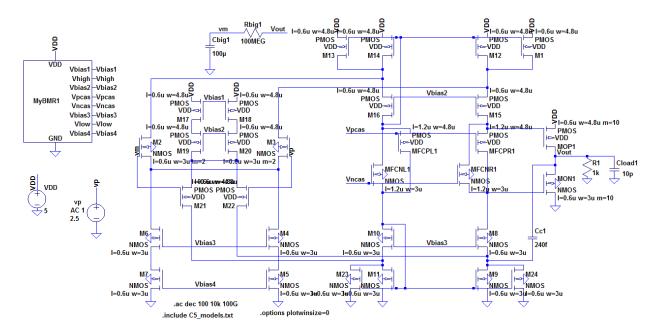

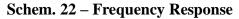

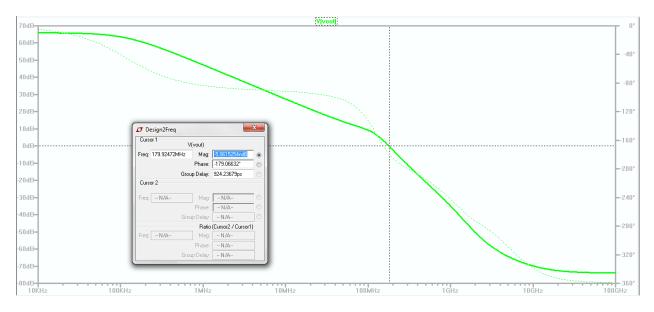

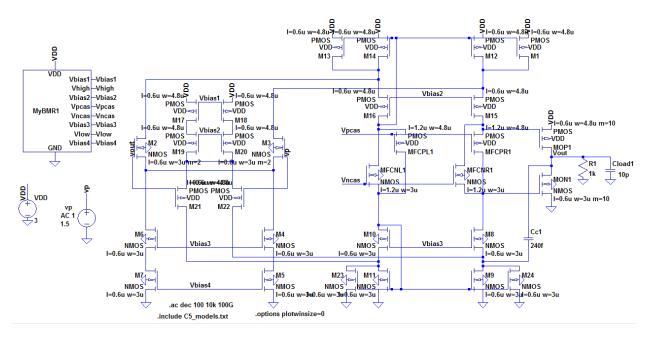

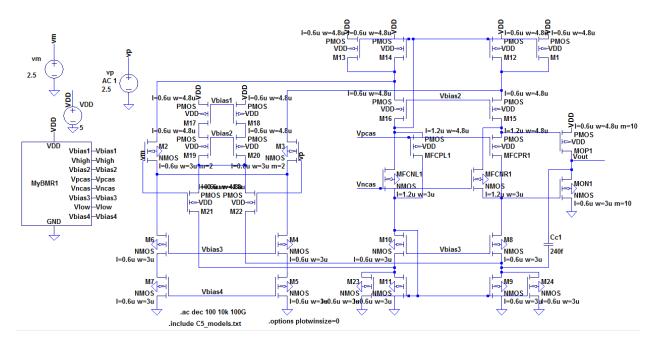

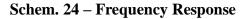

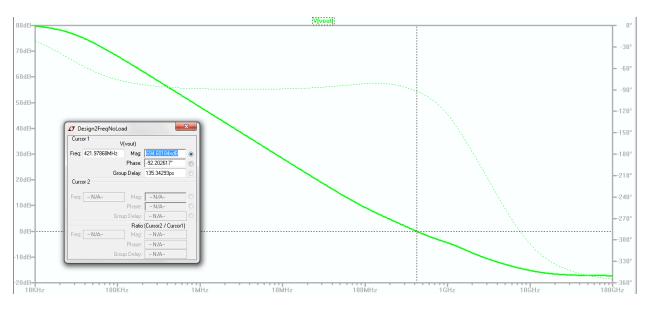

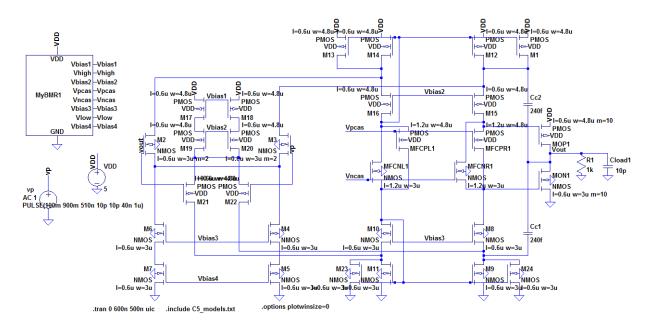

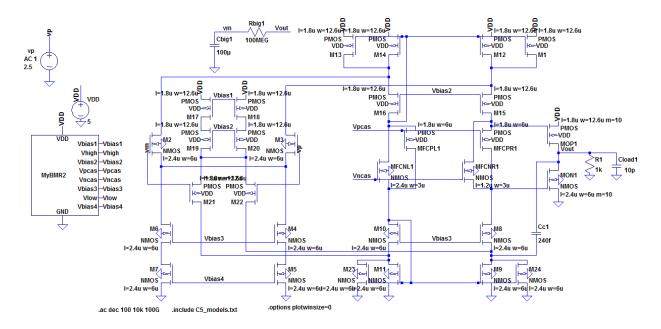

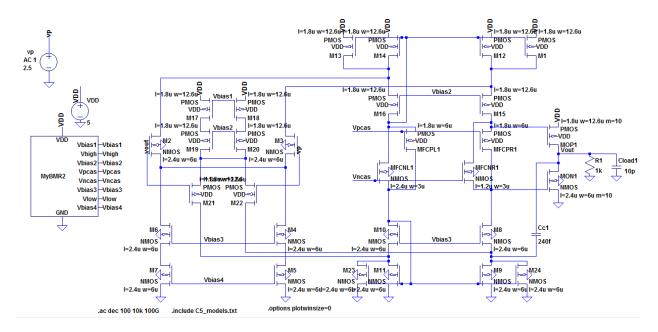

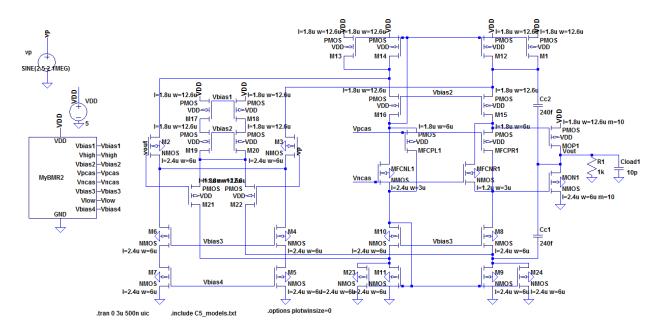

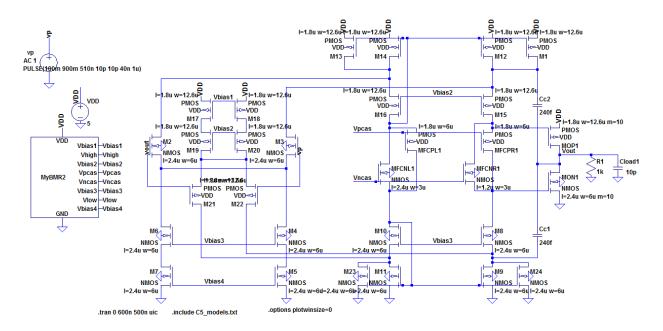

The op-amp design in Fig. 20.48 from the CMOSedu book was used as a starting point for the design of the voltage follower for Design 2. Except for a few different sized devices, all the NMOS are 3u/0.6u and the PMOS are 4.8u/0.6u. The width of the NMOS diff-pair is increased by setting m=2 for both the NMOS in the NMOS diff-pair. The NMOS and PMOS on the output act as a push-pull amplifier, and their widths are each increased by setting m=10. **Sim. 22** corresponding to **Schem. 22** shows the unity gain frequency at 0dB and gives  $f_{un}=179.9$ MHz.

Sim. 22 – Frequency Response(f<sub>un</sub>=179.9MHz)

Schem. 23 – Frequency Response

Sim. 23 – Frequency Response

Sim. 24 – Frequency Response

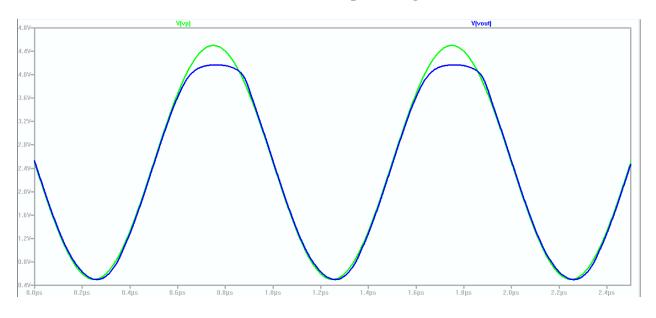

Schem. 25 and the corresponding Sim. 25 show the output swing of voltage follower for Design 2.

Schem. 25 – Output Swing

Sim. 25 – Output Swing

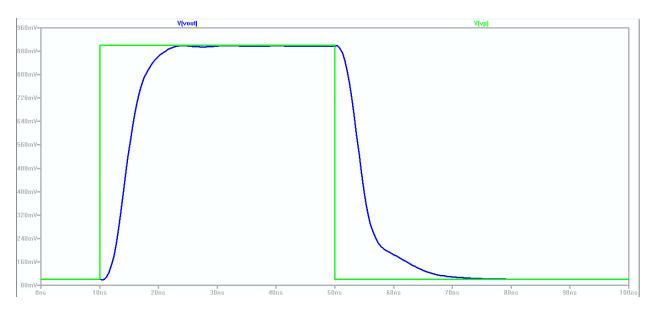

Schem. 26 and Sim. 26 shows a pulse input and the corresponding output. This is used to calculate the percent error difference as ((Vin-Vout)/(Vin+Vout))\*100. The percent error difference for Design 1 can then be calculated from Sim. 26 as ((0.9-0.8973)/(0.9+0.8973))\*100 = 0.15%.

$$\Rightarrow$$

% Error = 0.15%

Schem. 26 - % Error Difference

Sim. 26 - % Error Difference=0.15%

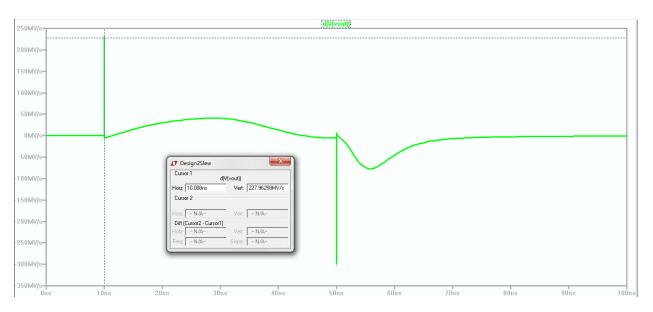

**Schem. 27** and **Sim. 27** show the slew rate of the output by plotting the derivative of the output voltage (deriv(vout)). **Sim. 27** shows the slew rate for Design 2 is 274.8MV/s=274.8V/us.

Gentry, Dane 37 EE 420: Final Project – Spring 2016

Schem. 27 – Slew Rate

Sim. 27 – Slew Rate=274.8MV/s=274.8V/us

Sim. Design 2 .op shows the total current draw from VDD for Design 2 as I(VDD)=739uA.

| * C:\Users\Dane\Documents\DLG\School\Spring 2016\EE 420\P |               |                |

|-----------------------------------------------------------|---------------|----------------|

| Ig(M13):                                                  | 0             | device_current |

| Ib(M13):                                                  | 6.3883e-013   | device_current |

| Is(M13):                                                  | 1.40852e-005  | device_current |

| Id(M12):                                                  | -1.40823e-005 | device_current |

| Ig(M12):                                                  | 0             | device_current |

| Ib(M12):                                                  | 6.38102e-013  | device_current |

| Is(M12):                                                  | 1.40823e-005  | device_current |

| Id(M1):                                                   | -1.40823e-005 | device_current |

| Ig(M1):                                                   | 0             | device_current |

| Ib(M1):                                                   | 6.38102e-013  | device_current |

| Is(M1):                                                   | 1.40823e-005  | device_current |

| I(Cc2):                                                   | 1.02522e-024  | device_current |

| I(Cc1):                                                   | -1.01888e-025 | device_current |

| I(Cload1):                                                | 1.00167e-024  | device_current |

| I(R1):                                                    | 0.000100167   | device_current |

| I(Vp):                                                    | 0             | device_current |

| I(Vdd):                                                   | -0.000739147  | device_current |

Sim. Design 2 .op – Total Current Draw from VDD

## **Voltage Follower: Design 3**

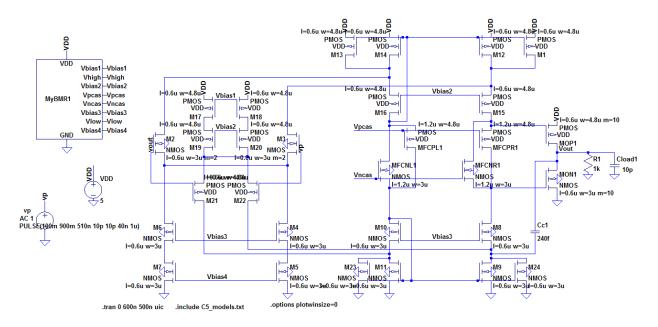

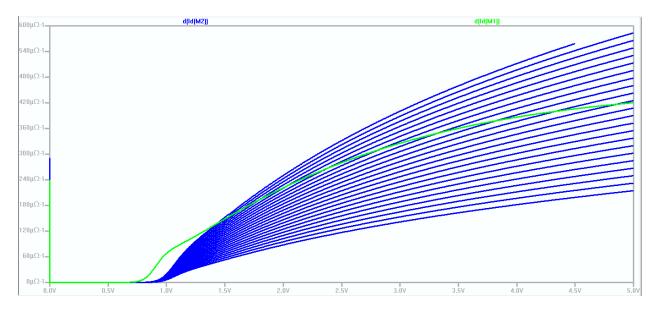

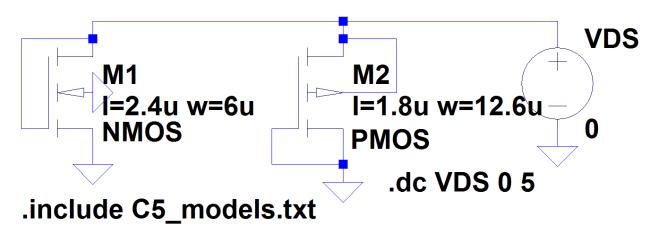

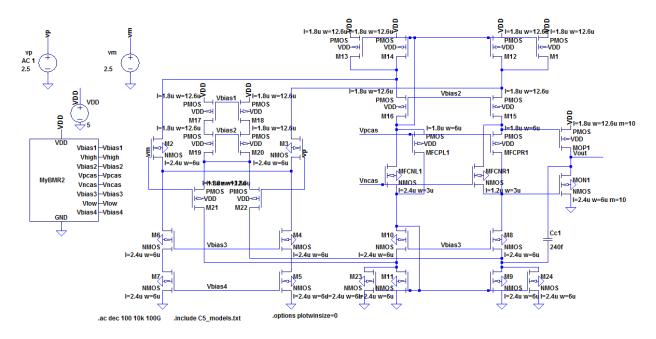

The op-amp design in Fig. 20.48 from the CMOSedu book was used as a starting point for the design of the voltage follower for Design 3. The use of minimum sizes (Lmin=0.6um, Wmin=3um) in Design 1 and Design 2 resulted in poor performance in certain aspects and did not meet all the required specifications due to certain characteristics related to minimum sizing including low gain. Design 3 was implemented by choosing the NMOS size to be 6u/2.4u. Matching the transconductances of a 6u/2.4u NMOS to a PMOS with a length of 1.8u is shown in **Schem. 28** and **Sim. 28** in which the width of the PMOS is stepped to determine what width of the PMOS gives the best matching of transconductances. **Schem 29** and **Sim. 29** show the PMOS width should be chosen to be 12.6u.

Schem. 28 - Matching NMOS & PMOS Transconductances (gmn & gmp)

Sim. 28 - Matching NMOS & PMOS Transconductances (gmn & gmp)

Schem. 29 - Matching NMOS & PMOS Transconductances (g<sub>mn</sub> & g<sub>mp</sub>) (W<sub>PMOS</sub>=12.6u)

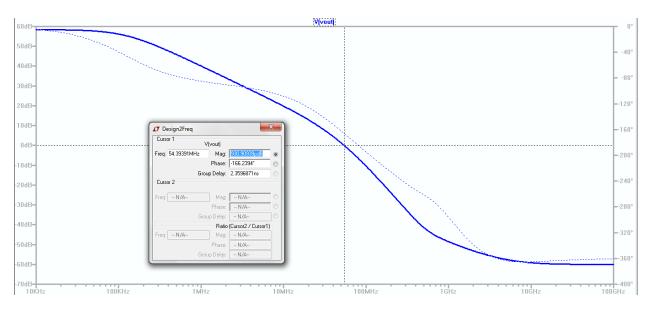

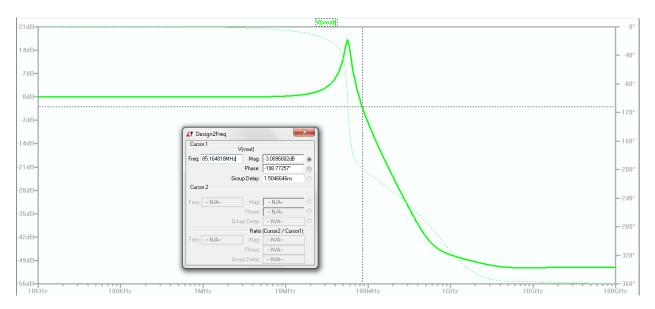

Sim. 29 - Matching NMOS & PMOS Transconductances ( $g_{mn} \& g_{mp}$ ) ( $W_{PMOS}$ =12.6u) Except for a few different sized devices, Design 3 was implemented with all the NMOS sized as 6u/2.4u and the PMOS sized as 12.6u/1.8u. The width of the NMOS diff-pair is increased by setting m=2 for both the NMOS in the NMOS diff-pair. The NMOS and PMOS on the output act as a push-pull amplifier, and their widths are each increased by setting m=10. Sim. 29 corresponding to Schem. 29 shows the unity gain frequency at 0dB and gives f<sub>un</sub>=54.4MHz.

Sim. 30 – Frequency Response (f<sub>un</sub>=54.4MHz)

Schem. 31 – Frequency Response

Sim. 31 – Frequency Response

Sim. 32 – Frequency Response

Schem. 33 and the corresponding Sim. 33 show the output swing of voltage follower for Design 3.

Schem. 33 – Output Swing

Sim. 33 – Output Swing

Schem. 34 and Sim. 34 shows a pulse input and the corresponding output. This is used to calculate the percent error difference as ((Vin-Vout)/(Vin+Vout))\*100. The percent error difference for Design 1 can then be calculated from Sim. 26 as ((1-0.9)/(1+0.9))\*100 = 5.26%.

Schem. 34 - % Error Difference

Sim. 34 % - Error Difference=5.26%

**Schem. 35** and **Sim. 35** show the slew rate of the output by plotting the derivative of the output voltage (deriv(vout)). **Sim. 35** shows the slew rate for Design 3 is 228.0MV/s=228.0V/us.

Schem. 35 – Slew Rate

Sim. 35 – Slew Rate=228.0MV/s=228.0V/us

Sim. Design 3 .op shows the total current draw from VDD for Design 3 as I(VDD)=1.67mA.

| Ig(M13):   | 0             | device_current |

|------------|---------------|----------------|

| Ib(M13):   | 7.90083e-013  | device_current |

| Is(M13):   | 4.41243e-005  | device_current |

| Id(M12):   | -4.40965e-005 | device_current |

| Ig(M12):   | 0             | device_current |

| Ib(M12):   | 7.83662e-013  | device_current |

| Is(M12):   | 4.40965e-005  | device_current |

| Id(M1):    | -4.40965e-005 | device_current |

| Ig(M1):    | 0             | device_current |

| Ib(M1):    | 7.83662e-013  | device_current |

| Is(M1):    | 4.40965e-005  | device_current |

| I(Cc2):    | 4.94594e-025  | device_current |

| I(Cc1):    | -4.20326e-026 | device_current |

| I(Cload1): | 1.04722e-024  | device_current |

| I(R1):     | 0.000104722   | device_current |

| I(Vp):     | 0             | device_current |

| I (Vdd) :  | -0.00167199   | device_current |

| ·          |               |                |

Sim. Design 3 .op – Total Current Draw from VDD

## **Table Summary of Design Results**

**Design 1 Design 3 Design 2** f<sub>un</sub> 145.9MHz 54.4MHz 179.9MHz % Error 0.012% 0.15% 5.26% 274.8V/us **Slew Rate** 124.2V/us 228.0V/us **Current Draw** 2.55mA 739uA **1.67mA** from VDD

Table 4 summarizes some important performance information for the three designs

Table 4 – Performance of the three designs

## Conclusion

Of the three designs included in this report, the first design (Design 1) performed the best as it was closest to the required specifications, though it did not meet every specification. Design 2 had the largest unity gain frequency while Design 1 had the lowest percent error difference. In addition, Design 2 had the largest slew rate yet lowest total current drawn from VDD while Design 1 had the smallest slew rate and largest total current drawn from VDD. In regard to the simulations presented in this report for each of the three designs, Design 1 seems to have the best overall performance in regard to meeting the required specifications. Much experience and knowledge was gained from this project, and over time I gained a good understanding of the expectations of the project as well as the process necessary in fulfilling these expectations. With more time, I would have continued trying different sizes based on known tradeoffs such as gain and speed in order to get my BMR to have better biasing for my design circuit. I encountered numerous issues throughout the project including designing the overall voltage follower to meet all the design requirements and perform as well as possible, and LTSpice presented a great deal of various problems especially in generating symbols for schematics in a hierarchy, but after much time and frustration, I was able to improve each of my designs. Despite any setbacks, many issues were overcome with time and yielded a better knowledge of LTSpice and circuit design in general. Having successfully completed this course project has certainly resulted in my becoming a more confident and experienced circuit designer as well as engineer.

## References

[1] Baker, R. J., CMOS: Circuit Design, Layout, and Simulation, 3<sup>rd</sup> ed., IEEE Press. John

Wiley & Sons Inc. 2010.