US007449953B2

# (12) United States Patent

Staples et al.

### (10) Patent No.: US

US 7,449,953 B2

(45) **Date of Patent:**

\*Nov. 11, 2008

## (54) INPUT BUFFER DESIGN USING COMMON-MODE FEEDBACK (CMFB)

(75) Inventors: Travis Staples, Meridian, ID (US);

Jacob Baker, Boise, ID (US)

(73) Assignee: Micron Technology, Inc., Boise, ID

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 11/979,327

(22) Filed: Nov. 1, 2007

(65) **Prior Publication Data**

US 2008/0061880 A1 Mar. 13, 2008

### Related U.S. Application Data

- (63) Continuation of application No. 11/208,858, filed on Aug. 23, 2005, now Pat. No. 7,310,018.

- (51) Int. Cl. *H03F 3/45* (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,5    | 571,554 | A *  | 2/1986  | Martin et al    | 330/252 |

|--------|---------|------|---------|-----------------|---------|

| 4,9    | 58,133  | A    | 9/1990  | Bazes           |         |

| 6,4    | 186,713 | B2   | 11/2002 | Wright et al.   |         |

| 6,8    | 306,743 | B2   | 10/2004 | Saito et al.    |         |

| 6,9    | 940,328 | B2   | 9/2005  | Lin             |         |

| 7,0    | 53,712  | B2 * | 5/2006  | Bonaccio et al  | 330/258 |

| 7,1    | 64,615  | B2 * | 1/2007  | Park et al      | 365/222 |

| 2002/0 | 011877  | A1   | 1/2002  | Lim             |         |

| 2005/0 | 243644  | A1   | 11/2005 | Taruishi et al. |         |

|        |         |      |         |                 |         |

#### FOREIGN PATENT DOCUMENTS

| .IP | 407307625 A | * 11/1995 | 330/258 |

|-----|-------------|-----------|---------|

\* cited by examiner

Primary Examiner—Henry K Choe (74) Attorney, Agent, or Firm—Dickstein Shapiro LLP

### (57) ABSTRACT

An input buffer includes a first stage for receiving an input signal and having a first pair of complementary output signals, the first stage including an input circuit for receiving the input signal, an output circuit for generating the first pair of complementary output signals based on the input signal, a resistance feedback circuit connected to the first pair of complementary output signals and generating a feedback signal, and a common mode circuit for balancing the complementary outputs based on the feedback signal.

### 25 Claims, 6 Drawing Sheets

Nov. 11, 2008

FIG. 1A

### **BACKGROUND ART**

FIG. 1B

### **BACKGROUND ART**

FIG. 1C

FIG. 2

BACKGROUND ART

FIG. 4

FIG. 5

1

## INPUT BUFFER DESIGN USING COMMON-MODE FEEDBACK (CMFB)

## CROSS REFERENCE TO RELATED APPLICATIONS

The present application is a continuation of U.S. patent application Ser. No. 11/208,858, filed on Aug. 23, 2005, now U.S. Pat. No. 7,310,018 the disclosure of which is incorporated by reference in its entirety.

### FIELD OF THE INVENTION

The present invention relates to an input buffer design.

### BACKGROUND OF THE INVENTION

Input buffers driven with single-ended signals, yet having differential outputs can be used, for instance, in signal processing where a signal must be transmitted over long distances with minimal signal degradation due to interference from external sources, i.e. noise. The differential output signal is produced to be output over two lines as a positive and negative form of the input signal. Because any signal noise would most likely affect both lines equally, the noise component may be removed from the signal by subtracting the two outputs.

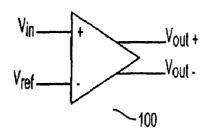

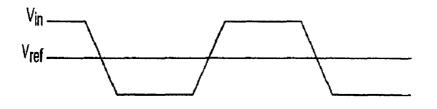

One problem associated with input buffers driven with single-ended input signals is ensuring a balanced differential output. FIG. 1A illustrates a schematic of a conventional 30 input buffer 100 depicted as an operational amplifier. The amplifier 100 receives an input voltage Vin at a positive terminal and a reference voltage Vref at a negative terminal. The amplifier 100 outputs differential outputs Vout+, Vout-based on the input voltage Vin. As shown in FIG. 1B, when the input 35 buffer is used as a comparator, the input signal Vin received by the conventional input buffer 100 may oscillate around the reference voltage Vref. FIG. 1C shows the differential outputs Vout+, Vout- from the conventional input buffer 100. As shown, the outputs Vout+, Vout- are not balanced; i.e., Vout- 40 should be the exact inverse of Vout+, such that the crossing points 150 of the two output signals Vout+, Vout-occur where if the output signals Vout+, Vout- were added, the net result would be zero.

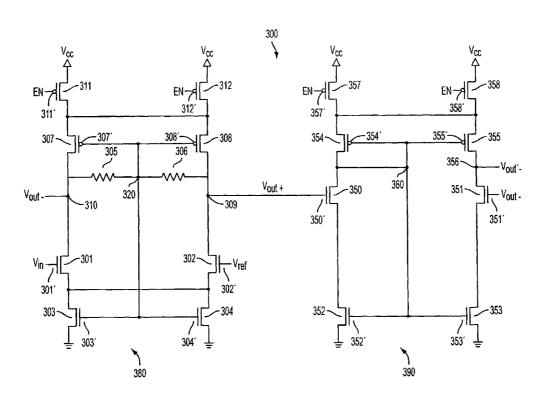

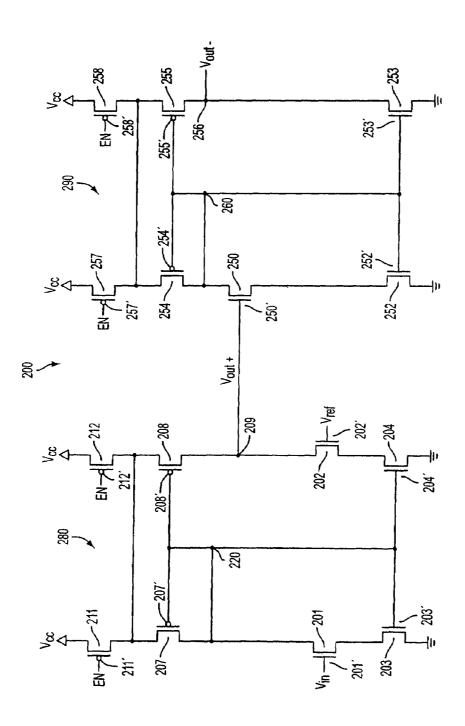

FIG. 2 illustrates a circuit diagram of a conventional input 45 buffer 200 that is driven with single-ended signals Vin and Vref and generates an unbalanced negative output signal Vout-. Input buffer 200 includes a first stage circuit 280 and a second stage circuit 290. The first stage circuit 280 includes a first input transistor 201 for receiving the input signal Vin at 50 a gate terminal 201', a second input transistor 202 for receiving a reference voltage Vref at a gate terminal 202', first and second general feedback transistors 203, 204 having associated gates 203', 204', and third and fourth general feedback transistors 207, 208 with associated gates 207', 208'. The 55 gates 203', 204' of the first and second general feedback transistors 203, 204 are electrically connected to each other, and the gates 207', 208' of the third and fourth general feedback transistors 207, 208 are electrically connected to each other. Also, a drain terminal of each of the third and fourth 60 general feedback transistors 207, 208 is respectively electrically connected to a source terminal of each of the first and second input transistors 201, 202. The first stage circuit 280 further includes an output node 209 at which positive output Vout+ is generated. The output node 209 is electrically con- 65 nected to the drain terminal of the fourth general feedback transistor 208 and to the source terminal of the second input

2

transistor 202. In addition, first stage circuit 280 includes a first connection node 220 which is connected to a drain terminal of the third general feedback transistor 207, to a source terminal of the first input transistor 201, to the gates 203', 204' of the first and second general feedback transistors 203, 204, and to the gates 207', 208' of the third and fourth general feedback transistors 207, 208.

Enable transistors 211, 212 may be connected between a power source Vcc and a source terminal of the third and fourth general feedback transistors 207, 208. The enable transistors 211, 212 receive an enable signal EN at a gate terminal 211', 212' to activate the first stage circuit 280.

The second stage circuit 290 includes a third input transistor 250 for receiving the output voltage Vout+ at a gate terminal 250', fifth and sixth general feedback transistors 252, 253 having associated gates 252', 253', and seventh and eighth general feedback transistors 254, 255 with associated gates 254', 255'. The gates 252', 253' of the fifth and sixth general feedback transistors 252, 253 are electrically connected to each other, and the gates 254', 255' of the seventh and eighth general feedback transistors 254, 255 are electrically connected to each other. Also, a drain terminal of the seventh general feedback transistor 254 is electrically connected to a source terminal of the third input transistor 250, and a drain terminal of the eighth general feedback transistor 255 is electrically connected to a source terminal of the sixth general feedback transistor 253. The second stage circuit 290 further includes an output node 256 at which negative output Vout- is generated. The output node 256 is electrically connected to the drain terminal of the eighth general feedback transistor 255 and to the source terminal of the sixth general feedback transistor 253. In addition, second stage circuit 290 includes a second connection node 260 which is connected to a drain terminal of the seventh general feedback transistor 254, to a source terminal of the third input transistor 250, to the gates 252', 253' of the fifth and sixth general feedback transistors 252, 253, and to the gates 254', 255' of the seventh and eighth general feedback transistors 254, 255.

Enable transistors 257, 258 may be connected between a power source Vcc and a source terminal of each of the third and fourth general feedback transistors 254, 255. The enable transistors 257, 258 receive an enable signal EN at a gate terminal 257', 258' to activate the second stage circuit 290.

The configuration of the conventional input buffer driven with single-ended signals and outputting only negative output signals generates unbalanced positive and negative output signals, such as that illustrated in FIG. 1C. Accordingly, there is a desire for a input buffer driven with single-ended signals that generates a better balanced differential output.

### BRIEF SUMMARY OF THE INVENTION

The present invention provides exemplary embodiments in which common mode feedback is used to obtain an optimized balanced differential output from an input buffer driven by a single-ended input signal.

One exemplary embodiment provides an input buffer, and method of forming the input buffer, having a first stage for receiving an input signal and having a first pair of complementary output signals, the first stage including an input circuit for receiving the input signal, an output circuit for generating the first pair of complementary output signals based on the input signal, a resistance feedback circuit connected to the first pair of complementary output signals and generating a feedback signal, and a common mode circuit for balancing the complementary outputs based on the feedback signal.

3

### BRIEF DESCRIPTION OF THE DRAWINGS

Other features and advantages of the present invention will become apparent from the following description of the invention which refers to the accompanying drawings, in which:

FIG. 1A is a schematic of a conventional input buffer;

FIG. 1B is a voltage chart illustrating exemplary input voltages of a conventional input buffer;

FIG. 1C is a voltage chart illustrating output voltages of a conventional input buffer based on exemplary input voltages; 10

FIG. 2 is a circuit diagram of a conventional input buffer; FIG. 3 is a circuit diagram of an input buffer constructed in

accordance with an exemplary embodiment of the present invention;

FIG. 4 is a voltage chart of the output voltages of an input 15

buffer constructed in accordance with an exemplary embodiment of the present invention;

FIG. 5 is a block diagram of a synchronous memory device incorporating an input buffer constructed in accordance with an exemplary embodiment of the present invention; and

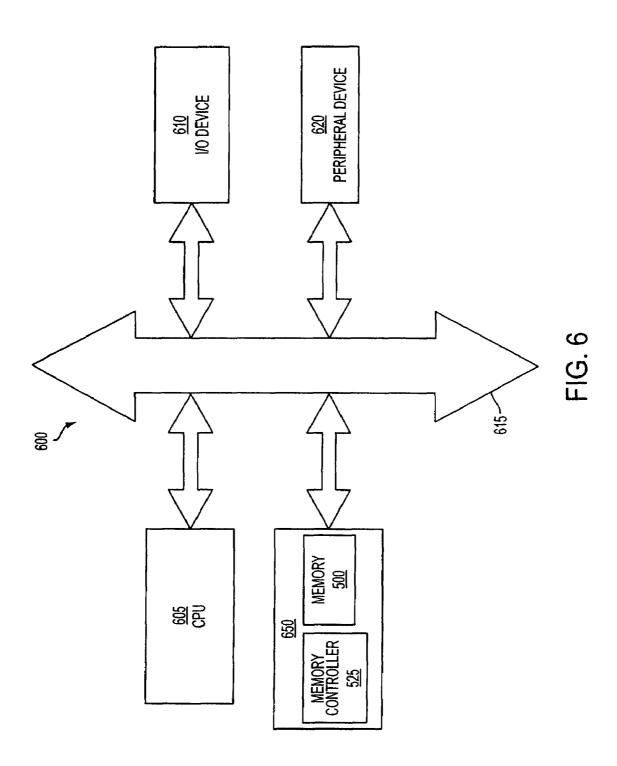

FIG. 6 is a schematic diagram of a processing system employing a synchronous memory device having an input buffer an input buffer constructed in accordance with an exemplary embodiment of the present invention.

### DETAILED DESCRIPTION OF THE INVENTION

In the following detailed description, reference is made to the accompanying drawings, which form a part hereof and show by way of illustration specific embodiments in which 30 the invention may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice the invention, and it is to be understood that other embodiments may be utilized, and that structural, logical, and electrical changes may be made without departing from the 35 spirit and scope of the present invention. The progression of processing steps described is exemplary of embodiments of the invention; however, the sequence of steps is not limited to that set forth herein and may be changed as is known in the art, with the exception of steps necessarily occurring in a certain 40 order.

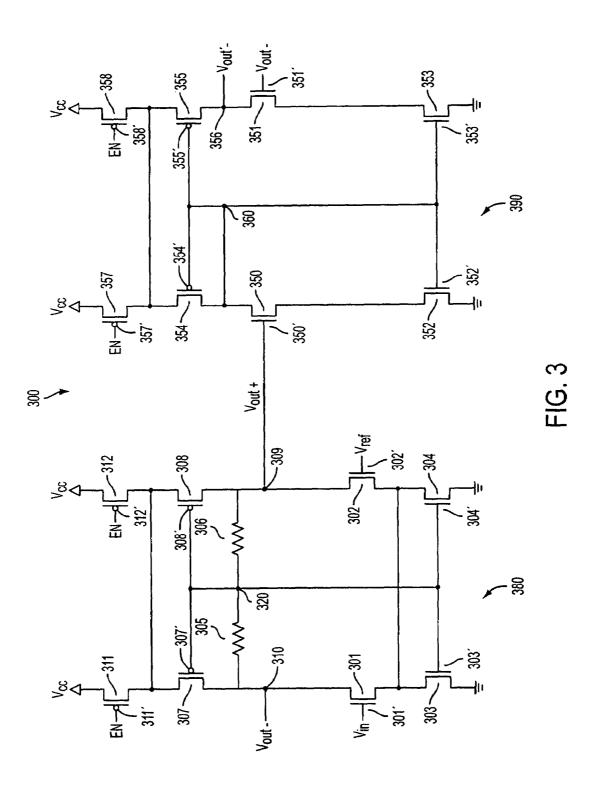

Now referring to the figures, where like numerals designate like elements, FIG. 3 illustrates a circuit diagram of an input buffer 300 of the invention, which includes a first stage circuit 380 and a second stage circuit 390. The first stage circuit 380 45 includes a first input transistor 301 for receiving an input signal Vin at a gate terminal 301', a second input transistor 302 for receiving a reference voltage Vref at a gate terminal 302', a first common mode feedback transistor 303 having an associated gate 303', wherein a source terminal of the first 50 common mode feedback transistor 303 is electrically connected to a drain terminal of the first input transistor 301, a second common mode feedback transistor 304 having an associated gate 304'. The gates 303', 304' of the first and second common mode feedback transistors 303, 304 are elec- 55 trically connected to each other, a source terminal of the second common mode feedback transistor 304 is electrically connected to a drain terminal of the second input transistor 302, and the source terminals of the first and second common mode feedback transistors 303, 304 are electrically connected 60 to each other. First stage circuit 380 further includes a resistance circuit, shown in FIG. 3 as including first and second resistors 305, 306, which is electrically connected between the source terminals of first and second input transistors 301, 302. In addition, first stage circuit 380 also includes first and 65 second output drive transistors 307, 308 for generating differential output signals Vout+, Vout-. A drain terminal of each

4

of the first and second output drive transistors 307, 308 is respectively electrically connected to the resistance circuit 305, 306. Vout+and Vout- are generated respectively at output nodes 309, 310. First stage circuit 380 further includes a first connection node 320 between resistors 305, 306 to which are connected the gates 303', 304' of first and second common mode feedback transistors 303, 304, and the gates 307', 307' of first and second output transistors 307, 308.

Enable transistors 311, 312 may be connected between a power source Vcc and a source terminal of each of the output drive transistors 307, 308. The enable transistors 311, 312 receive an enable signal EN at a gate terminal 311', 312' to activate the first stage circuit 380. In the illustrated embodiment, first and second input transistors 301, 302 and common mode feedback transistors 303, 304 are n-type, and output drive transistors 307, 308 and enable transistors 311, 312 are p-type, although this illustration is not intended to limit the invention to such a configuration.

The second stage circuit 390 includes third and fourth input 20 transistors 350, 351, for respectively receiving the positive output voltage Vout+and inversed/negative output voltage Vout- from first stage circuit 380 at gate terminals 350', 351', first and second general feedback transistors 352, 353 having associated gates 352', 353', and third and fourth general feed-25 back transistors 354, 355 with associated gates 354', 355'. The gates 352', 353' of the first and second general feedback transistors 352, 353 are electrically connected to each other, and the gates 354', 355' of the third and fourth general feedback transistors 354, 355 are electrically connected to each other. Also, a drain terminal of each of the third and fourth general feedback transistors 354, 355 is respectively electrically connected to a source terminal of each of the third and fourth input transistors 350, 351. The second stage circuit 390 further includes an output node 356 at which negative output Vout'- is generated. The output node 356 is electrically connected to the drain terminal of the fourth general feedback transistor 355 and to the source terminal of the fourth input transistor 351. In addition, second stage circuit 390 includes a second connection node 360 which is connected to a drain terminal of the third general feedback transistor 354, to a source terminal of the third input transistor 350, to the gates 352', 353' of the first and second general feedback transistors 352, 353, and to the gates 354', 355' of the third and fourth general feedback transistors 354, 355.

Enable transistors 357, 358 may be connected between a power source Vcc and a source terminal of each of the third and fourth general feedback transistors 354, 355. The enable transistors 357, 358 receive an enable signal EN at a gate terminal 357', 358' to activate the second stage circuit 390. In the illustrated embodiment, third and fourth input transistors 350, 351 and first and second general feedback transistors 352, 353 are n-type, and third and fourth general feedback transistors 354, 355 and enable transistors 357, 358 are p-type, although this illustration is not intended to limit the invention to such a configuration.

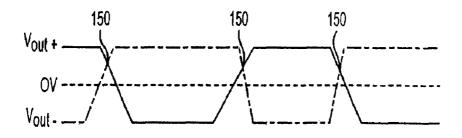

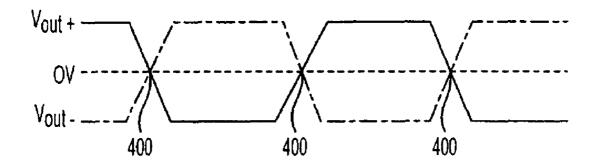

FIG. 4 illustrates the optimized differential output voltages generated by first stage circuit 380. Vout— is the inverse of Vout+, such that the crossing points 400 of the two output signals Vout+, Vout— occur where the voltages are zero and the output signals Vout+, Vout— would cancel each other if added. The absolute values of Vout+ and Vout— are equal at all points

Hence, the present invention describes an input buffer including a first stage for receiving an input signal and generating a first pair of complementary output signals. The first stage includes an input circuit for receiving the input signal, an output circuit for generating the first pair of complemen-

5

tary output signals based on the input signal, a resistance feedback circuit for averaging the first pair of complementary output signals and generating a feedback signal corresponding to the average, and a common mode circuit for balancing the complementary outputs based on the feedback signal. The 5 input buffer may also optionally include a second stage connected to the first pair of outputs and generating a second pair of outputs from the balanced first pair of complementary outputs.

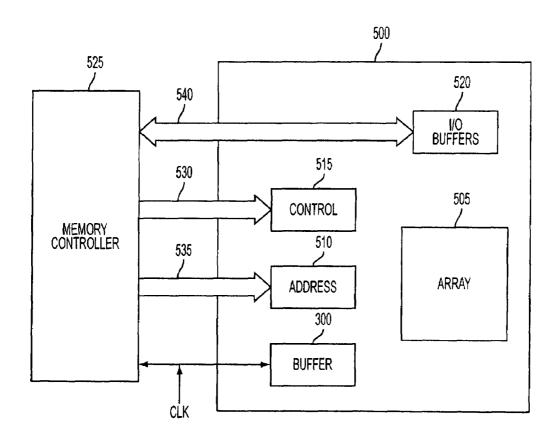

The above described single-ended input buffer generating 10 differential output signals is particularly useful in an integrated memory circuit. In particular, the input buffer is useful in synchronous memory devices such as a synchronous dynamic random access memory (SDRAM). A simplified block diagram of an SDRAM 500 is illustrated in FIG. 5. The 15 SDRAM includes an array of memory cells 505, address circuitry 510 for addressing the memory array, a differential input buffer 300 for receiving a clock signal (CLK), and control circuitry 515 for controlling the operation of the memory device. The differential input buffer 300 includes the 20 circuitry described above with respect to FIG. 3 for reducing clock skew. Input/output (I/O) buffer circuitry 520 is provided for data input and output. An external memory controller 525 is typically used to provide control signals on lines 530, address signals on lines 535, and transmit and receive 25 data on lines 540. It will be appreciated by those skilled in the art that the SDRAM of FIG. 5 is simplified to illustrate the present invention and is not intended to be a detailed description of all of the features of an SDRAM. It should also be understood that while a single SDRAM device is shown in 30 FIG. 5, that in practice there will be a plurality of SDRAM devices connected to controller 525 and that one or more SDRAM devices may be contained on a memory module. In addition to clock signals, the invention may be used for address signals, data signals, command signals, and other 35 signals where generating a balanced differential output would be beneficial.

FIG. 6 illustrates a typical processor system 600 which includes a memory device 650, which includes an input buffer 300 constructed in accordance with an exemplary embodiment of the present invention, and the memory device 500 and memory controller 525 as shown in FIG. 5. A processor system, such as a computer system, generally comprises a central processing unit (CPU) 605, such as a microprocessor, a digital signal processor, or other programmable digital logic 45 devices, which communicates with an input/output (I/O) device 610 over a bus 615. The memory device 500 communicates with the CPU 605 over bus 615 typically through a memory controller.

In the case of a computer system, the processor system may 50 include peripheral devices 620, such as a floppy disk drive or a compact disc (CD) ROM drive, which also communicate with CPU 605 over the bus 615. Memory device 500 is preferably constructed as an integrated circuit, which includes one or more input buffers, e.g., input buffer 300. If 55 desired, the memory device 500 may be combined with the processor, for example CPU 605, in a single integrated circuit.

The processes and devices described above illustrate preferred methods and typical devices of many that could be used 60 and produced. The above description and drawings illustrate embodiments, which achieve the objects, features, and advantages of the present invention. However, it is not intended that the present invention be strictly limited to the above-described and illustrated embodiments. For example, 65 although the invention is discussed only with reference to input buffers using p-type and n-type transistors as described,

6

other input buffers using common mode feedback are also intended to be within the scope of the invention. Additionally, any modifications, though presently unforeseeable, of the present invention that come within the spirit and scope of the following claims should be considered part of the present invention.

What is claimed as new and desired to be protected by Letters Patent of the United States is:

- 1. An input buffer comprising:

- a first stage circuit for receiving an input signal and generating a first pair of balanced complementary output signals based on the input signal, the first stage circuit comprising:

- a resistance feedback circuit for receiving the first pair of complementary output signals and generating a feedback signal; and

- a common mode circuit for balancing the complementary output signals based on the feedback signal; and

- a second stage circuit connected to the first stage configured to receive the balanced first pair of complementary output signals and to generate a third output based on the balanced first pair of complementary output signals.

- 2. The input buffer of claim 1, further comprising:

- a first pair of transistors each having respective source and drain terminals, the source and drain terminals connected respectively to the resistance circuit and to the common mode circuit.

- 3. The input buffer of claim 2, further comprising:

- a second pair of transistors having gate terminals connected to each other, and having drain terminals connected to the resistance feedback circuit.

- 4. The input buffer of claim 3, further comprising:

- a first enable transistor connected to the first stage circuit for receiving an enable signal and for enabling operation of the first stage circuit.

- 5. The input buffer of claim 4, further comprising:

- a second enable transistor connected to the second stage circuit for receiving the enable signal and for enabling operation of the second stage circuit.

- **6**. The input buffer of claim **5**, wherein the first stage circuit is further configured to:

receive a reference voltage; and

- generate the first pair of balanced complementary output signals based on the reference voltage.

- 7. The input buffer of claim 1, wherein the resistance feedback circuit comprises a pair of resistors connected in series.

- 8. A memory device comprising:

- a memory array containing a plurality of memory cells; and an input buffer for receiving signals related to operation of said array, said input buffer comprising:

- a first stage circuit for receiving the signals related to operation of said array and generating a first pair of first and second balanced complementary output signals based on the signals related to operation of said array, the first stage circuit comprising:

- a resistance feedback circuit for receiving the first pair of complementary output signals and generating a feedback signal; and

- a common mode circuit for balancing the complementary output signals based on the feedback signal; and

- a second stage circuit connected to the first stage configured to receive the balanced first pair of complementary output signals and to generate a third output based on the balanced first pair of complementary output signals.

- 9. The memory device of claim 8, wherein the memory device comprises a synchronous dynamic random access

- 10. The memory device of claim 9, further comprising: address circuitry for addressing the memory array; and control circuitry for controlling the operation of the memory device.

- 11. The memory device of claim 10, wherein the signals related to operation of said array comprise clock signals.

- 12. The memory device of claim 8, wherein the memory <sup>10</sup> device comprises an integrated circuit.

- 13. The memory device of claim 8, wherein the first stage circuit further comprises:

- a first input transistor for receiving the signals related to operation of said array; and

- a second input transistor for receiving a reference signal.

- 14. The memory device of claim 13, wherein the first stage circuit further comprises:

- first and second output transistors for respectively generating the first and second balanced complementary output signals based on the signals related to operation of said array and the reference signal.

- **15**. The memory device of claim **14**, wherein the first and second input transistors comprise a first conductivity type.

- **16.** The memory device of claim **15**, wherein the first and second output transistors comprise a second conductivity type

- 17. A processing system comprising:

- a processor; and

memory.

- a memory device coupled to said central processing unit to receive data from and supply data to said central processing unit, said memory device comprising:

- a memory array containing a plurality of memory cells; a memory controller for provide control signals for the 35

- a memory controller for provide control signals for the memory array; and

- an input buffer for receiving signals related to operation of said array, said input buffer comprising:

- a first stage circuit for receiving the signals related to operation of said array and generating a first pair of 40 balanced complementary output signals based on the signals related to operation of said array, the first stage circuit comprising:

- a resistance feedback circuit for receiving the first pair of complementary output signals and generating a feedback signal; and

- a common mode feedback circuit for balancing the complementary output signals based on the feedback signal; and

- a second stage circuit connected to the first stage configured to receive the balanced first pair of complementary output signals and to generate a third output based on the balanced first pair of complementary output signals.

- **18**. The processing system of claim **17**, wherein the common mode feedback circuit comprises:

8

- a first common mode feedback transistor having an associated gate; and

- a second common mode feedback transistor having an associated gate,

- wherein the gates of the first and second common mode feedback transistors are electrically connected to each other

- 19. A method of forming an input buffer, the method comprising:

- forming a first stage circuit for receiving an input signal and generating a first pair of balanced complementary output signals based on the input signal, the forming of the first stage circuit comprising:

- forming a resistance feedback circuit for receiving the first pair of complementary output signals and generating a feedback signal; and

- forming a common mode circuit for balancing the complementary output signals based on the feedback signal; and

- forming a second stage circuit connected to the first stage configured to receive the balanced first pair of complementary output signals and to generate a third output based on the balanced first pair of complementary output signals.

- 20. The method claim 19, wherein forming the first stage circuit further comprises:

- forming a first input transistor for receiving the signals related to operation of said array; and

- forming a second input transistor for receiving a reference signal.

- 21. The memory device of claim 20, wherein forming the first stage circuit further comprises:

- forming first and second output transistors for respectively generating the first and second balanced complementary output signals based on the signals related to operation of said array and the reference signal.

- 22. The memory device of claim 21, wherein the first and second input transistors are formed from a first conductivity type.

- 23. The memory device of claim 22, wherein the first and second output transistors are formed from a second conductivity type.

- **24**. A method of operating an input buffer, the method comprising:

- receiving an input signal;

- generating a first pair of balanced complementary output signals based on the input signal;

- generating a feedback signal based on the first pair of balanced complementary output signals;

- balancing the complementary output signals based on the feedback signal; and

- generating a third output based on the balanced first pair of complementary output signals.

- **25**. The method of claim **24**, wherein the input signal comprises a signal related to operation of a memory array.

\* \* \* \* \*