#### US006445231B1

### (12) United States Patent

Baker et al.

(10) Patent No.: US 6,445,231 B1

(45) **Date of Patent: Sep. 3, 2002**

## (54) DIGITAL DUAL-LOOP DLL DESIGN USING COARSE AND FINE LOOPS

(75) Inventors: R. Jacob Baker, Meridian; Feng Lin,

Boise, both of ID (US)

(73) Assignee: Micron Technology, Inc., Boise, ID

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/585,035

(22) Filed: Jun. 1, 2000

(51) Int. Cl.<sup>7</sup> ...... H03D 3/24

(52) **U.S. Cl.** ...... **327/158**; 327/278; 375/376

327/149, 3, 12, 276, 278, 291; 375/376,

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,109,394 A 4/1992 Hjerpe et al. ...... 375/119

| 5,355,037 A  | * 10/1994 | Andressen et al. | 307/158 |

|--------------|-----------|------------------|---------|

| 5,604,775 A  | * 2/1997  | Saitoh et al     | 331/25  |

| 5,744,991 A  | 4/1998    | Jefferson et al  | 327/158 |

| 6,049,239 A  | * 4/2000  | Eto et al        | 327/158 |

| 6,101,197 A  | 8/2000    | Keeth et al      | 370/517 |

| 6,130,552 A  | * 10/2000 | Jefferson et al  | 326/39  |

| 6,297,680 B1 | * 10/2001 | Kondo            | 327/276 |

<sup>\*</sup> cited by examiner

Primary Examiner—Dinh T. Le (74) Attorney, Agent, or Firm—Schwegman, Lundberg, Woessner & Kluth P.A.

#### (57) ABSTRACT

A dual-loop digital delay locked loop (DLL) is provided. The DLL includes a coarse loop to produce a first delayed signal and provides a wide frequency lock range. The DLL further includes a fine loop connected to the coarse loop to produce a second delayed signal and provides a tight locking. This dual-loop architecture can provide robust operation and tight synchronization over a wide range of delay variations.

#### 34 Claims, 20 Drawing Sheets

FIG. 5B

FIG. 12

#### DIGITAL DUAL-LOOP DLL DESIGN USING **COARSE AND FINE LOOPS**

#### TECHNICAL FIELD OF THE INVENTION

The present invention relates generally to integrated circuits and in particular to digital delay locked loops in semiconductor memory devices.

#### BACKGROUND OF THE INVENTION

Semiconductor memory devices such as dynamic random access memory (DRAM) devices are widely used to store data in computers and electronic products. A DRAM device comprises a plurality of memory cells for storing data. A data is stored or written into a DRAM device by a write 15 operation. The stored data is read from the DRAM device by a read operation.

During a read operation, a memory cell is accessed, the stored data is read from the memory cell and transmitted to an output pad. The data at the output pad is represented as 20 an electrical signal or a data signal (DQ). In order to determine a time window in which a valid data is present at the output pad, a data strobe signal (DS) is designed to track or lock to the data signal. Locking, or synchronizing, the DS and DQ signals ensures the integrity of the data, which is 25 especially essential in a high speed DRAM device.

When the DQ signal propagates from the memory cell to the output pad, a time delay occurs. It is difficult to predict the time delay of the DQ signal because of variations in temperature, supply voltage or other process variations 30 tionships of the DLL of FIG. 3A. within the DRAM device. Therefore locking the DS signal to the DQ signal requires careful timing calculation and reliable circuit design.

Different DRAM devices use different timing calculations and techniques for designing a circuit to lock the DS signal to the DQ signal. Some DRAM devices use analog circuits such as charge pump, loop filter and voltage-controlled delay line while other use a mix of analog and digital circuits for performing the necessary timing calculations. However, the inclusion of analog circuits often make it hard to scale for other process and applications and are unstable due to the variations in process, supply voltage and temperature. Furthermore, these analog implementations require complex tuning after the production in order to get a tight locking.

Thus, there is a need for a new technique which can more efficiently lock the strobe signal DS to the data signal DQ over wide range of frequency in integrated circuits. It is further desired that such circuits and method are portable and easy to scale for different process and applications 50 without requiring post production tuning.

#### SUMMARY OF THE INVENTION

The problem associated with DLL and other problems are addressed by the present invention and will be understood 55 by reading the following disclosure. A digital dual-loop delay locked loop (DLL) is provided which has a wide frequency lock range and tight locking without post production tunning. The digital dual-loop DLL is suitable for uses in a DRAM device to lock a strobe signal DS to a data 60 signal.

In one embodiment, a dual-loop digital DLL is provided. The DLL includes a coarse loop to produce a first delayed signal which is coarsely locked to the input signal. The coarse loop has a delay range to provide a wide frequency lock range. The DLL further includes a fine loop connected to the coarse loop to produce a second delayed signal. The

fine loop has a delay range which is substantially smaller than that of the coarse loop to provide a tight locking.

In vet another embodiment, a method for synchronizing two signals is described. The method includes applying an amount of delay to an input signal at a coarse loop to produce a first delayed signal. The method also includes applying an amount of small delay to the first delayed signal at a fine loop to produce an output signal. The method further includes comparing the output signal and the input signal and adjusting the delay of both loops until the output signal and the input signal are tightly synchronized.

#### BRIEF DESCRIPTION OF THE DRAWINGS

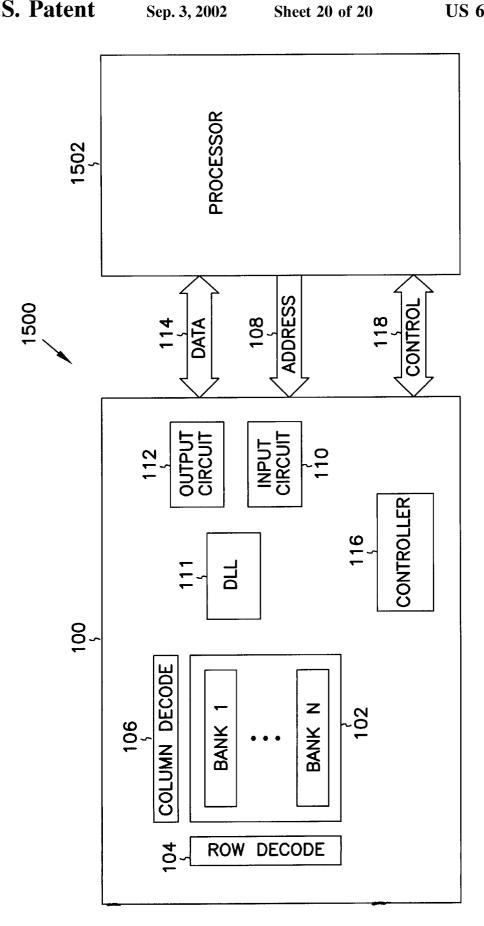

FIG. 1 illustrates an embodiment of a memory device of the invention;

FIG. 2A shows a block diagram illustrating a portion of the memory device of FIG. 1;

FIGS. 2B-D are timing diagrams illustrating signal relationships of the portion of the memory device shown in FIG.

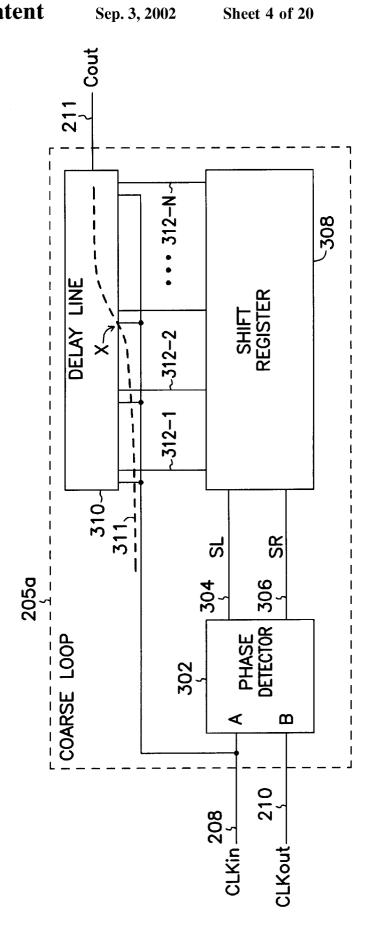

FIG. 3A is a block diagram illustrating a block diagram of a coarse loop of a delay locked loop (DLL) of the invention.

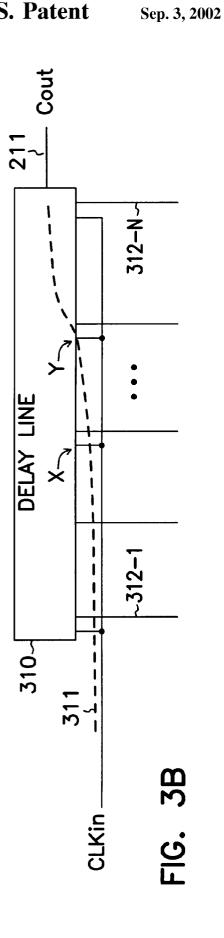

FIG. 3B shows one embodiment of a delay line for the DLL of FIG. 3A.

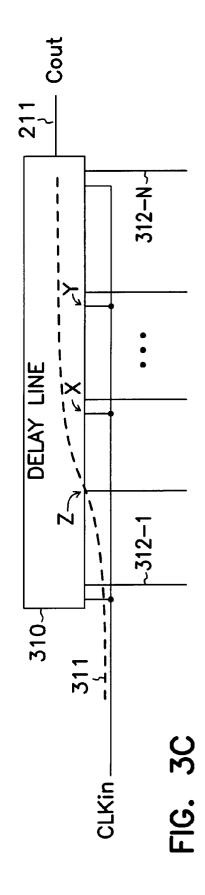

FIG. 3C shows another embodiment of a delay line for the DLL of FIG. 3A.

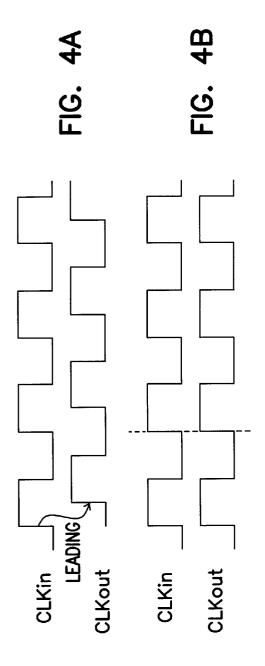

FIGS. 4A-D are timing diagrams showing signal rela-

FIG. 5A illustrates a schematic diagram of the coarse loop of the DLL of FIG. 3A.

FIG. 5B illustrates a schematic diagram of a delay of FIG. 5A.

FIG. 6A is a block diagram of delay stages of the DLL of FIG. **5**A.

FIG. 6B shows in more details a schematic diagram of a delay stage of the DLL of FIG. 6A.

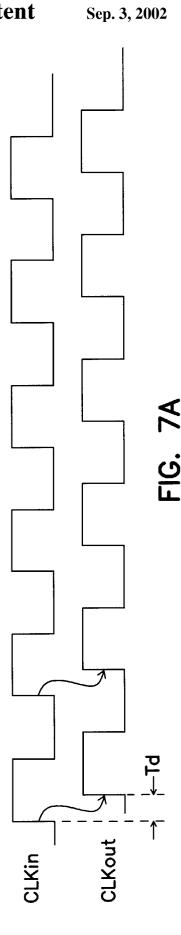

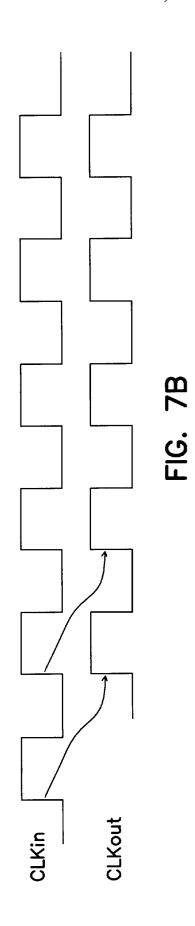

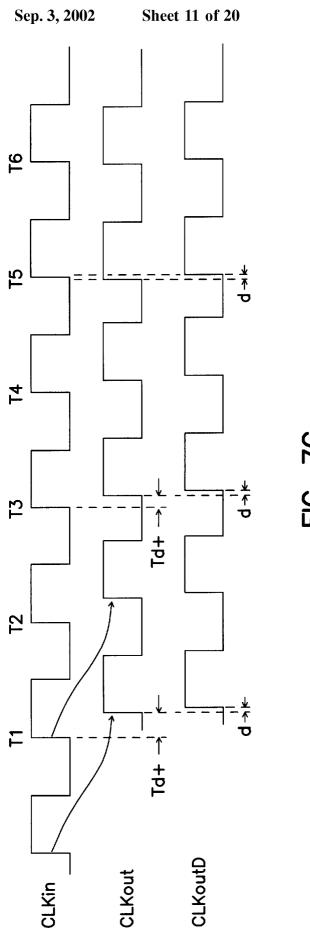

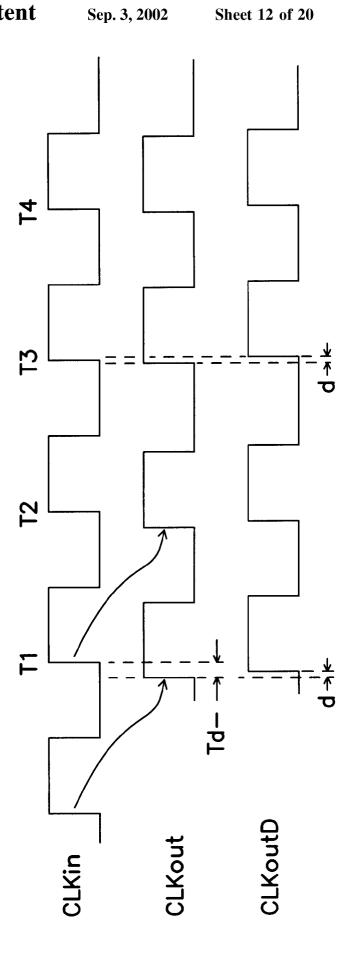

FIGS. 7A-D illustrate timing diagrams of FIG. 5A.

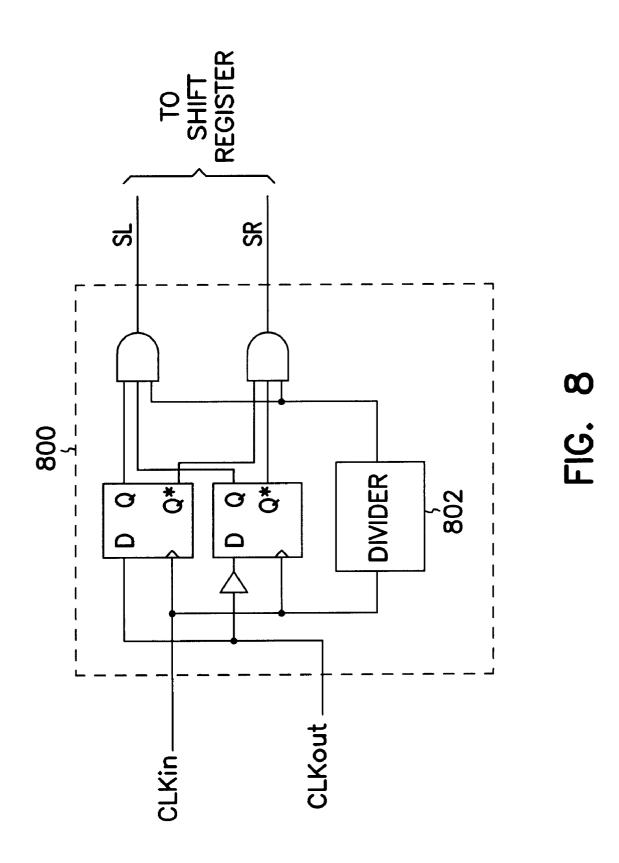

FIG. 8 shows another embodiment of a phase detector for the DLL of FIG. 5A.

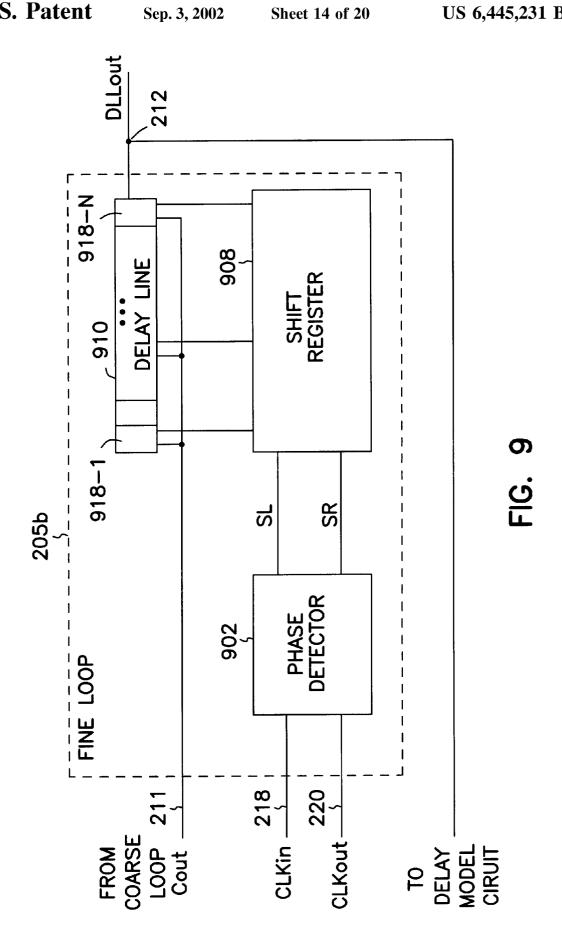

FIG. 9 illustrates one embodiment of a digital dual-loop DLL of the invention.

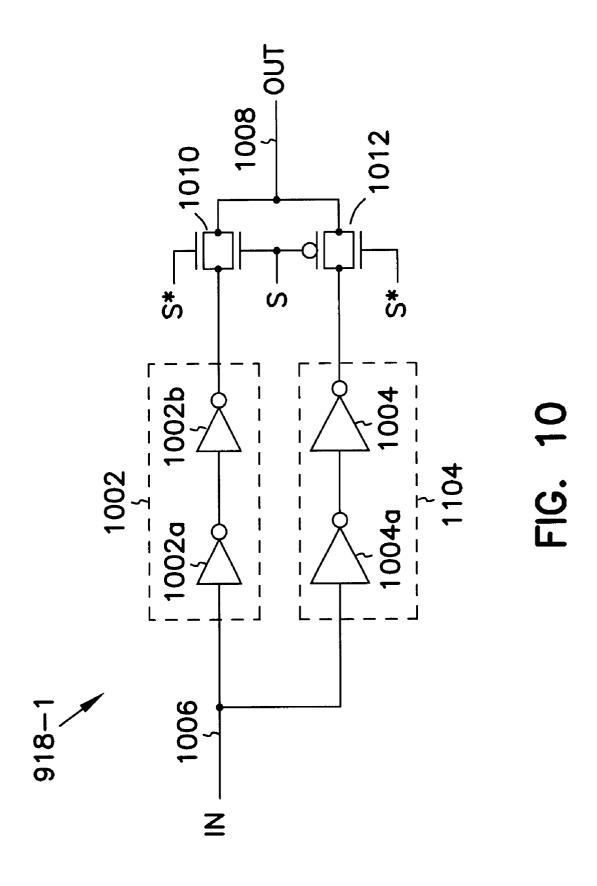

FIG. 10 illustrates a block diagram of a fine loop of the dual-loop DLL of FIG. 9.

FIG. 11 shows one embodiment of a delay cell of the delay line of FIG. 10.

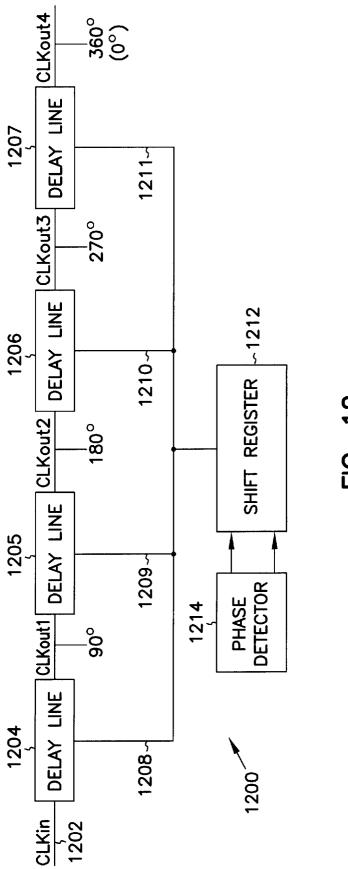

FIG. 12 is a block diagram showing an embodiment of a multi-phase generator including the novel DLL of FIG. 9.

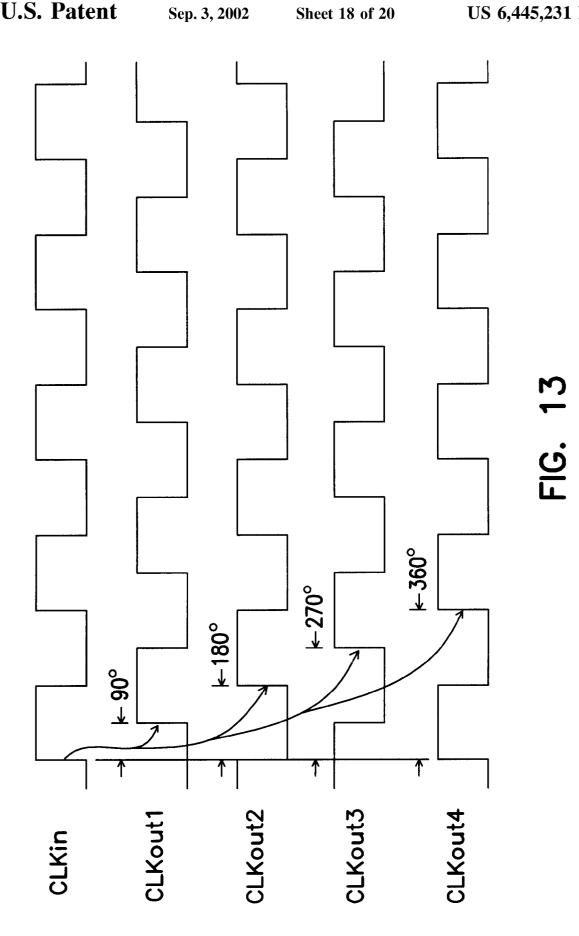

FIG. 13 is a timing diagram showing waveforms of the DLL of FIG. 12.

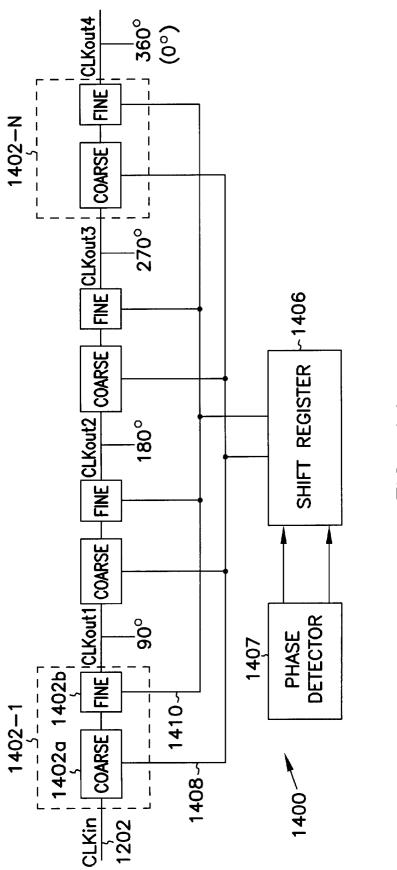

FIG. 14 is a block diagram showing another embodiment of a multi-phase generator having a DLL configuration of FIG. 9.

FIG. 15 illustrates a system including the memory device embodiment of FIG. 1.

#### DETAILED DESCRIPTION OF THE INVENTION

The following detailed description of the embodiments of the invention refers to the accompanying drawings which form a part hereof, and shows by way of illustration specific embodiments in which the inventions may be practiced. These embodiments are described in sufficient detail to

enable those skilled in the art to practice the invention, and it is to be understood that other embodiments may be utilized and that logical, mechanical and electrical changes may be made without departing from the spirit and scope of the present invention. The following detailed description is, therefore, not to be taken in a limiting sense, and the scope of the invention is defined only by the appended claims.

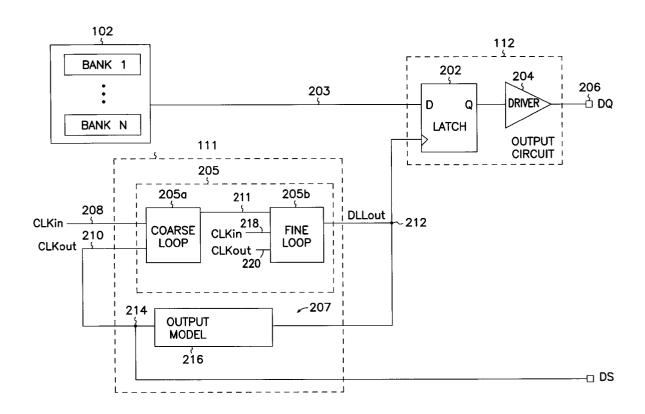

FIG. 1 illustrates a memory device 100 of the invention. In one embodiment, memory device 100 includes, by way of example and not limitation, a synchronous dynamic random 10 access memory device (SDRAM). As shown in FIG. 1, memory device 100 includes a main memory 102. Main memory 102 typically includes dynamic random access memory (DRAM) devices which include one or more memory banks, indicated by BANK 1-N. Each of the memory banks BANK 1-N includes a plurality of memory cells arranged in rows and columns. Row decode 104 and column decode 106 access the rows and columns in response to an address, provided on address bus 108 (ADDRESS) by an external controller (not shown), such as a microprocessor. 20 An input circuit 110 and an output circuit 112 connect to a data bus 114 (DATA) for bi-directional data communication with main memory 102. A memory controller 116 controls data communication between the memory 100 and external devices by responding to an input clock signal (CLK) and control signals provided on control lines 118 (CONTROL). The control signals include, but are not limited to, Chip Select (CS\*), Row Access Strobe (RAS\*), Column Access Strobe (CAS\*), Write Enable (WE\*), and Clock Enable (CKE).

As shown in FIG. 1, a delay locked loop (DLL) 111, formed according to the teaching of the present invention, connects to input circuit 110 and output circuit 112 for performing a timing adjustment, such as skew elimination or clock synchronization between two clock signals. According 35 to the teaching of the present invention DLL 111 is a digital dual-loop DLL which has the capability to provide a skew elimination over a wide range of frequencies with very tight locking. Those skilled in the art will readily recognize that the DRAM device 100 of FIG. 1 is simplified to illustrate the 40 present invention and is not intended to be a detailed description of all of the features of a DRAM device.

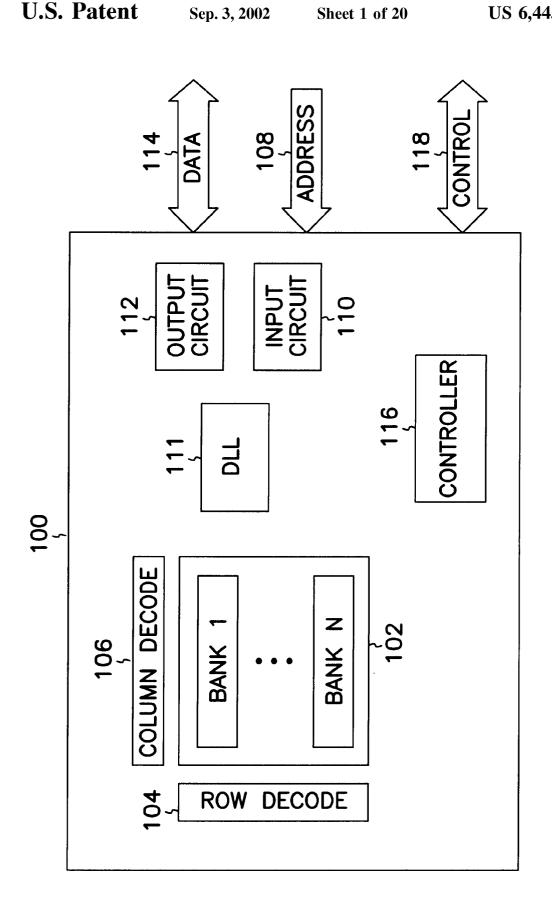

FIG. 2A is a block diagram illustrating a portion of memory device 100 of FIG. 1 including main memory 102, 112 includes an output latch 202 connected to an output driver **204**. Output latch **202** is connected to main memory 102 via connection line 203. Output driver 204 is connected to an output pad 206 which provides a data output signal or coarse loop **205***a* connected to a second loop or fine loop 205b. In one embodiment, coarse loop 205a has a range up to 20 ns (nanosecond) to provide a wide frequency lock range. Fine loop **205***b* has a delay range from about 1 to 1.2 ns to provide a tight locking. Coarse loop 205a has input 55 nodes 208 and 210 and an output node 211. Input node 208 receives an input clock signal CLKin. Input node 210 receives a feedback clock signal CLKout. And a first output node 211 provides a first delayed signal or coarse loop output signal Cout. Fine loop 205b receives Cout signal of coarse loop 205a at node 211, CLKin signal at node 218 and CLKout signal at node 220. Fine loop 205b outputs a second delayed signal DLLout at second output node or DLL output node 212. Thus DLLout signal is an output signal of DLL 111 which has dual loops indicated by coarse loop 205a and 65 node 211. fine loop 205b. CLKout is a feedback signal provided at node 214 of a feedback path 207. Feedback path 207

includes a delay model circuit 216. Delay model circuit 216 is connected to receive DLLout signal at node 212 and providing CLKout signal at node 214. Delay model circuit 216 is identical to output circuit 112. In other words, delay model circuit 216 can be constructed to have a delay time equal to a delay time of output circuit 112. In addition, at node 214, a data strobe signal DS is provided. Thus, DS and CLKout signal are the same signal. When DLL 111 is locked during a normal operation of the memory device, DS and DQ signals are synchronized.

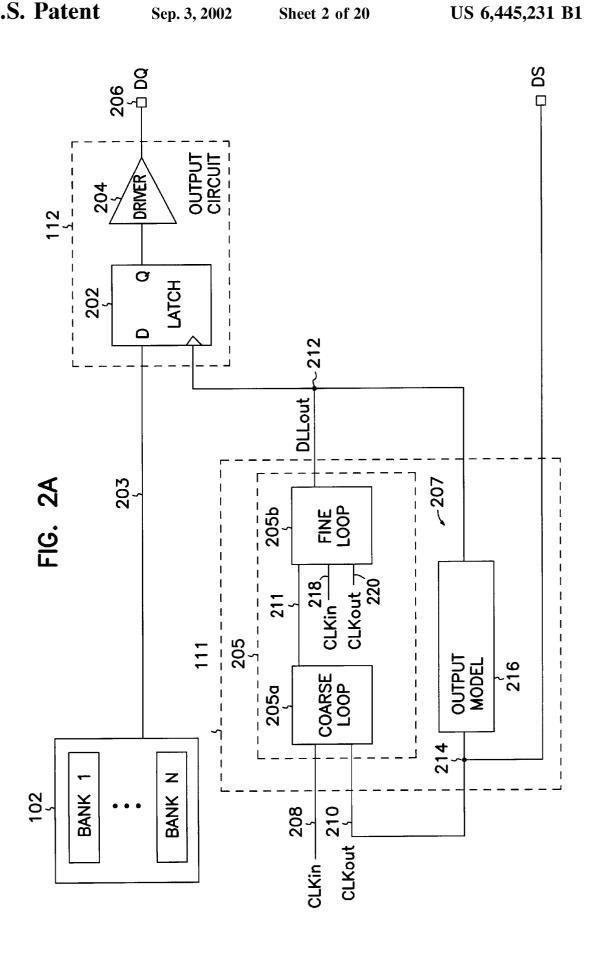

FIG. 2B shows timing diagram of DS and DQ signals when DLL 111 of FIG. 2A is locked. As shown in FIG. 2A, memory device 100 provides a data output signal DQ. The DQ can move around due to process variations within the device. Without DLL 111, data strobe signal DS may not latch the correct data, or to meet the setup or hold time requirement and the operating speed of the memory has to be slowed down. DLL 111 is designed to dynamically tracks the process variations and enables DS signal to correctly latch DQ signal or ensures that DQ and DS signals are synchronized. As shown in FIG. 2B, DS signal is tightly synchronized with the DQ signal. The synchronization is achieved by DLL 111, which automatically adjusts to the delay variations of memory device 100.

FIGS. 2C-D shows timing diagram of DS and DQ signals during a memory access operation of memory device 100. During a memory access such as a read operation, controller 116 (FIG. 1) receives a combination of control signals via control lines 118 indicating a read operation. Row decode 104 and column decode 106 access a memory cell using an address provided by address bus **108**. The accessed memory cell outputs a data stored in the memory cell via line 203 to output circuit 112. Output circuit 112 latches and drives the data out to output pad 206. At output pad 206, the data is represented as a DQ signal. To ensure a high performance of the memory device, DS signal must be locked to DQ signal. DLL 111 generates synchronized clock signal DLLout to latch the data and locks DS signal to DQ signal. As shown in the timing diagram of FIG. 2B, at the rising edge of DS signal, DQ signal is locked to or substantially synchronize with DQ signal. According to the teaching of the present invention, DLL 111 can be used in a double data rate DRAM device where data occurs on both rising and fall edge of a clock signal with little duty-cycle distortion. In FIG. 2C, data (DQ signal) occurs at the rising and falling edge of DS dual-loop DLL 111, and output circuit 112. Output circuit 45 signal. To achieve the locking, DLL 111 compares CLKin and CLKout signals and adjusts a time delay between the edges of CLKin and CLKout signals until both clock signals are substantially synchronized. The skew between CLKin and CLKout signals is determined by the minimum resolu-DQ. DLL 111 includes a forward path 205 having a first loop 50 tion of the delay cell. When the clock signals are synchronized, the DLL is locked and DS signal is locked to DQ signal.

> FIG. 3A illustrates a block diagram coarse loop 205a of DLL 111 of FIG. 2A. Coarse loop 205a of DLL 111 includes a phase detector 302 having an input A connected to input node 208 for receiving CLKin signal and an input B connected to input node 210 for receiving the CLKout signal. Phase detector 302 also includes outputs 304 and 306 for providing a shift left (SL) and a shift right (SR) signals to a shift register 308. Shift register 308 provides control and selects the amount of delay of a delay line 310 through a plurality of control lines 312 1-N. Delay line 310 receives CLKin signal at an input node 208 and provides a delayed output signal or coarse loop output signal Cout at output

> When a control line 312 1-N is selected, an entry point into delay line 310 is created at point X (FIG. 3A). CLKin

signal enters the delay line at point X and propagate through the delay line to output node 211. A path of CLKin from entry point X to output 211 is indicated as path 311. When point X is at the left most of the delay line, the most delay is applied to CLKin signal. In the opposite, when point X is at the right most of the delay line the least amount of delay applied to CLKin signal. The number of delay stages in the coarse loop determines the lock range of DLL 111. Detailed description of the operation of the DLL of FIG. 3A is best described in conjunction with timing diagrams illustrated in 10 FIGS. 3B-C and FIGS. 4A-B.

FIG. 3B shows delay 310 of DLL 111 when one of the control lines 312 1-N is selected. In the Figure, an entry at point Y is created resulting after a shift right from register 308. FIG. 3C shows another situation of delay line 310 in 15 which an entry at point Z is created after a shift left from register 308.

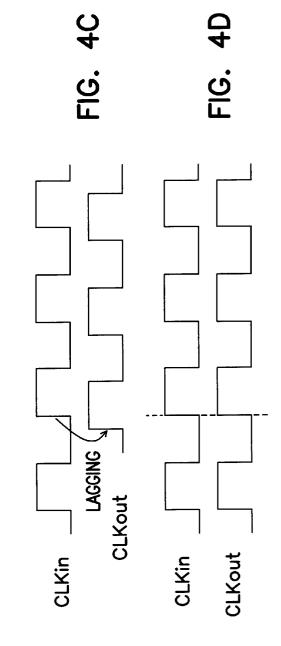

FIGS. 4A-B shows a timing diagram with waveforms of CLKin and CLKout signals. FIG. 4A shows a timing diagram when CLKin signal is leading CLKout signal. In this case, in order for both signals to be synchronized the amount of delay applied to CLKin signal must be decreased. FIG. 4B shows a timing diagram when CLKin signal is lagging CLKout signal. In this situation, the delay amount to CLKin signal must be increased to synchronize CLKin and CLK-

In the case when CLKin is leading CLKout, phase detector 302 compares a relative timing of the edges of CLKin and CLKout signals and produces a SR signal. Upon receiving the SR signal, shift register 308 selectively activates one of the control lines 312 1-N to select an entry point into delay line 310 to shift the point of entry to the right to decrease the delay amount. For example, assuming that before the shift, CLKin signal enters delay line 310 at point X. When shift register 308 receives the SR signal, it selects one of the control lines 312 1–N and creates a new point of entry at point Y, to the right of point X. Since point Y is closer to the right of the delay line than point X, the amount of delay to CLKin signal is decreased until CLKin and CLKout signals are synchronized, as shown in FIG. 4B.

In the case when CLKin is lagging CLKout, phase detector 302 produces SL signal. Subsequently, shift register 308 shift the point of entry to the left of point X at point Z. Since CLKin is increased. Consequently, CLKin and CLKout signal are synchronized, as shown in FIG. 4D.

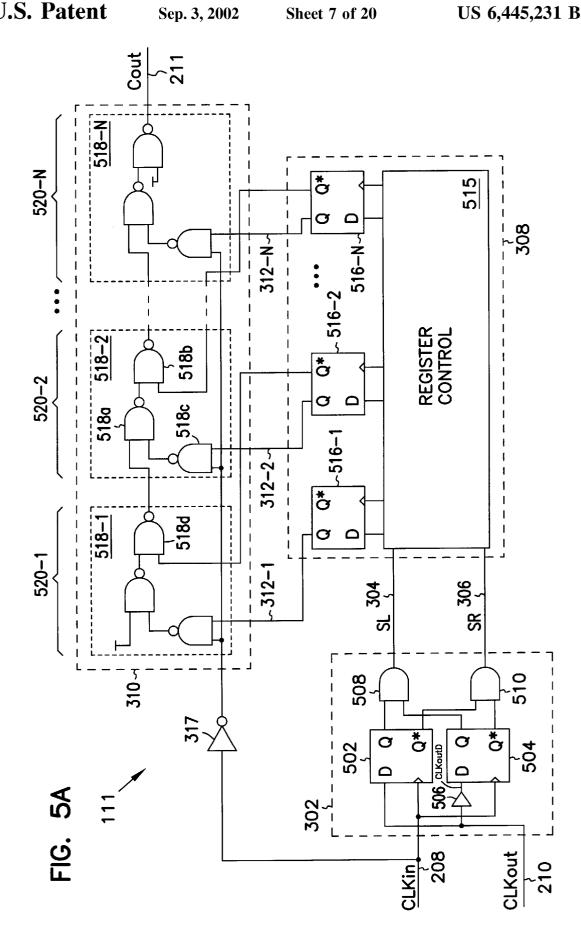

FIG. 5A illustrates a schematic diagram of DLL 111. In the Figure, phase detector 302 includes two flip flops (FF) **502** and **504**. Each of the flip flops includes inputs D and 50 CLK and complementary outputs Q and Q\*. Input D of FF 502 receives CLKin signal and input D of FF 504 receives a delay version of CLKin signal through a delay **506**. Both inputs CLK of the flip flops are connected to node 210 for receiving signal CLKout. Both outputs Q are connected to 55 AND gate 508. Both outputs Q\* are connected to AND gate 510. The outputs of AND gates 508 and 510 are connected to outputs 304 and 306 of phase detector 302, respectively. The outputs of AND gates 508 and 510 provide control signals to shift register 308. Shift register 308 includes a register control 515 which controls a plurality of register cells 516 1-N. Each of the register cells includes a D-type flip flop having output Q and a complementary output Q\*. Delay line 310 includes a plurality of delay cells 518 1-N. Each of the delay cells includes a plurality of delay 65 elements, such as NAND gates 518a, 518b and 518c of delay cell 518-2. Each of the delay cells receives an inversed

version of CLKin at an output of an inverter 317. For example, NAND gate 518c is connected to the output of inverter 317 to receive the inversed version of CLKin signal. The other input of NAND gate 518c receives a control signal from output Q of the register cells 516 1-N.

The register cells are connected to the delay cells through control lines 312 1-N to form a plurality of sequential delay stages 520 1-N. For instance, register cell 516-2 is connected to delay cell 518-2 via control line 312-2 to form a delay stage 504-2. Furthermore, output Q\* of each of the register cells is connected to a previous delay stage. For example, output Q\* of register cell 516-2 of delay stage **520-2** is connected to an input of NAND gate **518***d* of delay stage 520-1. Q\* is connected as such to ensure that when a particular delay state is selected by register cells 516 1-N, the previous delay stages are disabled. The contents of register cells in the previous stages will be ignored.

Each delay stage is capable of delaying a signal by about 200 ps (peco seconds). Thus it is a design choice to construct a total number of the delay stages to accommodate a range of operating frequency of the memory device. For example, a memory operating with a frequency of 100 MHz or a 10 ns (nano second) clock cycle, would have more delay stages than a memory operating at a 250 MHz (a 4 ns second clock cycle). With 100 MHz frequency, the minimum total number of delay stages required is 50 (10 ns divided by 200 ps), whereas with a 250 MHz frequency it would requires a minimum of 20 delay stages. Therefore the minimum operating frequency is the inverse of the product of the number of delay stages and the delay per stage. In the example above, a DRAM device having a delay line including 50 delay stages can be used in a frequency ranging from 100 MHz to 250 MHz assuming that the total delay is within one clock cycle.

Furthermore, the delay elements are constructed the same to ensure that a propagation from one delay element to the next delay element is the same. For example, delay element 518a and 518b are both NAND gates. This means that a propagation delay through the delay element (NAND gate) 40 of a high-to-low transition is equal to a propagation delay of a low-to-high transition and output of this delay line has little duty cycle distortion. This characteristic enables DLL 111 of the invention to be used in a double data rate (DDR) DRAM device, where a read or write operation occurs on point Z is closer to the left of the delay line, the delay to 45 both rising edge and falling edge of the a clock signal. In addition, using two input delay elements such as the two input NAND gates of delay cell 518-2, provides flexible control from shift register 308 to delay line 310. That means each of the delay cells can have at least two control inputs. For example, inputs of NAND gates 518b and 518c can be controlled by Q and Q\* of each of the register cells. Q is connected to create an entry point at NAND gate 518c while Q\* is connected to disable previous stages once the entry point is created.

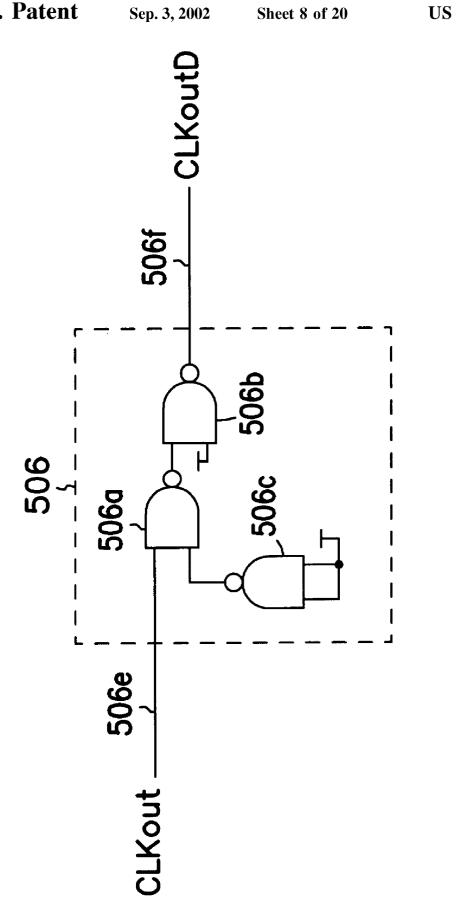

> FIG. 5B illustrates one embodiment of delay 506 of phase detector 302 of FIG. 5A. Delay 506 has similar construction to one of the delay cells 520 1-N of delay line 310. In the Figure, delay 506 includes NAND gates 506a-c arranged in the same way as NAND gates 508a-c of delay cell 518-2. Delay **506** has an input at node **506***e* of NAND gate **506***a* for receiving signal CLKout from node 210 and an output at node 506f for providing the CLKoutD signal. As shown in the Figure, the delay between CLKout and CLKoutD signals is equal to, or configured to be one of the delay cells 518 1-N of delay stages 520 1-N. This configuration is helpful to track the delay variation in the delay line and provide stable operations.

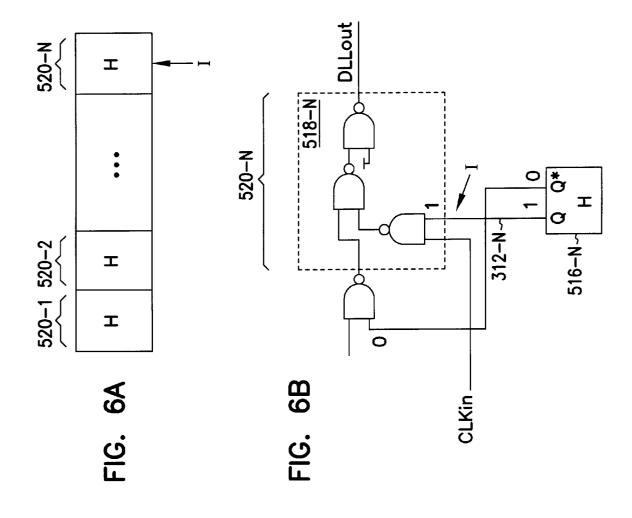

The DLL of FIG. **5**A is best understood with reference to FIGS. **6**A–7D. FIG. **6**A–B show an exemplary initial conditions of delay stage **520**-N. In FIGS. **6**A–B, all delay cells have a logic HIGH and the point of entry, point I, is the point closest to the right of the delay line at the last delay stage **520**-N. FIGS. **7**A–B show timing diagrams of exemplary initial conditions of waveforms of signals CLKin and CLK-out. FIG. **7**A shows a timing diagram when CLKin is leading CLKout by an amount of time indicated by Td. FIG. **7**B shows a timing diagram when CLKin and CLKout signals are synchronized.

In general, assuming that the frequency of CLKin is 200 MHz and an internal delay of memory device 100 is 2 ns, or CLKin is leading CLKout by 2 nano seconds (2 ns). In this case, more delay needs to be added to CLKin. Specifically, 3 ns is needed to add to CLKin to make the total delay equal to one clock cycle or 5 ns. After the delay is added both signals are synchronized as shown in FIG. 7B. When phase detector (FIG. 5) detects the time difference Td, it activates SL signal. Upon receiving the SL signal, register control 515 20 activate one of the control line 312 1-N to create an entry point into delay line 310. Since each of the delay stages 520 1-N has a 200 ps delay (0.2 ns), therefore 15 delay stages are needed to have a total of 3 ns delay. In this case, shift register 308 shifts the point of entry 15 position from the left of the current position. From both exemplary situations described in FIGS. 7A–7B, a total delay equals one clock cycle or the sum of the amount applied by the delay line plus the internal delay.

FIG. 7C shows a timing diagram of another exemplary 30 situation of DLL of FIG. 5. The Figure shows waveforms of CLKin, CLKout and a delay version of CLKout signal indicated as CLKoutD which is the input signal at input D of flip flop 504. In the Figure, at time T1, CLKin is leading CLKout by a time indicated by Td+. AT time T1, CLKin 35 transitions from Low to HIGH, input D of both FF 502 and 504 are LOW and both output Q\* are HIGH. This makes output of AND gate 510 HIGH which sends SR signal to register control 515. Shift register 308 makes a shift right at time T2 to decrease the amount of delay. At this time, one 40 of the control lines 312 1-N is selected and a new point of entry into delay line 310 is chosen. The new point of entry is positioned to the right of the current point of entry. The new point of entry enables the delay line to decrease the amount of delay, thus Td+ is smaller at time T3. At time T4, 45 phase detector 302 makes another decision and shift register further make another shift right because CLKin is still leading CLKout. At time T5 when the rising edge of CLKin is within (in between) the rising edges of CLKout and CLKoutD, that is CLKin transitions from LOW to HIGH after CLKout transition HIGH and before CLKoutD transition high. This makes both outputs of AND gates 508 and 510 are LOW, at this point the DLL is locked.

FIG. 7D shows timing diagram of another exemplary situation of DLL of FIG. 5. The Figure shows a waveforms of CLKin, CLKout and CLKoutD where CLKin is lagging CLKout by a time indicated by Td-. DLL 111 in this case performs a shift left instead of a shift right as in the case of FIG. 7C. In FIG. 7D. At time T1, CLKin transition HIGH, CLKout and CLKoutD are both HIGH thus both outputs Q of flip flop 502 and 504 are HIGH. This makes the output of AND gate 508 HIGH and an SL signal is sent to shift register 308 which enables the shift register to make a shift left to increase the amount of delay. At time T2 shift register 308 move the current point of entry to the left to apply appropriate amount of delay to CLKin signal. AT time T3 when the rising edge of CLKin is within the rising edges of

8

CLKout and CLKoutD, that is when CLKin transitions from LOW to HIGH after CLKout transition HIGH and before CLKoutD transition high. Thus both outputs of AND gates 508 and 510 are LOW which locks the DLL.

FIG. 8 shows another embodiment of a phase detector of coarse loop 205a of the invention. In the Figure, phase detector 800 is constructed similar to phase detector 302 of DLL 111 of FIG. 5A with the exception of a divider 802. Divider is used to provide enough time for the shift register to settle down and the flip flops (502 and 504) of the phase detector to solve the metastability problems. Those skilled in the art will readily recognize that the number of divider 802 can be calculated to meet timing specification or operating frequency of the DRAM device.

FIG. 9 shows a block diagram of fine loop 205b of DLL 111 FIG. 3A. Fine loop 205b is constructed and operates substantially the same as coarse loop 205a. In general, fine loop 205b can comprise a delay line having a plurality of delay stages. Each of the delay stages includes a vernier delay (for example, 20 ps), which is substantially smaller than a delay of each of the delay stages of the coarse loop (for example, 200 ps). Fine loop **205**b has a smaller delay range, for example a minimum delay of about 1 ns and a maximum delay of about 1.2 or a total range of 200 ps. Thus fine loop can include 10 delay stages. In FIG. 9, fine loop **205**b includes a delay line **910** connected to receive output signal Cout from coarse loop 205a at node 211. Delay line 910 is controlled by a shift register 908 which receives control signals, or shifting signals, SR and SL from a phase detector 902. Phase detector 902 receives CLKin signal at node 218 and CLKout signal at node 220. Delay line 910 includes a plurality of delay cells 918 1–N. One embodiment of a delay cell of delay line 910 is shown in FIG. 10.

FIG. 10 shows one embodiment of a delay cell of delay line 910 of fine loop 205b of FIG. 9. Delay cell 918-1 includes a plurality of inverters. Inverters 1002a and 1002b form a first path 1002 and inverters 1004a and 1004b form a second path 1004. The paths are connected to receive an input signal (IN) at node 1006. For example, path 1002 has a delay of 100 ps and path 1004 has a delay of 120 ps. The inverters of path 1004 can be constructed with longer L (channel length of a transistor in the inverter) than the inverters of path 1002 to have a longer delay. This vernier delay can be adjusted according to the resolution of the fine loop. Paths 1002 and 1004 are connected to switches 1010 and 1012 which are control by complementary control signals S and S\* which selectively control the passage of the input signal from node 1006 to an output at node 1008. In one embodiment, control signals S and S\* are connected the output Q and Q\* of the register cell.

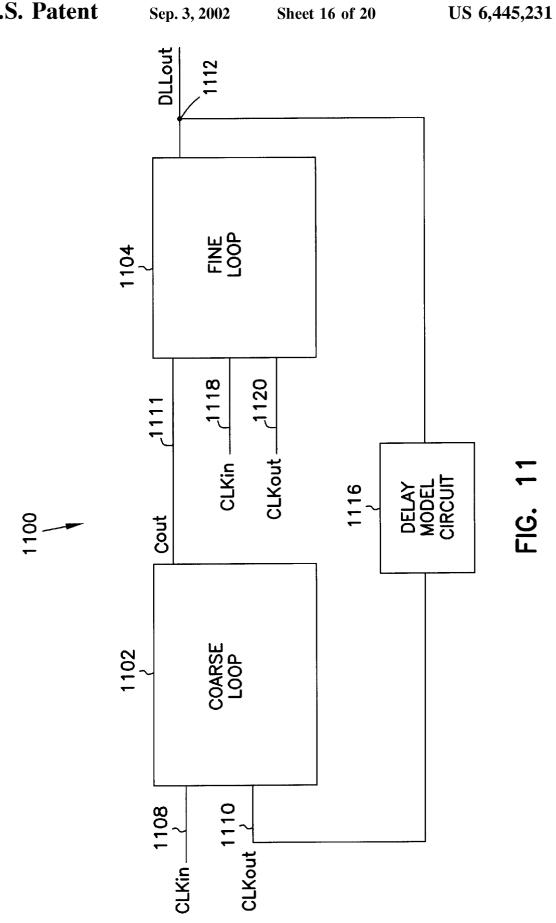

FIG. 11 shows one embodiment of a dual-loop DLL 1100 according to the invention. DLL 1100 having a coarse loop 1102 connected to a fine loop 1104. Coarse loop 1102 receive input signals CLKin at node 1108 and CLKout at node 1110. Coarse loop 1102 produces a first delayed output signal or coarse loop output signal Cout at node 1111. Fine loop 1104 receives Cout signal at node 1111, CLKin signal at node 1118 and CLKout signal at node 1120. Fine loop 1104 produces a second output signal DLLout at node 1112. A delay model circuit 1116 is included to the DLL and is connected at node 1112 to receive the DLLout signal and provide the CLKout signal at node 1110. Coarse loop 1102 and fine loop 1104 are constructed and operates the same as coarse loop 205a and 205b of DLL 111 of FIG. 5, respectively.

In operation, since it is a dual-loop DLL, DLL 1100 provides a wide lock range and tight locking by the dual

loops represented by coarse loop 1102 and fine loop 1104. DLL 1100 operates in the same manner as DLL 111. Fine loop 1104 further reduces the skew between the edges of CLKin and CLKout of coarse loop 1102. That is when coarse loop 1102 is locked, the edges of CLKin and CLKout have about 200 ps peak-to-peak jitter because the coarse loop has two NAND gates or 200 ps delay in each of the delay cells. This jitter from the coarse loop, in some cases, may not be preferable for a high speed DRAM device. The fine loop interpolates the delay and the jitter is even smaller, about 20 ps peak-to-peak (10 times smaller) and provides overall a tight locking.

FIG. 12 shows an embodiment of a multi-phase generator including the novel DLL of the invention. Multi-phase generator 1200 including a plurality of delay lines 1204–7, each of the delay lines have the same delay time. The delay lines receives an input clock signal CLKin at note 1202 and produce a plurality of output signal CLKout1–4 at the outputs of the delay lines. When each of the delay lines is locked and four delay lines are used, the output signal at the output of each of the delay lines is a multiple of 90 degrees out of phase with the input signal CLKin. That means the output signal of delay line 1204–7 is 90, 180, 270 or 360 degrees out of phase with CLKin signal, respectively. A shift register 1212 is connected to receive control signals from a 25 phase detector 1214 to control the delay lines.

FIG. 13 is a timing diagram showing signal relationship of the input signal CLKin and the output signals CLKout1-4. The operation of multi-phase generator 1200 is similar to the operation of DLL 111 described above. Con- 30 trol register 1202 simultaneously applies a shift to delay lines 1204-7. When the multi-phase generator is locked, assuming the delay is equal to one clock period, it has four different clock signals having four different phases at its outputs. As shown in FIG. 13, when multi-phase generator 35 1200 is locked, output signal CLKout1 is 90 degrees out of phase with the input signal CLKin. Output signal CLKout2 is 180 degrees out of phase with the input signal CLKin. Output signal CLKout3 is 270 degrees out of phase with the input signal CLKin. And output signal CLKout4 is 360 40 degrees out of phase with the input signal CLKin. Those skilled in the art will readily recognize that other number of delay lines of multi-phase generator 1200 can be used to generate other output signals with different phases. For example, to generate six different phases with each having 45 a 60 degrees out of phase, six delay lines are needed.

FIG. 14 shows another embodiment of a multi-phase generator including the novel dual-loop DLL of the invention. Multi-phase generator 1400 is similar to multi-phase generator 1200 of FIG. 12 with the exception of an addition 50 of a plurality of fine loops. In the Figure, multi-phase generator 1400 includes a series connected delays 1402 1-N, each of the delay includes a coarse loop 1402a and fine loop 1402b. The coarse loop has a time delay substantially greater than a time delay of the fine loop. The coarse loop 55 and fine loop of multi-phase generator 1400 is constructed the same as the coarse loop and fine loop of DLL 111 of FIG. 1. In this embodiment, the output signals are produced at the output of each of the fine loop. When each of the dual-loop DLL is locked and four DLL are used, the output signal at 60 the output of each of the fine loop is a multiple of 90 degrees out of phase with the input signal CLKin. That means the output signal of fine loop 1402 1-N is 90, 180, 270 or 360 degrees out of phase with CLKin signal. A control register **1406** is connected to receives control signals from a phase 65 detector 1407. Control register 1406 controls the shifting within the coarse and the fine loops through a plurality of

10

control lines 1408 and 1410. Multi-phase generator 1400 functions in a similar manner as the multi-phase generator of FIG. 12. That is every clock cycle, 4 shifts are perform to generate 4 different phases at the output of each of the fine loops.

FIG. 15 illustrates a system including the memory device having a DLL of the invention. System 1500 includes a processor 1502 connected to memory device 100 via the address bus 108, data bus 114 and control signals 118 which include, but are not limited to, a Chip Select (CS\*), Row Access Strobe (RAS\*), Column Access Strobe (CAS\*), Write Enable (WE\*), Clock Enable (CKE). During a memory access, such as a read or a write operation, processor 1502 provides an address on address bus 108. A combination of the control signals provided on control lines 118 indicates whether a read or a write operation needs to be performed. In case of a read operation, memory device 100 accesses main memory 102 using row decode 104 and column decode 106, and provides data read from main memory 102 to output circuit 112 and consequently to data bus 114. In case of a write operation, memory device 100 receives external data provided on data bus 114 at input circuit 110. The data is then written into main memory 102 at a location indicated by an address provided on address bus

Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art that any arrangement which is calculated to achieve the same purpose may be substituted for the specific embodiment shown. This application is intended to cover any adaptations or variations of the present invention. Therefore, it is intended that this invention be limited only by the claims and the equivalents thereof.

What is claimed is:

- 1. A delay locked loop system comprising:

- a coarse loop to produce a first delayed signal, the coarse loop including

- a delay range and including:

- a phase detector;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements;

- a fine loop connected to the coarse loop to receive the first delay signal to produce a second delayed signal, the fine loop having a delay range, wherein the delay range of the fine loop is substantially smaller than the delay range of the coarse loop.

- 2. The delay locked loop of claim 1, wherein the coarse loop comprises:

- a first phase detector connected to an input node;

- a first shift register connected to the phase detector; and

- a first delay line connected to the input node and the first shift register, the first delay line having a first output node.

- 3. The delay locked loop system of claim 1, wherein the fine loop comprises:

- a fine phase detector connected to the input node;

- a fine shift register connected to the fine phase detector; and

- a fine delay line connected to the fine shift register, the fine delay line having an output node to produce the second delayed signal.

11

- 4. The delay locked loop system of claim 1, wherein the coarse loop further comprises a plurality of delay stages, when one delay stage is activated, previous delay stages are disabled.

- 5. The delay locked loop of claim 4, wherein each of the 5 delay stages comprises a plurality of delay cells, each of the delay cells having a plurality of delay elements, wherein the delay elements are the same type of elements and have the same time delay.

- 6. The delay locked loop of claim 2, wherein the first 10 delay line has an entry point, wherein the entry point is shifted by the first shift register in one direction to increase the amount of delay and is shifted in another direction to decrease the amount of delay.

- 7. The delay locked loop system of claim 3 further 15 comprising a delay model circuit connected to the coarse and fine loops, the delay model circuit delaying the second delayed signal to provide a feedback signal.

- 8. A delay locked loop system comprising:

- a first input node to receive an input signal;

- a second input node to receive a feedback signal:

- a coarse loop connected to the first and second input nodes to receive the input and feedback signals to produce a first delayed signal, wherein the first delay and feedback signals have a skew, the coarse loop including:

- a phase detector connected to the first and second input nodes:

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein 30 each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements; and

- a fine loop connected to the first and second input nodes and the coarse loop to receive the input, feedback and first delayed signals to produce a second delayed signal, the second delayed and feedback signals having a skew that is smaller than the skew between the first delayed and feedback signal.

- 9. The delay locked loop of claim 8, wherein the coarse loop comprises:

- a first phase detector connected to an input node;

- a first shift register connected to the phase detector; and

- a first delay line connected to the input node and the first 45 shift register, the first delay line having a first output node.

- 10. The delay locked loop system of claim 8, wherein the fine loop comprises:

- inputs node;

- a fine shift register connected to the fine phase detector;

- a fine delay line connected to the first output node and the output node.

- 11. The delay locked loop system of claim 8, wherein the coarse loop further comprises a plurality of delay stages, when one delay stage is activated, unnecessary delay stages are inactivated.

- 12. The delay locked loop of claim 11, wherein each of the delay stages comprises a plurality of delay cells, each of the delay cells having a plurality of delay elements, wherein the delay elements are the same type of elements and have the same time delay.

- 13. The delay locked loop system of claim 8, wherein the delay line has an entry point, wherein the entry point is

12

shifted by the shift register in one direction to increase an amount of delay applied to the input signal and is shifted in another direction to decrease an amount of delay applied to the input signal.

- 14. The delay locked loop system of claim 8 further comprising a delay model circuit connected to the coarse and fine loops.

- 15. A delay locked loop system comprising:

- an input node to receive an input signal;

- a forward path connected to the input node, the forward path having a first delay locked loop circuit and a second delay locked loop circuit, wherein the first delay locked loop circuit has a first delay range and the second delay locked loop circuit has a second delay range, and wherein the forward path produces a delayed signal, wherein the first delay locked loop circuit including:

- a phase detector;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements; and

- a feedback path connected to the forward path to delay the delayed signal to produce a feedback signal, the feedback signal being fed back to the forward, wherein the forward path applies variable amounts of delay to the input signal until the input signal and the feedback signal are synchronized.

- 16. The delay locked loop of claim 15, wherein the first loop comprises:

- a first phase detector connected to an input node;

- a first shift register connected to the phase detector; and

- a first delay line connected to the input node and the first shift register, the first delay line having a first output node.

- 17. The delay locked loop system of claim 15, wherein the second delay locked loop circuit comprises:

- a fine phase detector connected to the input node;

- a fine shift register connected to the fine phase detector;

- a fine delay line connected to the fine shift register, the fine delay line having an output node to produce the second delayed signal.

- 18. The delay locked loop system of claim 15, wherein the first delay locked loop circuit further comprises a plurality of a fine phase detector connected to the first and second 50 delay stages, when one delay stage is activated, previous delay stages are disabled.

- 19. The delay locked loop of claim 18, wherein each of the delay stages comprises a plurality of delay cells, each of the delay cells having a plurality of delay elements, wherein the fine shift register, the fine delay line having a second 55 delay elements are the same type of elements and have the same time delay.

- 20. The delay locked loop system of claim 15, wherein the delay line has an entry point, wherein the entry point is shifted by the shift register in one direction to increase an amount of delay applied to the input signal and is shifted in another direction to decrease an amount of delay applied to the input signal.

- 21. The delay locked loop system of claim 15, wherein the feedback path comprising a delay model circuit to delay the 65 delayed signal to provide the feedback signal.

- 22. A delay locked loop system comprising: an input node to receive a clock signal;

- a coarse loop comprising:

- a phase detector connected to the input node;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein 5 each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements, wherein the delay cells are connected to the input node to receive the clock signal to produce a first delayed signal, wherein the first delayed signal and the clock signal has a first skew;

- a fine loop connected to the coarse loop to receive the first delayed signal to produce a second delayed signal, wherein the second delayed signal and the clock signal have a second skew, wherein the second skew is 15 substantially smaller than the first skew; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce a feedback signal.

- 23. The delay locked loop system of claim 22, wherein the coarse loop further comprises a plurality of delay stages, when one delay stage is activated, previous delay stages are

- 24. The delay locked loop of claim 23, wherein each of the delay stages comprises a plurality of delay cells, each of the delay cells having a plurality of delay elements, wherein the delay elements are the same type of elements and have the same time delay.

- 25. The delay locked loop system of claim 22, wherein the delay line has an entry point, wherein the entry point is shifted by the shift register in one direction to increase an 30 amount of delay applied to the input signal and is shifted in another direction to decrease an amount of delay applied to the input signal.

- **26**. A memory device comprising:

- a main memory:

- an output circuit connected to the main memory, the output circuit having an output pad for producing an output signal; and

- a delay locked loop system connected to the output  $_{40}$ circuit, the delay locked loop system comprises:

- a coarse loop to produce a first delayed signal, the coarse loop including a first delay range and includ

- a phase detector;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells 50 includes a plurality of identical delay elements;

- a fine loop connected to the coarse loop to receive the first delay signal to produce a second delayed signal, the fine loop having a second delay range, wherein the second delay range is substantially smaller than 55 the first delay range; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce a strobe signal.

- 27. The memory of claim 26, wherein the delay model circuit and the output circuit have the same construction.

- **28**. A memory device comprising:

- a main memory:

- an output circuit connected to the main memory, the output circuit having an output pad for producing an output signal; and

- a delay locked loop system connected to the output circuit, the delay locked loop system comprising:

14

- an input node to receive an input signal;

- a coarse loop connected to the input node to receive the input signal to produce a first delayed signal, wherein the first delayed signal and the input signal has a first skew, the coarse loop including:

- a phase detector connected to the first and second input nodes;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements;

- a fine loop connected to the coarse loop to receive the first delayed signal to produce a second delayed signal, wherein the second delayed signal and the input signal has a second skew, wherein the second skew is substantially smaller than the first skew; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce a strobe signal.

- 29. The memory of claim 28, wherein the delay model circuit and the output circuit have the same construction.

- **30**. A memory device comprising:

- a main memory;

35

60

- an output circuit connected to the main memory, the output circuit having an output pad for producing an output signal; and

- a delay locked loop system connected to the output circuit, the delay locked loop system comprising: an input node to receive a clock signal;

- a coarse loop comprising:

- a phase detector connected to the input node;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements, wherein the delay cells are connected to the input node to receive the clock signal to produce a first delayed signal, wherein the first delayed signal and the clock signal has a first skew;

- a fine loop connected to the coarse loop to receive the first delayed signal to produce a second delayed signal, wherein the second delayed signal and the clock signal have a second skew, wherein the second skew is substantially smaller than the first skew; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce a feedback

- 31. The memory of claim 30, wherein the delay model circuit and the output circuit have the same construction.

- **32**. A system comprising:

- a processor; and

- a memory device connected to the processor, the memory device comprising:

- a main memory;

- an output circuit connected to the main memory, the output circuit having an output pad for producing an output signal; and

- a delay locked loop system connected to the output circuit, the delay locked loop system comprises:

- a coarse loop to produce a first delayed signal, the coarse loop including a first delay range and including:

- a phase detector;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected 5 to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements;

- a fine loop connected to the coarse loop to produce a second delayed signal, the fine loop having a 10 second delay range, wherein the second delay range is substantially smaller than the first delay range; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce a 15 strobe signal.

#### 33. A system comprising:

- a processor; and

- a memory device connected to the processor, the memory device comprising:

- a main memory;

- an output circuit connected to the main memory, the output circuit having an output pad for producing an output signal; and

- a delay locked loop system connected to the output circuit, the delay locked loop system comprising: an input node to receive an input signal;

- a coarse loop connected to the input node to receive the input signal to produce a first delayed signal, wherein the first delayed signal and the input signal has a first skew, the coarse loop including:

- a phase detector connected to the first and second input nodes;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements:

- a fine loop connected to receive the first delayed signal to produce a second delayed signal, wherein

16

- the second delayed signal and the input signal has a second skew, wherein the second skew is substantially smaller than the first skew; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce a strobe signal.

#### **34**. A system comprising:

- a processor; and

- a memory device connected to the processor, the memory device comprising:

- a main memory;

- an output circuit connected to the main memory, the output circuit having an output pad for producing an output signal; and

- a delay locked loop system connected to the output circuit, the delay locked loop system comprising: an input node to receive a clock signal;

- a coarse loop comprising:

- a phase detector connected to the input node;

- a shift register connected to the phase detector, the shift register including a plurality of register cells;

- a delay line including a plurality of delay cells, wherein each of the register cells is connected to two delay cells, wherein each of the delay cells includes a plurality of identical delay elements, wherein the delay cells are connected to the input node to receive the clock signal to produce a first delayed signal, wherein the first delayed signal and the input signal has a first skew;

- a fine loop connected to the coarse loop to receive the first delayed signal to produce a second delayed signal, wherein the second delayed signal and the clock signal has a second skew, wherein the second skew is substantially smaller than the first skew; and

- a delay model circuit connected to the fine loop to delay the second delayed signal to produce an output signal.

\* \* \* \* \*

# UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO. : 6,445,231 B1 Page 1 of 1

DATED : September 3, 2002

INVENTOR(S) : R. Jacob Baker and Feng Lin

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

#### Column 11,

Line 29, insert -- and -- after "cells;".

#### Column 12,

Lines 12 and 16, delete "wherein" before "the".

Lines 13 and 14, delete "has" and insert -- having --, therefor.

Line 15, delete "and wherein" before "the".

Line 15, delete "produces" and insert -- producing --, therefor.

Line 28, insert -- path -- after "forward".

#### Column 13,

Lines 4 and 47, insert -- and -- after "cells;".

#### Column 14,

Lines 9 and 35, insert -- and -- after "cells;".

#### Column 15,

Lines 3 and 37, insert -- and -- after "cells;".

#### Column 16,

Line 23, insert -- and -- after "cells;".

Signed and Sealed this

First Day of April, 2003

JAMES E. ROGAN

Director of the United States Patent and Trademark Office