#### US006026050A

**Patent Number:**

**Date of Patent:**

## United States Patent [19]

#### Baker et al.

# · OF

5-282868 10/1993 Jai

[11]

[45]

6,026,050

Feb. 15, 2000

[54] METHOD AND APPARATUS FOR ADAPTIVELY ADJUSTING THE TIMING OF A CLOCK SIGNAL USED TO LATCH DIGITAL SIGNALS, AND MEMORY DEVICE USING SAME

[75] Inventors: Russel Jacob Baker; Troy A.

Manning, both of Meridian, Id.

[73] Assignee: Micron Technology, Inc., Boise, Id.

[21] Appl. No.: 09/248,194

[22] Filed: Feb. 10, 1999

#### Related U.S. Application Data

| [63] | Continuation of application | No. 08/890,055, Jul. 9, 1997. |

|------|-----------------------------|-------------------------------|

| [51] | Int. Cl. <sup>7</sup>       | G11C 7/00                     |

| [52] | U.S. Cl                     |                               |

| [58] | Field of Search             |                               |

|      |                             | 365/230.01, 189.01            |

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,633,174 | 1/1972 | Griffin 340/1       | 172.5 |

|-----------|--------|---------------------|-------|

| 4,077,016 | 2/1978 | Sanders et al 3     | 331/4 |

| 4,096,403 | 6/1978 | Schroeder et al 307 | 7/362 |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

| 0 295 515 A1 | 12/1988 | European Pat. Off. |

|--------------|---------|--------------------|

| 0 406 786 A1 | 1/1991  | European Pat. Off. |

| 0 450 871 A2 | 10/1991 | European Pat. Off. |

| 0 476 585 A3 | 3/1992  | European Pat. Off. |

| 0 655 741 A2 | 5/1995  | European Pat. Off. |

| 0 655 834 A1 | 5/1995  | European Pat. Off. |

| 0 680 049 A2 | 11/1995 | European Pat. Off. |

| 0 703 663 A1 | 3/1996  | European Pat. Off. |

| 0 704 848 A3 | 4/1996  | European Pat. Off. |

| 0 704 975 A1 | 4/1996  | European Pat. Off. |

| 0 767 538 A1 | 4/1997  | European Pat. Off. |

| 6-1237512    | 10/1986 | Japan .            |

| 2-112317     | 4/1990  | Japan .            |

| 4-135311     | 5/1992  | Japan .            |

| 5-136664     | 6/1993  | Japan .            |

|              |         |                    |

| 5-282868    | 10/1993 | Japan . |

|-------------|---------|---------|

| 0-7319577   | 12/1995 | Japan . |

| WO 94/29871 | 12/1994 | WÎPO .  |

| WO 95/22206 | 8/1995  | WIPO .  |

| WO95/22200  | 8/1995  | WIPO .  |

| WO 96/10866 | 4/1996  | WIPO .  |

| WO 97/14289 | 4/1997  | WIPO .  |

| WO 97/42557 | 11/1997 | WIPO .  |

#### OTHER PUBLICATIONS

Alvarez, J. et al. "A Wide–Bandwidth Low Voltage PLL for PowerPC <sup>TM</sup> Microprocessors" IEEE IEICE Trans. Electron., vol. E–78. No. 6, Jun. 1995, pp. 631–639.

Anonymous, "Programmable Pulse Generator", IBM Technical Disclosure Bulletin, vol. 17, No. 12, May 1975, pp. 3553–3554.

Anonymous, "Pulse Combining Network", IBM Tehnical Disclosure Bulletin, vol. 32, No. 12, May 1990, pp. 149–151.

Anonymous, "Variable Delay Digital Circuit", IBM Technical Disclosure Bulletin, vol. 35, No. 4A, Sep. 1992, pp. 365–366.

(List continued on next page.)

Primary Examiner—Vu A. Le Attorney, Agent, or Firm—Dorsey & Whitney LLP

#### [57] ABSTRACT

A system for adjusting the phase of an internal clock signal relative to an external clock signal in a packetized dynamic random access memory device. The system applies a plurality of initialization packets of the memory device that are captured in a shift register responsive to a transition of the internal clock signal. However, the phase of the internal clock signal is sequentially incremented after each initialization packet has been captured in the shift register. After a plurality of initialization packets have been captured, an evaluation circuit identifies which phases of the internal clock signal clocked the shift register at the proper time to accurately capture each initialization packet. A single phase of the internal clock signal is then selected from within the range of internal clock signal phases that successfully captured initialization packets. This selected phase of the internal clock signal is used during normal operation of the memory device.

#### 27 Claims, 17 Drawing Sheets

|                        | U.S. PA            | TENT DOCUMENTS             |

|------------------------|--------------------|----------------------------|

| 4,404,474              | 9/1983             | Dingwall 307/260           |

| 4,481,625              | 11/1984            | Roberts et al 370/85       |

| 4,511,846              | 4/1985             | Nagy et al 328/164         |

| 4,514,647              | 4/1985             | Shoji                      |

| 4,600,895              | 7/1986             | Landsman 331/1 A           |

| 4,638,187              | 1/1987             | Boler et al                |

| 4,687,951              | 8/1987             | McElroy                    |

| 4,773,085<br>4,789,796 | 9/1988<br>12/1988  | Cordell                    |

| 4,893,087              | 1/1990             | Davis                      |

| 4,902,986              | 2/1990             | Lesmeister                 |

| 4,958,088              | 9/1990             | Farah-Bakhsh et al 307/443 |

| 4,984,204              | 1/1991             | Sato et al                 |

| 5,020,023              | 5/1991             | Smith                      |

| 5,038,115<br>5,086,500 | 8/1991<br>2/1992   | Myers et al                |

| 5,080,300              | 2/1992             | Sato et al                 |

| 5,122,690              | 6/1992             | Bianchi 307/475            |

| 5,128,560              | 7/1992             | Chern et al 307/475        |

| 5,128,563              | 7/1992             | Hush et al                 |

| 5,134,311              | 7/1992<br>9/1992   | Biber et al                |

| 5,150,186<br>5,165,049 | 11/1992            | Pinney et al               |

| 5,179,298              | 1/1993             | Hirano et al               |

| 5,194,765              | 3/1993             | Dunlop et al 307/443       |

| 5,212,601              | 5/1993             | Wilson 360/51              |

| 5,220,208              | 6/1993             | Schenck                    |

| 5,239,206<br>5,243,703 | 8/1993<br>9/1993   | Yanai                      |

| 5,254,883              | 10/1993            | Horowitz et al             |

| 5,256,989              | 10/1993            | Parker et al               |

| 5,257,294              | 10/1993            | Pinto et al 375/120        |

| 5,268,639              | 12/1993            | Gasbarro et al             |

| 5,274,276              | 12/1993            | Casper et al               |

| 5,276,642<br>5,278,460 | 1/1994<br>1/1994   | Lee                        |

| 5,281,865              | 1/1994             | Yamashita et al            |

| 5,283,631              | 2/1994             | Koerner et al 307/451      |

| 5,295,164              | 3/1994             | Yamamura                   |

| 5,311,481              | 5/1994             | Casper et al               |

| 5,311,483<br>5,321,368 | 5/1994<br>6/1994   | Takasugi                   |

| 5,337,285              | 8/1994             | Ware et al                 |

| 5,347,177              | 9/1994             | Lipp 307/443               |

| 5,347,179              | 9/1994             | Casper et al 307/451       |

| 5,355,391              | 10/1994            | Horowitz et al             |

| 5,361,002<br>5,390,308 | 11/1994<br>2/1995  | Casper                     |

| 5,400,283              | 3/1995             | Raad                       |

| 5,408,640              | 4/1995             | MacIntyre et al 395/550    |

| 5,410,263              | 4/1995             | Waizman 327/141            |

| 5,416,436              | 5/1995             | Rainard                    |

| 5,420,544<br>5,428,311 | 5/1995<br>6/1995   | Ishibashi                  |

| 5,430,676              | 7/1995             | Ware et al                 |

| 5,432,823              | 7/1995             | Gasbarro et al             |

| 5,438,545              | 8/1995             | Sim                        |

| 5,440,260              | 8/1995             | Hayashi et al              |

| 5,440,514              | 8/1995<br>8/1995   | Flannagan et al            |

| 5,446,696<br>5,448,193 | 9/1995             | Ware et al                 |

| 5,451,898              | 9/1995             | Johnson 327/563            |

| 5,457,407              | 10/1995            | Shu et al                  |

| 5,465,076              | 11/1995            | Yamauchi et al             |

| 5,473,274<br>5,473,575 | 12/1995            | Reilly et al               |

| 5,473,575<br>5,473,639 | 12/1995<br>12/1995 | Farmwald et al             |

| 5,485,490              | 1/1996             | Leung et al                |

| 5,488,321              | 1/1996             | Johnson 327/66             |

| 5,489,864              | 2/1996             | Ashuri                     |

| 5,497,127 | 3/1996  | Sauer                         |

|-----------|---------|-------------------------------|

| 5,498,990 | 3/1996  | Leung et al 327/323           |

| 5,506,814 | 4/1996  | Hush et al 365/230.03         |

| 5,508,638 | 4/1996  | Cowles et al 326/38           |

| 5,513,327 | 4/1996  | Farmwald et al 395/309        |

| 5,539,345 | 7/1996  | Hawkins 327/150               |

| 5,544,203 | 8/1996  | Casasanta et al 375/376       |

| 5,552,727 | 9/1996  | Nakao                         |

| 5,568,075 | 10/1996 | Curran et al                  |

| 5,568,077 | 10/1996 | Sato et al                    |

| 5,572,557 | 11/1996 | Aoki                          |

| 5,574,698 | 11/1996 | Raad                          |

| 5,576,645 | 11/1996 | Farwell                       |

| 5,577,236 | 11/1996 | Johnson et al                 |

| 5,578,940 | 11/1996 | Dillon et al                  |

| 5,578,941 | 11/1996 | Sher et al 326/34             |

| 5,579,326 | 11/1996 | McClure 371/61                |

| 5,581,197 | 12/1996 | Motley et al 326/30           |

| 5,589,788 | 12/1996 | Goto                          |

| 5,590,073 | 12/1996 | Arakawa et al 365/185.08      |

| 5,594,690 | 1/1997  | Rothenberger et al 365/189.01 |

| 5,614,855 | 3/1997  | Lee et al                     |

| 5,619,473 | 4/1997  | Hotta                         |

| 5,621,340 | 4/1997  | Lee et al                     |

| 5,621,690 | 4/1997  | Jungroth et al                |

| 5,621,739 | 4/1997  | Sine et al                    |

| 5,627,780 | 5/1997  | Malhi                         |

| 5,627,791 | 5/1997  | Wright et al                  |

| 5,631,872 | 5/1997  | Naritake et al 365/227        |

| 5,636,163 | 6/1997  | Furutani et al                |

| 5,636,173 | 6/1997  | Schaefer                      |

| 5,636,174 | 6/1997  | Rao                           |

| 5,638,335 | 6/1997  | Akiyama et al 365/230.03      |

| 5,657,481 | 8/1997  | Farmwald et al 395/551        |

| 5,668,763 | 9/1997  | Fujioka et al                 |

| 5,692,165 | 11/1997 | Jeddeloh et al 395/551        |

| 5,694,065 | 12/1997 | Hamasaki et al 327/108        |

| 5,712,580 | 1/1998  | Baumgartner et al 327/12      |

| 5,719,508 | 2/1998  | Daly 327/12                   |

| 5,740,123 | 4/1998  | Uchida                        |

| 5,751,665 | 5/1998  | Tanoi                         |

| 5,789,947 | 8/1998  | Sato 327/3                    |

| 5,926,436 | 7/1999  | Toda et al                    |

|           |         |                               |

#### OTHER PUBLICATIONS

Arai, Y. et al., "A CMOS Four Channel ×1K Time Memory LSI with 1–ns/b Resolution", IEEE Journal of Solid–State Circuits, vol. 27, No. 3, M, 8107 Mar., 1992, No. 3, New York, US, pp. 359–365 and pp. 528–531.

Arai, Y. et al., "A Time Digitizer CMOS Gate—Array with a 250 ps Time Resolution", XP 000597207, IEEE Journal of Solid—State Circuits, vol. 31, No. 2, Feb. 1996, pp. 212–220. Aviram, A. et al., "Obtaining High Speed Printing on Thermal Sensitive Special Paper With a Sensitive Ribbon Print Head", IBM Technical Disclosure Bulletin, vol. 27, No. 5, Oct. 1984, pp. 3059–3060.

Bazes, M., "Two Novel Fully Complementary Self-Biased CMOS Differential Amplifiers", IEEE Journal of Solid-State Circuits, vol. 26, No. 2, Feb 1991, pp. 165–168.

Chapman, J. et al., "A Low-Cost High-Performance CMOS Timing Vernier for ATE", IEEE International Test Conference, Paper 21.2, 1995, pp. 459–468.

Cho, J. "Digitally-Controlled PLL with Pulse Width Detection Mechanism for Error Correction", ISSCC 1997, Paper No. SA 20.3, pp. 334–335.

Christiansen, J., "An Integrated High Resolution CMOS Timing Generator Based on an Array of Delay Locked Loops", IEEE Journal of Solid–State Circuits, vol. 31, No. 7, Jul. 1996, pp. 952–957.

Combes, M. et al., "A Portable Clock Multiplier Generator Using Digital CMOS Standard Cells", IEEE Journal of Solid–State Circuits, vol. 31, No. 7, Jul. 1996, pp. 958–965. Descriptive literature entitled, "400MHz SLDRAM, 4M ×16 SLDRAM Pipelined, Eight Bank, 2.5 V Operation," SLDRAM Consortium Advance Sheet, published throughout the United States, pp. 1–22.

Donnelly, K. et al., "A 660 MB/s Interface Megacell Portable Circuit in 0.3  $\mu$ m $-0.7 \mu$ m CMOS ASIC", IEEE Journal of Solid–State Circuits, vol. 31, No. 12, Dec. 1996, pp. 1995–2001.

"Draft Standard for a High-Speed Memory Interface (SyncLink)", Microprocessor and Microcomputer Standards Subcommittee of the IEEE Computer Society, Copyright 1996 by the Institute of Electrical and Electronics Engineers, Inc., New York, NY, pp. 1–56.

Goto, J. et al., "A PLL–Based Programmable Clock Generator with 50–to 350–MHz Oscillating Range for Video Signal Processors", IEICE Tans. Electron., vol. E77–C, No. 12, Dec. 1994, pp. 1951–1956.

Hamamoto, T., "400–MHz Random Column Operating SDRAM Techniques with Self–Skew Compensation", IEEE Journal of Solid–State Circuits, vol. 33, No. 5, May 1998, pp. 770–778.

Ishibashi, A. et al., "High–Speed Clock Distribution Architecture Employing PLL for 0.6µm CMOS SOG", IEEE Custom Integrated Circuits Conference, 1992, pp. 27.6.1–27.6.4.

Kim, B. et al., "A 30MHz High–Speed Analog/Digital PLL in 2µm CMOS", ISSCC, Feb. 1990.

Kikuchi, S. et al., "A Gate–Array–Based 666MHz VLSI Test System", IEEE International Test Conference, Paper 21.1, 1995, pp. 451–458.

Ko, U, et al., "A 30-ps Jitter, 3.6-µs Locking, 3.3-Volt Digital PLL For CMOS Gate Arrays", IEEE Custom Integrated Circuits Conference, 1993, pp. 23.3.1-23.3.4.

Lee, T. et al., "A 2.5V Delay–Locked Loop for an 18Mb 500MB/s DRAM", IEEE International Solid–State Circuits Conference Digest of Technical Papers, Paper No. FA 18.6, 1994, pp. 300–301.

Lesmeister, G., "A Densely Integrated High Performance CMOS Tester", International Test Conference, Paper 16.2, 1991, pp. 426–429.

Ljuslin, C. et al., "An Integrated 16-channel CMOS Time to Digital Converter", IEEE Nuclear Sciences Symposium & Medical Imaging Conference Record, vol. 1, 1993, pp. 625–629.

Maneatis, J., "Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques", IEEE Journal of Solid-State Circuits, vol. 31, No. 11, Nov. 1996, pp. 1723–1732.

Nakamura, M. et al., "A 156 Mbps CMOS Clock Recovery Circuit for Burst-mode Transmission", Symposium on VLSI Circuits Digest of Technical Papers, 1996, pp. 122–123.

Nielson, E., "Inverting latches make simple VCO", EDN, Jun. 19, 1997.

Novof, I. et al., "Fully Integrated CMOS Phase–Locked Loop with 15 to 240 MHz Locking Range and ±50 ps JItter", IEEE Journal of Solid–State Circuits, vol. 30, No. 11, Nov. 1995, pp. 1259–1266.

Santos, D. et al., "A CMOS Delay Locked Loop And Sub-Nanosecond Time-to-Digital Converter Chip", IEEE Nuclear Science Symposium and Medical Imaging Conference Record, vol. 1 Oct. 1995, pp. 289–291.

Saeki, T. et al., "A 2.5-ns Clock Access, 250-MHz 256-Mb SDRAM with Synchronous Mirror Delay", IEEE Journal of Solid-State Circuits, vol. 31, No. 11, Nov. 1996, pp. 1656-1665.

Shirotori, T. et al., "PLL-based, Impedance Controlled Output Buffer", 1991 Symposium on VLSI Circuits Digest of Technical Papers, pp. 49–50.

Sidiropoulos, S. et al., "A 700–Mb/s/pin CMOS Signaling Inteface Using Current Integrating Receivers", IEEE Journal of Solid–State Circuits, vol. 32, No. 5, May 1997, pp. 681–690.

Sidiropoulos, S. et al., "A CMOS 500 Mbps/pin synchronous point to point link inteface", IEEE Synposium on VLSI Circuits Digest of Technical Papers, 1994, pp. 43–44.

Sidiropoulos, S. et al., "A Semi–Digital DLL with Unlimited Phase Shift Capability and 0.08–400MHz Operating Range, "IEEE International Solid State Circuits Conference, Feb. 8, 1997, pp. 332–333.

Soyuer, M. et al., "A Fully Monolithic 1.25GHz CMOS Frequency Synthesizer", IEEE Symposium on VLSI Circuits Digest of Technical Papers, 1994, pp. 127–128.

Taguchi, M. et al., "A 40–ns 64–Mb DRAM with 64–b Parallel Data Bus Architecture", IEEE Journal of Solid-State Circuits, vol. 26, No. 11, Nov. 1991, pp. 1493–1497. Tanoi, S. et al., "A 250–622 MHz Deskew and Jitter–Suppressed Clock Buffer Using a Frequency– and Delay–Locked Two–Loop Architecture", 1995 Symposium on VLSI Circuits Digest of Technical Papers, vol. 11, No. 2, pp. 85–86.

Tanoi, S. et al., "A 250–622 MHz Deskew and Jitter–Suppressed Clock Buffer Using Two–Loop Architecture", IEEE IEICE Trans. Electron., vol. E–79–C. No. 7, Jul. 1996, pp. 898–904.

von Kaenel, V. et al., "A 320 MHz, 1.5 mW @ 1.35 V CMOS PLL for Microprocessor Clock Generation", IEEE Journal of Solid–State Circuits, vol. 31, No. 11, Nov. 1996, pp. 1715–1722.

Watson, R. et al., "Clock Buffer Chip with Absolute Delay Regulation Over Process and Environmental Variations", IEEE Custom Integrated Circuits Conference, 1992, pp. 25.2.1–25.2.5.

Yoshimura, T. et al., "A 622–Mb/s Bit/Frame Synchronizer for High–Speed Backplane Data Communication", IEEE Journal of Solid–State Circuits, vol. 31, No. 7, Jul. 1996, pp. 1063–1066.

Fig. 3

Feb. 15, 2000

Fig. 6

Fig. 7A

Fig. 7B

Feb. 15, 2000

Fig. 9

Fig. 10

Fig. 11

Fig. 13

Fig. 14

Fig. 15

#### METHOD AND APPARATUS FOR ADAPTIVELY ADJUSTING THE TIMING OF A CLOCK SIGNAL USED TO LATCH DIGITAL SIGNALS, AND MEMORY DEVICE **USING SAME**

#### CROSS-REFERENCE TO RELATED APPLICATION

This application is a continuation of pending U.S. patent application Ser. No. 08/890,055, filed Jul. 9, 1997.

#### TECHNICAL FIELD

The present invention relates to integrated circuit devices, and more particularly, to adjusting the timing of an internal 15 clock signal derived from an external clock signal so that it can be used to latch an external digital signal at the optimum time.

#### BACKGROUND OF THE INVENTION

Conventional computer systems include a processor coupled to a variety of memory devices, including read-only memories ("ROMs") which traditionally store instructions for the processor, and a system memory to which the processor may write data and from which the processor may read data. The processor may also communicate with an external cache memory, which is generally a static random access memory ("SRAM"). The processor also communicates with input devices, output devices, and data storage devices.

Processors generally operate at a relatively high speed. Processors such as the Pentium® and Pentium Pro® microprocessors are currently available that operate at clock speeds of at least 200 MHz. However, the remaining components of the computer system, with the exception of SRAM cache memory, are not capable of operating at the speed of the processor. For this reason, the system memory devices, as well as the input devices, output devices, and data storage devices, are not coupled directly to the processor bus. Instead, the system memory devices are generally coupled to the processor bus through a memory controller, and the input devices, output devices, and data storage devices are coupled to the processor bus through a bus bridge. The memory controller allows the system memory devices to operate at a clock frequency that is substantially lower than the clock frequency of the processor. Similarly, the bus bridge allows the input devices, output devices, and data storage devices to operate at frequency that is a substantially lower than the clock frequency of the processor. Currently, for example, a processor having a 200 MHz clock frequency may be mounted on a mother board having a 66 MHz clock frequency for controlling the system memory devices and other components.

processor.

The time required for the processor, operating, for example, at 200 MHz, to read data from or write data to a system memory device operating at, for example, 66 MHz, greatly slows the rate at which the processor is able to accomplish its operations. Thus, much effort has been devoted to increasing the operating speed of system memory devices.

System memory devices are generally dynamic random access memories ("DRAMs"). Initially, DRAMs were asyn- 65 these components. chronous and thus did not operate at even the clock speed of the motherboard. In fact, access to asynchronous DRAMs

often required that wait states be generated to halt the processor until the DRAM had completed a memory transfer. However, the operating speed of asynchronous DRAMs was successfully increased through such innovations as burst and page mode DRAMs, which did not require that an address be provided to the DRAM for each memory access. More recently, synchronous dynamic random access memories ("SDRAMs") have been developed to allow the pipelined transfer of data at the clock speed of the motherboard. However, even SDRAMs are typically incapable of operating at the clock speed of currently available processors. Thus, SDRAMs cannot be connected directly to the processor bus, but instead must interface with the processor bus through a memory controller, bus bridge, or similar device. The disparity between the operating speed of the processor and the operating speed of SDRAMs continues to limit the speed at which processors may complete operations requiring access to system memory.

A solution to this operating speed disparity has been proposed in the form of a computer architecture known as "SyncLink." In the SyncLink architecture, the system memory may be coupled to the processor directly through the processor bus. Rather than requiring that separate address and control signals be provided to the system memory, SyncLink memory devices receive command packets that include both control and address information. The SyncLink memory device then outputs or receives data on a data bus that is coupled directly to the data bus portion of the processor bus.

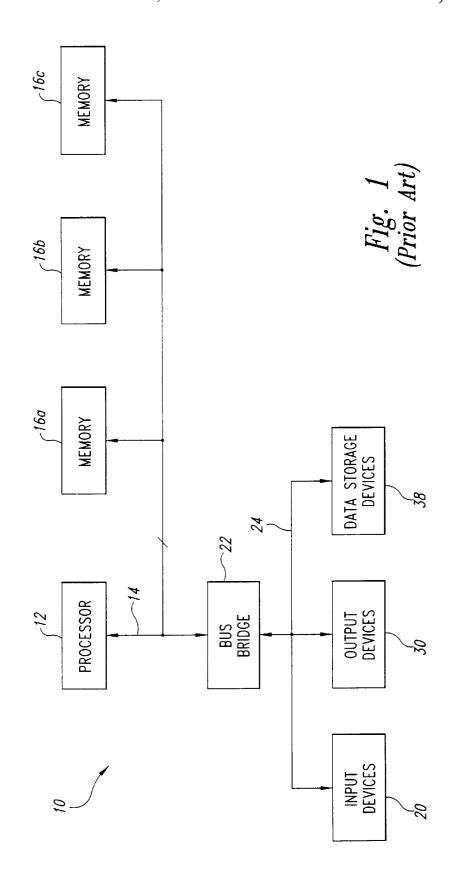

An example of a computer system 10 using the SyncLink architecture is shown in FIG. 1. The computer system 10 includes a processor 12 having a processor bus 14 coupled to three packetized dynamic random access memory or SyncLink DRAMs ("SLDRAM") devices 16a-c. The computer system 10 also includes one or more input devices 20, such as a keypad or a mouse, coupled to the processor 12 through a bus bridge 22 and an expansion bus 24, such as an industry standard architecture ("ISA") bus or a Peripheral component interconnect ("PCI") bus. The input devices 20 allow an operator or an electronic device to input data to the computer system 10. One or more output devices 30 are coupled to the processor 12 to display or otherwise output data generated by the processor 12. The output devices 30 are coupled to the processor 12 through the expansion bus 24, bus bridge 22 and processor bus 14. Examples of output 45 devices 24 include printers and a video display units. One or more data storage devices 38 are coupled to the processor 12 through the processor bus 14, bus bridge 22, and expansion bus 24 to store data in or retrieve data from storage media (not shown). Examples of storage devices 38 and storage media include fixed disk drives floppy disk drives, tape cassettes and compact-disk read-only memory drives.

In operation, the processor 12 communicates with the memory devices 16a-c via the processor bus 14 by sending the memory devices 16a-c command packets that contain Access to system memory is a frequent operation for the 55 both control and address information. Data is coupled between the processor 12 and the memory devices 16a-c, through a data bus portion of the processor bus 14. Although all the memory devices 16a-c are coupled to the same conductors of the processor bus 14, only one memory device 16a-c at a time reads or writes data, thus avoiding bus contention on the processor bus 14. Bus contention is avoided by each of the memory devices 16a-c on the bus bridge 22 having a unique identifier, and the command packet contains an identifying code that selects only one of

> The computer system 10 also includes a number of other components and signal lines which have been omitted from

FIG. 1 in the interests of brevity. For example, as explained below, the memory devices 16a-c also receive an external clock signal CKEXT to provide internal timing signals, a data clock signal DCLK clocking data into or out of the memory device 16, and a FLAG signal signifying the start of a command packet.

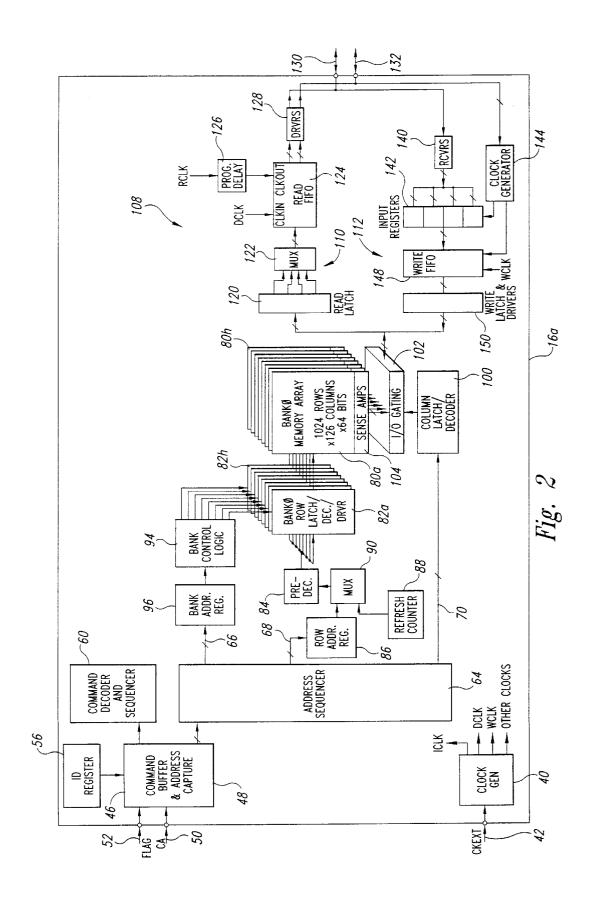

One of the memory devices 16a is shown in block diagram form in FIG. 2. The memory device 16a includes a clock generator circuit 40 that receives a master clock signal CKEXT and generates an internal clock signal CKINT and a large number of other clock and timing signals to control the timing of various operations in the memory device 16. The memory device 16 also includes a command buffer 46 and an address capture circuit 48 which receive an internal clock signal CKINT, a command packet CA0-CA9 on a 10-bit command bus 50, and a FLAG signal on line 52. The memory controller (not shown) or other device normally transmits the command packet CA0-CA9 to the memory device 16a in synchronism with the external clock signal CKEXT. As explained above, the command packet contains  $_{20}$ control and address information for each memory transfer, and the FLAG signal identifies the start of a command packet which may include more than one 10-bit packet word. In fact, a command packet is generally in the form of a sequence of 10-bit packet words on the 10-bit command bus 50. The command buffer 46 receives the command packet from the bus 50, and compares at least a portion of the command packet to identifying data from an ID register 56 to determine if the command packet is directed to the memory device 16a or some other memory device 16b, c. If the command buffer 46 determines that the command packet is directed to the memory device 16a, it then provides a command word to a command decoder and sequencer 60. The command decoder and sequencer 60 generates a large number of internal control signals to control the operation of 35 the memory device 16a during a memory transfer.

The address capture circuit 48 also receives the command words from the command bus 50 and outputs a 20-bit address corresponding to the address information in the command packet. The address is provided to an address sequencer 64 which generates a corresponding 3-bit bank address on bus 66, a 10-bit row address on bus 68, and a 7-bit column address on bus 70. The column address and row address are processed by column and row address paths 73, 75 as will be described below.

One of the problems of conventional DRAMs is their relatively low speed resulting from the time required to precharge and equilibrate circuitry in the DRAM array. The packetized DRAM 16a shown in FIG. 2 largely avoids this problem by using a plurality of memory banks 80, in this case eight memory banks 80a-h. After a memory read from one bank 80a, the bank 80a can be precharged while the remaining banks 80b-h are being accessed. Each of the memory banks 80a-h receive a row address from a respective row latch/decoder/driver 82a-h. All of the row latch/ decoder/drivers 82a-h receive the same row address from a predecoder 84 which, in turn, receives a row address from either a row address register 86, redundant row circuit 87, or a refresh counter 88 as determined by a multiplexer 90. However, only one of the row latch/decoder/drivers 82a-h is active at any one time as determined by bank control logic 94 as a function of a bank address from a bank address register 96.

The column address on bus **70** is applied through a column address path **75** to a redundant column circuit **71** that 65 determines if the column address corresponds to a defective address. The redundant column circuit **71** outputs either the

4

column address or a redundant column address to a column latch/decoder 100 which supplies I/O gating signals to an I/O gating circuit 102. The I/O gating circuit 102 interfaces with columns of the memory banks 80a-h through sense amplifiers 104. Data is coupled to or from the memory banks **80***a*–*h* through the sense amplifiers **104** and I/O gating circuit 102 to a data path subsystem 108 which includes a read data path 110 and a write data path 112. The read data path 110 includes a bank of DC sense amplifiers 103 and a read latch 120 that amplify and store data from the I/O gating circuit 102. In the memory device 16a shown in FIG. 2, 64 bits of data are stored in the read latch 120. The read latch then provides four 16-bit data words to an output multiplexer 122 that sequentially supplies each of the 16-bit data words to a read FIFO buffer 124. Successive 16-bit data words are clocked through the read FIFO buffer 124 by a clock signal RCLK generated from the internal clock CKINT by a programmable delay circuit 126. The read FIFO buffer 124 sequentially applies the 16-bit words to a driver circuit 128 which, in turn, applies the 16-bit data words to a data bus 130 forming part of the processor bus 14.

The write data path 112 includes a receiver buffer 140 coupled to the data bus 130. The receiver buffer 140 sequentially applies 16-bit words from the data bus 130 to four input registers 142, each of which is selectively enabled by a signal from a clock generator circuit 144 responsive to the data clock DCLK applied to the memory device 16a on line 132. As with the external clock signal CKEXT and command packet CA0-CA9, the memory controller or other device (not shown) normally transmits the data to the memory device 16a in synchronism with the data clock signal DCLK. Thus, the input registers 142 sequentially store four 16-bit data words and combine them into one 64-bit data word applied to a write FIFO buffer 148. The write FIFO buffer 148 is clocked by a signal from the clock generator 144 and an internal write clock WCLK to sequentially apply 64-bit write data to a write latch and driver 150. The write latch and driver 150 applies the 64-bit write data to one of the memory banks 80a-h through the I/O gating circuit 102 and the sense amplifiers 104.

As mentioned above, an important goal of the SyncLink architecture is to allow data transfer between a processor and a memory device to occur at a significantly faster rate. However, as the rate of data transfer increases, it becomes more difficult to maintain synchronization between signals 45 transmitted to the memory device 16a. For example, as mentioned above, the command packet CA0-CA9 is normally transmitted to the memory device 16a in synchronism with the external clock signal CKEXT, and the data is normally transmitted to the memory device 16a in synchronism with the data clock signal DCLK. However, because of unequal signal delays and other factors, the command packet CA0-CA9 may not arrive at the memory device 16a in synchronism with the external clock signal CKEXT, and the data may not arrive at the memory device 16a in synchronism with the data clock signal DCLK. Even if these signals are actually coupled to the memory device 16a in synchronism with each other, they may loose synchronism once they are coupled to circuits within the memory device. For example, internal signals require time to propagate to various circuitry in the memory device 16a. Difference in length of the signal routing can cause differences in the times at which signals reach the circuitry. Differences in capacitive loading of signal lines can also cause differences in the times at which signals reach the circuitry. These differences in arrival times can become significant at high speeds of operation and eventually limit the operating speed of memory devices.

As mentioned above, the above-described problems are exacerbated as timing tolerances become more severe with higher data transfer rates. For example, if the internal clock CKINT derived from the external clock CKEXT does not latch the command packet CA0-CA9 at the proper time, errors in the operation of the memory device may result. Similarly, if the data clock DCLK does not latch the data applied to the memory device at the proper time, data errors may result.

Unfortunately, there has heretofore been no suitable 10 means for ensuring that digital signals, such the command packets CA0-CA9 and digital signals, are latched in memory devices, such as the packetized DARM shown in FIG. 2, at the proper time at very high data transfer rates.

Although the foregoing discussion is directed to the need for faster command buffers in packetized DRAMs, similar problems exist in other memory devices, such as asynchronous DRAMs and synchronous DRAMs, which must process control and other signals at a high rate of speed.

#### SUMMARY OF THE INVENTION

Although the inventive system for adaptively adjusting the timing of an internal clock signal may be used in any integrated circuit, it is particularly well adapted for use in a memory device, such as a packetized dynamic random  $^{25}$ access memory device, to control the latching of commands applied to the memory device. The invention may be embodied in a variety of systems that adaptively adjust the phase of an internal clock signal relative to an external clock signal. The systems may operate by repetitively receiving a 30 circuit used in the phase control circuit of FIGS. 7A and 7B. digital signal each of which is latched responsive to respective phases of the internal clock signal. The latched digital signals are then examined to determine if they were correspond to the received digital signals. A phase of the internal clock signal is then selected from within the range of phases  $^{35}$ of the internal clock signal that accurately latched the respective digital signals. The system preferably includes a clock generator circuit that generates the internal clock signal. The internal clock signal has a phase relative to the external clock signal determined by a phase command 40 phase control circuit of FIGS. 7A and 7B. signal. The internal clock signal triggers a latch circuit, such as a shift register. The latch circuit is coupled to one of the input terminals of the integrated circuit so that the latch stores an input signal applied to the input terminal responsive to a transition of the internal clock signal. The timing control system also includes a load control circuit generating a plurality of phase command signals responsive to storing a plurality of respective input signals in the latch. Each of the phase command signals corresponds to different respective phases of the internal clock signal. An evaluation circuit coupled to the latch receives a plurality of latched signals and determines if each of the latched signals was accurately captured by the latch. The evaluation circuit generates a plurality of respective results signals indicative of whether each of the latched signals was accurately captured by the 55 latch. The results signals are then stored in a register that is coupled to the evaluation circuit and the load control circuit. An analysis circuit coupled to the register examines the results signals stored in the register and, based on the examination of the stored results signals, generates and continuously applies to the clock generator circuit the phase command signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a block diagram of a conventional computer 65 system using a plurality of SyncLink packetized memory devices.

FIG. 2 is a block diagram of a conventional packetized DRAM used in the computer system of FIG. 1.

FIG. 3 is a block diagram of a preferred embodiment of a portion of a command buffer and clock generator circuit in accordance with the invention that is usable in the packetized DRAM of FIG. 2.

FIG. 4 is a more detailed block diagram of the portion of the command buffer and clock generator circuit shown in

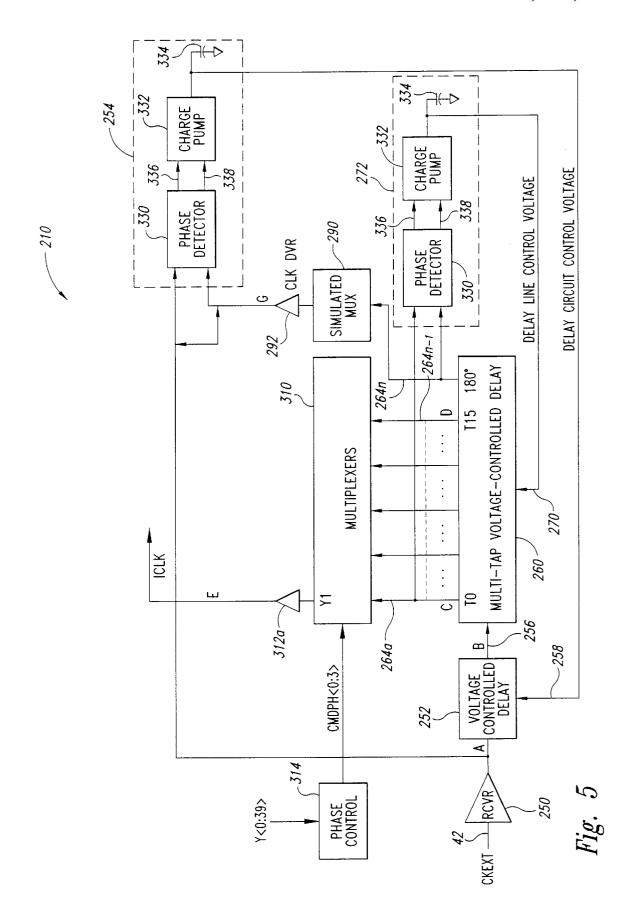

FIG. 5 is a logic diagram and block diagram of the clock control circuit used in the clock generator circuit of FIG. 4.

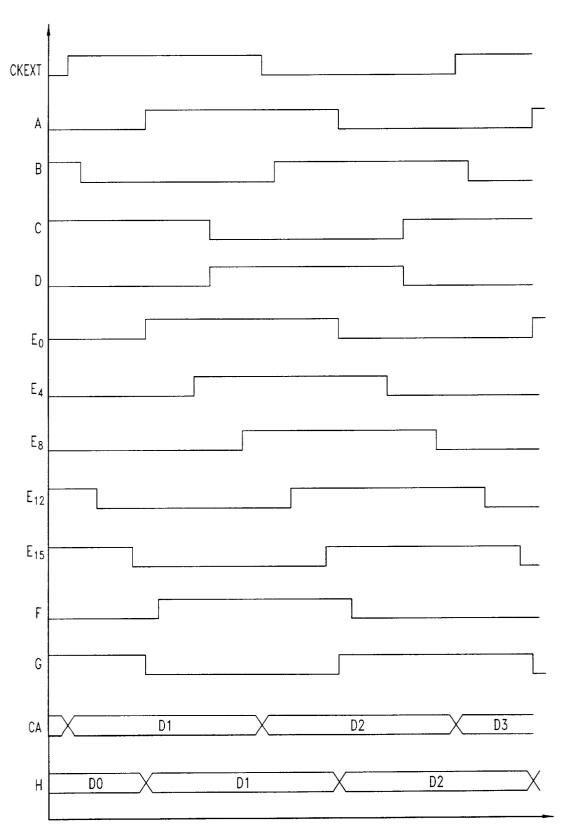

FIG. 6 is a timing diagram showing various signals present in the clock control circuit of FIG. 5.

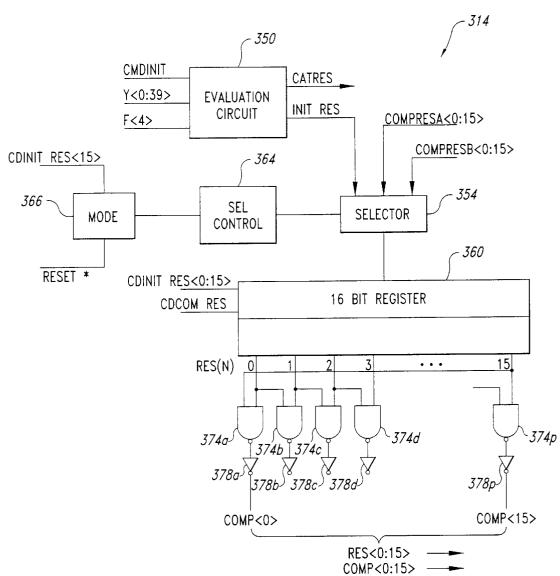

FIGS. 7A and 7B are a block diagram of one embodiment of a phase control circuit used in the clock control circuit of FIG. 5.

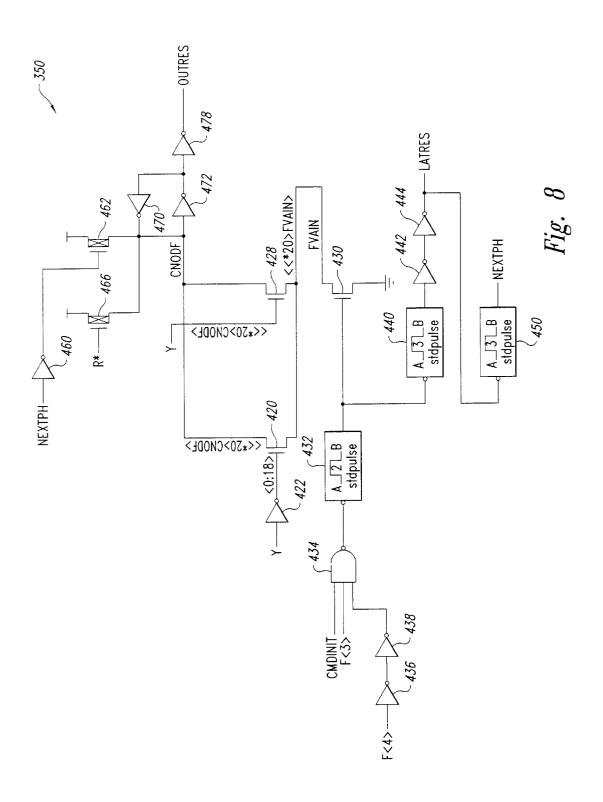

FIG. 8 is a logic diagram and schematic of an evaluation circuit used in the phase control circuit of FIGS. 7A and 7B.

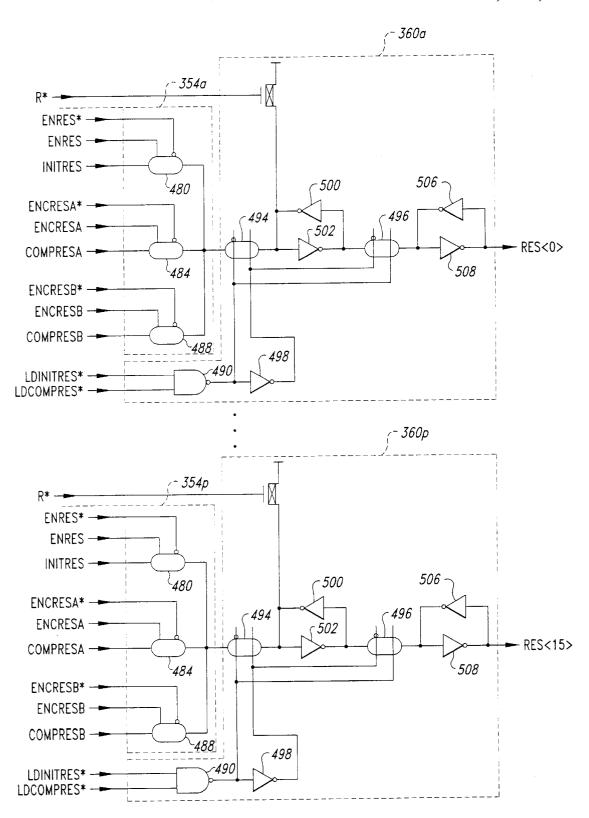

FIG. 9 is a logic diagram and schematic of a register and a signal selector used in the phase control circuit of FIGS. **7A** and **7**B.

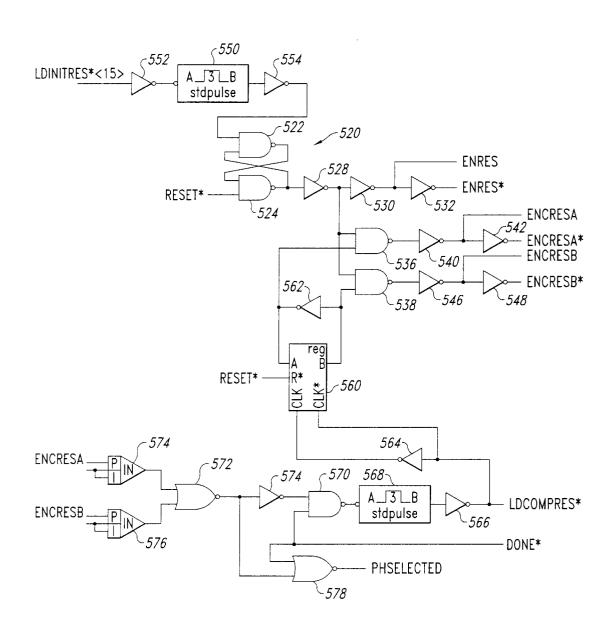

FIG. 10 is a logic diagram of a mode circuit and selector control circuit used in the phase control circuit of FIGS. 7A and 7B.

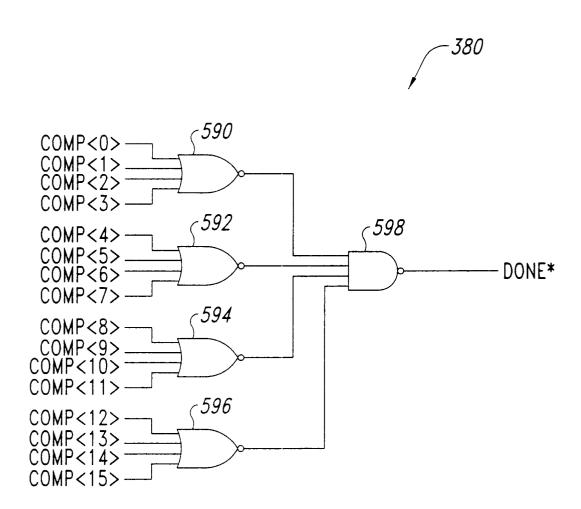

FIG. 11 is a logic diagram of a zero detector circuit used in the phase control circuit of FIGS. 7A and 7B.

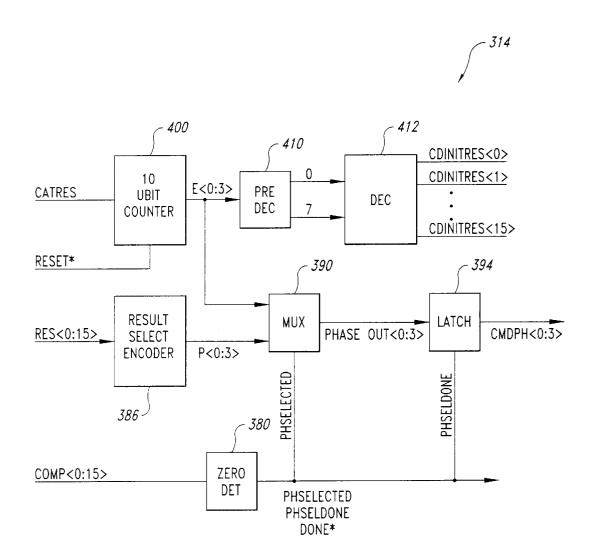

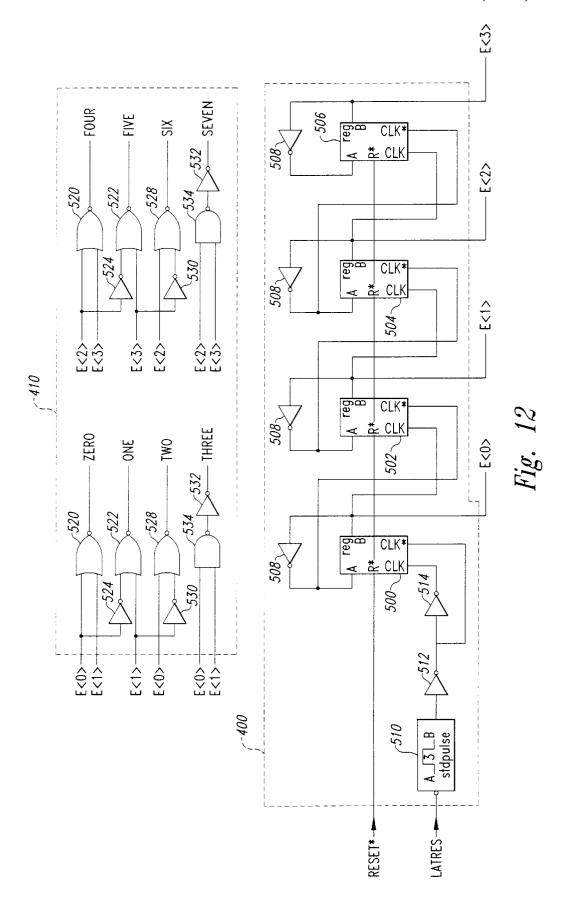

FIG. 12 is a logic diagram of a counter and a predecoder

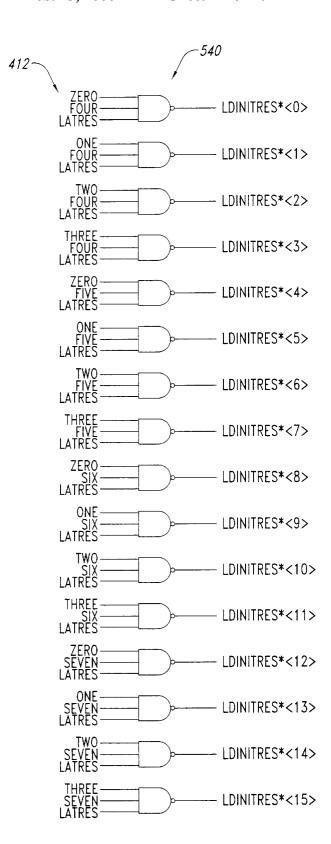

FIG. 13 is a logic diagram of a decoder circuit used in the phase control circuit of FIGS. 7A and 7B.

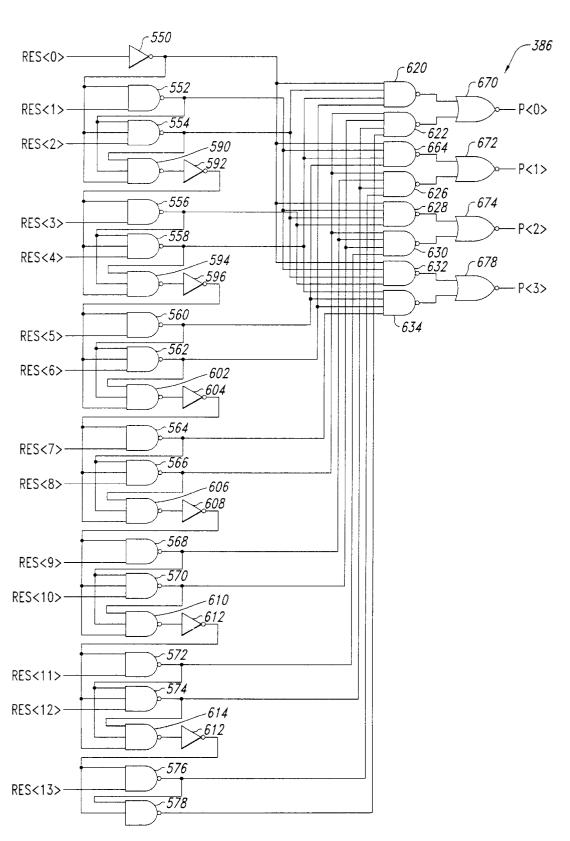

FIG. 14 is a logic diagram and schematic of a results selector encoder used in the phase control circuit of FIGS. 7A and 7B.

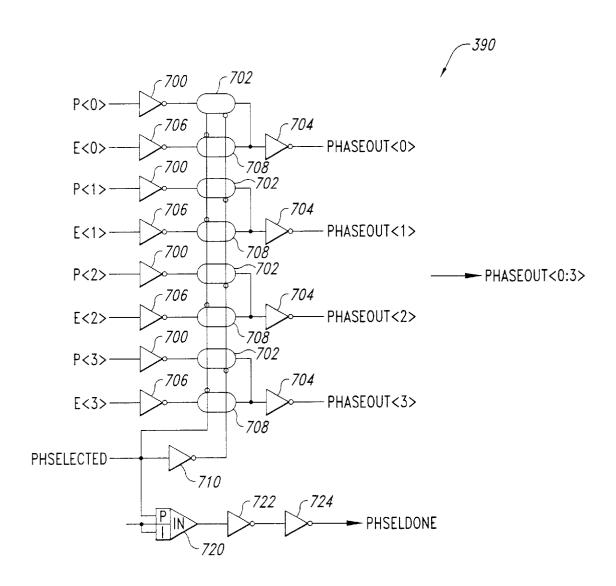

FIG. 15 is a logic diagram of a multiplexer circuit used in the phase control circuit of FIGS. 7A and 7B.

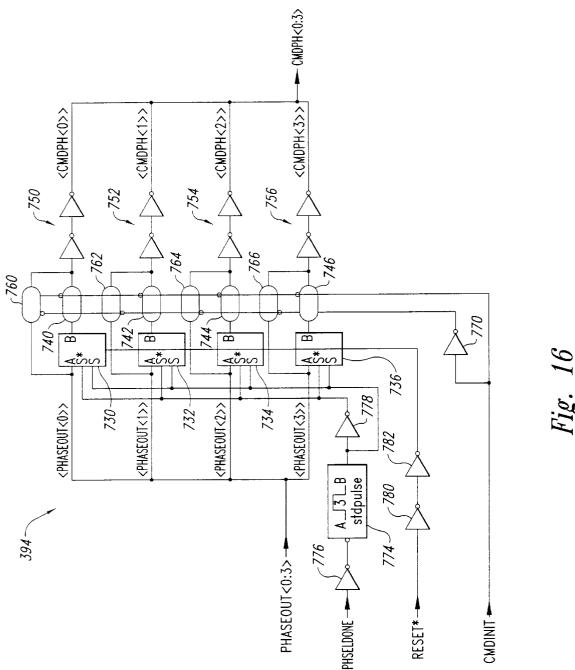

FIG. 16 is a logic diagram of a latch circuit used in the

#### DETAILED DESCRIPTION OF THE INVENTION

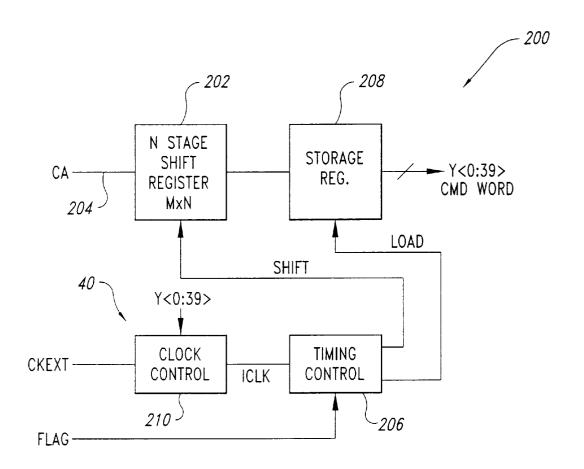

One embodiment of a command buffer and clock control 45 circuit 200 in accordance with the invention is illustrated in FIG. 3. The command buffer and clock control circuit 200 can be used in place of the command buffer 46 and clock generator 40 in FIG. 2, and the resulting memory device may be used in the computer system shown in FIG. 1. With 50 reference to FIG. 3, a command packet CA consisting of a plurality of packet words is applied to a shift register 202 via a command bus 204. The width of the bus 204 corresponds to the size of the shift register 202, and the number of packet words in the command packet corresponds to the number of stages of the shift register 202. In the embodiment shown in FIG. 3, the shift register 202 has four stages, each of which is 10 bits wide. Thus, the shift register 202 sequentially receives four 10-bit packet words CA<0:9>. Each of the four packet words is shifted into the shift register 202, and from one shift register stage to the next, responsive to each of a plurality of SHIFT pulses.

Coincident with the start of a four packet word command packet, a FLAG signal is applied to a timing control circuit 206. The FLAG signal enables the timing control circuit 206 to generate the SHIFT pulses responsive to the internal clock signal ICLK. After four packet words have been shifted into the shift register 202, the control circuit 206 generates a

LOAD signal that is applied to a storage register 208. The storage register 208 is then loaded with all of the data stored in the shift register 202. In the embodiment shown in FIG. 3 in which four 10-bit packet words are shifted into the shift register 202, the storage register 208 receives and stores a 40-bit command word. However, in the more general case, the shift register 202 has N stages, each of which has a width of M bits, and the storage register 208 loads an M\*N bit command word. After the storage register 208 has been loaded, it continuously outputs the M\*N bit command word Y<0:39>.

As explained above, at high operating speeds, it is important that the SHIFT signal be applied to the shift register 202 at the proper time so that it latches signals on the command bus 204 when valid packet words are present on the command bus 204. If, for example, the shift register 202 is clocked by SHIFT pulses during a transition from one packet word to the next, spurious data will be shifted into the shift register 202. It is particularly difficult to ensure that the SHIFT pulses are generated at the proper time because the propagation delay of both the external clock signal CKEXT and the command packet CA is difficult to either predict or control. Furthermore, even if the propagation delay of both the external clock signal CKEXT and the command packet CA could be precisely controlled, it would be difficult to precisely control or predict the propagation delay of these signals within a memory device using the command buffer and clock generator circuit 200.

The command buffer and clock generator circuit 200 illustrated in FIG. 3 is able to precisely control the timing of the SHIFT pulses using a clock control circuit 210 which 30 generates the internal clock signal ICLK from the external clock signal CKEXT. More specifically, the clock control circuit 210 adaptively external clock signal CKEST and generating the internal clock signal ICLK so that the SHIFT pulses are applied to the shift register 202 at the proper time. 35 As explained in greater detail below, during initialization of a memory device using the command buffer and clock generator circuit 200, an initialization packet having a known data pattern is repetitively applied to the shift register 202 along with the external clock signal CKEST and the 40 FLAG signal. After the four packet words of each initialization packet have been shifted into the shift register 202 and stored in the storage register 208, the bits of each packet word are applied to the clock control circuit 210. The clock control circuit 210 then determines if the shift register was 45 successful in capturing the initialization packet. After determining whether each initialization packet was successfully captured by the shift register 202, the clock control circuit alters the delay between receipt of the external clock signal CKEST and generating the internal clock signal ICLK. The 50 clock control circuit 210 then once again determines if the packet words of the initialization packet were successfully captured. After repeating this procedure several times, the clock control circuit determines what delay values between CKEXT and ICLK are successful in capturing the initialization packet. The clock control circuit then uses one of these delay values as the delay between CKEXT and ICLK during normal operation of a memory device using the command buffer and clock generator circuit 200. In this manner, the clock control circuit 210 adapts to whatever external or internal delays exist in the coupling of the command packet CA and the external clock CKEXT, thereby allowing the command buffer and clock generator circuit 200 to operate at optimum speed. A similar system may be used to ensure that the data is latched into the 65 memory device 16a responsive to the data clock DCLK (FIG. 2).

8

It will be understood that necessary portions of the command buffer and clock generator circuit 200 have been omitted from FIG. 3 in the interests of brevity since they are somewhat peripheral to the claimed invention. For example, 5 the command buffer and clock generator circuit 200 will contain circuitry for allowing the command buffer to determine if a command packet is directed to it, circuitry for pipelining command words output from the storage register 208, circuitry for generating lower level command signals 10 from the command word, etc.

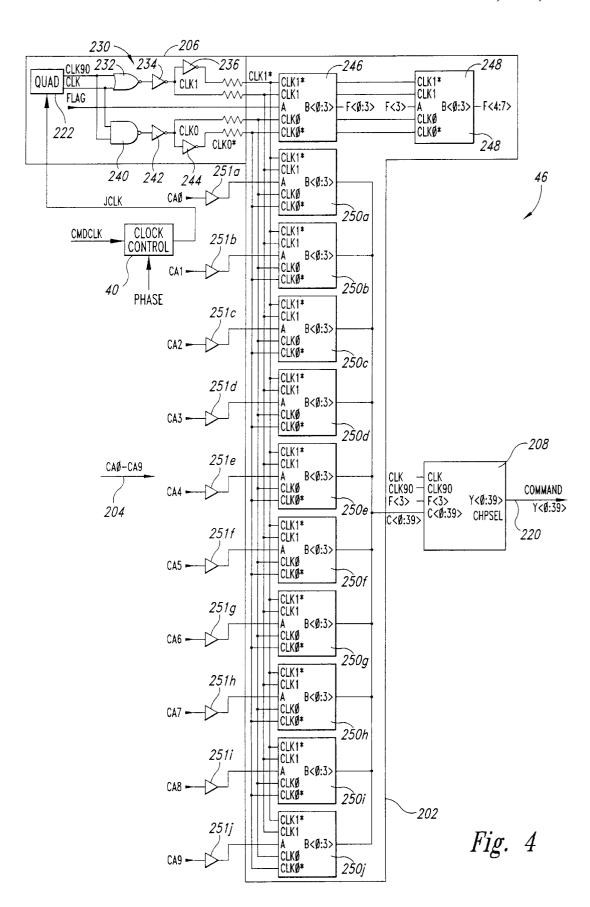

The relevant portions of the command buffer and clock generator circuit 200 are shown in greater detail in the block diagram of FIG. 4. As shown in FIG. 4, the timing control circuit 206 includes a clock circuit 220 that receives a clock signal CLK and its quadrature CLK90 from a conventional quadrature circuit 222 responsive to the internal clock signal ICLK. The internal clock signal ICLK is generated by the clock control circuit 210 from the external clock signal EXCLK, as explained above with reference to FIG. 3. The structure and operation of the clock control circuit 210 will be explained in detail with reference to FIGS. 5 and 6. The CLK and CLK90 signals are applied to a NOR gate 232 which outputs a high whenever ICLK and ICLK90 are both low. The output of the NOR gate 232 is applied through a first inverter 234 to generate a CLK1 signal and then through a second inverter 236 to generate a CLK1\* signal (the " symbol after a signal name is used throughout to designate the compliment of the signal).

The CLK90 and CLK signals are also applied to a NAND gate **240** which outputs a low whenever both CLK and CLK90 are high. The output of the NAND gate **240** is coupled through an inverter **242** to generate a CLK0 signal and then through a second inverter **244** to generate a CLK0\* signal. These CLK0, CLK0\*, CLK1, and CLK1\* signals correspond to the SHIFT pulses described with reference to FIG. **3**.

The clock circuit 220 also includes a pair of shift register circuits 246, 248 that are connected in series with each other to form an 8-stage shift register. The shift register circuit 246 receives the FLAG signal, and the FLAG signal is then sequentially shifted through the four stages of the shift register circuit 246 and the four stages of the shift register circuit 248 responsive to the CLK0, CLK0\*, CLK1, and CLK1\* signals. The FLAG signal is shifted through two stages of the shift register circuits 246, 248 each cycle of the CLK signals. Thus, when FLAG goes high, two successive F<0:7> outputs of the shift register circuits 246, 248 sequentially go high each clock cycle.

The shift register **202** shown in FIG. **4** includes ten separate shift register circuits **250***a*–*j*, each of which receives a respective bit CA**0**–CA**9** of the incoming 10-bit packet word coupled through respective buffers **251***a*–*j*. Each of the shift register circuits **250***a*–*j* includes four shift register stages. Thus, after four clock cycles, four packet word bits CA have been shifted into each shift register circuit **250**, and all four of these bits are available as a 4-bit word B<0:3>. Thus, the ten shift register circuits **250***a*–*j* collectively store and then output a 40-bit command word C<0:39>.

The storage register **208** also receives the CLK and CLK90 signals. However, bits B<0:3> for the four packet words stored in the shift register **202** are not latched into the storage register **208** until the F<3> signal is generated. The clock circuit **220** generates the F<3> signal four transitions of the CLK signal after receipt of the FLAG signal, i.e., after four command packets have been shifted into the shift register **202**. The storage register then stores and continu-

ously outputs the 40-bit command word Y<0:39>. The command word Y<0:39> is then used to control the operation of a memory device containing the command buffer and clock generator circuit 200. As mentioned above, the command word Y<0:39>is also used by the clock control circuit 210 to select the optimum delay between receipt of the external clock signal CKEXT and generating the internal clock signal ICLK.

One embodiment of the clock control circuit 210 in accordance with the present invention, is shown in FIG. 5. As explained above, it is very difficult to clock the shift register 202 (FIGS. 3 and 4) at the proper time at the maximum speed of the command decoder 200. The function of the clock control circuit 210 is to provide an internal clock signal ICLK to the input of the quadrature circuit 222 at the proper time so that the timing control circuit 206 can clock the shift register 202 at even the fastest operating speed of the command decoder 200. However, it will be understood that the clock control circuit 210 may be used for other purposes both in dynamic random access memories and in other circuits. For example, it may be used to generate the data clock signal DCLK to accurately clock data into the memory device 16a, as explained above.

With reference to FIG. 5, the external clock CKEXT is coupled from line 42 through a receiver buffer 250 to a conventional voltage controlled delay circuit 252 and to one input of a phase detector 254. The voltage controlled delay circuit 252 couples the output of the receiver buffer 250 to an output line 256 with a delay that is a function of a control signal applied to the delay circuit 252 on line 258. Although the control signal on line 258 is an analog voltage, it will be understood that other types of control signals, including digital words, may alternatively be used. The output of the voltage controlled delay circuit 252 is applied to a multi-tap voltage controlled delay line 260.

The multi-tap voltage controlled delay line 260 couples 35 the clock signal applied to its input on line 256 to a plurality of output lines 264a-264n. The incoming clock signal is coupled to the output lines 264 with an increasing delay from the first line 264a to the last line 264n. In the embodiment illustrated in FIG. 3, there are 17 output lines 264, but the delay line 260 may have a greater or lesser number of output lines 264. When a delay locked loop that includes the delay line 260 is locked as explained below, the signals at the first output line 264a and the last or 17th output line 264n are other. The signals on the 17 lines are therefore delayed by 11.25 degrees more than the signal coupled to the previous line 264. Thus, the first line 264a has a relative phase of zero degrees, the 16th line 264n-1 has a phase of 168.75 degrees and the last line 264n has a phase of 180 degrees. More specifically, a control voltage applied to the delay line 260 through line 270 is adjusted so that the phase of the signal on the last line 264n relative to the phase on the first line **264***a* is 180 degrees. This is accomplished by applying the first line 264a and the last line 264n to respective inputs of 55 a phase detector 272.

As mentioned above, the delay line 260 and phase detector 272 implement a first delay locked loop. When the first delay locked loop is locked, the signal on line 264n will have a phase relative to the phase of the signal on line **264***a* of 180 degrees. Therefore, as mentioned above, the signal on each of the output lines 264a–26n will sequentially increase from zero degrees to 180 degrees. Although the signals on lines **264***a*–*n* are equally phased apart from each other, it will be understood that equal phasing is not required.

The clock control circuit 210 also includes a second delay locked loop formed by the phase detector 254, the voltage 10

controlled delay circuit 252 and the voltage controlled delay line 260. More particularly, the last output line 264n of the delay line 260 is applied through a simulated multiplexer circuit 290 and a clock driver 292 to one input of the phase detector 254. It will be recalled that the other input of the phase detector 254 receives the output of the receiver buffer **250**. Like the phase detector **272**, when the second delay locked loop is locked, the signals applied to the phase detector 254 are the inverse of each other. Thus, when the second loop is locked, the phase of the signal at the output of the clock driver 292 is 540 degrees (effectively 180 degrees) relative to the phase of the signal at the output of the receiver buffer 250.

The remaining output lines 264a-264n-1 of the delay line 260 are coupled to a multiplexer 310 having an output line coupled to clock driver 312. The multiplexer 310 couples the input of the clock driver 312 to any one of the output lines 264a-264n-1 as determined by respective four-bit phase command word CMDPH<0:3>. The four-bit phase command CMDPH<0:3> is generated by a phase control circuit 314 based on the command word Y<0:39> during an initialization procedure. The structure and operation of the phase control circuit 314 is described in detail in the remaining Figures. The clock driver 312 is used to generate the internal clock signal ICLK which is used to derive the clock signals that are applied to the clock inputs of the shift register 202 (FIGS. 3 and 4).

The phase detectors 254, 272 are each implemented using to a phase detector circuit 330, a charge pump 332 and a capacitor 334. However, other varieties of phase detectors may alternatively be used.

The phase detector circuit 330 applies either an increase signal on line 336 or a decrease signal on line 338 to respective inputs of the charge pump 332. The phase detector circuit 330 generates the increase signal on line 336 whenever the phase of a first signal on one of its inputs relative to a second signal on the other of its inputs is less than 180 degrees. As explained below, the increase signal on line 336 causes the charge pump 332 to adjust the control voltage to increase the delay of the first signal so that the phase of the first signal relative to the phase of the second signal approaches 180 degrees. The phase detector circuit 330 generates the decrease signal on line 338, in the opposite condition, i.e., when the phase of the second signal relative the inverse of each other, ie., phased 180 degrees from each 45 to the first signal is greater than 180 degrees. The decrease signal on line 338 causes the charge pump 332 to adjust the control voltage to reduce the delay of second signal toward 180 degrees.

> Although the phase detector circuit 330 may be implemented in a variety of ways, it may simply use two set-reset flip-flops (not shown) for generating the increase and decrease signals, respectively. The increase flip-flop is set by the rising edge of the first signal on one of the inputs and reset by the falling edge of the second signal on the other input. Thus, the duration that the flip-flop is set, and hence the duration of the increase signal on line 336, corresponds to the period of time that the second signal must be further delayed to have a phase of 180 degrees relative to the phase of the first signal. Similarly, the flip-flop producing the decrease signal on line 338 is set by the falling edge of the second signal and reset by the rising edge of the first signal so that the duration of the decrease signal on line 338 corresponds to the time that the second signal is delayed beyond the time that it would have a phase of 180 degrees 65 relative to the phase of the first signal.

There are also a variety of approaches for implementing the charge pump 332. However, the charge pump 332 can be

implemented by simply applying a constant current to the capacitor 334 for the duration of each increase signal on line 336 and removing a constant current from the capacitor 334 for the duration of each decrease signal on line 338. Appropriate circuitry could also be included in either the phase detector circuit 330 or the charge pump 332 to provide hysteresis in a band when the first and second signals have relative phases of approximately 180 degrees from each other as will be apparent to one skilled in the art.

The operation of the clock control circuit **210** of FIG. **5** in 10 the command decoder of FIG. 4 can best be explained with reference to the timing diagram of FIG. 6. As illustrated in FIG. 6, the external clock signal CKEXT on line 42 is delayed by approximately 70 degrees in passing through the receiver buffer 250 to node A (FIG. 5). Assuming that both of the delay-lock loops are locked, the signal at the output of the receiver buffer 250 is delayed by 120 degrees in passing through the voltage controlled delay circuit 252 to node B. The signal on node B is then coupled to node C with a delay of another 120 degrees and to node D with a delay 20 of 300 degrees so that the signals at nodes C and D are phased 180 degrees apart from each other. Since the signals at nodes C and D are compared to each other by the phase detector 272, the phase detector 272 adjusts the control voltage on line 270 to ensure that the signals at nodes C and D are phased 180 degrees from each other. The other outputs from the delay line 260 have phases relative to the phase of the signal at node C that increase 11.25 degrees for each output in sequence from the first line 264a to the last line 264n.

As mentioned above, one of the first 16 output lines 264a-264n-1 of the delay lines 260 is coupled through the multiplexer 310 and the clock driver 312 to provide the internal clock signal ICLK at node E. In passing through the multiplexer 310 and the clock driver 312a, the selected 35 output from the delay line is delayed by another 120 degrees. Thus, the signal Eo coupled from the first output line of the delay line **260** is delayed by 120 degrees, the signal E4 from the fifth output is delayed by 165 degrees, the signal E8 from the ninth output is delayed by 210 degrees, the signal E12 40 from the 13th output is delayed by 255 degrees, and the signal E15 from the 16th output is delayed by 288.75 degrees. Although the output signals are coupled from the delay line 260 through the multiplexer 310 and clock driver 312a with a delay, that delay is matched by the coupling of 45 the signal from line 264n through the simulated multiplexer 290 and clock driver 292 since the same circuit is used for the simulated multiplexer 290 as the multiplexer 310 and the clock driver 292 is identical to the clock driver 312a. For this reason, and because the phase of the signal on line 264n is 50 180 degrees relative to the phase of the signal on line 264a, the signal at the output of the clock driver 292 at node G has a phase relative to the phase of the signal Eo at the output of the clock 312a of 180 degrees. Since the signals applied to the inputs of the phase detector 254 are the inverse of each 55 other when the delay-locked loop is locked, the signal Eo has substantially the same phase as the signal at the output of the receiver buffer 250. Furthermore, the delay of the voltage controlled delay circuit 252 will be adjusted so that the signal Eo always has the same phase as the command clock coupled to the output of the receiver buffer 250 at A. Assuming the each packet word in the command packet is valid on the rising edge of the external clock CKEXT signal, the packet word coupled to the shift register 202 (FIG. 4) is valid on the rising edge of ICLK since ICLK is properly phased to the signal at node A and the delay through the receiver buffer 250 is substantially the same as the delays

through the buffers 251*a*–*j*. In operation, the multiplexer 310 selects one of the outputs from the delay line 260 as determined by the phase command word CMDPH<0:3> signal so that the optimum clock signal between Eo and E15 (FIG. 6) will be used as the internal clock ICLK.

In summary, the "inner" delay locked loop formed by the phase detector 272 and the voltage controlled delay circuit 260 generates a sequence of signals that have increasing phases from zero to 180 degrees. The "outer" delay locked loop formed by the phase detector 254, the voltage controlled delay circuit 252 and the delay line 260 align one of the clock signals in the sequence to the command clock. As a result, all of the clock signals at the output of the delay line 260 have respective predetermined phases relative to the phase of the command clock at node A.

Although the embodiment of the clock generator 210 illustrated in FIG. 5 uses delay-locked loops, it will be understood that other locked loop circuits, as well as circuits not using a locked loop, may be used in the clock control circuit 210.

Basically, the phase control circuit 314 determines the optimum phase command CMDPH<0:3> after two operating modes have been completed, namely a load mode and an analysis mode. In the load mode, the phase control circuit 314 sequentially increments the phase command CMDPH<0:3> to sequentially couple each tap of the delay line 310 (FIG. 5) to the ICLK driver 312 while the command decoder 200 repetitively receives initialization packets. Thus, the command decoder 200 attempts to accurately capture each initialization packet in the shift register 202 (FIG. 4) responsive to respective internal clock signals ICLK that sequentially vary in their timing relationship to the initialization packets. During the load mode, the phase control circuit 314 determines which initialization packets were successfully captured in the shift register 202. A record is then made identifying which phase commands CMDPH<0:3> (ie. which taps of the delay line 260) caused ICLK to clock the shift register 202 at the proper time to successfully capture these initialization packets.

In the analysis mode, the phase command in the command record are evaluated. More specifically, a single phase command CMDPH<0:3> that is most likely to be able to successfully capture packet words in a command packet is selected from the phase commands that successfully captured an initialization packet. This selected phase command CMDPH<0:3> is the command that is used to generate the ICLK signal during normal operation. A block diagram of the phase control circuit 314 for generating the phase command CMDPH<0:3> is illustrated in FIGS. 7A and 7B.

With reference to FIG. 7A, an evaluation circuit 350 receives an initialization word Y<0:39>, an F<4> signal, and an initialization command CMDINIT. The F<4> signal is generated by the shift register (FIG. 4) in the clock circuit 220 one-half clock period after four initialization packet words, ie., the entire initialization packet, have been latched into the shift register 202 and transferred to the storage register 208. The initialization word Y<0:39> is generated at the output of the storage register 208 and corresponds to the 4 packet words in each initialization packet. The initialization command CMDINIT is generated by other circuitry (not shown) in the command decoder 200 during the initialization procedure.

In operation, when the initialization command CMDINIT is active high, the evaluation circuit **350** analyzes the initialization word Y<0:39> to determine if the initialization packet has been accurately captured by the shift register **202**

(FIG. 4). If the captured initialization word Y<0:39> matches the initialization packet, the evaluation circuit 350 outputs an active high initialization result signal INITRES. The evaluation circuit also outputs a latch result signal LATRES responsive to each F<4> pulse as long as CMDINIT is high, regardless of the state of the initialization result signal INITRES. As mentioned above, in the load mode of the initialization procedure, the evaluation circuit **350** evaluates 16 initialization packets that are applied to the command decoder 200 at 16 respective time relationships to the internal clock signal ICLK. Thus, in the load mode, the evaluation circuit outputs 16 LATRES pulses and between 0 and 16 INITRES signals depending on the number of initialization packets successfully captured by the shift register 202.

Where multiple memory devices using the phase control circuit 314 are in a computer system, e.g., the computer system of FIG. 1, the evaluation circuit 350 may include means (not shown) for preventing more than one phase control circuit 314 from responding to the same initialization  $_{20}$ packets. For example, one memory device could be selected to be the first memory device to be initialized. After being initialized, the first memory device and all subsequent memory devices would enable initialization of the next memory device. Alternatively, the clock control circuits 210 of all of the memory devices in the computer system could be initialized at the same time responsive to the same 16 initialization packets.

With further reference to FIG. 7A, the initialization result INITRES from each of 16 evaluations is applied to a selector 30 circuit 354 along with two compressed result words, COM-PRESA<0:15> and COMPRESB<0:15>. The selector circuit 354 couples one of these three signals to a 16-bit register 360 responsive to signals from a selector control circuit 364. The selector control circuit 354 is, in turn, controlled by a 35 mode circuit 366. The mode circuit receives an active low RESET\* signal to place the phase control circuit 314 in the load mode, and an active high LDINITRES<15> (load initial response) signal to transition the phase control circuit 314 to the analysis mode.

In the load mode, the mode circuit 366 controls the selector control circuit 364 so that it causes the selector circuit 354 to couple the INITRES signal from the evaluation circuit 350 to the 16-bit register 360. Also, during the stored is controlled by a respective LDNITRES<0:15> signal. Thus, for example, when the INITRES signal (which indicates whether the initialization packet was successfully captured) obtained for a first phase of ICLK corresponding to the first tap of the delay line **260** is applied to the register 360, a LDINITRES<0> signal causes the INITRES signal to be stored in the first bit location of the register 360. Similarly, the INITRES signal obtained for a second phase of ICLK corresponding to the second tap of the delay line 260 is stored in the second bit location of the register 360 responsive to a LDINITRES<1> signal, etc. Finally, the INITRES signal obtained for the 16th phase of ICLK corresponding to the last tap of the delay line 260 is stored in the last bit location of the register 360 responsive to a LDINITRES<15> signal. At this time, the register **360** stores 16 bits of information indicative of which of the 16 phases of the ICLK signal corresponding to the 16 taps of the delay line 260 were successful in capturing the 16 initialization packets coupled to the command decoder 200 in the load mode. The stored information is output from the register **360** 65 as RES<0:15>. As mentioned above, the LDINITRES<15> signal then switches the mode circuit 366 to the analysis

mode since all of the information indicative of the capture of the initialization packets has then been loaded into the register 360.

By way of example, the register 360 may output "0000110011111000" as RES<0:15> after the completion of the load mode. The logic "1" values of RES<3-7, 10, and 11> thus indicates that the ICLK signal coupled from the 4th-8th, 11th, and 12th taps of the delay line 260 were successful in capturing initialization packets.

When the LDINITRES<15> signal switches the mode circuit 366 to the analysis mode, the mode circuit 366 controls the selector control circuit 364 so that it causes the selector circuit 354 to alternately apply COMPRESA<0:15> and COMPRESB<0:15> to the 16-bit register 360. The 16 outputs of the register 360 are coupled to 16 NAND gates 374a-p which are, in turn coupled to respective inverters 378a-p so that the NAND gates 374 and inverters 378together perform AND functions. The inputs of each NAND gate 374 receive a respective bit of the register 360 and an adjacent bit of the register 360, except for the first NAND gate 374a, which receives the output from bit 16 of the register 360. The outputs of the inverters are designated as  $\overrightarrow{COMP} < 0.15$ , where  $\overrightarrow{COMP} < N > = RES(N) * \overrightarrow{RES}(N-1)$ (except for COMP<0> which is equal to RES<15>\*RES<0>). The COMP<N> signals are fed back to a respective input of the register 360. However, the outputs of the inverters 378 are fed back differently for the COM-PRESA<0:15> signals and the COMPRESB<0:15> signals. For COMPRESA<0:15>, each COMPRESA<N>is equal to COMP<N>\*COMP<N-1>. For COMPRESB<0:15>, each COMPRESB<N> is equal to COMP<N>\*COMP<N+1>. Further, in the analysis mode, the register 360 is controlled by the LDCOMPRES signal so that the 16 bits fed back to the register 360 are loaded into the register 360 in parallel.

The operation of the selector circuit 354, register 360, NAND gates 374 and inverters 378 in the analysis mode is best understood using the above example of "0000110011111000" for the initial RES<0:15>. After these values for RES<0:15> are coupled through the NAND gates and inverters 378, COMP<0:15> is "0000010001111000". It can be seen by comparing RES<0:15> to COMP<0:15> that COMP<0:15> is the same as RES<0:15> except that every "1" that is to the right of a "0" has been converted to a "0". Thus, when the COMP<0:15> signals are fed back to the register 360 as load mode, the bit location at which the INITRES signal is 45 COMPRESA<0:15>, the each "1" that is positioned to the right of a "0" is changed to a "0". As a result, the new values of RES<0:15> are the previous values for COMPRESA<0:15>, i.e., "0000010001111000". After these values for RES<0:15> are coupled through the NAND gates 374 and inverters 378, COMP<0:15> becomes "000000000111000". However, since COMPRESB<N>= COMP<N>\*COMP<N+1>, COMP<0:15> is coupled back to the register 360 as "000000001110000". Thus, when the COMP<0:15> signals are fed back to the register 360 as COMPRESB<0:15>, each "1" that is positioned to the left of a "0" is changed to a "0". After RES<0:15> is coupled back to the register once more as COMPRESA<0:15>, the new RES<0:15> is "000000000110000", i.e., the "1" to the right of a "0" is changed to a "0". Finally, when this last RES<0:15> is coupled back to the register once more as COMPRESB<0:15>, the new RES<0:15> is "000000000100000", i.e., the "1" to the left of a "0" is changed to a "0". When this final RES<0:15> is coupled through the NAND gates 374 and the inverters 378, the new COMP<0:15> is "00000000000000000".

> With reference to FIG. 7B, a COMP<0:15> of all "0"s is detected by a zero detector circuit 380, which then generates

a phase selected signal PHSELECTED, a phase selected done signal PHSELDONE, and a DONE signal, each of which signifies that the optimum phase of the internal clock signal ICLK has been determined. At this time, a result select encoder 386 determines from the final RES<0:15> of "000000000100000" that the 6th bit of the register, i.e., RES<5> is the location in the register 360 that contains a "1". The result select encoder 386 then outputs a corresponding binary value P<0:3> of "0101". The result select encoder 386 also arbitrates between a result in which two or 10 more "1"s are in the final RES<0:15>. For example, an initial RES<0:15> of "0111001110011100" would produce a final RES<0:15> of "0010000100001000" thereby providing an indication that three phases of ICLK are equally likely of capturing a command packet. The result select encoder 386 selects the lowest order "1" as the final result so that a final RES<0:15> of "0010000100001000" would be interpreted as "000000000001000".

As mentioned above, when the final RES<0:15> is obtained, the zero detector circuit 380 outputs 20 PHSELECTED, PHSELDONE, and DONE signals. The PHSELECTED signal causes a multiplexer to couple the P<0:3> word from the result select encoder 386 to a PHASEOUT<0:3> word that is stored in a latch 394 responsive to the PHSELDONE signal. The latch 394 then outputs the P<0:3> word corresponding to the final RES<0:15> as the phase command CMDPH<0:3>. As explained above, the phase command CMDPH<0:3> is used by the multiplexer 310 (FIG. 5) to select one of the taps of the delay line 260 to generate the internal clock signal ICLK. In the example 30 given above where P<0:3> is "0101", the multiplexer 310 would select the sixth tap of the delay line 260 to generate

The multiplexer 390 and latch 394 are also used in the each of the taps of the delay line 260. Since PHSELECTED load initial results signals LDINITRES<0:15>. As explained above, the LDINITRES<0:15> signals are used by the register 360 to determine the bit of the register 360 in which an INITRES signal from the evaluation circuit 350 is stored. Thus, the counter output E<0:3> is initially "0000" to cause the LDINITERS<0> signal to be "1" and the LDINI-TRES<1:15> signals to be "0", thereby causing the evaluation result INITRES from receipt of the first initialization packet to be stored as bit zero in the register 360. As the same time, the counter output E<0:3> of "0000" is coupled through the multiplexer 390 and the latch 394 so that the phase command CMDPH<0:3> is "0000". The "0000" value of CMDPH<0:3> causes the multiplexer 310 to select the first tap of the delay line 260 to generate ICLK. After the counter 400 has been incremented to 15, i.e., "1111", CMDPH<0:3> also becomes "1111" thereby causing the multiplexer 310 to select the last tap of the delay line 260 to generate ICLK. At the same time the "1111" value of E<0:3> causes the decoder 412 to output an active high LDINI-TRES<15> to cause the INITRES from the evaluation circuit to be stored in bit 15 of the register 360. As mentioned above, the active high LDINITRES<15> also causes the mode circuit 366 (FIG. 7A) to transition to the analyze mode, since the initial results obtained in the load mode have now been loaded into the register. The phase control circuit 314 shown in FIGS. 7A and 7B thus adapts itself to use the ICLK phase that is most likely to be successful in capturing a command packet in normal operation.

The circuitry used in the block diagram of FIGS. 7A and 7B is shown in greater detail in FIGS. 8–16. With reference to FIG. 8, the evaluation circuit 350 is specifically adapted to detect a predetermined initialization packet. In the embodiment of FIG. 8, the initialization packet that the load mode to cause the multiplexer 310 to sequentially select 35 evaluation circuit 350 is adapted to detect is shown in Table 1, below.

TABLE 1

|     | Flag | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 | CA7 | CA8 | C <b>A</b> 9 |

|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------|

| PW1 | 1    | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0            |

| PW2 | 1    | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1            |

| PW3 | 0    | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0            |

| PW4 | 0    | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1            |

is inactive low prior to the end of the analyze mode, the multiplexer 390 couples the E<0:3> word from a 4-bit counter 400 to the input of the Latch 394. The inactive low PHSELDONE signal generated prior to the end of the  $^{50}$ analyzer mode causes the latch 394 to couple PHASEOUT <0:3> (corresponding to E<0:3>) through the latch 394 as CMDPH<0:3>. The CMDPH<0:3> word determines which tap of the delay line 260 is selected to generate ICLK.

The 4-bit counter 404 is enabled by an active low 55 RESET\* signal which, as explained above, occurs in the load mode. The counter 400 is incremented by each LATRES pulse which, as explained above, is generated by the evaluation circuit 350 (FIG. 7A) each time an initialization packet is received. Thus, as each initialization packet is received in the load mode, the counter 400 is incremented by one. The count of the counter 400 is coupled through the multiplexer 390 to the latch 394. The CMDPH<0:3> signals at the output of the latch 394 then sequentially selects each The count of the counter 400, i.e., E<0:3> is also applied to a predecoder 410 and decoder 412 to generate corresponding

The initialization packet thus consists of four packet words, PW1-PW4, arranged in a checkerboard pattern, with the first two packet words, PW1 and PW2, having a flag bit. The initialization packet shown in Table 1, if successfully captured by the shift register 202 (FIG. 4), produces an initialization word Y<0:39> in which the initialization bits alternate between 0 and "1" from Y<0> to Y<39>. The initialization bits that should be a logic "1" are applied to the gate of a respective first NMOS transistor 420 through a respective inverter 422. Although only one NMOS transistor 420 and one inverter 422 is shown in FIG. 8, there are actually 20, i.e., one for each initialization bit that should be "1". The NMOS transistors 420 for all of the initialization bits are connected between CNODE and EVAL. Similarly, The initialization bits that should be a logic "0" are applied directly to the gate of a respective second NMOS transistor 428. Once again, although only one NMOS transistor 428 is shown in FIG. 8, there are actually 20, i.e., one for each tap of the delay line 260 as the counter 400 is incremented. 65 initialization bit that should be "0". The NMOS transistors 428 for all of the initialization bits are also connected between CNODE and EVAL.

After each initialization word Y<0:39> has been captured. the EVAL node is pulled to ground by turning ON an NMOS transistor 430. The transistor 430 is turned ON by a pulse from a pulse generator 432 which is, in turn, triggered by a falling edge from a NAND gate 434. As mentioned above with reference to FIG. 7A, the CMDINT signal is active high during initialization, thereby enabling the NAND gate 434. However, the NAND gate 434 initially outputs a high because the F<3> signal from the clock circuit 220 (FIG. 4) and F<4> coupled through a pair of inverters 436, 438 are 10 initially low. Further, since there is generally a FLAG signal sent with only the first packet word of a command packet, F<3> and F<4> are generally never high at the same time. However, as shown in Table 1, a FLAG signal is sent with the first two initialization words of each initialization packet. 15 Thus, for initialization packets, F<3> and F<4>, even after being delayed through the inverters 436, 438, are both high for a short time after the initialization word has been stored in the storage register 208 (FIG. 4). At this time, the output of the NAND gate 434 goes low, thereby triggering the pulse 20 generator 432 to turn ON the transistor 430 and pull the EVAL node low.