R. Jacob Baker Department of Electrical and Computer Engineering Boise State University 1910 University Dr., ET 201 Boise, ID 83725 jbaker@boisestate.edu

Abstract – Memory technology development, in particular dynamic random access memory (DRAM), has been the greatest driving force in the advancement of solid-state technology for integrated circuit development over the last 40 years. The origin of DRAM circuits and technology can be traced to Dr. Dennard's Patent (Number 3,387,286) granted on June 4, 1968. This truly visionary work, using a single transistor and capacitor (the 1T1C), is one of the most manufactured devices in the history of mankind. This talk will review the impact of his invention and discuss the brilliance of Dr. Dennard for conceiving the invention of the 1T1C cell prior to the maturity of metal oxide semiconductor (MOS) technology and in the face of critics that may have likely asked "why in the world would we want a memory, DRAM, that forgets its' contents!?"

Let's Step Back in Time

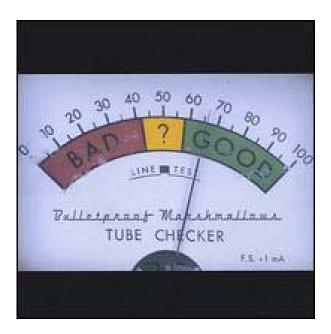

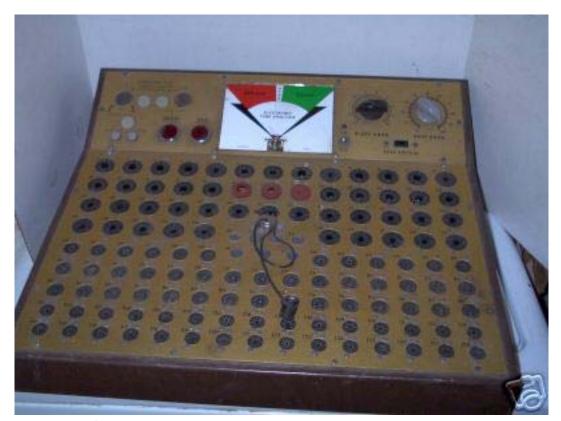

□ What are the following (hint: they were found in your local supermarket in the 50s, 60s, and early 70s)

Photos taken from ebay.com

# BOISE Semiconductor-based Electronics were still new during this period of time

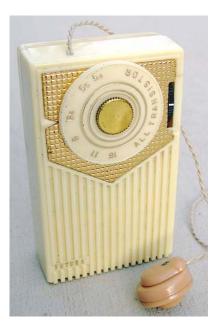

- Does anyone remember the birth of the transistor radio?

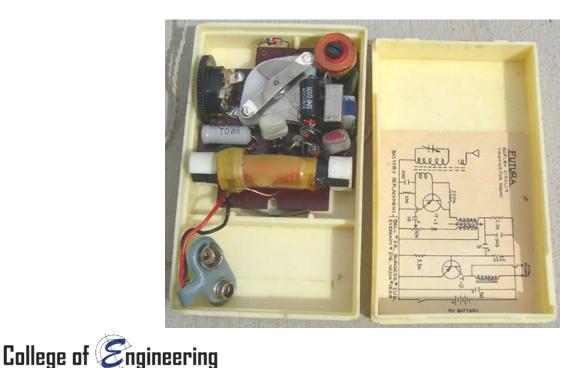

- Below is seen the 2-transistor Furtura transistor radio (ca. 1955)

- $\checkmark$  Note the output is via an earphone

- ✓ Also note the schematic (not many, if any, consumer electronics products today come with a schematic)

Photos taken from ebay.com

Baker

These were a big deal both because they were portable (something not practically possible with vacuum tube radios) and because they used a new technology (solid-state devices that didn't wear out)

Baker

Growing Complexity

□ Note the use of bipolar junction technology to replace vacuum tubes

Photo taken from ebay.com

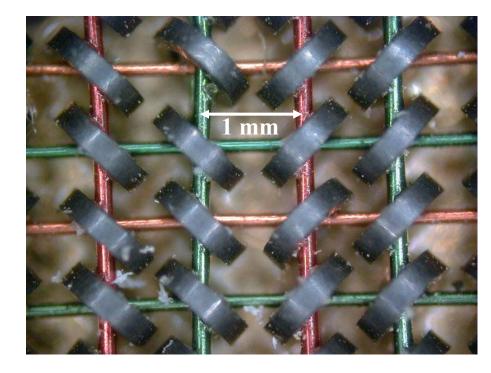

- Dominated by the magnetic core memory seen below

- During the 1960s solid-state memory was developed based on the BJT

- ✓ Ultimately wasn't successful (compared to MOS-based memory)

Image from wikipedia.org

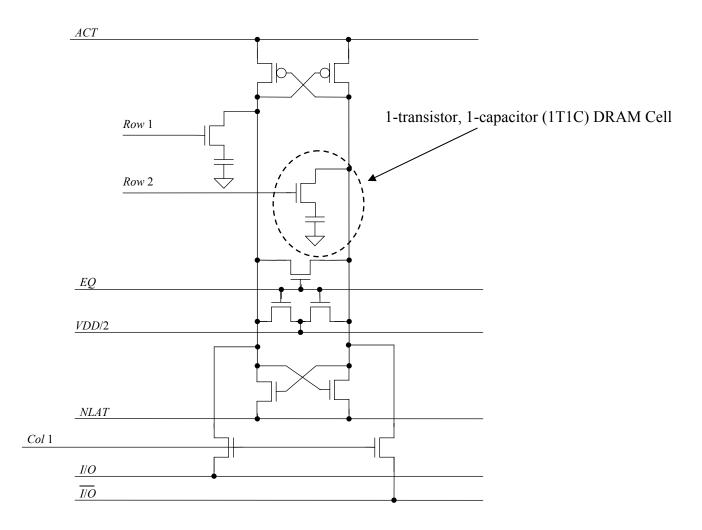

- During the excitement of bipolar technology replacing vacuum tubes in most electronic devices he filed an invention disclosure on July 14, 1967 that

- ✓ Used metal-oxide-semiconductor (MOS) technology

- ✓ Proposed a memory, the one-transistor, one-capacitor (1T1C cell), that forgets its contents!

- □ Why is using MOS technology such a big deal over bipolar?

- ✓ MOS technology is scalable!

- $\checkmark$  Another significant contribution from Dr. Dennard's is scaling theory.

- □ Why is a memory that forgets its contents such a big deal?

- ✓ It's small!

- ✓ It's fast!

#### Predicted that MOS devices would continue to shrink in size (scale) over time

- ✓ Higher density

- ✓ Faster

- ✓ Low power

- □ Also discussed how interconnect would scale

- ✓ RC times of the lines don't scale but as distances shrink delays drop

- Dennard, R.H.; Gaensslen, F.H.; Rideout, V.L.; Bassous, E., and LeBlanc, A.R., "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE Journal of Solid-State Circuits*, Volume 9, Issue 5, Oct 1974, pp. 256 - 268

#### □ Scaling from Dennard's paper

- ✓ Device and Circuit Scaling

- ✓ Interconnect Scaling

- ✓ Scale parameter is about 1.4 ( $1/\kappa = 0.7$ )

| Device or Circuit Parameter  | Scaling Factor |

|------------------------------|----------------|

| Device dimension tax, L, W   | $1/\kappa$     |

| Doping concentration Na      | κ              |

| Voltage V                    | 1/ĸ            |

| Current I                    | 1/ĸ            |

| Capacitance £4/t             | 1/ĸ            |

| Delay time/circuit VC/I      | $1/\kappa$     |

| Power dissipation/circuit VI | $1/\kappa^2$   |

| Power density VI/A           | 1              |

| Parameter                           | caling Factor |  |  |  |

|-------------------------------------|---------------|--|--|--|

| Line resistance, $R_L = \rho L/W t$ | ĸ             |  |  |  |

| Normalized voltage drop IRt/V       | ĸ             |  |  |  |

| Line response time $R_L C$          | 1             |  |  |  |

| Line current density I/A            | ĸ             |  |  |  |

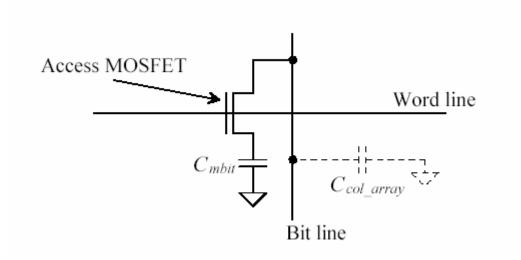

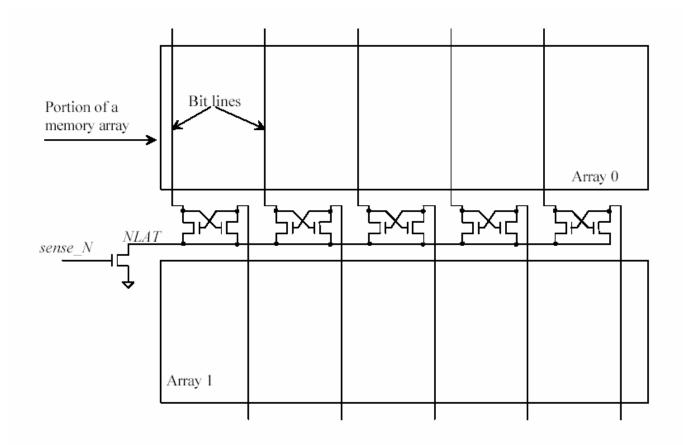

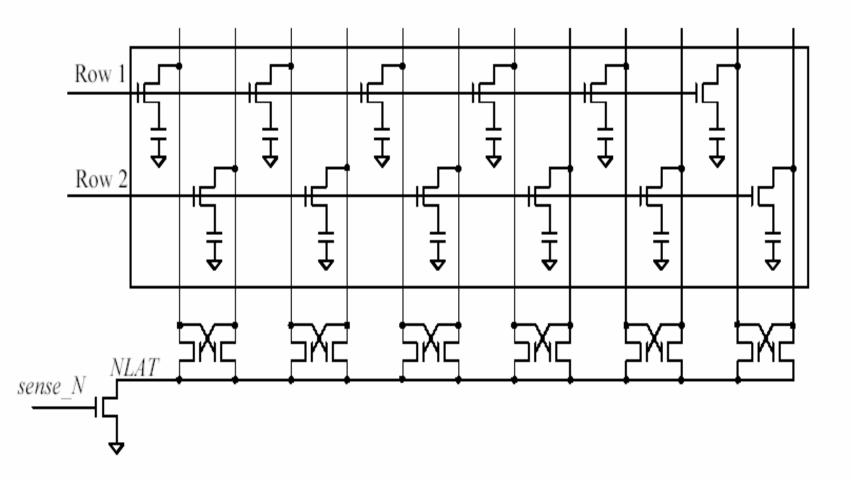

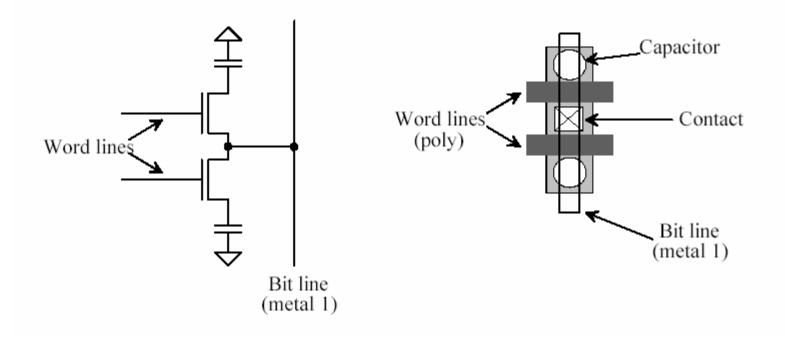

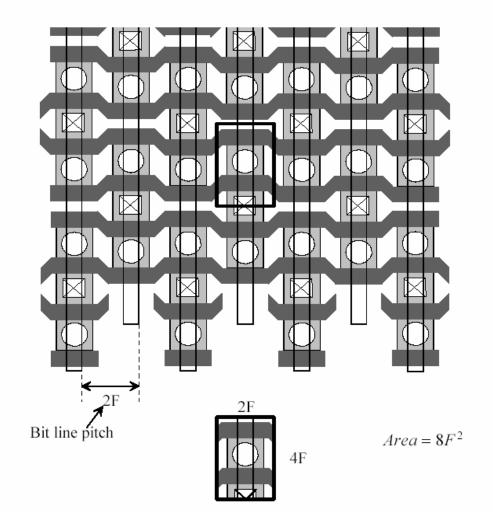

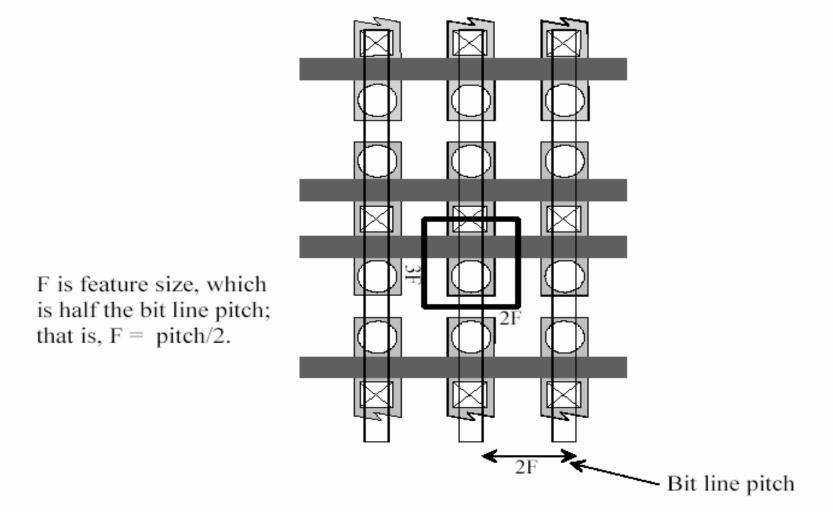

□ The array is formed with word (row) and column (bit) lines

# Folded and Open Arrays

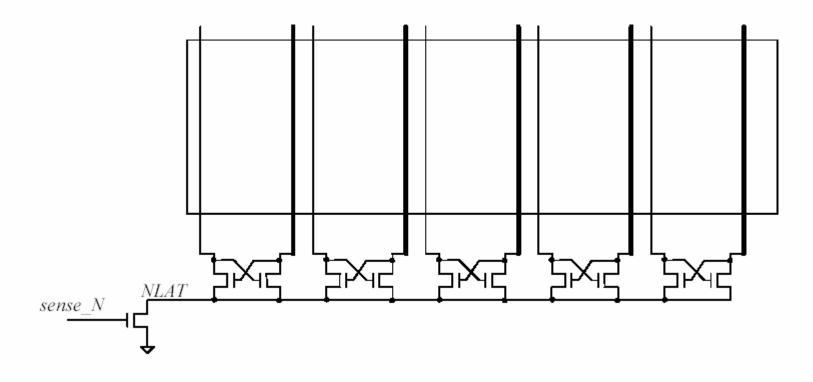

□ The open array

Folded and Open Arrays

□ The folded array

The Folded Array

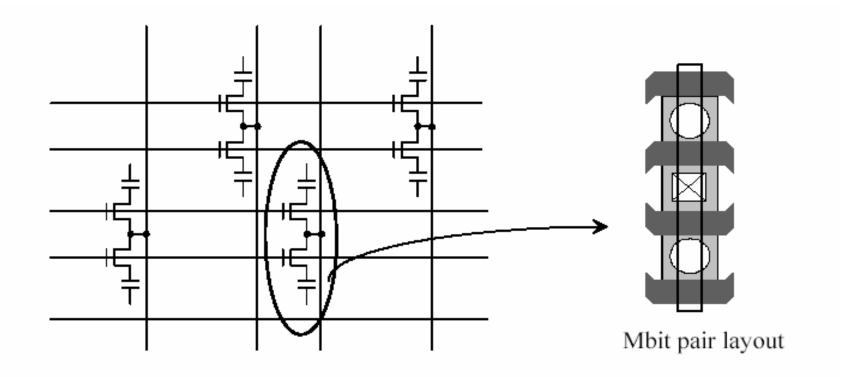

# Further Reduction in Cell Size

#### □ Sharing the bitline contact

Mbit Pair: Folded Array

Folded Array Cell Size

Open Array: 6F<sup>2</sup>

#### Array Block

| RD | 256k |

|----|------|----|------|----|------|----|------|----|------|----|------|----|------|----|------|

|    | SA   |

| RD | 256k |

|    | SA   |

| RD | 256k |

|    | SA   |

| RD | 256k |

|    | SA   |

| RD | 256k |

|    | SA   |

| RD | 256k |

|    | SA   |

| RD | 256k |

|    | SA   |

| RD | 256k |

|    | SA   |

Row decoder and driver circuitry

Sense amplifier and column decoder circuitry.

# The 1T1C DRAM Cell

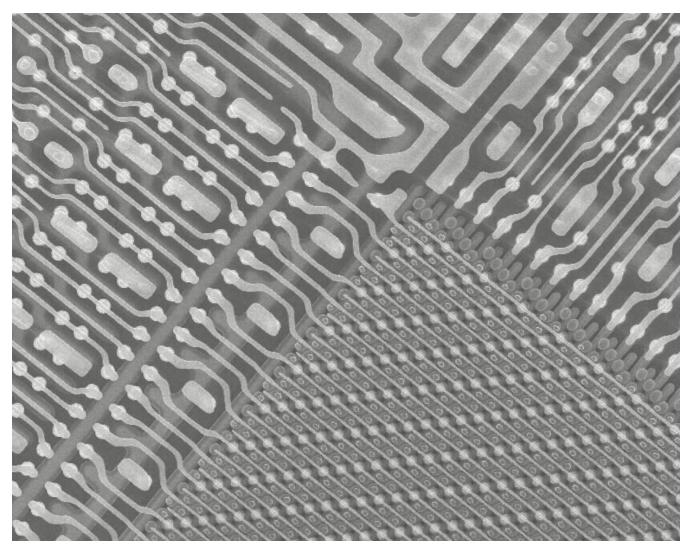

### SEM Photo of a Modern DRAM Array

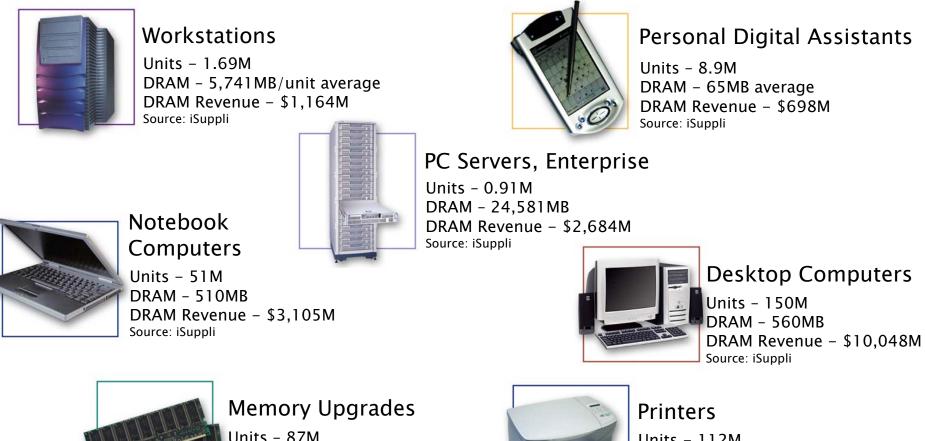

# How is DRAM used today?

Units – 87M DRAM – 295MB DRAM Revenue – \$3,060M Source: iSuppli

Units – 112M DRAM – 35MB DRAM Revenue – \$156M Source: iSuppli

# Communications and Networking Market

DSL Modems Units - 55M DRAM - 8MB Flash -2MB

Cellular Base Stations

Units - 0.35M DRAM - 256MB Flash - 5112MB

LAN Switches Units – 113.5M DRAM – 15MB

Low-End to Mid-Range Routers Units - 1.5M DRAM - 406MB

Sources: iSuppli, Gartner, Portelligent, Instat

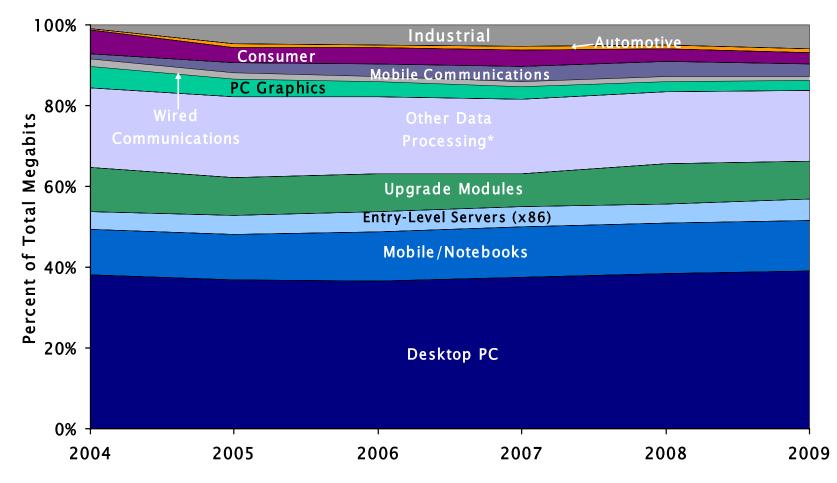

DRAM Demand by End-Use Application

\*Other Data Processing includes mainframe servers, enterprise servers, workstations, handheld PCs, storage cards, printers, and internet appliances

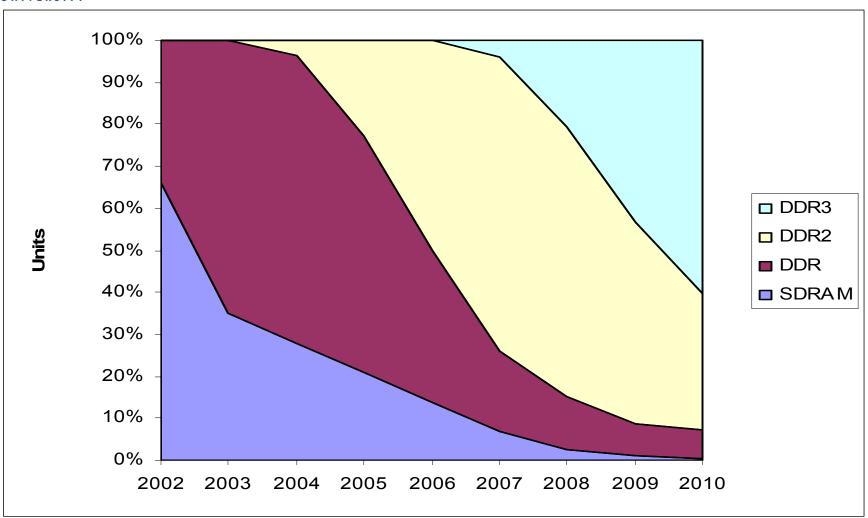

BOISE Worldwide DRAM Shipments by Type 100% SIZMB DDR 1Gb DDR2 90% 1Gb DDR3 Percent of Total Megabytes Produced 80% 70% 128Mb 512 Mb DDR2 RDRAM 60% 512Mb 256Mb DDR DDR3 50% 256Mb SD 40% 128Mb DDR 30% 64Mb DDR 128Mb SDR 20% 64Mb EDO 64Mb SDRAM 10%

I 0%

I 6Mb SDRAM

0%

I 6Mb SDRAM

0%

I 6Mb SDRAM

2002

2003

2002

2003

2004

2005

2006

2007

2008

2009

#### **DRAM** Technology Trends

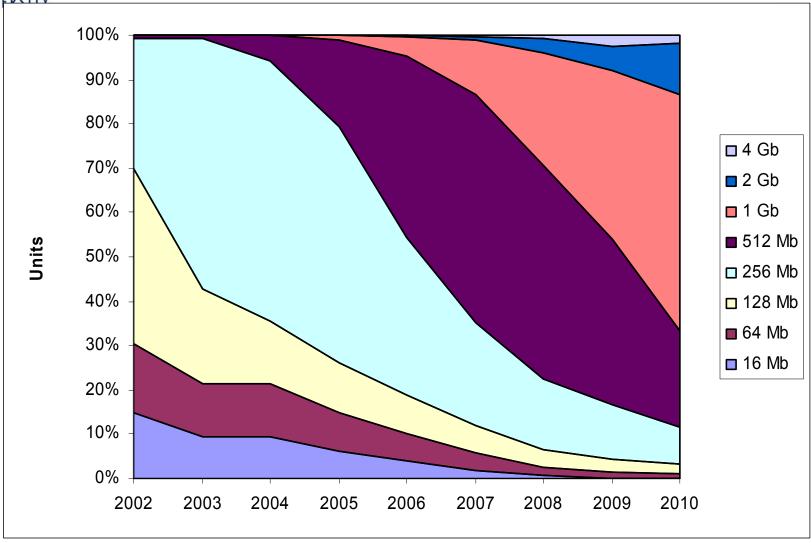

#### **DRAM Density Trends**

Source: IDC, Isuppli, Gartner, IC Insights Q106

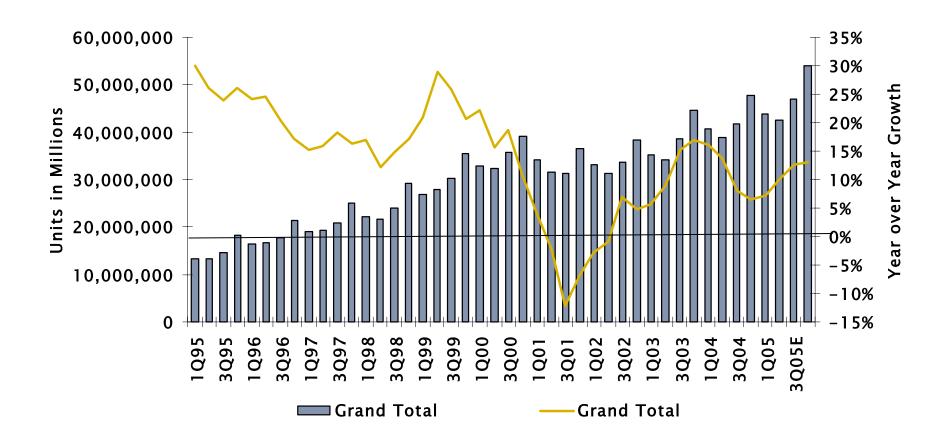

#### Historical PC Market Growth

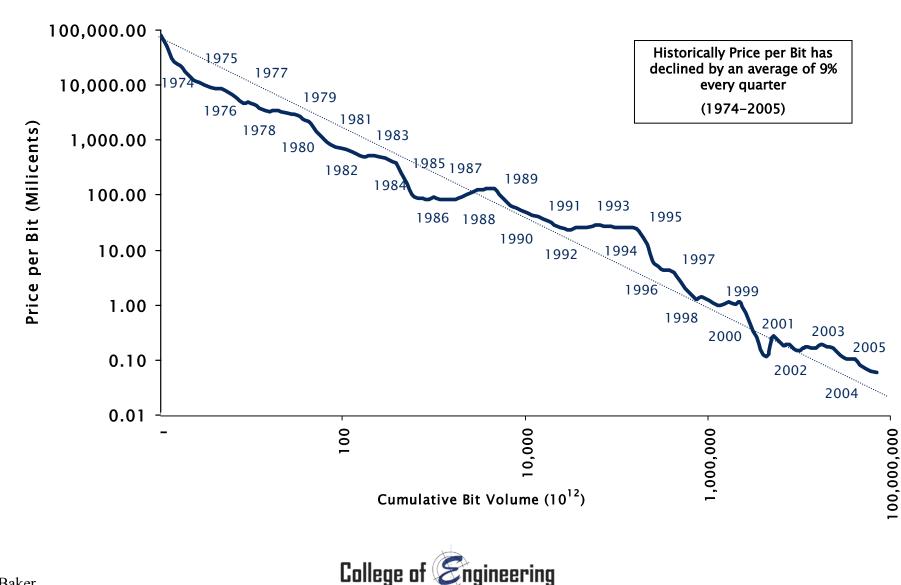

# Price per Bit Cycles

Baker

UN

VFRSI

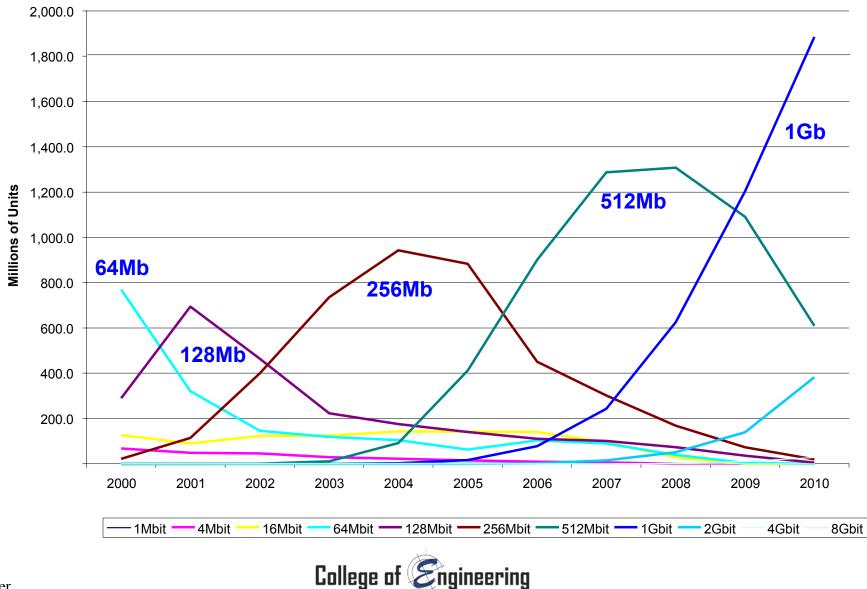

# Americas DRAM Unit Shipments by Density

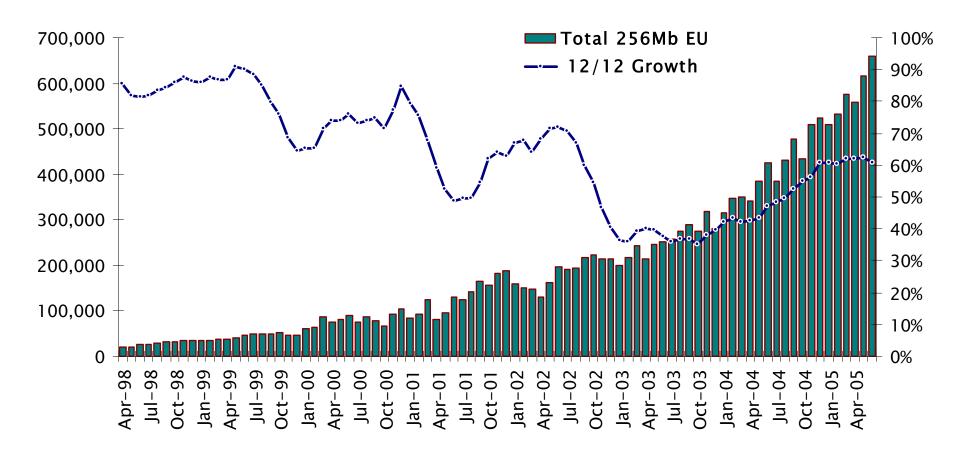

# 256Mb Equivalent Unit DRAM Shipments

256Mb Equivalent Units Shipped

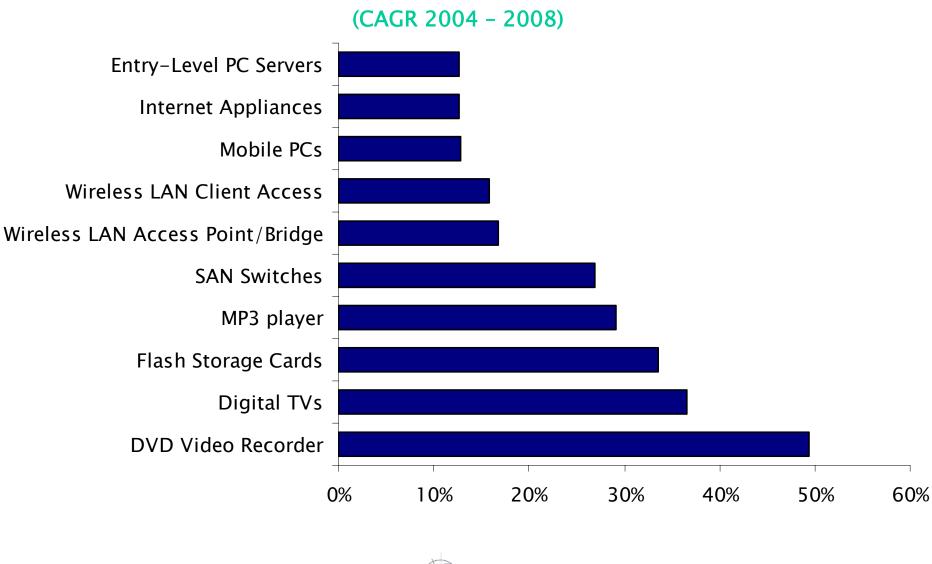

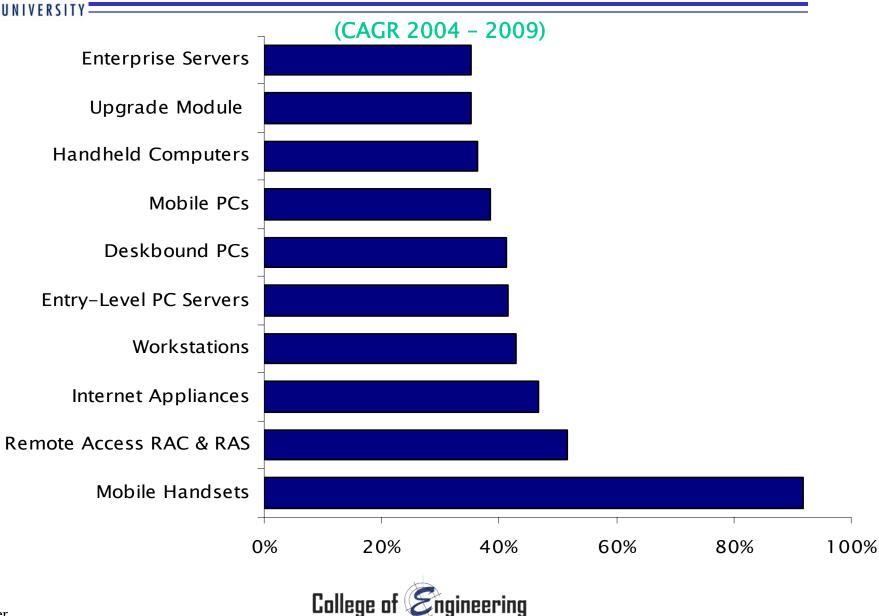

#### DRAM Applications with the Highest Unit Growth Rates

College of Engineering

□ DRAM chips are found in virtually every computer in use today. Looking at the simplicity of the 1T1C cell one might wonder about the significance of this invention by modern day standards. However, if it is remembered that this idea was conceived back in the 1960s before MOS technology had matured enough for production or the idea that circuits could be "dynamic" (only operating correctly for a short period of time) the significance of the invention becomes clear. What is usually not mentioned when talking about Dr. Dennard's contributions to the 1T1C memory cell is his contributions of seeing this idea to product (the true test for any practical electrical engineer). The MOS process development (and the concerns for defects and reliability which have a drastic effect on the dynamic operation of MOS circuits) and supporting circuitry are also extremely important contributions that Dr. Dennard made while at IBM. In summary, Dr. Dennard cut the path for modern DRAM memory chip developments.