# A Compact Delay-Locked Loop for Multi-Phase Non-Overlapping Clock Generation

## Chris Gagliano and R. Jacob Baker

Department of Electrical and Computer Engineering Boise State University Boise, ID, U.S.A.

#### Introduction

Delay-locked loops (DLLs) have become ubiquitous in digital circuits. For example, for the last ten years DLLs have been included on all double-data rate (DDR) dynamic access memories (DRAMs), Fig. 1 [1]. These all-digital designs are robust but lack the tuning range of an analog-controlled DLL [2]. This paper presents an analog-controlled DLL that compact, low power, and tolerant to power supply noise. The DLL is used with clock generation circuitry to generate 32 phases of clock signals for use in multi-phase switched capacitor circuits.

#### A. Benefits of a DLL

Delay-locked loops (DLLs) are a lower jitter alternative to phase-locked loops (PLLs) when there is a reference clock available at the desired frequency [3]. A PLL uses a variable oscillator that is, generally, voltage-controlled to generate the output clock signal. A DLL uses a variable delay line that is controlled to phase shift the output signal to achieve phase-lock with the reference clock. A PLL integrates the phase difference of its input data and its oscillator to control the oscillator frequency, which results in a second-order feedback loop. A DLL, on the other hand, integrates the phase difference between the reference clock and its delay line output to control the phase of its output, which results in a first-order feedback loop. A first-order feedback loop is easier to stabilize and ultimately results in better jitter performance for a DLL when compared to a PLL.

The main challenges faced when designing a DLL include the locking range (set by the maximum and minimum delays of the delay line), the resolution of the delay line (for a digital delay this is at least a gate delay), and making the DLL's output immune to power supply noise. While there are trade-offs with any design the one presented here uses an analog-controlled delay line that results in good delay range and resolution. The major concern, when using an analog delay, is the sensitivity to power supply noise.

## DLL and Clock Generator Building Blocks

The DLL consists of a phase detector, charge pump, loop filter, and a variable delay line. Figure 2 shows a block diagram of the DLL. In this case, the input clock is both the input data  $(\Phi_{la})$  and the reference clock  $(\Phi_{clock})$  since the DLL is used for clock generation rather than to align output data with the reference clock (another common use for DLLs). The output of the DLL ( $\Phi_{out}$ ) is used as the input to a non-overlapping clock generation circuit as shown in

The schematic and layout of the phase detector (PD) circuit is shown in Figures 4 and 5. The transistors are sized with small widths to reduce power consumption and layout size. This PD design is robust and well-used [3]. Notice, in the layout seen in Fig. 5, the abundant use of both well and substrate contacts to reduce the effects of substrate noise.

Figure 4. Phase detector schematic

#### B. Charge Pump and Loop Filter

The schematic and layout of the charge pump is shown in Figures 6 and 7. The loop filter consists of five parallel NMOS capacitors on the charge pump output. Because current sources are used in this design, noise on either the power supply or ground, ideally, doesn't affect the operation of the circuit. Noise on VDD, for example, couples directly to the gates of the PMOS devices keeping their source-gate voltages constant. Similarly, noise on ground couples directly to the gates of the NMOS devices resulting in constant gate-source voltages. Noise on ground, however, does couple directly into the charge pump's output. As we'll see this control voltage is used to bias an NMOS device in the delay element. It's also desirable, in this delay element, to keep the gate-source voltages of the NMOS devices used in the delay element constant, so the coupling between the control voltage and ground is desirable (and why we use an NMOS device and not a PMOS device)

As just mentioned the loop filter capacitor voltage (out) is the control signal input to the voltage-controlled delay line. The charge pump charges or discharges the loop filter capacitor depending on the output signals from the PD. When the input clock (clock) and delayed clock (DLLout) inputs to the PD are in phase, the Inc and Dec outputs of the PD will both be low and the loop filter capacitor will neither be charged nor discharged by the charge pump

The cascode PMOS and NMOS devices on the charge pump output help to isolate the loop filter from power supply noise. They also supply large output impendence for a large RC time constant when the Inc and Dec inputs are both low and the loop filter capacitor voltage is decaying.

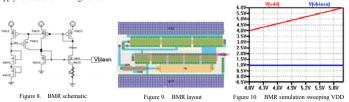

#### C. Beta-Multiplier Reference

The charge pump circuit bias voltage (Vbiasn) is generated by a beta-multiplier reference (BMR), Figs. 8 and 9. The BMR is self-biased and thus has an ideally flat response as VDD varies, thus reducing the susceptibility to power supply noise as shown in Figure 10.

D. Voltage-Controlled Delay Line

The voltage-controlled delay line (VCDL) consists of eight delay stages in series and a bias circuit (for the delay stages). The concise schematic of the VCDL and bias generator is shown in Figure 11. The full VCDL circuit layout is seen in Fig. 12. Again note the use of an abundant number of well and substrate contacts on the top and bottom of the

Each delay stage consists of a current-starved inverter followed by two additional inverters to clean up the signal and ensure fast edge transitions. The schematic of a VCDL delay stage is shown in Figure 14. Notice the decoupling capacitor (the NMOS device on the right) in the schematic. It's important that the variation across the delay element be slowed, using decoupling capacitors, so that the loop response can compensate for variations in VDD. If this is the case then simpler, low-power circuits, can be used without a hit to VDD sensitivity.

The bias current in the current-starved inverter stage, and thus the delay of the stage, is set by the bias voltages vbp and vbn, Fig. 13. These bias voltages are ultimately controlled by the input to the VCDL (Vindel), which is connected to the loop filter capacitor voltage (out).

D. Non-overlapping Clock Generator

The DLL output is the input to the non-overlapping clock generation circuit. The schematic of the non-overlapping clock generator is shown in Figure 3 and the layout is shown in Figure 15. The circuit generates two non-overlapping clock signal outputs (labeled p1 and p2 in the layout) and their complements (labeled p1i and p2i in the layout).

Figure 15. Non-overlapping clock generation circuit layout

## Summary

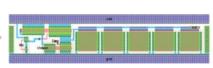

The layout of the full DLL and clock generator circuit is shown in Figure 16. There are eight delay stages, with the output of each delay stage being fed to a non-overlapping clock generator circuit. Therefore, there are 32 clock signals generated by the circuit. The full circuit takes up an area of 810 µm x 95 µm in the 0.5 µm CMOS process.

Figure 17 shows the simulation results with a 100 MHz input clock. The first stage outputs (p1/0) and p2/0) and the last stage outputs (p1[7] and p2[7]) are shown. Each stage has two non-overlapping clock outputs and their complements. The complement signals are not shown.

Table 1 provides a summary of the DLLs simulation results. With 400 mV peak-to-peak noise added to the VDD supply, the jitter on the DLL output is 250 ps at 100 MHz.

Figure 16. DLL and clock generator circuit

Non-overlapping clock generation simulation

| Process             | 0.5 μm CMOS                |

|---------------------|----------------------------|

| VDD                 | 5 V                        |

| Operating Frequency | 20 Mhz - 100 Mhz           |

| Layout Area         | 810 μm x 95 μm             |

| Peak-to-Peak jitter | 250 ps @ 100 Mhz           |

| Power dissipation   | 17.5 mW (includes buffers) |

Table 1 Summary of results

#### References

- Lin, F., Miller J., Schoenfeld A., Ma, M. and Baker, R.J., "A Register-Controlled Symmetrical DLL for Double-Data-Rate DRAM," IEEE Journal of Solid State Circuits, Vol. 34, No. 4, pp. 565-568

- Lin, F., Research and Design of Low Jitter, Wide Locking-Range Phase-Locked and Delay-Locked Loops, Electrical Engineering Doctoral Dissertation, University of Idaho, 2000.

- R. Jacob Baker, CMOS Circuit Design, Layout and Simulation, Revised 2<sup>nd</sup> ed., Wiley-IEEE, 2008.