# DESIGN NOTE A microchannel plate image-intensifier gating circuit capable of pulse widths from 30 ns to 10 $\mu$ s

## S T Ward<sup>†</sup>, R J Baker<sup>†</sup> and H W Li<sup>‡</sup>

† Department of Electrical Engineering, University of Idaho, Boise Engineering, 1910 University Drive, ET201, Boise, Idaho 83725, USA

‡ Department of Electrical Engineering, University of Idaho, Moscow, Idaho 83844, USA

Received 17 July 1995, accepted for publication 25 August 1995

**Abstract.** A pulse generator is described for driving gated microchannel plate image intensifiers. The circuitry is power MOSFET-based and capable of producing -400 V pulses into a capacitive load. The pulse widths are adjustable from 30 ns up to 10  $\mu$ s with fall times of 10 ns and rise times of 15 ns, when driving a 10 pF load.

#### 1. Introduction

Gated microchannel plate detectors require high-voltage, nanosecond pulses to achieve high-speed operation. Traditionally, these driving circuits have been designed using various types of vacuum tubes or avalanche bipolar transistors [1–3]. This design note describes an alternative circuit using power MOSFETs. Power MOSFETs are more reliable than avalanche transistors and require less power and space than vacuum tubes.

This particular circuit was designed to drive the microchannel plate of an electronically gateable proximityfocused image intensifier in dynamically gated mode [4]. A positive voltage with respect to the earthed anode, greater than 100 V, is applied to the photocathode of the microchannel plate image intensifier (MCPII) in the gated off mode. A pulsed negative voltage, near -200 V, is applied to the photocathode and used to gate the MCPII [4]. In order to achieve the proper gating time, the pulse width is adjustable from 30 ns to 10  $\mu$ s (for focusing). The amplitude of the gating pulse is adjustable from 0 to 400 V.

#### 2. An overview of the electronic circuitry

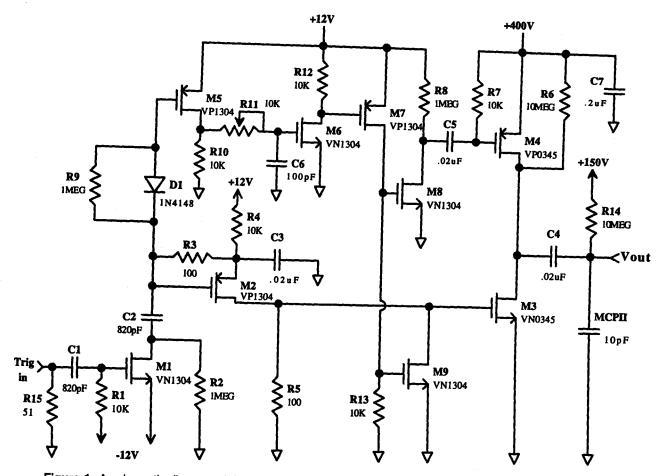

The complete circuit is shown schematically in figure 1. The design is centred around MOSFETs M3 and M4. In non-triggered operation, M3 and M4 are off and their drain voltages are at 400 V. With the MCPII initially charged to 150 V, it is off and C4 is charged to 250 V. When triggered, M3 turns on and its drain voltage is pulled down to about 0 V. Because the voltage across C4 cannot change instantaneously, the MCPII's voltage is pulled down to about -250 V, turning it on. When M3 turns off, its large off resistance and the large resistor, R6, hold the drain voltage near 0 V.

When M4 turns on, its drain voltage is pulled back up to 400 V, turning off the MCPII. The large-bias resistors, R6 and R14, and the short pulse widths enable the voltage across C4 to remain nearly constant at 250 V. The remaining circuitry provides proper timing and variable pulse width generation.

All MOSFETs are manufactured by Supertex [5] and were selected for their low input capacitance, on-resistance, and drain-source leakage currents. MOSFETs M3 and M4 require higher breakdown voltages than the other MOSFETs, thus different devices were used.

When triggering occurs, the gate voltage of M1, through the capacitor, C1, rises above its threshold voltage and turns on. The drain voltage of M1 is pulled down to -12 V, causing the gate of M2 to be pulled down to 0 V and forward biasing the diode, D1. The gate voltage on M5 is pulled down to about 5 V. Consequently, M2 and M5 are turned on. MOSFET M5 activates the timing circuitry and M2 allows the capacitor, C3, to dump charge into the gate of M3. M3 is quickly turned on and pulls the MCPII's voltage down to -250 V.

The resistor, R3, holds M2 on for about 10 ns. After M2 turns off, the gate voltage of M3 begins to discharge through R5. When the MOSFET, M9, turns on, it draws the remaining charge off the gate of M3. When the voltage on

Figure 1. A schematic diagram of the circuit, with de-coupling capacitors for some supplies not shown.

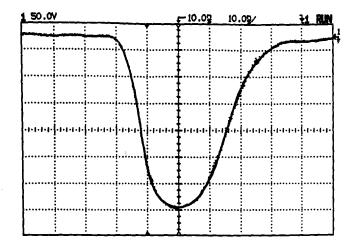

Figure 2. A 30 ns pulse of magnitude 325 V.

the gate is less than M3's threshold voltage, M3 is turned off.

When the timing circuitry is activated. M5 is on and the gate voltage of M6 begins to charge up through the variable resistor, R11, the capacitor C6, and the gate capacitance of M6. Varying the resistance of R11 adjusts the output pulse width by changing the charging RC time constant. To achieve larger pulse widths, up to 10  $\mu$ s, a 15 nF capacitor may be added in parallel with C6. When M6 charges above

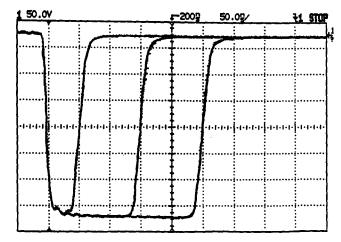

Figure 3. 50, 150 and 250 ns pulses of magnitude 350 V.

its threshold voltage, it turns on, turning on M7. Turning on M7 also turns on both M8 and M9. The drain of M8 is pulled down to earth, pulling the gate of M4, through the capacitor C5, down to 0 V. M4 turns on its drain voltage is pulled back up to 400 V, shutting off the MCPII.

The repetition rate of the circuit is limited to about 100 Hz, due to the resistor, R9, in parallel with the diode. The resistor and the diode ensure that M5 will be on long enough to turn on M6. To ensure proper circuit operation, de-coupling capacitors are mandatory, especially C7, the capacitor on the 400 V supply.

#### 3. Experimental results

In testing the circuit, the 150 V supply was earthed and the results were referenced from earth. To ensure that the entire waveform was visible on the oscilloscope, pulse magnitudes were kept under 400 V. A 30 ns negative pulse with a magnitude near 325 V is shown in figure 2. The waveform has a 10 ns fall time and a 15 ns rise time. Three negative pulses, of varying widths, are shown in figure 3. The pulse widths are in the range 50–250 ns, with each having fall times of 10 ns and rise times of 15 ns.

### 4. Conclusions

A high-voltage, nanosecond driving circuit was designed for a microchannel plate image intensifier. The circuit was capable of 30 ns pulses and adjustable up to 10  $\mu$ s. The circuitry was designed using power MOSFETs and passive devices.

#### References

- King N S P 1981 Overview of pulsers for nanosecond gating of image shutter tubes *Proc. SPIE* 288 425–33

- [2] Yates G J, Ogle J W and King N S P 1982 Overview of pulsers for nanosecond gating of image shutter tubes *Proc. SPIE* 348 434-7

- [3] Yates G J, King N S P, Jaramillo S A, Noel B W and Gobby P L 1984 Nanosecond image shuttering studies at Los Alamos National Laboratory *IEEE Trans. Nucl. Sci.* 31 484-9

- [4] ITT Electro-Optical Products Division 1984 Technical Design Note E23

- [5] Supertex, Inc 1992 Databook for Integrated Circuits and DMOS Transistors (1225 Bordeaux Drive, Sunnyvale, California 94088-3607, USA)