# Stacking power MOSFETs for use in high speed instrumentation

R. J. Baker and B. P. Johnson

Department of Electrical Engineering, College of Engineering, University of Nevada, Reno, Reno, Nevada 89557-0030

(Received 29 June 1992; accepted for publication 3 August 1992)

A reliable circuit configuration is described for stacking power metal-oxide semiconductor field effect transistors (MOSFETs). The resulting circuit has a hold off voltage N times larger than a single power MOSFET, where N is the number of power MOSFETs used. The capability to switch higher voltages and thus greater amounts of power, into a 50  $\Omega$  load, in approximately the same time as a single device is realized. Design considerations are presented for selecting a power MOSFET. Using the design method presented, a 1.4 kV pulse generator, into 50  $\Omega$ , with a 2 ns rise time and negligible jitter is designed.

## I. INTRODUCTION

Power metal-oxide semiconductor field effect transistors (MOSFETs) have the potential to solve many problems in high speed, nanosecond and subnanosecond, instrumentation design.<sup>1-4</sup> The intrinsic speed of the commercial devices is limited mainly by packaging (lead inductances) and the combination of the drain, source and gate resistances, and the device junction capacitances. These factors limit device switching speed to approximately 500 ps depending to a large extent on packaging, device type, and circuit configuration.

To date, the main limitation of power MOSFETs in the design of instrumentation has been their hold off voltage (the maximum voltage which can safely be applied between the drain and source). This has resulted in examining power MOSFETs in stacks to acquire the cumulative voltage ratings required. Stacking power MOSFETs has been reported<sup>1-3</sup> for use in high speed instrumentation. These reported methods rely on driving each MOSFET individually whereas the method reported herein drives only the bottom MOSFET in the stack. Circuit part count is lower and board layout is simpler.

Currently 1 kV devices are available from several manufacturers with peak pulsed current ratings in the range of 20 A. If a 50  $\Omega$  load must be driven with greater than 1 kV, a lower voltage MOSFET with a higher peak current capability must be used in a stack configuration. This limitation in hold off voltage has forced applications requiring high voltage signals varying in the nanosecond region (such as sweep circuits for streak cameras<sup>5,6</sup> and gating of pockels cells<sup>7</sup> and microchannel plate image intensifers) to rely on avalanche transistor strings.<sup>8</sup>

To further understand the desirability of using power MOSFETs, consider the design of a streak camera ramp circuit. This circuit must provide a constant current to the streak tube deflection capacitance (typically 10 pF) over a range of 1.5 kV. A constant current charging a capacitance produces a linearly increasing voltage or in other words a ramp. Varying the current, and thus the ramp or sweep rate, is easily done with power MOSFETs by varying the gate-source voltage. On the other hand varying the ramp rate using Avalanche transistors requires major circuit modifications or else tolerating a highly nonlinear sweep. This is because the MOSFET can operate as a linear device while the avalanche transistor is inherently a nonlinear device.

#### **II. STACKING POWER MOSFETs**

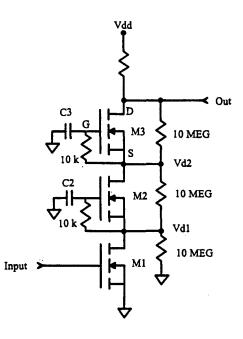

Figure 1 shows a reliable method of stacking power MOSFETs. The resistor values are not critical and are used to set the dc operating voltages. The main cause of failure when stacking power MOSFETs is exceeding the maximum gate-source voltage specification of typically  $\pm 20$  V resulting in a puncturing of the SiO<sub>2</sub> interface. The circuit shown in Fig. 1 relies on a voltage division between the effective gate source capacitances of M2 and M3 with C2 and C3 to stay below 20 V. A properly designed circuit will force all of the MOSFETs to turn on at the same rate.

When M1 turns ON the voltage change on its drain divides across the effective gate source capacitance of M2,  $C'_{gs2}$ , and the capacitor C2. The change in voltage between the gate and source of M2,  $\Delta V_{gs2}$ , is given by

$$\Delta V_{gs2} = \Delta V_{d1} \cdot \frac{C2}{C2 + C'_{gs2}},$$

(1)

where  $C'_{gs2}$  is given by

$$C'_{gs2} \cong C_{gs2} + A_{V2} \cdot C_{gd2}$$

(2)

The gain  $A_{V2}$  is determined by the ratio of the change in drain-source voltage to the gate-source voltage change. Similar equations may be written for M3 with the main difference being  $V_{d2}=2V_{d1}$ . This results in  $C3 \approx \frac{1}{2}$  C2. If four MOSFETs are used then  $C4 \approx \frac{1}{3}$  C2, or in general Cn = [1/(n-1)]C2. Most data sheets supply values for  $C_{iss}$ ,  $C_{rss}$ , and  $C_{oss}$  and for power MOSFETs  $C_{iss} \approx C_{gs}$  and  $C_{rss} = C_{gd}$ .

A zener diode or switching diode between the gate and source<sup>4</sup> of M2 and M3 can be used in place of a resistor. The cathode of the diode should be connected to the gate of the MOSFET. Also when calculating  $C'_{gs2}$  the diode capacitance will be added in Eq. (2). A diode between the gate and source has two advantages over the resistor. First, for wide pulses the resistor acts to shut the MOSFETs off by drawing a conduction current while the diode leakage cur-

FIG. 1. Reliable method of stacking power MOSFETs.

rent is negligible. Second, a zener diode will protect the gate-source oxide from overvoltages.

## **III. AN EXAMPLE**

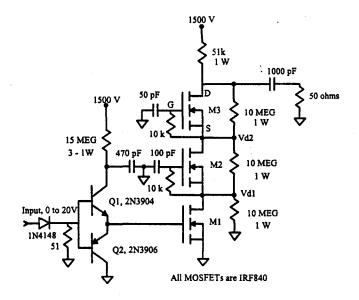

Figure 2 shows a pulse generator designed around the method given above. The IRF840 has  $C_{iss} = 1300 \text{ pF}$  and  $C_{rss} = 50 \text{ pF}$ . Since the drain-source voltage of each MOSFET will change by 500 V while at the same time the gate-source voltage must not exceed 20 V, the voltage gain, Av, is approximately 25. The equivalent gate-source capacitance of M1, M2, or M3 is 2500 pF (1300 pF+25×50 pF). For amplifier or ramp design where swing linearity is important, 10 V is a better choice for the maximum  $V_{gs}$ . For  $V_{gs}$  larger than 10 V, the MOSFET will be in its linear region, or in other words the MOSFET will be ON.

FIG. 2. Pulse generator using stacked MOSFETs.

N N a

L

S

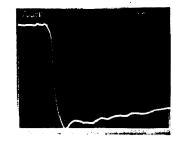

FIG. 3. Output of MOSFET pulser. 200 V/div and 5 ns/div.

Transistor Q1 is operated as an avalanche transistor<sup>4,8</sup> with breakdown voltage of 120 V. When Q1 is triggered by the input signal, 0 to 20 V, it dumps the charge on the 470 pF capacitor into the input capacitance of M1. If the input of M1 looks like a capacitor only, no lead inductances, a capacitive voltage divider exists between the 470 pF avalanche transistor capacitor and the 2500 pF input capacitance of M1. This voltage division limits the applied gate drive to 20 V. Adding the effects of the lead inductance can cause the gate potential to rise above 20 V. The driver compensates for the voltage induced by the lead inductances by increasing the voltage applied to the gate of M1. When the gate potential rises above 20 V Q2 turns on, after a delay long enough to charge M1's input capacitance, and pulls the gate back to 20 V.

The gate capacitors of M2 and M3 are 100 and 50 pF or  $\frac{1}{25}$  2500 and  $\frac{1}{50}$  2500 pF. The output of this pulse generator is shown in Fig. 3. The amplitude is 1400 V with a rise time of approximately 2 ns. There was no noticeable jitter. Several of these circuits were built with no MOSFET failures. The switching time of a single device was 2 ns approximately the same as the stack.

Another concern when stacking MOSFETs is maintaining the manufacturers specification on peak pulsed current. When selecting a power MOSFET, the peak current needed will determine the type of MOSFET used while the peak voltage needed will determine the number of devices. In the example given above, three IRF840s, with 500 V and 32 A ratings, provide the maximum number that may be used for a 50  $\Omega$  load.

### **IV. DISCUSSION**

One of the benefits of using the circuit presented in this paper is the ease in which variable width pulses of several thousand volts may be generated. At the present time pulses of this nature use tubes such as the krytron or planar triode with a pulse forming line. A practical limitation in amplitude of 4 kV (80 A) exists with power MOSFETs currently available. Another benefit of the power MOS-FET is its virtually unlimited lifetime when operated properly. This is very attractive when considering the limited lifetime of tubes that perform comparable functions.

Future work will involve developing sweep camera ramp circuits adjustable from subnanoseconds to hundreds of nanoseconds and a more universal MOSFET driver. The MOSFET driver will combine commercially available MOSFET drivers, such as the MIC4420 18 V/6 A, with avalanche transistors.

## ACKNOWLEDGMENT

۲

This work was supported by E.G.&G. Energy Measurements Inc., Las Vegas, Nevada.

<sup>1</sup>M. T. Bernius and A. Chutjian, Rev. Sci. Instrum. 60, 779 (1989).

- <sup>2</sup>M. T. Bernius and A. Chutjian, Rev. Sci. Instrum. 61, 925 (1990).

- <sup>3</sup> R. E. Continetti, D. R. Cyr, and D. M. Neumark, Rev. Sci. Instrum. 63. 1840 (1992).

- <sup>4</sup>R. J. Baker and M. D. Pocha, Rev. Sci. Instrum. 61, 2211 (1990).

- <sup>5</sup>Hamamatsu operators manual for the C1370 Temporal Photometer (streak camera).

- <sup>6</sup>S. W. Thomas, R. L. Griffith, and W. R. McDonald, Opt. Eng. 25, 405 (1986).

- <sup>7</sup>Quantel Avalanche Board PF 410 Schematic, Drawing No. 501-6700-2. <sup>8</sup>R. J. Baker, Rev. Sci. Instrum. 62, 1031 (1991).