# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| BEFORE THE PATENT TRIAL AND APPEAL BOARD                                                       |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

| Micron Technology, Inc.; Micron Semiconductor Products, Inc.; and Micron Technology Texas LLC, |

| Petitioners,                                                                                   |

| V.                                                                                             |

| Unification Technologies LLC,                                                                  |

| Patent Owner.                                                                                  |

|                                                                                                |

| Case No. IPR2021-00941                                                                         |

| U.S. Patent No. 8,762,658                                                                      |

|                                                                                                |

|                                                                                                |

PETITION FOR *INTER PARTES* REVIEW OF CLAIMS 1-5 AND 8-12 OF U.S. PATENT NO. 8,762,658

# **TABLE OF CONTENTS**

|       |      |                                                                                                                                                                                      | Page |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| PETI  | TIOI | NERS' EXHIBIT LIST                                                                                                                                                                   | V    |

| I.    | Intr | oduction                                                                                                                                                                             | 1    |

| II.   | Peti | itioners Meet Requirements for Inter Partes Review                                                                                                                                   | 2    |

| III.  | Pro  | secution History of the '658 Patent                                                                                                                                                  | 2    |

| IV.   | Tec  | hnology Background                                                                                                                                                                   | 3    |

| V.    | Sun  | nmary of the '658 Patent                                                                                                                                                             | 5    |

| VI.   |      | e Priority Date of the '658 Patent Does Not Precede September 22,                                                                                                                    | 6    |

|       | A.   | Priority Requires Every Limitation to Have Explicit, Implicit, or Inherent Support                                                                                                   |      |

|       | В.   | Summary of the 2006 Provisional                                                                                                                                                      |      |

|       | C.   | The 2006 Provisional Has No Support for Claim 1's "message comprising a logical identifier, the message indicating that data associated with the logical identifier has been erased" |      |

|       | D.   | The 2006 Provisional Has No Support for the "storage module configured to store persistent data in the non-volatile storage medium in response to the indication"                    | 16   |

|       | Е.   | The 2006 Provisional Has No Support for "the persistent data is configured to indicate that the data associated with the logical identifier is erased"                               |      |

|       | F.   | The Dependent Claims Similarly Lack Priority                                                                                                                                         | 21   |

| VII.  | Lev  | vel of Ordinary Skill in the Art                                                                                                                                                     |      |

| VIII. | Cla  | im Construction                                                                                                                                                                      | 23   |

| IX.   | Pre  | cise Relief Requested                                                                                                                                                                | 25   |

|       | A.   | Ground 1                                                                                                                                                                             | 25   |

|       | B.   | Qualifying Prior Art                                                                                                                                                                 | 25   |

|       | C.   | The Proposed Ground Is Not Cumulative or Redundant                                                                                                                                   | 28   |

| X.    | The  | Prior Art                                                                                                                                                                            | 30   |

|       | A.   | Summary of the Shu Patent                                                                                                                                                            | 30   |

|       | В.            | Summary of Shu's Trim Proposals                                                                                       | 31 |

|-------|---------------|-----------------------------------------------------------------------------------------------------------------------|----|

|       | C.            | Summary of IBM                                                                                                        | 32 |

|       | D.            | Motivation to Combine                                                                                                 | 34 |

| XI.   |               | ound 1: Obvious over the Shu Patent (Ex. 1003) in View of the Shu<br>in Proposals (Exs. 1017-1018) and IBM (Ex. 1027) | 36 |

|       | A.            | Claim 1                                                                                                               | 37 |

|       | B.            | Claim 2                                                                                                               | 50 |

|       | C.            | Claim 3                                                                                                               | 52 |

|       | D.            | Claim 4                                                                                                               | 53 |

|       | Ε.            | Claim 5                                                                                                               | 54 |

|       | F.            | Claim 8                                                                                                               | 55 |

|       | G.            | Claim 9                                                                                                               | 56 |

|       | Н.            | Claim 10                                                                                                              | 57 |

|       | I.            | Claim 11                                                                                                              | 58 |

|       | J.            | Claim 12                                                                                                              | 60 |

| XII.  | Sec           | ondary Considerations                                                                                                 | 61 |

| XIII. | Mai           | ndatory Notices                                                                                                       | 62 |

|       | A.            | Real Parties-in-Interest                                                                                              | 62 |

|       | B.            | Related Proceedings                                                                                                   | 63 |

|       | C.            | Lead and Backup Counsel                                                                                               | 64 |

|       | D.            | Electronic Service                                                                                                    | 64 |

| XIV.  | Fee           | s                                                                                                                     | 65 |

| XV.   | Cor           | nclusion                                                                                                              | 65 |

| CLA]  | IM L          | ISTING                                                                                                                | 67 |

| CER   | ΓΙFΙ          | CATE OF COMPLIANCE                                                                                                    | 71 |

| CER   | rifi <i>(</i> | CATE OF SERVICE                                                                                                       | 72 |

# **TABLE OF AUTHORITIES**

| Cases                                                                                               | Page(s) |

|-----------------------------------------------------------------------------------------------------|---------|

| Cisco Sys., Inc. v. Capella Photonics, Inc., IPR2014-01276, Paper 40 (P.T.A.B. Feb. 17, 2016)       | 27      |

| Dynamic Drinkware, LLC v. Nat'l Graphics, Inc., 800 F.3d 1375 (Fed. Cir. 2015)                      | 7, 27   |

| Gen. Plastic Indus. Co. v. Canon Kabushiki Kaisha, IPR2016-01357, Paper 19 (P.T.A.B. Sept. 6, 2017) | 29, 64  |

| Geo. M. Martin Co. v. All. Mach. Sys. Int'l LLC,<br>618 F.3d 1294 (Fed. Cir. 2010)                  | 61      |

| <i>In re Giacomini</i> , 612 F.3d 1380 (Fed. Cir. 2010)                                             | 27      |

| LizardTech, Inc. v. Earth Res. Mapping, Inc.,<br>424 F.3d 1336 (Fed. Cir. 2005)                     | 7       |

| Polaris Indus., Inc. v. Arctic Cat Inc.,<br>IPR2016-01713, Paper 9 (P.T.A.B. Feb. 27, 2017)         | 27      |

| Purdue Pharma L.P. v. Faulding Inc.,<br>230 F.3d 1320 (Fed. Cir. 2000)                              | 7, 9    |

| In re Robertson,<br>169 F.3d 743, 49 USPQ2d 1949 (Fed. Cir. 1999)                                   | 8       |

| Rozbicki v. Chiang,<br>590 F. App'x 990 (Fed. Cir. 2014)                                            | 8       |

| In re Smith,<br>458 F.2d 1389, 173 USPQ 679 (CCPA 1972)                                             | 9       |

| Spherix Inc. v. Matal,<br>703 F. App'x 982 (Fed. Cir. 2017)                                         | 36      |

| Target Corp. v. Proxicom Wireless, LLC, IPR2020-00904, Paper 11 (P.T.A.B. Nov. 10, 2020)            | 36      |

| Vas-Cath Inc. v. Mahurkar,<br>935 F.2d 1555 (Fed. Cir. 1991)                                                                   | 8        |

|--------------------------------------------------------------------------------------------------------------------------------|----------|

| ZTE (USA) Inc. v. Evolved Wireless LLC,<br>IPR2016-00757, Paper 42 (P.T.A.B. Nov. 30, 2017)                                    | 61, 62   |

| Statutes                                                                                                                       |          |

| 35 U.S.C. § 102(e)                                                                                                             | 27       |

| 35 U.S.C. § 112                                                                                                                | , 25, 27 |

| 35 U.S.C. § 119(e)(1)                                                                                                          | 27       |

| 35 U.S.C. § 120                                                                                                                | 7, 8, 25 |

| Other Authorities                                                                                                              |          |

| 37 C.F.R. § 42.104(a)                                                                                                          | 2        |

| MPEP §§ 714.02 and 2163.06                                                                                                     | 9        |

| MPEP § 2163                                                                                                                    | 8, 9, 22 |

| PTAB Consolidated Trial Practice Guide at 59, available at www.uspto.gov/sites/default/files/documents/ tpgnov.pdf (Nov. 2019) | 29       |

# **PETITIONERS' EXHIBIT LIST**

| Ex. No. | Brief Description                                                      |

|---------|------------------------------------------------------------------------|

|         | U.S. Pat. No. 8,762,658 B2, titled "SYSTEMS AND                        |

| 1001    | METHODS FOR PERSISTENT DEALLOCATION," to Flynn                         |

|         | et al.                                                                 |

|         | U.S. Provisional Pat. App. No. 60/912,728, titled "REMOVE-             |

| 1002    | ON-DELETE TECHNOLOGIES FOR SOLID STATE DRIVE                           |

|         | OPTIMIZATION," to Frank Shu et al. ("Shu Provisional").                |

|         | U.S. Pat. No. 9,207,876, titled "REMOVE-ON-DELETE                      |

| 1003    | TECHNOLOGIES FOR SOLID STATE DRIVE                                     |

|         | OPTIMIZATION," to Frank Shu et al. ("Shu Patent").                     |

| 1004    | Expert Declaration of Jacob Baker, Ph.D., P.E., Regarding U.S.         |

| 1004    | Patent No. 8,762,658 (June 4, 2021).                                   |

|         | American National Standard for Information Technology-                 |

| 1005    | ATA/ATAPI Command Set – 2 (ACS-2), ANSI INCITS 482-                    |

|         | 2012 (May 30, 2012) (excerpts filed with permission).                  |

| 1006    | Serial ATA: High Speed Serialized AT Attachment Revision               |

| 1000    | 1.0, Serial ATA International Organization (Aug. 29, 2001).            |

| 1007    | Serial ATA (SATA) ATA Revision 2.5, Serial ATA                         |

| 1007    | International Organization (Oct. 27, 2005).                            |

| 1008    | William D. Brown & Joe E. Brewer, Nonvolatile                          |

| 1000    | Semiconductor Memory Technology (IEEE 1998).                           |

| 1009    | Brian Dipert & Markus Levy, Designing with FLASH                       |

| 1007    | MEMORY (Annabooks 1994).                                               |

| 1010    | April 2007 Plenary Minutes 2, e07156r0 (T13 and INCITS,                |

| 1010    | Apr. 24, 2007).                                                        |

|         | U.S. Pat. No. 8,533,406 B2, titled "APPARATUS, SYSTEM,                 |

| 1011    | AND METHOD FOR IDENTIFYING DATA THAT IS NO                             |

|         | LONGER IN USE," to Flynn et al.                                        |

|         | Original Complaint for Patent Infringement, <i>Unification Techs</i> . |

| 1012    | LLC v. Micron Tech. Inc., No. 6:20-cv-500 (W.D. Tex. 2020),            |

|         | ECF No. 1.                                                             |

|         | Exhibit A to Plaintiff's First Amended Infringement                    |

| 4.5.1.5 | Contentions: Unification Technologies' Allegations of                  |

| 1013    | Infringement with Respect to U.S. Patent No. 8,762,658,                |

|         | Unification Techs. LLC v. Micron Tech. Inc., No. 6:20-cv-500           |

|         | (W.D. Tex. 2020).                                                      |

| 1014 | Frank Shu & Nathan Obr, <i>Data Set Management Commands</i> Proposal for ATA8-ACS2, T13 (rev. 6, Dec. 12, 2007).                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1015 | U.S. Provisional Pat. App. No. 60/873,111, titled "ELEMENTAL BLADE SYSTEM," to Flynn et al. (Dec. 6, 2006) ("2006 Provisional").                                                                                                                                             |

| 1016 | Docket Report for <i>Unification Techs. LLC v. Micron Tech. Inc.</i> , No. 6:20-cv-500 (W.D. Tex. 2020) (accessed June 3, 2021).                                                                                                                                             |

| 1017 | Frank Shu, <i>Notification of Deleted Data Proposal for ATA8-ACS2</i> , T13 (rev. 0, Apr. 21, 2007).                                                                                                                                                                         |

| 1018 | Frank Shu & Nathan Obr, <i>Data Set Management Commands Proposal for ATA8-ACS2</i> , T13 (rev. 1, July 26, 2007).                                                                                                                                                            |

| 1019 | Excerpt of Plaintiff's Responses to Defendant's First Set of Interrogatories (No. 16) (April 26, 2021), <i>Unification Techs</i> . <i>LLC v. Micron Tech. Inc.</i> , No. 6:20-cv-500 (W.D. Tex. 2020).                                                                       |

| 1020 | Eran Gal et al., <i>Mapping Structures for Flash Memories:</i> Techniques and Open Problems, Proceedings of the IEEE INTERNATIONAL CONFERENCE ON SOFTWARE—SCIENCE, TECHNOLOGY & ENGINEERING (digital version), Herzlia, Israel, 2005, pp. 83-92, doi: 10.1109/SWSTE.2005.14. |

| 1021 | Public file history of U.S. Pat. No. 8,672,658, titled "SYSTEMS AND METHODS FOR PERSISTENT DEALLOCATION," to Flynn et al.                                                                                                                                                    |

| 1022 | Frank Shu, Solid-State Drives: Next-Generation Storage, Microsoft WinHEC 2007 (May 14-17, 2007).                                                                                                                                                                             |

| 1023 | Wayback Machine Archive of Microsoft WinHEC 2007<br>Conference Presentations Website, captured Sept. 12, 2007,<br>https://web.archive.org/web/20070214023104/http://www.microsoft.com/whdc/winhec.                                                                           |

| 1024 | Frank Shu, Windows 7 Enhancements for Solid-State Drives, Microsoft WinHEC 2008 (Nov. 4-6, 2008).                                                                                                                                                                            |

| 1025 | U.S. Pat. No. 5,404,485A, titled "FLASH FILE SYSTEM," to Ban.                                                                                                                                                                                                                |

| 1026 | Curriculum vitae of Jacob Baker, Ph.D., P.E.                                                                                                                                                                                                                                 |

| 1027 | H. Niijima, <i>Design of a Solid-State File Using Flash EEPROM</i> , IBM JOURNAL OF RESEARCH AND DEVELOPMENT, vol. 39, no. 5, pp. 531-45, Sept. 1995.                                                                                                                        |

| 1028 | U.S. Pat. No. 7,057,942, titled "MEMORY MANAGEMENT DEVICE AND MEMORY DEVICE" to Suda et al.                                                                                                                                                                                  |

| 1029 | U.S. Pat. No. 7,624,239, titled "METHODS FOR THE MANAGEMENT OF ERASE OPERATIONS IN NON-                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | VOLATILE MEMORIES," to Bennett et al.                                                                                                                                                                                                                 |

| 1030 | Plaintiff's Reply Claim Construction Brief, <i>Unification Techs</i> . <i>LLC v. Micron Tech. Inc.</i> , No. 6:20-cv-500 (W.D. Tex. 2020), ECF No. 57.                                                                                                |

| 1031 | Computer-generated redline comparison of changes from the Shu Provisional to the Shu Patent.                                                                                                                                                          |

| 1032 | SD Specifications Part 1 PHYSICAL LAYER Simplified Specification Version 1.10, SD Group and SD Card Association Technical Committee (Mar. 18, 2005).                                                                                                  |

| 1033 | U.S. Pat. 6,014,724, titled "FLASH TRANSLATION LAYER BLOCK INDICATION MAP REVISION SYSTEM AND METHOD," to Jenett.                                                                                                                                     |

| 1034 | U.S. Provisional Pat. App. No. 60/974,470 for "Apparatus, System, and Method for Object-Oriented Solid-State Storage," to Flynn et al. ("September 2007 Provisional").                                                                                |

| 1035 | Claim Construction Order, <i>Unification Techs. LLC v. Micron Tech. Inc.</i> , No. 6:20-cv-500 (W.D. Tex. 2020), ECF No. 67.                                                                                                                          |

| 1036 | U.S. Pat. No. 6,677,432 B2, titled "MEMORY MANAGEMENT SYSTEM SUPPORTING OBJECT DELETION IN NON-VOLATILE MEMORY," to Saltz et al.                                                                                                                      |

| 1037 | U.S. Pat. No. 9,632,727 B2, titled "SYSTEMS AND METHODS FOR IDENTIFYING STORAGE RESOURCES THAT ARE NOT IN USE," to Flynn et al.                                                                                                                       |

| 1038 | Expert Report of Sylvia D. Hall-Ellis, Ph.D., Regarding Public Availability of the IBM Journal Publication (Ex. 1027), dated May 26, 2021.                                                                                                            |

| 1039 | Declaration of Frank Shu Regarding Publication of Proposals (Exs. 1017, 1018), dated June 2, 2021.                                                                                                                                                    |

| 1040 | American National Standard for Information Technology—AT Attachment with Packet Interface – 7 Volume 1 – Register Delivered Command Set, Logical Register Set (ATA/ATAPI-7 V1), ANSI INCITS 397-2005 (Feb. 7, 2005) (excerpts filed with permission). |

#### I. Introduction

The challenged claims in the U.S. Patent No. 8,762,658 ("the '658 Patent") should never have issued. The fatal flaw for these claims arises from the classic scenario of an applicant forced to amend claims to overcome prior art rejections, in a manner unsupported by the broad, high-level disclosure of an earlier provisional application. When applying the proper priority date—here, the September 22, 2007 filing date of the second provisional application<sup>1</sup> (the "September 2007 Provisional")—intervening prior art invalidates the challenged claims.

The intervening prior art in this case is exceptionally strong. In co-pending litigation, Unification Technologies LLC ("UTL") alleges that challenged claims cover products that implement the "Trim" command. Here, the intervening prior art consists of Frank Shu's initial proposal of the accused Trim command (Ex. 1017) to the standards-setting Technical Committee 13 ("T13") and his U.S. Pat. No. 9,207,876 encompassing the same. Ex. 1003. Indeed, Frank Shu led Microsoft's efforts to announce that the popular Windows operating system would support Trim

\_

<sup>&</sup>lt;sup>1</sup> Petitioners assume priority for the challenged claims is properly supported by the September 2007 Provisional application because the prior art herein predates September 22, 2007, but Petitioners reserve the right to challenge this assumption in the co-pending district court litigation.

months before the assumed September 2007 priority date for the challenged claims. Ex. 1022 at 1, 2, 9; Ex. 1023 at 3; Ex. 1024 at 1, 2, 5.

Given these facts, the Board can easily resolve the present IPR challenge. If the Board finds that the earliest provisional application does not fully support the challenged claims, the claims are unquestionably invalid.

# II. Petitioners Meet Requirements for *Inter Partes* Review

Petitioners certify under 37 C.F.R. § 42.104(a) that the '658 Patent "is available for *inter partes* review and that the Petitioners are not barred or estopped from requesting an *inter partes* review challenging the patent claims on the grounds identified in the petition." UTL sued Petitioners for alleged infringement less than one year ago on June 5, 2020. Exs. 1012, 1016.

### III. Prosecution History of the '658 Patent

During examination, to overcome a rejection based on U.S. Patent No. 6,014,724 to Jenett, the applicant amended claim 51 (later issued as claim 1) to recite: "a message comprising a logical identifier, the message indicating an indication that data associated with [[a]] the logical identifier has been erased." Ex. 1021 at 1234. The applicant argued that in light of this amendment, the prior art does not comprise a message compromising a "logical identifier [that] has been erased." *Id.* at 1241-42. Section VI below explains why the earliest 2006 provisional application for the '658 Patent ("the 2006 Provisional") lacks support

for this amendment.

On September 25, 2013, the applicant disclosed a December 12, 2007 proposal by Frank Shu to T13 in an information disclosure statement ("the 2013 IDS") as one of 191 references. *Id.* at 980 (cite no. D19). The 2013 IDS, however, failed to indicate that the proposal was the "sixth revision" of Frank Shu's proposal or otherwise suggest the possibility of earlier revisions that predate the September 2007 Provisional. Ex. 1014, cover. The Examiner likely realized that the September 2007 Provisional predated the cited December 12, 2007 date without further considering the reference and without realizing that earlier proposals existed.

The applicant's amendment and selective IDS disclosure of the sixth Trim proposal led the Examiner to believe that "the art of record fails to teach or suggest receiving a message/hint/identifier comprising a logical identifier that indicates data associated with the logical identifier has been erase[d]." Ex. 1021 at 1261-63.

### IV. Technology Background

Flash memory is a form of solid-state nonvolatile computer memory. Flash memory is organized in erasable units called "blocks," which are made up of smaller "pages." Ex. 1004 (Expert Declaration of Jacob Baker, hereinafter "Baker") ¶ 110.

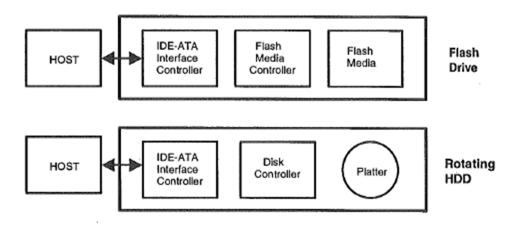

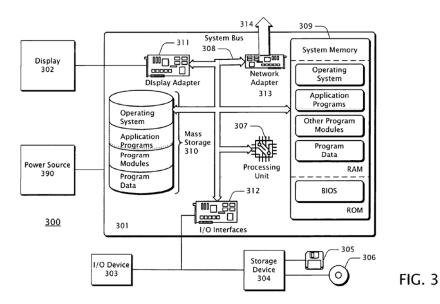

Since at least the early 1990s, the generic architecture of both flash (e.g., solid-state drive ("SSD")) and magnetic-platter (e.g. hard disk drive ("HDD")) mass-storage devices has included: (1) an interface, (2) a controller to manage data in the

storage device, and (3) a storage medium in the form of flash memory or a magnetic platter. *E.g.*, Ex. 1009 at 66, Fig. 4.14 (reproduced below); Ex. 1025 at Fig. 1.

Figure 4.14: Mass Storage Architecture

Flash memory has long used a flash translation layer ("FTL") to map logical addresses to physical addresses. Baker ¶¶ 128-129; *see also, e.g.*, Ex. 1020 at 3, 9 (crediting Ban with patenting the FTL in 1995); Ex. 1025 (Ban's FTL patent); Ex. 1033, 5:21-26; Ex. 1015 at 77 (admitting that "[t]raditional" flash storage systems used FTL's like those patented by M-Systems, referring to Ex. 1025); Ex. 1027 Fig. 1 (showing direct and reverse Address Translation Tables between logical addresses ("LA") and physical addresses ("PA")). The FTL allows computer systems to operate and address data in a logical address space (e.g., logical address 0x0000 through 0xFFFF) without concern for where a solid-state storage device physically saves the data (e.g., in which particular block/page). Baker ¶ 131.

Unlike magnetic-platter hard drives, flash memory cannot be directly overwritten—a block must be erased before written to again. *Id.* ¶ 72. To improve

an SSD's ability to identify and erase invalid data, Jenett invented sending file indication maps from an operating system to a flash memory controller so that the flash memory controller can track invalid blocks and erase them. Ex. 1033. Later, Frank Shu improved upon Jenett's idea and proposed that the operating system instead send the Trim command, which specifies the logical block addresses of invalid data, instead of sending an entire file indication map. Exs. 1003, 1017. Frank Shu then led Microsoft Windows to announce support for the Trim command. Ex. 1022 at 8; Ex. 1023; Ex. 1024 at 2, 4, 10. The industry would go on to adopt the Trim command as part of the ACS-2 standard. Ex. 1005 § 7.9.3.2.

# V. Summary of the '658 Patent

Independent claim 1 recites an apparatus that includes a non-volatile storage medium, a request receiver module, and a storage module. Ex. 1001, 53:2-16. The request receiver module is configured to receive a message comprising a logical identifier that is mapped to a physical storage location of the non-volatile storage medium. *Id.* The message indicates that "data associated with the logical identifier has been erased." *Id.* The storage module is configured to store persistent data on the non-volatile storage medium where the persistent data is (1) configured to indicate that the data associated with the logical identifier is erased and (2) stored in response to the indication that data associated with the logical identifier has been erased. *Id.*

UTL contends that the "message" in claim 1 covers Frank Shu's Trim command. Ex. 1013, passim.

# VI. The Priority Date of the '658 Patent Does Not Precede September 22, 2007

The '658 Patent claims priority to provisional application nos. 60/873,111, filed December 6, 2006, and 60/974,470, filed September 22, 2007. The disclosure of the '658 Patent diverged greatly from the 2006 Provisional. In fact, none of the inventors executed declarations contemporaneous with the as-filed '658 Patent application. Instead, the applicant recycled declarations signed five years prior to the '658 Patent's 2012 filing date. Ex. 1021 at 152-54.

The 2006 Provisional does not support the priority date for the challenged claims. Instead, as shown herein, the 2006 Provisional lacks support for at least three claim limitations of issued claim 1:

- (1) "a message comprising a logical identifier, the message indicating that data associated with the logical identifier has been erased,"

- (2) "a storage module configured to store persistent data on the non-volatile storage medium in response to the indication," and

- (3) "the persistent data is configured to indicate that the data associated with the logical identifier is erased."

The 2006 Provisional also fails to support the dependent claims. UTL contends that certain sections of the 2006 Provisional provide support (Ex. 1019 at

35-36), but each section lacks support for the reasons explained below. Thus, the priority date for the challenged claims comes on or after September 22, 2007.

# A. Priority Requires Every Limitation to Have Explicit, Implicit, or Inherent Support

To comply with the written description requirement of 35 U.S.C. § 112 and receive an earlier priority date under 35 U.S.C. § 120,<sup>2</sup> each claim limitation must be expressly, implicitly, or inherently supported in the originally filed disclosure. MPEP § 2163(II)(A)(3)(b). That original disclosure "must describe the invention" sufficiently to convey to a person of skill in the art that the patentee had possession of the claimed invention at the time of the application, i.e., that the patentee invented what is claimed." LizardTech, Inc. v. Earth Res. Mapping, Inc., 424 F.3d 1336, 1345 (Fed. Cir. 2005). "In other words, the specification of the provisional must 'contain a written description of the invention and the manner and process of making and using it, in such full, clear, concise, and exact terms, '35 U.S.C. § 112 ¶ 1, to enable an ordinary skilled artisan to practice the invention claimed in the non-provisional application." Dynamic Drinkware, LLC v. Nat'l Graphics, Inc., 800 F.3d 1375, 1378 (Fed. Cir. 2015). One skilled in the art, reading the original disclosure, "must immediately discern the limitation at issue in the claims." Purdue Pharma L.P. v.

<sup>&</sup>lt;sup>2</sup> Nothing in 35 U.S.C. § 112 or § 120 allows the Patent Owner to provide support by arguing that the claims were obvious under § 103 in view of the provisional.

Faulding Inc., 230 F.3d 1320, 1323 (Fed. Cir. 2000).

The written description requirement "guards against the inventor's overreaching by insisting that he recount his invention in such detail that his future claims can be determined to be encompassed within his original creation." *Vas-Cath Inc. v. Mahurkar*, 935 F.2d 1555, 1561 (Fed. Cir. 1991). If the originally filed disclosure does not provide support for each claim limitation, a priority or benefit claim under 35 U.S.C. § 120 must be denied. MPEP § 2163(II)(A)(3)(b).

Narrowing the claims by introducing elements or limitations that are not supported by the as-filed disclosure is a violation of the written description requirement of pre-AIA 35 U.S.C. § 112. MPEP § 2163.05(II); see, e.g., Rozbicki v. Chiang, 590 F. App'x 990, 996 (Fed. Cir. 2014) (nonprecedential) (finding that patentee "cannot now improperly narrow its language by importing limitations not supported by the claim language or written description").

When an explicit limitation in a claim "is not present in the written description whose benefit is sought[,] it must be shown that a person of ordinary skill would have understood, at the time the patent application was filed, that the description requires that limitation." MPEP § 2163(II)(A)(3)(b) (citing cases) (emphasis added). "Inherency, however, may not be established by probabilities or possibilities. The mere fact that a certain thing may result from a given set of circumstances is not sufficient." In re Robertson, 169 F.3d 743, 745, 49 USPQ2d

1949, 1950-51 (Fed. Cir. 1999) (citations omitted). A subgenus is not necessarily implicitly described by a genus encompassing it and a species upon which it reads. *In re Smith*, 458 F.2d 1389, 1395, 173 USPQ 679, 683 (CCPA 1972). "[O]ne cannot disclose a forest in the original application, and then later pick a tree out of the forest and say here is my invention. In order to satisfy the written description requirement, the blaze marks directing the skilled artisan to that tree must be in the originally filed disclosure." *Purdue Pharma*, 230 F.3d at 1326-27.

When filing an amendment to pending claims, "an applicant should show support in the original disclosure for new or amended claims." MPEP § 2163(II)(A)(3)(b); see also MPEP §§ 714.02 and 2163.06 ("Applicant should ... specifically point out the support for any amendments made to the disclosure."). The applicant here never argued that the claim amendments at issue are supported by the 2006 Provisional. Ex. 1021 at 1232-43.

# B. Summary of the 2006 Provisional

The 2006 Provisional contains a scattershot of separate ideas catalogued as "claims," none of which match the '658 Patent's challenged claims. *Compare* Ex. 1015, *with* Ex. 1001. Most of these "claims" in the 2006 Provisional have nothing to do with the challenged claims. *See, e.g.*, Ex. 1015, 20-22 (describing "identical card pairings" for pairing together cards in a blade server chassis), 24 (describing a business model of leasing storage to third parties).

UTL asserts in the co-pending litigation that the 2006 Provisional's "claim" 18 provides § 112 support for the challenged claims of the '658 Patent. Ex. 1030 at 10 (citing the "empty block directive").

"Claim" 18 of the 2006 Provisional presents a high-level problem and solution. The problem: "Garbage collection based storage systems such as those commonly used with NAND flash get very poor performance when they do not have enough free space." Ex. 1015 at 40. The stated solution references an "empty-block directive" or "hint":

#### Statement of Solution

Most agents that use block storage do not need the contents of every block to be preserved. File systems, for example, are rarely filled to near the capacity of the block storage on which they are storing the data. If the file system were to supply a hint to the block storage regarding which specific blocks do not hold data that needs to be preserved, the efficiency of the garbage collection on the underlying block storage system can be greatly enhanced.

The empty-block directive can be added to the block storage API and protocols. File systems and other clients of that API/protocol can be enhanced to issue these directives. For example, when a file is deleted, the file-system can issue an "empty-block" directive for the blocks that contained the data for that file, but no longer need to remember the contents. This directive could even serve a secondary security purpose by incorporating a flag to indicate that the data not only need not be preserved, but should be destroyed.

*Id.* The applicant also provided an "alternative" solution. In the alternative solution, instead of sending the hint/command, the 2006 Provisional states that agents can write zeros to the storage medium, thereby overwriting the blocks whose contents are no longer needed:

An alternative to introducing this empty-block directive could be to have the agents simply write all zeros to the blocks whose contents are no longer needed. The underlying block storage system can recognize all-zero blocks and avoid having to actually store the contents. Subsequent reads can return the same all-zero data. Certain file systems such as XFS, for security purposes, have options for zeroing out the blocks that held data from deleted files. Simply enabling those options could be sufficient to allow garbage collection based block storage systems to achieve high efficiency by interpreting those zeroed blocks as "free". Or, those file systems could be enhanced to issue an "empty-block" directive in place of zeroing the blocks.

Id.

# C. The 2006 Provisional Has No Support for Claim 1's "message comprising a logical identifier, the message indicating that data associated with the logical identifier has been erased"

As explained in Section IV above, Jenett invented sending a file indication map to an SSD to indicate invalid data, and in April 2007, Frank Shu proposed that this type of command should identify the specific logical block address of invalid data (instead of sending a whole file indication map). Ex. 1033; Exs. 1017-1018. The 2006 Provisional lacks any disclosure of this concept.

Instead, the 2006 Provisional has no disclosure about the structure of the "hint" or "empty-block" directive other than it could incorporate "a flag" that indicates whether data should be destroyed. Baker ¶¶ 68-69. Nowhere does the 2006 Provisional state that the "empty-block" hint/directive should comprise "a logical identifier." *Id.* ¶¶ 68-87. At best, the 2006 Provisional describes a hint "regarding which specific blocks do not hold data" and that "file-systems can issue an 'empty-block' directive for the blocks that contained data for that file." Ex. 1015 at 40. But this disclosure falls short of disclosing that the hint or directive uses or "compris[es] a logical identifier" for identifying such blocks, as opposed to

identifying the blocks some other way. For these reasons, a POSITA would not have understood "claim" 18 of the 2006 Provisional to explicitly teach that the "indication comprises a logical identifier." Baker  $\P$  68-69. Thus, the 2006 Provisional contains no explicit support of a "message comprising a logical identifier" as recited in the challenged claims. *Id*.

Nor does the 2006 Provisional provide an inherent or implicit disclosure of the empty-block hint/directive comprising a logical identifier. Id. ¶¶ 69-72. In a related patent, the applicant claimed the empty-block directive separately from logical block addresses. Ex. 1037, 54:55-56. The '658 Patent discloses that some commands use physical addresses, not logical addresses, to identify blocks. Ex. 1001, 15:29-32, 18:18-26, 21:47-53, 35:44-48. Based on this disclosure, a POSITA would have recognized that a hint or directive might have identified a physical address instead of the claimed logical identifier. Baker ¶ 70. Indeed, a POSITA would have recognized even more alternatives for the structure of the hint or directive. For example, a different instruction, separate from the hint or directive, could include the logical identifier, which is similar to how erase commands worked in the SD Specification. Id.; Ex. 1032 § 4.3.5 (requiring, in sequence, a command CMD32 to identify the START block, a separate command CMD33 to identify the END block, and finally the command CMD38 to ERASE the previously indicated blocks). As yet another example, Jenett solved this same problem by sending an

entire "file indication map." Ex. 1033, Fig. 5 block 600, *passim*; Ex. 1021 at 936-37.

Because the empty-block hint/directive does not comprise a logical identifier, the 2006 Provisional further lacks support for "data associated with the logical identifier has been erased." The 2006 Provisional describes providing a "hint" that "specific blocks do not hold data that needs to be preserved" and further describes "when a file is deleted, the file system can issue an 'empty-block directive' for the blocks that contained the data for that file, but no longer need to remember the contents." Ex. 1015 at 40. The 2006 Provisional further describes potentially "incorporating a flag to indicate that data not only need not be preserved, but should be destroyed." *Id*.

But the descriptions of data that "do not ... need[] to be preserved" or "should be destroyed" does not support claim 1's recital of "data associated with the logical identifier has been erased." Baker ¶ 71. Instead, these disclosures teach that the data has <u>not</u> been erased: either the data is still present and (i) need not be "preserved" or (ii) the data is still present and "should be destroyed." *Id.* ¶¶ 71-72. In fact, these disclosures would have led a POSITA away from a message indicating that data "has been erased." *Id.* ¶ 71. Thus, the empty-block hint/directive has nothing to do with indicating a message using a logical identifier to indicate that anything associated with the logical identifier "has been erased," as claimed in the

'658 Patent. *Id.* ¶¶ 71-72.

The 2006 Provisional mentions that one example condition for sending an empty-block directive is when "a file is deleted." Ex. 1015 at 40. But the 2006 Provisional does not say that the empty-block directive indicates that the file is erased and that the file is identified using a logical identifier. The language describing what is indicated is: "for the blocks that contained the data for that file, but no longer need to remember the contents." *Id.*; Baker ¶ 72. This means that the data exists and no longer needs to be remembered; the data is not indicated as "erased" as claimed. Baker ¶ 72.

For these reasons, "claim" 18 of the 2006 Provisional fails to expressly, implicitly, or inherently disclose any of these options, much less the specific option that the hint or directive comprises "a logical identifier."

UTL cannot salvage support from other parts of the 2006 Provisional. The alternative solution of writing zeros also makes no reference to using a logical identifier. Ex. 1015 at 40. Aside from "claim" 18, the only other 2006 Provisional "claims" that mention an empty-block hint/directive include "claims" 14 and 29. Baker ¶¶ 75, 82; Ex. 1015 at 35, 103. But, these "claims" discuss entirely different problems and solutions, and neither discloses a hint/directive comprises a logical identifier. Baker ¶¶ 75, 82; Ex. 1015 at 35, 103. Moreover, provisional "claim" 14 operates under an incompatible assumption—"that every block contains contents

that must always be remembered—in other words, no block can be considered free space". Ex. 1015 at 35; Baker ¶ 73. If anything, provisional "claim" 14, titled "object based storage with garbage collection," shows that the inventors had not solved how to integrate object storage and garbage collection because this provisional "claim" recites incomplete and incomprehensible sentences as the purported "solution." Ex. 1015 at 35; Baker ¶ 75.

Furthermore, other passages in the 2006 Provisional mention a "logical block" in other contexts, but these parts also fail to describe an empty-block hint/directive involving a logical identifier. For example, "claims" 22 and 24 of the 2006 Provisional mention logical blocks *in a map* but say nothing about receiving logical identifiers with the empty-block hint/directive. Baker ¶ 74; Ex. 1015 at 68, 72-74.

Additionally, to the extent that UTL refers to the 2006 Provisional's "claim" 30, this description only involves an ObjectID as part of object-based commands—a type of command different from block commands such as the empty-block hint/directive. Baker ¶ 83; Ex. 1015 at 104. Also, this provisional "claim" directs the POSITA away from block-based commands entirely because it purportedly gives the POSITA "a killer reason to change from block access to object access." Ex. 1015 at 104; Baker ¶ 83. Provisional "claims" 31 and 32 also discuss an incompatible object-based system and provide no further detail about the empty-block hint/directive. Ex. 1015 at 105-06; Baker ¶ 83.

Provisional "claims" 22 and 23 mention "messages," but these "messages" refer to "units on NAND flash" or, in other words, "encapsulate raw data" on a media. Ex. 1015 at 69-70. "A message is written by placing commands on the command queues." *Id.* at 69. Thus, the disclosures about the structure of a "message" in provisional "claims" 22 and 23 do not support the structure of a command like the empty-block hint/directive. Baker ¶¶ 77-78.

Provisional "claim" 27(E) relates to a "NAND controller" and a "NAND Write Agent." Ex. 1015 at 92. This "claim" relates to a controller command for writing new data to pages of flash memory and has nothing to do with the emptyblock hint/directive sent from an operating system to the SSD. Baker ¶ 80.

The remaining provisional "claims" 2 and 9 cited by UTL have nothing to do with the empty-block hint/directive. Ex. 1015 at 23, 31; Baker ¶ 86.

For these reasons, the 2006 Provisional fails to describe "a message comprising a logical identifier" in sufficient detail so that one skilled in the art could reasonably conclude that the applicant had possession of the claimed invention and thus fails to provide written description support for the challenged claims. Baker ¶87.

# D. The 2006 Provisional Has No Support for the "storage module configured to store persistent data in the non-volatile storage medium in response to the indication"

The 2006 Provisional makes no mention of a storage module "configured to

store persistent data on the non-volatile storage medium in response to the indication." Ex. 1001, 53:11-13; Ex 1015; Baker ¶¶ 89-101.

"Claim" 18 in the 2006 Provisional only discloses what the empty-block hint/directive signifies, not what to do afterward—especially not what a *storage module* does in response to the empty-block hint/directive. Ex. 1015 at 40; Baker ¶¶ 90-92. Moreover, nothing in the 2006 Provisional discloses storing any type of *persistent* data in response to the empty-block hint/directive. Baker ¶ 93. The lack of this detail is important because the 2006 Provisional teaches that some data structures "may not be stored persistently at all." Ex. 1015 at 68.

At best, the 2006 Provisional only mentions that as a result of the hint/directive, "the efficiency of the garbage collection on the underlying block storage system can be greatly enhanced." Ex. 1015 at 40. But the 2006 Provisional never explains how. Baker ¶92. The lack of this teaching leaves the implementation to the imagination of a POSITA, including whether to preserve the data or destroy it, as signified by the empty-block hint/directive. *Id.* ¶¶ 91, 94. In any event, the 2006 Provisional's disclosure fails to suggest the possibility of storing more, persistent data in response to the empty-block hint/directive. *Id.* Indeed, continuation Patent No. 8,533,406 describes different actions optionally performed in response to receiving an indication. Ex. 1011, 54:15-55:14. For these reasons, the 2006 Provisional fails to expressly, implicitly, or inherently disclose a "storage

module configured to store persistent data in the non-volatile storage medium in response to the indication." Baker ¶¶ 89-94.

UTL cannot salvage support from other parts of the 2006 Provisional. For example, provisional "claim" 25 describes garbage collection that operates under the opposite, incompatible assumption: "Blocks are always considered valid, their contents needing to be preserved, even if the client (say a file system) doesn't have anything useful stored in a given block." Ex. 1015 at 74; Baker ¶ 96. This incompatible assumption would have prevented a POSITA from combining provisional "claim" 18's "hint ... regarding which specific blocks do not hold data that needs to be preserved" with the garbage collection system of provisional "claim" 25. Ex. 1015 at 40, 74; Baker ¶ 96. Provisional "claim" 25 also describes a different solution that occurs in response to a different condition: "Whenever data is appended to the medium, we identify the old data that is becoming garbage." Ex. 1015 at 75. This disclosure of identifying old data in response to a different condition (when new data is appended) does not support the '658 Patent's claimed storage module configured to store persistent data indicating that the data associated with the logical identifier in the message is erased in response to the indication. Baker ¶ 97.

Along the same lines, provisional "claim" 29 relates to "Object Storage" and only briefly mentions "providing an 'empty-block' directive can additionally

improve the efficiency of emulating a block device on top of object based storage that uses garbage collection underneath" without the further detail needed to support the claims. *Id.* ¶ 98; Ex. 1015 at 103. Provisional "claim" 29 says nothing about what happens during garbage collection in response to receiving the empty-block hint/directive. Baker ¶ 98.

Aside from provisional "claims" 18 and 29, only provisional "claim" 14 mentions the same empty-block hint/directive. Claim 14 discloses nothing about storing persistent data in response to the empty-block hint/directive and provides an incomprehensible solution. *Id.*; Ex. 1015 at 35. Also, provisional "claim" 24 relates to identifying "bad" blocks that are "no longer useable" due to defects, but this has nothing to do with the empty-block hint/directive. Ex. 1015 at 72; Baker ¶ 99. None of the other provisional "claims" 2, 9, 22-25, 27, or 30-32 further describe any persistent storage in response to the empty-block hint/directive for the reasons discussed in section VI.C above.

For these reasons, the 2006 Provisional fails to describe a "storage module configured to store persistent data in the non-volatile storage medium in response to the indication" in sufficient detail so that a POSITA could reasonably conclude that the applicants had possession of the claimed invention and thus fails to provide written description support for the challenged claims. Baker ¶¶ 88-101.

# E. The 2006 Provisional Has No Support for "the persistent data is configured to indicate that the data associated with the logical identifier is erased"

For the reasons discussed above, the 2006 Provisional does not disclose what the claimed message indicates and what a storage module does in response to receiving the message. For the same reasons, the 2006 Provisional fails to further disclose, in response to receiving a message comprising a logical identifier, storing persistent data that indicates that the data associated with the logical identifier "is erased."

The 2006 Provisional discloses that the empty-block hint/directive "regard[s] which specific blocks do not hold data that needs to be preserved" and "could even ... incorporat[e] a flag to indicate that data not only need not be preserved, but should be destroyed." Ex. 1015 at 40. These sentences teach that the data "should be destroyed" or "not preserved," meaning that the data is *not yet erased*. Baker ¶ 103. Along the same lines, the 2006 Provisional discloses, "For example, when a file is deleted, the file-system can issue an 'empty-block' directive for the blocks that contained the data for that file, but no longer need to remember the contents." Ex. 1015 at 40. This sentence has nothing to do with storing persistent data indicating that data is erased because "no longer need to remember" means that the data still exists at this time but may be erased in the future. Baker ¶ 103. Thus, these sentences would have led a POSITA *away* from using persistent data to "indicate

that the data associated with the logical identifier is erased." *Id.* If anything, this provisional disclosure would have led a POSITA to understand that associated data *does not need to be preserved*, or perhaps that data *should be destroyed*, but certainly not that the data "is erased," as claimed. *Id.*

For these reasons, the 2006 Provisional fails to describe "the persistent data is configured to indicate that the data associated with the logical identifier is erased" in sufficient detail so that one skilled in the art could reasonably conclude that the applicants had possession of the claimed invention and thus fails to provide written description support for the challenged claims. *Id.* ¶¶ 102-104.

# F. The Dependent Claims Similarly Lack Priority

Claims 2-5 and 8-12 depend from claim 1 and thus lack priority support from the 2006 Provisional because of dependency.

Claims 2-5 independently lack priority support from the 2006 Provisional because the 2006 Provisional contains no details about the claimed "reconstruction module" at all, much less a reconstruction module that indicates the various types of "erased" information recited in claims 2-5. *Id.* ¶ 106. Claim 8 independently lacks priority because the 2006 Provisional says nothing about the claimed "read request module" returning the recited indication while data remains on the physical storage location. Ex. 1015 at 40, 70, 96; Baker ¶ 106. Claims 9-10 independently lack priority because the 2006 Provisional says nothing about the claimed "marking

module" that operates as claimed in response to an indication. Ex. 1015 at 40; Baker ¶ 106. Claims 11-12 independently lack priority because the 2006 Provisional says nothing about the claimed "storage recovery module" or "erase module" that operates in response to the indication. Ex. 1015 at 40; Baker ¶ 106.

UTL repeatedly cites provisional "claims" 30-32 to support the challenged dependent claims. Ex. 1019 at 35-36. Not only do these provisional "claims" 30-32 fail to support the dependent claims, these provisional "claims" relate only to an incompatible object storage system instead of a block-based system. Baker ¶¶ 73, 106; Ex. 1015 at 104-06. Aside from provisional "claim" 18, other provisional "claims" assume that "the contents of every block must be preserved ALWAYS," which is incompatible with an empty-block hint/directive that indicates certain data does not need to be preserved. Ex. 1015 at 35 ("Block based storage assumes that every block contains contents that must always be remembered."), 104; Baker ¶¶ 73, 106. UTL also relies on the 2007 Provisional disclosure of read agents and erase agents, but these sections lack disclosure about the claimed functionality and say nothing about operating in response to the empty-block hint/directive. Ex. 1015 at 94, 96.

Thus, the 2006 Provisional disclosure would not have conveyed possession of these dependent claims to a POSITA, and the priority claim to the 2006 Provisional "must be denied" for the dependent claims. Baker ¶ 107; MPEP § 2163(II)(A)(3)(b).

# VII. Level of Ordinary Skill in the Art

A POSITA in September 2007 would have a bachelor of science degree in computer science or electrical engineering and at least two years of experience in the design, development, implementation, or management of solid-state memory devices. Baker ¶ 58. The references cited in this Petition, the state of the art, and the experience of Dr. Jacob Baker as described in his expert declaration (Ex. 1004) reflect this level of skill in the art. In this Petition, reference to a POSITA refers to a person with these or similar qualifications.

The POSITA in September 2007 would have also known about Frank Shu's Trim proposals to T13 and Microsoft's announcement to support Trim at WinHEC 2007. *Id.* ¶ 60. The POSITA would also have known fundamental concepts related to flash memory management. *Id.* ¶ 59 (explaining concepts).

#### VIII. Claim Construction

The Board construes claims under the same claim construction standard as civil actions in federal district court. The district court for the co-pending litigation has construed certain terms. Ex. 1035. Although the parties have disputed the claim constructions, the construction disputes do not affect the outcome of this Petition.<sup>3</sup> The district court's constructions for the claims at issue in this Petition are as follows:

<sup>&</sup>lt;sup>3</sup> Petitioners reserve all rights to appeal the district court's claim constructions.

| Claim Term                       | Court                                              |

|----------------------------------|----------------------------------------------------|

| "logical identifier"             | An identifier that can be associated with a        |

| Claims 1, 4, 8-10                | physical address on a storage device for           |

|                                  | identifying data stored at the physical address.   |

| "marking module"                 | Not indefinite; not subject to § 112(f); plain and |

| Claims 9, 10                     | ordinary meaning.                                  |

| "storage module"                 | Not indefinite; not subject to § 112(f); plain and |

| Claim 1                          | ordinary meaning.                                  |

| "data associated with the        | Not indefinite; plain and ordinary meaning.        |

| logical identifier [has been/is] |                                                    |

| erased"                          |                                                    |

| Claims 1, 3-5, 8                 |                                                    |

UTL appears to contend that the plain and ordinary meaning of "data associated with the logical identifier [has been/is] erased" refers to "data associated with the logical identifier has been erased by a device connected to the [accused] Product (e.g., by a computer)" and, as a result, "[f]rom the user's perspective, this data has been deleted from a document." Ex. 1013 at 2. Further, UTL contends that this term does *not* refer to data on a non-volatile device being already physically erased. *See*, *e.g.*, *id*. ("The TRIM command tells the SSD that specific areas contain data ....").

#### IX. Precise Relief Requested

#### A. Ground 1

Claims 1-5 and 8-12 are rendered obvious by U.S. Pat. No. 9,207,876 to Frank Shu et al., (the "Shu Patent," Ex. 1003) in view of Frank Shu's Trim Proposals revisions 0-1 (Exs. 1017-1018), and the IBM Journal article, *Design of a solid-state file using flash EEPROM* (Ex. 1027, "IBM").

# **B.** Qualifying Prior Art

For the reasons discussed in Section VI above, the challenged claims of the '658 Patent have an effective filing date no earlier than September 22, 2007.

The Shu Patent has priority to the "Shu Provisional," application no. 60/912,728, filed on April 19, 2007, and is § 102(a) and (e) prior art. Ex. 1003; Ex. 1002. The Shu Patent contains minor edits in comparison to its provisional. Ex. 1031 (showing computer-generated comparison). As shown in the table, the Shu Provisional provides full support for the claims under 35 U.S.C. §§ 112, 120. Thus, the Shu Patent has priority to its provisional filing date.

| Shu Patent Element       | Shu Provisional Support (Ex. 1002)                 |

|--------------------------|----------------------------------------------------|

| 1. A system              | Fig. 3 (showing system).                           |

| comprising:              |                                                    |

| [1a] a computing device  | Fig. 3 (showing computing device 301, processing   |

| that includes at least   | unit 307, memory 309), [0028].                     |

| one processor and        |                                                    |

| memory;                  |                                                    |

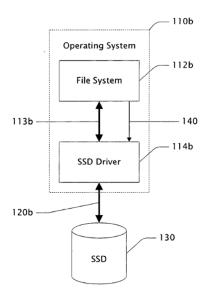

| [1b] a file system; and  | Fig. 1 (showing file system 112b), [0014], [0016]- |

|                          | [0017].                                            |

| [1c] a solid state drive | Fig. 1 (showing SSD driver 114b), [0012]-[0014],   |

| ("SSD") driver that,<br>based on execution by<br>the at least one<br>processor, is configured<br>to:                                                                                                                                                                             | [0016]-[0019], [0021], [0023], [0025]-[0027]. "Processor 307 typically processes or executes various computer-executable instructions to control the operation of computing device 301," which includes the operating system shown in Fig. 3, which includes the SSD driver shown in Fig. 1. [0026].                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

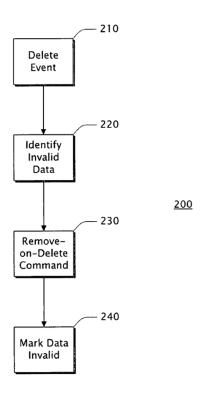

| [1d1] receive, from a file system, a remove-on-delete command that includes invalid data information                                                                                                                                                                             | Fig. 1 (showing SSD driver 114b, receiving the remove-on-delete command via interface 140, from the file system 112b), [0017] ("File system 112b utilizes new interface 140 to communicate invalid data information to SSD driver 114b."), [0023] ("Block 230 indicates a remove-on-delete command. This command typically includes the invalid data information and instructs the SSD device and/or its driver to mark the indicated data as invalid.").                                                                                                                                                                                                                                                                                               |

| [1d2] that indicates that, based on a deletion of at least a portion of a file in the file system, particular data that is stored on an SSD and corresponds to the at least the portion of the file is, as indicated by the deletion, considered invalid by the file system; and | [0015] ("For example, when a file is deleted, the data associated with the file is invalid."); [0017] ("File system 112b utilizes new interface 140 to communicate invalid data information to SSD driver 114b Interface 140 enables file system 112b to indicate to SSD driver 114b via the invalid data information exactly which data stored on SSD 130 are invalid."); [0014] (generally); Fig. 2 at 210-230; [0021] ("Block 210 indicates a delete event impacting data stored on the SSD device. One example of such a delete event is a file delete operation performed by a file system wherein the file is stored on an SSD device."); [0023] ("[S]uch a command is issued by the system performing the delete operation and an SSD driver."). |

| [1e] instruct, based on<br>the received invalid<br>data information, the<br>SSD to mark the<br>particular data invalid<br>on the SSD.                                                                                                                                            | Fig. 2 block 240, [0014], [0017], [0019] ("SSD driver 114b typically interacts with SSD 130 via interface 120b to mark appropriate data, blocks, pages, or the like as invalid."); [0020] ("Such a method may be used to mark deleted SSD data as invalid, otherwise known as 'remove-on-delete."); [0023] ("Block 230 indicates a remove-on-delete command. This command typically instructs                                                                                                                                                                                                                                                                                                                                                           |

| the SSD device and/or its driver to mark the      |

|---------------------------------------------------|

| indicated data as invalid."); [0024] ("Block 240  |

| indicates marking the deleted data as invalid."). |

A pre-AIA 35 U.S.C. § 102(e) prior art reference "shall have the same effect," including a patent-defeating effect, . . . as though it was filed on the date of the . . . provisional" to which it claims priority, as long as certain requirements are met. In re Giacomini, 612 F.3d 1380, 1383-84 (Fed. Cir. 2010) (quoting 35 U.S.C. § 119(e)). In particular, the Board has held that a § 102(e) reference is available as prior art as of its provisional application's filing date when the provisional provides support for: (1) at least one claim of the § 102(e) reference and (2) the subject matter on which the petitioner relies. Cisco Sys., Inc. v. Capella Photonics, Inc., IPR2014-01276, Paper No. 40 at 21-22 (P.T.A.B. Feb. 17, 2016). With respect to the first prong, the provisional application must disclose an invention claimed in the § 102(e) reference "in the manner provided by the first paragraph of section 112." § 119(e)(1); Dynamic Drinkware, LLC v. Nat'l Graphics, Inc., 800 F.3d 1375, 1378 (Fed. Cir. 2015). Only one claim from the later-issued patent must be supported by the provisional. See Cisco Sys. IPR2014-01276, Paper No. 40 at 22 n.9; Polaris Indus., Inc. v. Arctic Cat Inc., IPR2016-01713, Paper 9, at 13 (P.T.A.B. Feb. 27, 2017).

The Shu Trim Proposals published from April 2007 (rev. 0) to August 2007 (rev. 1) and qualify as prior art under § 102(a). Ex. 1010 § 8.1.2; Ex. 1017; Ex. 1018;

Ex. 1039. T13 published the proposal on its freely accessible website T13.org, and industry representatives met to discuss Frank Shu's original Trim Proposal. Ex. 1010 § 8.1.2 (referencing the document number of Ex. 1017); Ex. 1039. Ground 1 below includes citations to the Shu Provisional to show that the provisional discloses the same technology in the Shu Patent.

IBM published by 1996 and qualifies as prior art under § 102(a) and (b). Ex. 1027; Ex. 1038 ¶¶ 40-47.

### C. The Proposed Ground Is Not Cumulative or Redundant

The grounds for trial presented in this Petition are not cumulative to issues already examined during prosecution. The applicant never informed the Patent Office of Frank Shu's original April 21, 2007 Trim Proposal. The Patent Office did not know that UTL contends that the claims cover the Trim command. Because the applicant disclosed only the sixth revision of the Trim Proposal dated after both the 2006 Provisional and the September 2007 Provisional, the Examiner had no reason to look at the sixth revision of the Trim Proposal before allowing the application.

Not only did the Examiner never consider the April 21, 2007 Trim Proposal, the Examiner also never considered IBM. So although the Examiner considered U.S. Publication 2008/0263305 to Shu et al., the Examiner did not do so in view of the April 21, 2007 Trim Proposal and IBM as proposed herein.

The grounds for trial presented in this Petition are not cumulative to issues

already examined in a parallel IPR proceeding, IPR2021-00344. The parallel IPR proceeding assumed, without conceding, the December 2006 priority date and thus did not raise Shu Trim Proposals or the Shu Patent as prior art. The PTAB "recognizes that there may be circumstances in which more than one petition may be necessary, including, for example, . . . when there is a dispute about priority date requiring arguments under multiple prior art references." PTAB Consolidated Trial Practice Guide at 59, *available at* www.uspto.gov/sites/default/files/documents/tpgnov.pdf (Nov. 2019).

The General Plastic factors do not warrant denying this Petition. Gen. Plastic Indus. Co. v. Canon Kabushiki Kaisha, IPR2016-01357, Paper 19 (P.T.A.B. Sept. 6, 2017). IPR2021-00344 relates to overlapping claims of the '658 Patent and was filed on December 22, 2020. At that time, investigation into the Shu Trim Proposals remained ongoing, and Petitioners did not have possession of relevant materials, such as Frank Shu's presentations (Ex. 1022; Ex. 1024) until recently. UTL also delayed providing its priority contentions until late April 2021. Ex. 1019. Discovery remains ongoing. The earlier IPR petition dealt with different prior art and assumed a different priority date; thus, UTL's Preliminary Response to the earlier petition confers no unfair advantage here. The limited resources of the Board will be put to efficient use because the Board is already familiar with the technology and mainly needs to decide a priority date challenge to prevent the applicant from unfairly using

hindsight to capture Frank Shu's invention.

#### X. The Prior Art

## A. Summary of the Shu Patent

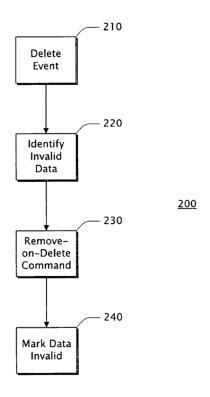

The Shu Patent relates to managing SSDs with flash memory. Ex. 1003, 1:12-15. The Shu Patent teaches that SSDs might unnecessarily preserve invalid data during "wear leveling" and "merge" operations because SSDs "are generally unaware of what data ... is invalid." *Id.*, 1:20-43. Thus, the Shu Patent proposes that an operating system or file system send a "remove-on-delete" command to identify the invalid data to the SSD. *Id.*, 4:4-7, 4:51-5:4. The SSD can then mark the deleted data as invalid using "any form sufficient to identify the invalid data." *Id.*, 5:5-11. These invalid marks allow the SSD to avoid unnecessarily preserving the invalid data during wear leveling operations. *Id.*, abstract, 5:11-13. Shu Patent figure 2 shows the process:

# B. Summary of Shu's Trim Proposals

In these Trim Proposals, Frank Shu proposes the "Trim" command, which corresponds to the "remove-on-delete" command described in the Shu Patent. Baker ¶¶ 156-157; Exs. 1017-1018. These Trim Proposals describe the Trim command that UTL now accuses of infringement. Exs. 1017-1018. The exact format of the Trim command varied across revisions, but all formats reserve bits for a logical block address ("LBA") and a "Count" field to indicate the starting address of data and a length of the data.

| Word   | Name    | Description                                                                          |

|--------|---------|--------------------------------------------------------------------------------------|

| 00h    | Feature | XXh                                                                                  |

|        |         | Number of 256 word-blocks of LBA Range Entry to be transferred. 0000h specifies that |

| 01h    | Count   | 65,536 blocks are to be transferred                                                  |

| 02-04h | LBA     | Reserved                                                                             |

| 05h    | Command | XXh                                                                                  |

Ex. 1017 § 3. Later revisions bundled the Trim command as part of the Data Set Management (DSM) command. Ex. 1018 § 6.1.1.

# C. Summary of IBM

IBM presents "dynamic sector allocation" (also known as "wear leveling") and background garbage collection. Ex. 1027 at 531-32. IBM discusses flash EEPROM characteristics of both NOR and NAND flash memory, including the relatively slow write speeds, the need to erase "all the cells in a block ... at the same time," and the inability to freely overwrite data. *Id.* at 533-34. IBM specifically addresses two problems: (1) "How to extend the lifetime" of flash memory in view of limited erase cycles, and (2) "How to develop an effective algorithm for the erase operation, so that the erase overhead will be almost hidden." *Id.* at 534.

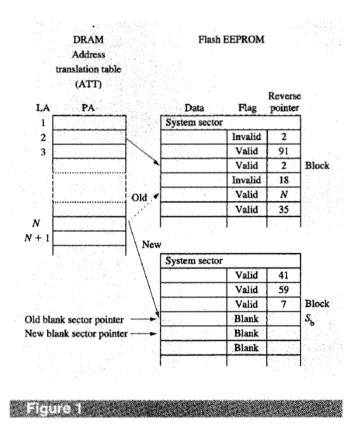

To address both problems, IBM first uses an "address translation table (ATT)" to store "[t]he relation between the logical sector address and the physical sector address" in volatile memory. *Id.* at 535. The system also stores "information for reconstructing the ATT" in nonvolatile flash memory, including whether data is "valid," "invalid," or "blank." *Id.* at 535-36. The system uses the nonvolatile

information to reconstruct the ATT after each power off. Id.at 535.

*Id.* at 535.

To avoid prematurely wearing out a block by repeatedly rewriting/erasing to the same block, a controller writes the physical addresses of a new, blank sector (e.g.,  $S_b$ ; sectors correspond to blocks) in the address translation table ("ATT") when writing data to the same logical address. *Id.* In the picture above, the logical address N will be associated with an address pointing to the new physical sector  $S_b$  (e.g., 4th row) instead of the old physical sector (e.g., 5th row). Baker ¶ 164. This way, the same logical address will relate to different physical addresses. *Id.*

IBM also explains the background garbage collection technique for the

erasable cluster, "which may consist of only one block." Ex. 1027 at 538-39. This technique will ultimately "[e]rase the selected cluster" that contains "garbage" (invalid data), thereby allowing the block to quickly write new data. *Id.* at 539. But before erasing the cluster, all valid sectors are copied to blank sectors, and the ATT is updated appropriately, to preserve the valid data. *Id.*