# UNITED STATES PATENT AND TRADEMARK OFFICE

# **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

# TCT MOBILE (US), INC.; TCT MOBILE (US) HOLDINGS, INC.; HUIZHOU TCL MOBILE COMMUNICATION CO. LTD.; AND TCL COMMUNICATION, INC., Petitioners

v.

FUNDAMENTAL INNOVATION SYSTEMS INTERNATIONAL LLC, Patent Owner

U.S. Patent No. 8,624,550 Issue Date: January 7, 2014 Title: MULTIFUNCTIONAL CHARGER SYSTEM AND METHOD

Case No. IPR2021-

# PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT 8,624,550 CHALLENGING CLAIMS 1-18 UNDER 35 U.S.C. §312 AND 37 C.F.R. §42.104

Mail Stop PATENT BOARD Patent Trial and Appeal Board United States Patent and Trademark Office PO Box 1450 Alexandria, Virginia 22313–1450

# **TABLE OF CONTENTS**

| I.   | INTR                     | ODU    | CTION                                                                       | 1                                                                                                                                                                                                                                                                  |  |  |

|------|--------------------------|--------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| II.  | SUM                      | MARY   | Y OF CHALLENGE 37 C.F.R. §42.104(B)                                         | 3                                                                                                                                                                                                                                                                  |  |  |

| III. |                          |        | ON SHOULD BE GRANTED; DISCRETIONARY<br>NOT APPROPRIATE                      | 4                                                                                                                                                                                                                                                                  |  |  |

|      | A.                       | The A  | pple/Fintiv Factors Support Institution                                     | 4                                                                                                                                                                                                                                                                  |  |  |

|      | B.                       | The C  | General Plastics Factors Support Institution                                | ARY<br>4<br>4<br>4<br>8<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>14<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>26<br>27<br>27<br>5766<br>29<br>29<br>et (Ex.<br>30<br>30<br>31 |  |  |

|      | C.                       | The F  | Cactors Under 35 U.S.C. § 325(d) Support Institution                        | 9                                                                                                                                                                                                                                                                  |  |  |

| IV.  | OVE                      | RVIEV  | V OF THE '550 PATENT                                                        | 10                                                                                                                                                                                                                                                                 |  |  |

|      | A.                       | Discl  | osure of the '550 Patent                                                    | 10                                                                                                                                                                                                                                                                 |  |  |

|      | B.                       | Priori | ty Applications of the '550 Patent                                          | 13                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 1.     | The '021 Application                                                        | 13                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 2.     | The '486 Application                                                        | 14                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 3.     | Priority Date                                                               |                                                                                                                                                                                                                                                                    |  |  |

|      | C.                       | Prose  | cution History of the '550 Patent                                           |                                                                                                                                                                                                                                                                    |  |  |

| V.   | PERS                     | SON O  | F ORDINARY SKILL IN THE ART                                                 | 16                                                                                                                                                                                                                                                                 |  |  |

| VI.  | SUMMARY OF THE PRIOR ART |        |                                                                             |                                                                                                                                                                                                                                                                    |  |  |

|      | A.                       | USB    | 1.1 Specification                                                           | 16                                                                                                                                                                                                                                                                 |  |  |

|      | B.                       | Use o  | f SE1 State in Various Contexts                                             | 26                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 1.     | US Patent 6,531,845 ("Kerai") (Ex. 1012)                                    | 27                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 2.     | US Patent 6,625,738 ("Shiga") (Ex. 1013)                                    | 27                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 3.     | US Patent Application Publication US20030135766<br>("Zyskowski") (Ex. 1014) |                                                                                                                                                                                                                                                                    |  |  |

|      |                          | 4.     | US Patent 6,625,790 ("Casebolt") (Ex. 1015)                                 | 29                                                                                                                                                                                                                                                                 |  |  |

|      |                          | 5.     | Cypress Semiconductor enCoReUSB Datasheet (Ex. 1016)                        | 30                                                                                                                                                                                                                                                                 |  |  |

|      | C.                       | USB    | 2.0 Specification                                                           | 30                                                                                                                                                                                                                                                                 |  |  |

|      | D.                       | Overv  | view of Morita                                                              | 31                                                                                                                                                                                                                                                                 |  |  |

|      | Е.                       | Overv  | view of Dougherty                                                           | 34                                                                                                                                                                                                                                                                 |  |  |

| VII.  | CLA | IM CO | NSTR    | UCTI           | ON                                                                                                                                                      | 36 |

|-------|-----|-------|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | A.  | speci | ficatio | n" (cla        | ciated condition specified in a USB<br>aim 1) and "at least one USB Specification                                                                       | 27 |

|       | л   | 1     |         |                | laim 10)                                                                                                                                                |    |

|       | B.  |       |         |                | ondition" (claims 4, 6, 7, 13, 15, and 16)                                                                                                              |    |

| VIII. |     |       |         |                |                                                                                                                                                         | 39 |

|       | A.  |       |         |                | f Knowledge of a POSITA Renders The<br>Claims 1-18 Obvious                                                                                              | 39 |

|       |     | 1.    | Clain   | n 1            |                                                                                                                                                         | 39 |

|       |     |       | a.      | 1[a].          | An adapter comprising                                                                                                                                   | 39 |

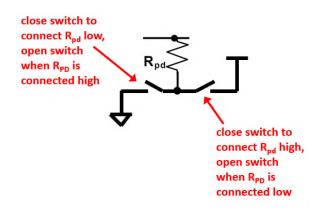

|       |     |       | b.      |                | a USB $V_{BUS}$ line and a USB communication                                                                                                            | 40 |

|       |     |       | c.      | the V<br>assoc | said adapter configured to supply current on<br>V <sub>BUS</sub> line without regard to at least one<br>viated condition specified in a USB<br>fication | 43 |

|       |     |       |         | (1)            | Supplying More than 100 mA or 500mA of Current                                                                                                          | 43 |

|       |     |       |         | (2)            | Supplying More than 100mA of Current without Enumeration.                                                                                               | 46 |

|       |     | 2.    |         |                | ne adapter of claim 1 wherein said associated<br>a current limit                                                                                        | 47 |

|       |     | 3.    |         |                | ne adapter of claim 1 wherein said current is thout USB enumeration                                                                                     | 48 |

|       |     | 4.    | suppl   | ied in         | ne adapter of claim 1 wherein said current is<br>response to an abnormal data condition on<br>ommunication path                                         | 48 |

|       |     | 5.    |         |                | ne adapter of claim 4 wherein said USB<br>tion path includes a D+ line and a D- line                                                                    | 53 |

|       |     | 6.    | data o  | conditi        | ne adapter of claim 5 wherein said abnormal<br>ion is an abnormal data line condition on said<br>l said D– line.                                        | 53 |

| 7.  | Claim 7: The adapter of claim 6 wherein said abnormal data line condition is a logic high signal on each of said D+ and D- lines.                         | 54 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 8.  | Claim 8: The adapter of claim 7, wherein each said logic high signal is greater than 2V.                                                                  | 55 |

| 9.  | Claim 9: The adapter of claim 2 wherein said current limit is 500 mA.                                                                                     | 55 |

| 10. | Claim 10:                                                                                                                                                 | 56 |

|     | a. 10[a]. An adapter comprising                                                                                                                           | 56 |

|     | b. $10[b]$ . a USB V <sub>BUS</sub> line and a USB communication path                                                                                     | 56 |

|     | c. $10[c]$ . said adapter configured to supply current on<br>the V <sub>BUS</sub> line without regard to at least one USB<br>Specification imposed limit. | 56 |

| 11. | Claim 11: The adapter of claim 10, wherein said USB<br>Specification imposed limit is a current limit                                                     | 57 |

| 12. | Claim 12: The adapter of claim 10, wherein said current is supplied without USB enumeration.                                                              | 57 |

| 13. | Claim 13: The adapter of claim 10, wherein said current<br>is supplied in response to an abnormal data condition on<br>said USB communication path.       | 57 |

| 14. | Claim 14: The adapter of claim 13, wherein said USB communication path includes a D+ line and a D- line                                                   | 58 |

| 15. | Claim 15: The adapter of claim 14, wherein said<br>abnormal data condition is an abnormal data line<br>condition on said D+ line and said D- line.        | 58 |

| 16. | Claim 16: The adapter of claim 15, wherein said<br>abnormal data line condition is a logic high signal on<br>each of said D+ and D- lines                 | 58 |

| 17. | Claim 17: The adapter of claim 16, wherein each said logic high signal is greater than 2V.                                                                | 58 |

| 18. | Claim 18: The adapter of claim 11, wherein said current limit is 500 mA.                                                                                  | 59 |

|     | B.  | U     | •       | In View Of the USB 1.1 Renders The Subject<br>Claims 1-2, 9, 10-11, And 18 Obvious                                                                                        | 59 |

|-----|-----|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |     | 1.    |         | n 1                                                                                                                                                                       |    |

|     |     |       | a.      | 1[a]. An adapter comprising                                                                                                                                               | 59 |

|     |     |       | b.      | 1[b] a USB V <sub>BUS</sub> line and a USB communication path                                                                                                             | 61 |

|     |     |       | c.      | 1[c] said adapter configured to supply current on<br>the V <sub>BUS</sub> line without regard to at least one<br>associated condition specified in a USB<br>specification | 64 |

|     |     | 2.    |         | n 2: The adapter of claim 1, wherein said associated tion is a current limit                                                                                              | 67 |

|     |     | 3.    |         | n 9: The adapter of claim 2 wherein said current is 500 mA.                                                                                                               | 68 |

|     |     | 4.    | Clain   | n 10:                                                                                                                                                                     | 68 |

|     |     |       | a.      | 10[a] An adapter comprising                                                                                                                                               | 68 |

|     |     |       | b.      | 10[b] a USB $V_{BUS}$ line and a USB communication path                                                                                                                   | 68 |

|     |     |       | c.      | 10[c] said adapter configured to supply current on<br>the V <sub>BUS</sub> line without regard to at least one USB<br>Specification imposed limit                         | 69 |

|     |     | 5.    |         | n 11: The adapter of claim 10 wherein said USB<br>fication imposed limit is a current limit                                                                               | 69 |

|     |     | 6.    |         | n 18: The adapter of claim 11 wherein said current is 500 mA.                                                                                                             | 70 |

| IX. | CON | CLUS  | ION     |                                                                                                                                                                           | 70 |

| X.  | MAN | IDATO | DRY N   | IOTICES – 37 C.F.R. §42.8                                                                                                                                                 | 1  |

|     | А.  | Real  | Party-i | in-Interest (37 C.F.R. §42.8(b)(1))                                                                                                                                       | 1  |

|     | B.  | Relat | ed Ma   | tters (37 C.F.R. §42.8(b)(2))                                                                                                                                             | 1  |

|     | C.  | Lead/ | Back-   | up Counsel (37 C.F.R. §42.8(b)(3))                                                                                                                                        | 2  |

|     | D.  | Servi | ce Info | ormation (37 C.F.R. §42.8(b)(4))                                                                                                                                          | 3  |

| XI. | GRO | UNDS  | FOR     | STANDING – 37 C.F.R. §42.104(A)                                                                                                                                           | 3  |

| AII. FEES – 37 C.F.K. §42.15(A) | XII. | FEES – 37 C.F.R. §42.15(A) |

|---------------------------------|------|----------------------------|

|---------------------------------|------|----------------------------|

# **TABLE OF AUTHORITIES**

# Cases

| <i>Allergen USA, INC. v. Prollenium US Inc.</i> ,<br>1-20-cv-00104, Dkt. No. 34 (July 16, 2020)                     |

|---------------------------------------------------------------------------------------------------------------------|

| Apple Inc. v. Fintiv, Inc.,<br>IPR2020-00019, Paper 11 (PTAB Mar. 20, 2020)4                                        |

| <i>Apple Inc. v. Seven Networks, LLC,</i><br>IPR2020-00156, Paper 10 (PTAB June 15, 2020)6                          |

| General Plastic Industrial Co., Ltd. v. Canon Kabushiki Kaisha,<br>IPR2016-01357, Paper 19 (P.T.A.B. Sept. 6, 2017) |

| HP Inc. v. Neodron LTD,<br>IPR2020-00459, Paper 17 (PTAB Sept. 14, 2020)                                            |

| LG Electronics, Inc. v. Bell Northern Research, LLC,<br>IPR 2020-00319                                              |

| <i>Microsoft Corp. v. Uniloc 2017, LLC,</i><br>IPR 2019-01252                                                       |

| Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co. Ltd.,<br>868 F.3d 1013 (Fed. Cir. 2017)                        |

| ParkerVision, Inc. v. Qualcomm Inc.,<br>903 F.3d 1354 (Fed. Cir. 2018)                                              |

| <i>Phillips v. AWH Corp.</i> ,<br>415 F.3d 1303 (Fed. Cir. 2005) ( <i>en banc</i> )37                               |

| Sand Revolution II, LLC v. Continental Intermodal Group5 Trucking LLC,                                              |

| IPR2019-01393, Paper 24 (PTAB June 16, 2020)4                                                                       |

| <i>Thryv, Inc. v. Click-To-Call Techs., LP,</i><br>140 S. Ct. 1367 (2020)                                           |

| Toyota Motor Corp.,<br>IPR2016-00422                                                              |             |

|---------------------------------------------------------------------------------------------------|-------------|

| <i>Uniloc 2017 LLC v. Vudu, Inc.</i> ,<br>1-19-cv-00183, Dkt. No. 72 (March 26, 2020)             | 5           |

| <i>ZTE (USA) Inc. et al. v. Fundamental Innovation System International LLC,</i><br>IPR2018-00110 | 9, 10       |

| <i>ZTE (USA) Inc. et al. v. Fundamental Innovation System International LLC,</i><br>IPR2018-00111 | .16, 37, 38 |

| Statutes                                                                                          |             |

| 35 U.S.C. § 102(a)                                                                                | 30, 31      |

| 35 U.S.C. § 102(a) and (b)                                                                        | .16, 17, 20 |

| 35 U.S.C. § 102(e)                                                                                | .27, 29, 34 |

| 35 U.S.C. §103                                                                                    | 1           |

| 35 U.S.C. § 103(a)                                                                                | 3, 4        |

| 35 U.S.C. §§ 314(a)                                                                               | 4           |

| 35 U.S.C. §315(e)(2)                                                                              | 7           |

| 35 U.S.C. § 325(d)                                                                                | 9           |

| Other Authorities                                                                                 |             |

| 37 C.F.R. §42.104(B)                                                                              | 3           |

| 157 Cong. Rec. S1363 (Mar. 8, 2011)                                                               | 5           |

| Exhibit | Description                                                                                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1001    | U.S. Patent No. 8,624,550 to Fischer et al., "Multifunctional<br>Charger System and Method," filed June 28, 2012 (the "550<br>Patent")                                                              |

| 1002    | U.S. Patent File History of the '550 Patent Excerpts (the "'550 File History")                                                                                                                      |

| 1003    | Declaration of Dr. Jacob Baker regarding U.S. Patent No. 8,624,550 ("Baker")                                                                                                                        |

| 1004    | Curriculum Vitae of Dr. Jacob Baker                                                                                                                                                                 |

| 1005    | Amended Complaint, <i>Fundamental Innovation Systems Int'l LLC</i><br>v. <i>TCT Mobile (US) Inc. et al.</i> , No. 1:20-cv-00552-CFC (D. Del.<br>Sep. 11, 2020) ("Complaint")                        |

| 1006    | U.S. Patent No. 7,360,004 ("Dougherty")                                                                                                                                                             |

| 1007    | Japanese Patent Application No. 2000-165513A ("Morita")                                                                                                                                             |

| 1008    | U.S. Provisional Application No. 60/273,021                                                                                                                                                         |

| 1009    | U.S. Provisional Application No. 60/330,486                                                                                                                                                         |

| 1010    | Universal Serial Bus Specification, Revision 1.1, September 23, 1998 ("USB 1.1")                                                                                                                    |

| 1011    | Universal Serial Bus Specification, Revision 2.0, April 27, 2000<br>("USB 2.0")                                                                                                                     |

| 1012    | U.S. Patent No. 6,531,845 ("Kerai")                                                                                                                                                                 |

| 1013    | U.S. Patent No. 6,625,738 ("Shiga")                                                                                                                                                                 |

| 1014    | U.S. Patent Application Publication No. 2003/0135766<br>("Zyskowski")                                                                                                                               |

| 1015    | U.S. Patent No. 6,625,790 ("Casebolt")                                                                                                                                                              |

| 1016    | Cypress CY7C63722/23 CY7C63742/43 enCoRe <sup>™</sup> USB<br>Combination Low-Speed USB & PS/2 Peripheral Controller, by<br>Cypress Semiconductor Corporation, published May 25, 2000<br>("Cypress") |

| 1017    | U.S. Patent No. 5,923,146 ("Martensson")                                                                                                                                                            |

# Petitioners' Exhibit List

#### I. INTRODUCTION

TCT Mobile (US), Inc.; TCT Mobile (US) Holdings, Inc.; Huizhou TCL Mobile Communication Co. Ltd.; and TCL Communication, Inc. ("Petitioners") petition for *inter partes* review of claims 1-18 (the "Challenged Claims") of U.S. Patent No. 8,624,550 (the "550 Patent") on the grounds that they are unpatentable under 35 U.S.C. §103.

The Challenged Claims relate to an adapter that uses an industry standard Universal Serial Bus ("USB") port to charge a device. Providing power through USB ports was well understood and routine by the priority date of the '550 Patent, but the Challenged Claims purport to "invent" an adapter that provides current "without regard" to the power/current limits in the USB specification(s). In other words, the Challenged Claims cover little more than a charger/adapter that uses a USB interface but does not follow one or more of the requirements of the USB specification. Independent claims (1 & 10), for example, require an "adapter" that supplies current "without regard" to an associated "condition" or "limit" imposed by the USB Specification. Certain dependent claims (2, 9, 11, 18) clarify that the disregarded "condition" or "limit" is the USB Specification's requirement that no more than 500mA of current be supplied to any single device.

The USB specification itself, however, notes that certain devices will disregard this condition/limit in certain situations. Accordingly, this "invention"

1

would have been known and obvious to a POSITA as of the priority date of the '550 Patent. Specifically, the USB specification indicates that "high powered" ports will provide a *minimum* of 500 mA of current to downstream devices. Accordingly, those high powered ports—which were known and used in the art as of the priority date of the '550 Patent—are themselves invalidating prior art because they are configured to supply current without regard to the 500 mA limit when, for example, connected to a single downstream device (e.g., when used as a phone charger). Indeed, the provisional application to which the '550 Patent claims priority admits that such devices were known and available. Ex. 1008 ('021 Application) (discussing prior art "high powered" hubs configured to supply around 700mA-800mA of current).

The prior art cited in this petition has not been fully considered by the patent office. The Morita patent has not been considered by the examiner or the PTAB in any proceedings and it renders all 18 claims obvious. Specifically, Morita discloses a charging device that plugs directly into a power outlet, contains a high-powered port, and charges a single device (a phone) in a charging mode that does not involve communicating over the USB data lines. In that mode, a POSITA would have understood that the device provides more than 500mA of current to the phone and, accordingly, supplies current without regard to the corresponding USB limit.

The Dougherty reference discloses a docking station that supplies 2,500 mA of current—far exceeding the corresponding 500 mA limit—to a laptop device. The PTAB considered certain arguments related to Dougherty in prior proceedings, but found that the prior petitions pointed to an *external* "communication path" instead of an *internal* "communication path" (which the PTAB found to be required by the Challenged Claims). The PTAB noted, however, "[i]t is possible, if not highly probable," that the docking station of Dougherty includes the required "communication path" and, thus, essentially invited further arguments regarding Dougherty's internal "communication path." As explained herein, Dougherty in view of the USB 1.1 Specification discloses that the docking station of Dougherty does indeed have such an internal communication path

Because there is a reasonable likelihood that Petitioners will prevail with respect to these claims, Petitioners respectfully request that the Board institute *inter partes* review.

# II. SUMMARY OF CHALLENGE 37 C.F.R. §42.104(B)

Petitioners requests that the Board review and cancel claims 1-18 of the '550 Patent based on the following grounds.

| Ground | Claims | Basis | References                                   |  |

|--------|--------|-------|----------------------------------------------|--|

| 1      | 1-18   |       | Morita in view of the knowledge of a POSITA. |  |

|  | 2 | 1-2, 10-11,<br>18 | Pre-AIA 35 U.S.C. § 103(a) | Dougherty in view of the USB 1.1 Specification. |

|--|---|-------------------|----------------------------|-------------------------------------------------|

|--|---|-------------------|----------------------------|-------------------------------------------------|

# **III. INSTITUTION SHOULD BE GRANTED; DISCRETIONARY DENIAL IS NOT APPROPRIATE**

The Board should not exercise its discretion to deny institution under 35 U.S.C. §§ 314(a) or 325(d). If the Board considers exercising its discretion to deny institution, Petitioner respectfully requests leave to file a reply to address any discretionary denial arguments Patent Owner makes in its preliminary response.

## A. The Apple/Fintiv Factors Support Institution.

There is a parallel district court proceeding involving the '550 Patent in the District of Delaware. Ex. 1005. The complaint was filed on April 23, 2020. However, the *Apple/Fintiv* factors support institution despite the existence of the Delaware litigation. *Apple Inc. v. Fintiv, Inc.,* IPR2020-00019, Paper 11 (PTAB Mar. 20, 2020).

First, potential for a district court stay, is neutral or weighs in favor of institution. Neither party has requested a stay,<sup>1</sup> so at worst this factor is neutral because the Board "will not attempt to predict" how the district court will proceed. *Sand Revolution II, LLC v. Continental Intermodal Group5 Trucking LLC,* IPR2019-01393, Paper 24 at 7 (PTAB June 16, 2020) (informative). Congress, however,

<sup>&</sup>lt;sup>1</sup> Petitioner does intend to move for a stay of the Delaware case.

intended for district courts to be liberal in granting stays pending PTAB proceedings, especially in cases where petitioners moved quickly after service of a complaint. 157 Cong. Rec. S1363 (Mar. 8, 2011) (Sen. Schumer) (Congress placed "a very heavy thumb on the scale in favor of a stay being granted"). Given that Petitioners have moved expeditiously (*see* factor 2 discussion below), this factor favors institution. Furthermore, Judge Connolly has consistently granted stays in similar patent litigation cases, especially those where the petitions are instituted. *See, e.g., Allergen USA, INC. v. Prollenium US Inc.,* 1-20-cv-00104, Dkt. No. 34 (July 16, 2020); *Uniloc 2017 LLC v. Vudu, Inc.,* 1-19-cv-00183, Dkt. No. 72 (March 26, 2020).

Second, the proximity of the trial date to the final written decision, weighs in favor of institution. The Court has scheduled a *Markman* hearing for June 23, 2021. PTAB will likely issue an institution decision before the Court issues a final *Markman* decision. Judge Connolly consistently grants stays when the PTAB institutes trial in such instances. *See id.* And, even in the unlikely case that Judge Connolly does not grant a stay, the trial date is scheduled for October 17, 2022. This is several months after the PTAB's expected final written decision based on this Petition's filing date of January 12, 2021, which would tentatively calendar an institution date of approximately July 12, 2021 and final written decision date of approximately early July, 2022 (depending on the accorded filing date).

Third, investment in the parallel proceeding, weighs in favor of institution. Discovery will still be in the early stages, with the deadline not until December 17, 2021. It is unlikely that any fact depositions will have taken place before the institution decision. Further, as stated above, it is unlikely that the district court will have issued a *Markman* ruling by the time of the institution decision, and little to no Court resources will have been devoted to analyzing prior art invalidity issues. Again, the parallel district court litigation is likely to be stayed once the present Petition is instituted.

Furthermore, as part of a holistic analysis, the Board considers the speed with which the petitioner acted. *Apple Inc. v. Seven Networks, LLC,* IPR2020-00156, Paper 10 at 11–12 (PTAB June 15, 2020). In cases where the petitioner acted diligently and without meaningful delay, as here, any investment of the parties in the parallel district court litigation is mitigated. *HP Inc. v. Neodron LTD,* IPR2020-00459, Paper 17 at 40 (PTAB Sept. 14, 2020). Here, Petitioners filed this Petition within about four months of the Answer date, and roughly two months after Patent Owner served preliminary infringement contentions. Such diligence favors institution.

Fourth, overlap of issues, weighs in favor of institution. The Petition challenges claims that are not asserted in the district court action. And while the petition also challenges the same claims as the parallel district court proceeding, there is a high likelihood that Judge Connolly grants a stay upon institution. In the unlikely instance where a stay is not granted, a final written decision will still issue before the beginning of trial. The final written decision, once issued, will trigger estoppel for in the district court litigation for grounds that were raised or reasonably could have been raised. *See* 35 U.S.C. §315(e)(2).

Fifth, whether the parties are the same, weighs in favor of institution. The parties with respect to this Petition are the same as those engaged in the parallel district court case.

Finally, other circumstances strongly favor institution. Petitioners advance a targeted Petition with two grounds: the first ground has never been submitted to the Board, and the second ground is one which the Board considered and noted it is "highly probable" to have certain required elements (which it does, *see* Section III.C, *infra*). The strength of the present Petition strongly weighs in favor of institution. The '550 Patent has been asserted against several large electronics companies such as Coolpad, Lenovo, and Petitioners, which litigation remains pending. Patent Owners assert that USB adapters, which are ubiquitous, and the mobile devices they charge infringe the '550 Patent and related patents. Given the substantial impact that the '550 Patent and related patents could have on the mobile device industry, it is in the public interest to address invalidity, especially under new prior art never before submitted to the Board. And as the Supreme Court recently explained, there

is a significant public interest against "leaving bad patents enforceable." *Thryv, Inc. v. Click-To-Call Techs., LP*, 140 S. Ct. 1367, 1374 (2020).

#### **B.** The General Plastics Factors Support Institution

The General Plastics factors support institution despite earlier IPRs being filed by other, unrelated entities. General Plastic Industrial Co., Ltd. v. Canon Kabushiki Kaisha, IPR2016-01357, Paper 19 (P.T.A.B. Sept. 6, 2017); see also Section X.B (Related Matters). First, the current Petitioner (and the real parties-ininterest) are different from the prior petitioners; and there is no relation between them. Id. Second, because the current Petitioner had not been sued or provided notice of alleged infringement when the earlier petitions were filed, the current Petitioner did not know of the prior art in this Petition when the earlier petitions were filed (nor did it have any reason to search for the prior art). Id. Third, while the preliminary responses and decisions from the earlier IPRs did issue before the filing of the current Petition, this timing is the result of Patent Owner not suing the current Petitioner until after said issuance and is thus not the result of current Petitioner's delay. Id.; Microsoft Corp. v. Uniloc 2017, LLC, IPR 2019-01252, Paper 7 at 8-9 (PTAB Dec. 20, 2019). Fourth, Petitioner was diligent in filing the current petition as well as promptly moving to file petitions on the other asserted patents after receiving Patent Owner's selection of claims. Section X.B; LG Electronics, Inc. v.

Bell Northern Research, LLC, IPR 2020-00319, Paper 15 at 13 (PTAB June 23, 2020).

#### C. The Factors Under 35 U.S.C. § 325(d) Support Institution

The factors under 35 U.S.C. § 325(d) also support institution.

The primary reference cited herein (Morita), which is the basis for Ground 1, is a USB mobile device charger that was not considered by the patent examiner or by the PTAB during any of the prior IPR proceedings. Accordingly, this petition presents and relies principally on evidence and argument not yet considered by the examiner or the Board.

In certain earlier proceedings, the PTAB did consider the Dougherty reference cited herein. The PTAB found, however, that the claims of the '550 Patent require a "communications path" that is internal to the claimed "adapter" and that petitioners cited only a communications path that was external to the "adapter" of Dougherty. *See ZTE (USA) Inc. et al. v. Fundamental Innovation System International LLC*, IPR2018-00110 at Paper 12 (Decision Denying Institution of *Inter Partes* Review) at 9-12. Because the petitioners presented no evidence or argument regarding the internal communications path of Dougherty, the PTAB denied institution. *Id.* at 11-12.

The PTAB noted, however, that it is likely the adapter of "Dougherty" comprises the necessary communication path. *Id.* at 12 ("It is possible, if not highly

probable, that docking station 200 contains an internal USB communication path that is utilized for these purposes.") Accordingly, the PTAB essentially invited an explanation as to how Dougherty satisfies the challenged claims as construed in that decision. *Id.* Petitioner provides the corresponding argument and evidence here.

#### IV. OVERVIEW OF THE '550 PATENT

#### A. Disclosure of the '550 Patent

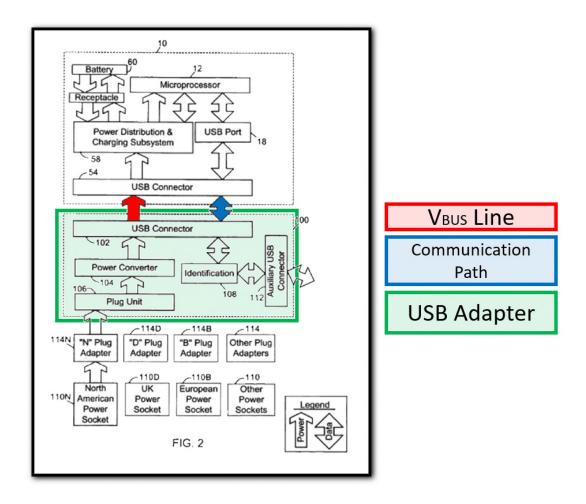

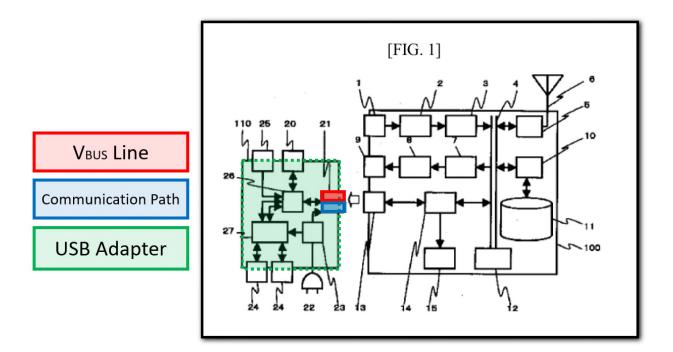

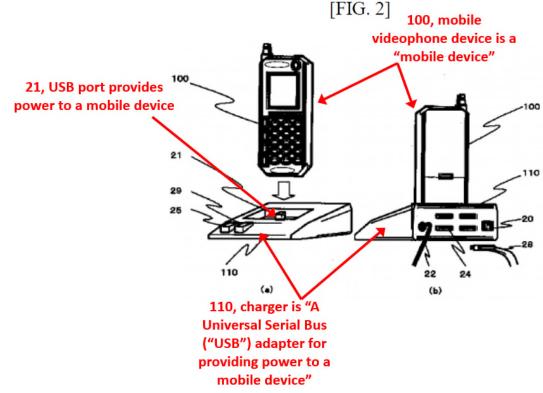

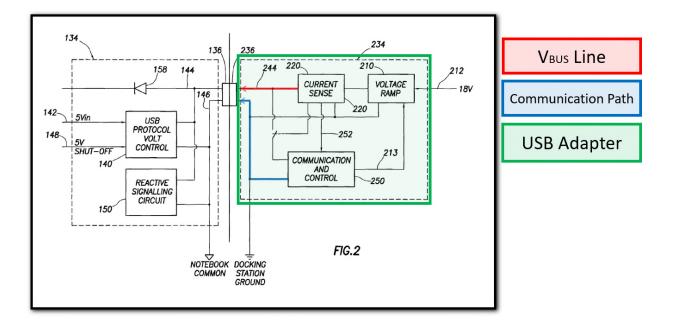

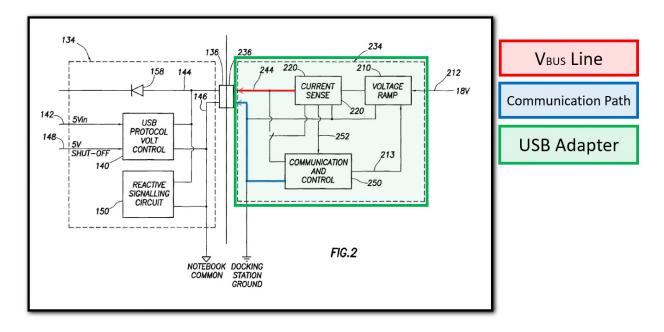

The '550 Patent discloses "a USB adapter" that provides power to a connected device "through a USB port." Ex. 1001 ('550 Patent) at 2:34-36. The USB adapter comprises a "USB  $V_{BUS}$  line" and a "USB Communication Path." *Id.* at Claims 1 and 10. Figure 2, reproduced below, is a schematic diagram of the disclosed USB adapted coupled to an exemplary mobile device. *Id.*, 3:23-24.

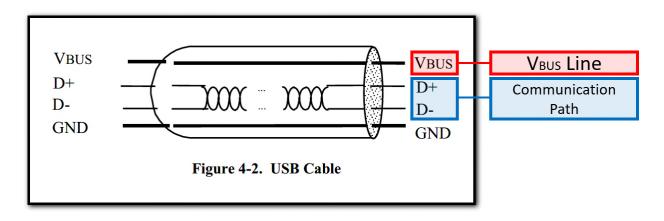

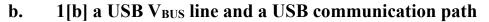

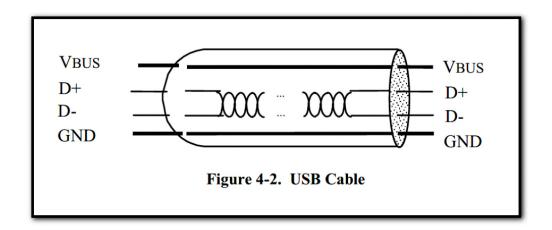

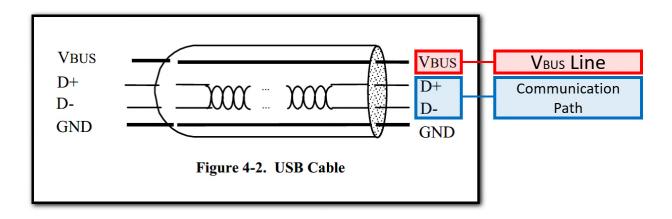

Both the " $V_{BUS}$  line" and the "communication path" were well known and understood components of USB devices. They are expressly accounted for in USB specifications which a POSITA would have been familiar with:

See e.g., Ex. 1010 (USB 1.1) at 17 and Figure 4-2 (annotated).

The challenged claims also require that the "adapter" be "configured to" supply current on the  $V_{BUS}$  line "without regard" to a "condition" or "limit" stated in a USB Specification. Ex. 1001 ('550 Patent) at Claims 1, 10. As discussed in more detail herein, this may involve, for example, being configured to supply current in excess of an amount specified by a USB specification (e.g., the 500mA that may be supplied to a particular device) (Claims 2, 9, 11, 18). *See* Section VII (Claim Construction).

Certain of the challenged claims also require that the adapter be configured to supply current "without USB enumeration" (Claims 3 and 12) or in response to an "abnormal data condition" (Claims 4 and 13) such as a logic high signal on the D+ and D- lines of the communication path (Claims 6-7 and 15-16). As discussed in more detail herein, USB "enumeration" is the communication engaged in by USB devices when connected in order to configure them. *See* USB 1.1 at 179; Baker, ¶ 74. The '550 Patent discloses that an adapter can supply current without engaging in the enumeration process using "an abnormal data line condition at the USB port 18." *Id.* at 9:21-24. Specifically, the '550 patent discloses that a device that detects "voltages on both the D+ and D- lines of the USB connector [that] are greater than 2 Volts (step 220), [will] determine[] that the device connected to the USB connector 54 is not a typical USB host or hub and that a USB adapter 100 has been detected." *Id.*, 9:39-44. In such a scenario, the mobile device can charge the battery or otherwise use the power from the USB connector, without waiting for enumeration. *Id.* at 9:44-47.

#### **B.** Priority Applications of the '550 Patent

The '550 patent claims priority through a series of continuations to two provisional applications: (1) U.S. Provisional Application 60/273,021 (the "'021 Application") (Ex. 1008), filed March 1, 2001; and (2) U.S. Provisional Application No. 60/330,486 (the "'486 Application") (Ex. 1009), filed October 23, 2001.

### 1. The '021 Application

The '021 Application was filed on March 1, 2001. Ex. 1008. The application does not disclose, describe, or purport to invent any novel adapter or charger. To the contrary, the specification discloses "a charging circuit" that is part of a mobile device and that can use current <u>received from the mobile device's USB connection</u> to charge the device's battery. *Id.* at 18 ("... this invention relates to adapting power from the USB for use as a power source by the charging system of the mobile device .....") (emphasis added); *id.* at 20 ("It is an object of the invention ... to <u>use the power traditionally available on the USB</u> as an alternate power source for recharging the portable power supply of the mobile device.") (emphasis added); *id.* at 20 (describing embodiments of "charging circuit" in mobile device).

The '021 Application also noticeably omits any discussion of using an "abnormal data condition" on the USB communication path (claims 4 and 13), that comprises a "logic high signal on each of said D+ and D- lines" (claims 7 and 16), wherein "each said logic high signal is greater than 2V" (claims 8 and 17). *Id.* at 20-30 (discussing various embodiments).

Although the '021 Specification does not purport to invent a USB device that supplies current "without regard" to the USB Specifications, it does make clear that such devices existed at the time. Specifically, the application discloses that the patentee tested *existing* USB hubs to see how much current they would supply. *Id.* at 22-33 ("It was determined experimentally that current can be drawn from several USB ports at a high rate"). The patentee noted that the tested "high powered" hubs were configured to provide up to 700mA-800mA of current before automatically shutting off the power. *Id.* at 22 ("Furthermore, it seems that certain high-power USB ports, such as a self-powered hub, appear to implement only an over-current protection, i.e., they turn off the voltage on the VBUS line for current valued exceeding 700mA-800mA.").

## 2. The '486 Application

The '486 Application was filed on October 23, 2001. Ex. 1009 ('486 Application). The application, for the first time, discussed "a USB power adapter that can provide power to charge a USB chargeable device via the device USB

14

interface." *Id.* at 14. The application also discusses, again for the first time, the use of "abnormal data line conditions" including a signal in which D+ and D- are held high. *Id.* at 24-25.

#### 3. **Priority Date**

Because the '021 Application does not describe various elements of the Challenge Claims, those claims are entitled to the October 23, 2001 priority date of the '486 Application at the earliest. The priority date, however, will not affect the arguments herein as each of the references cited constitutes prior art under either priority date.

#### C. Prosecution History of the '550 Patent

The '550 Patent issued from U.S. Patent Application No. 13/536,767, which was filed on June 28, 2012. On the filing date, the Applicant cancelled all pending claims and added 18 new claims. Ex. 1002 ('550 Patent File History Excerpts) at 1-65. On May 28, 2013, the Examiner rejected all pending claims based upon obviousness-type double patenting over claims 1-12 of U.S. Patent No. 7,986,127. *Id.* at 147-150. The original Patent Owner subsequently filed a terminal disclaimer (*id.* at 162), and the Examiner issued a notice of allowance without further rejections. *Id.* at 169.

#### V. PERSON OF ORDINARY SKILL IN THE ART

The PTAB held in the context of the '550 Patent that a POSITA "would have had a bachelor's degree in electrical engineering and 3-5 years of experience in circuit or device design, or equivalents thereof." *ZTE (USA) Inc. et al. v. Fundamental Innovation System International LLC*, IPR2018-00111 at Paper 62 at 14. At a minimum, such a person would have been aware of and familiar with the USB Specifications that existed as of the priority date of the '550 Patent, including the USB 1.1 and USB 2.0 Specifications discussed herein. Baker, ¶¶ 68. For purposes of this petition, petitioner adopts this description of the hypothetical person of ordinary skill in the art ("POSITA") of the subject matter of the '550 Patent.

### VI. SUMMARY OF THE PRIOR ART

## A. USB 1.1 Specification

The Universal Serial Bus Specification, Revision 1.1, ("USB 1.1") was published by the USB Implementers Forum, Inc. on September 23, 1998. Ex. 1010. It is prior art to the '550 Patent under at least 35 U.S.C. § 102(a) and (b). Moreover, the USB 2.0 Specification would have been part of the knowledge of a POSITA as of the priority date of the '550 Patent. Baker, ¶ 69.

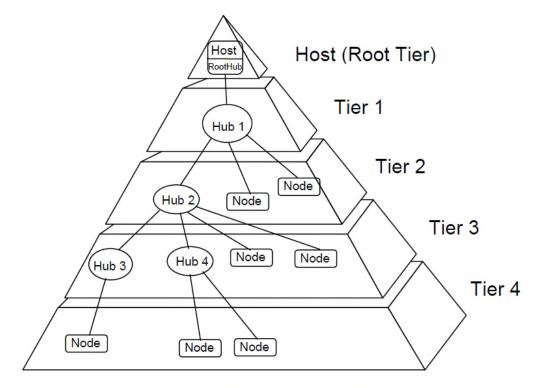

Figure 4-1, below, shows the bus topology for a USB system. Generally, each such system requires a "host" with a "root hub" for purposes of communication. USB 1.1 at 16; Baker, ¶ 70. Without such a hub, there will be no communication

among the devices. For example, connecting, Hub 1 to a node (a node is a connected device, also called a "function") or Hub 2 without connecting Hub 1 to the Host via the Root Hub will not result in a functioning/communicating, USB system. *Id*.

Figure 4-1. Bus Topology

USB 1.1 at 16 (annotated).

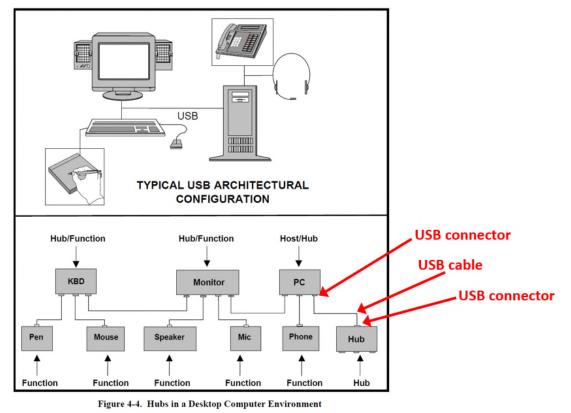

Generally, USB 1.1 instructs that a USB device (*i.e.*, node or function) is plugged into a port on a hub using a cable. USB 1.1 at 23. The cable is connected between a USB connector on a USB device and a USB connector on a host or hub. Baker, ¶ 71.

Figure 4-4 illustrates how hubs provide connectivity in a typical computer environment.

USB 1.1 at 23 (annotated).

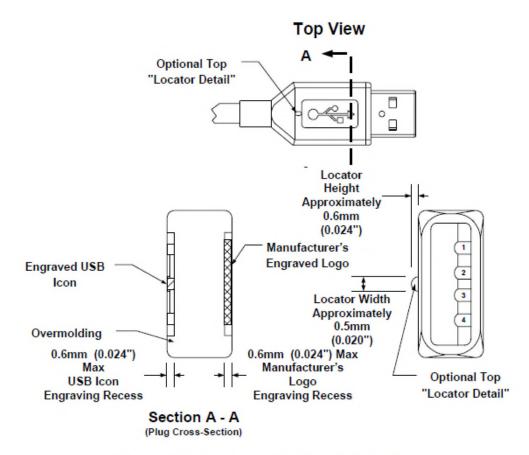

USB 1.1 teaches a POSITA how to implement a USB plug and that a USB connector includes four contacts:  $V_{BUS}$ , D+, D-, and GND:

Figure 6-6. Typical USB Plug Orientation

| Table 0-1         | . USB Connector Terminati | on Assignment                |

|-------------------|---------------------------|------------------------------|

| Contact<br>Number | Signal Name               | Typical Wiring<br>Assignment |

| 1                 | VBUS                      | Red                          |

| 2                 | D-                        | White                        |

| 3                 | D+                        | Green                        |

| 4                 | GND                       | Black                        |

| Shell             | Shield                    | Drain Wire                   |

Table 6-1. USB Connector Termination Assignment

USB 1.1 at 81 and 82; Baker, ¶¶ 72-73.

The USB 1.1 Specification indicates that that the host is responsible for providing power to an attached USB device. USB 1.1 at 24 ("The host is responsible for . . . [p]roviding power to the attached USB devices.") The USB Specification also sets forth conditions and limits for the supply of power on the  $V_{BUS}$  line. Baker, ¶¶ 73-74. The Specification does so in terms of milliamps (mA) of current and in terms of "unit loads." USB 1.1 at 134. "A unit load is defined to be 100mA" of current. *Id.* Notably, the USB Specification includes the following current conditions:

- A "high-power" hub port supplies a minimum of 500mA

- A "low-power" device is supplied with a maximum of 100mA of current

• A "high-power" device is supplied with a maximum of 500 mA of current These conditions/limitations, as well as others, are listed in table 7-5 of the USB 1.1 Specification:

| Parameter                      | Symbol  | Conditions              | Min. | Max. | Units |

|--------------------------------|---------|-------------------------|------|------|-------|

| Supply Voltage:                |         |                         |      |      |       |

| High-power Port                | VBUS    | Note 2, Section 7.2.1   | 4.75 | 5.25 | V     |

| Low-power Port                 | VBUS    | Note 2, Section 7.2.1   | 4.40 | 5.25 | V     |

| Supply Current:                |         |                         |      |      |       |

| High-power Hub Port (out)      | ICCPRT  | Section 7.2.1           | 500  |      | mA    |

| Low-power Hub Port (out)       | ICCUPT  | Section 7.2.1           | 100  |      | mA    |

| High-power Function (in)       | ICCHPF  | Section 7.2.1           |      | 500  | mA    |

| Low-power Function (in)        | ICCLPF  | Section 7.2.1           |      | 100  | mA    |

| Unconfigured Function/Hub (in) | ICCINIT | Section 7.2.1.4         |      | 100  | mA    |

| Suspended High-power Device    | Іссян   | Section 7.2.3 ; Note 15 |      | 2.5  | mA    |

| Suspended Low-power Device     | ICCSL   | Section 7.2.3           |      | 500  | μA    |

**Table 7-5. DC Electrical Characteristics**

USB 1.1 at 142 (annotated).

The USB Specification defines a "high power" port as one that obtains its power externally (e.g., from an outlet). *Id.* at 134 ("Systems that obtain operating power externally, either AC or DC must supply at least five unit loads to each port. Such ports are called high-power ports.") In other words, the USB specification, on its own, acknowledges that certain USB ports (high-powered ports) will supply current in excess of the 500mA limit supplied to a particular USB device (e.g., when the high-power hub port is (1) connected to its own external power sources and (2) connected to a single USB device). *Id.*; Baker, ¶ 74.

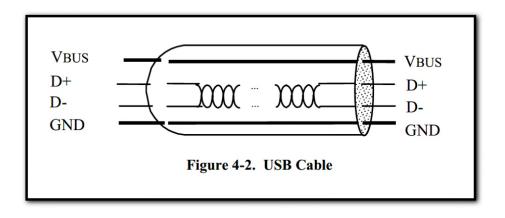

USB 1.1 discloses that an attached device can operate at "full-speed" or "lowspeed." USB 1.1 discloses "The speed of an attached device is determined by the placement of a pull-up resistor on the device (see Section 7.1.5)." USB 1.1 at 251. The specific nature of how D+ and D- are connected is discussed in detail below and in USB 1.1. *See* Baker, ¶¶ 77-83. "Hubs, and the devices to which they connect, use a combination of pull-up and pull-down resistors to control D+ and D- in the absence of their being actively driven. These resistors establish voltage levels used to signal connect and disconnect and maintain the data lines at their idle values when not being actively driven." USB 1.1 at 256.

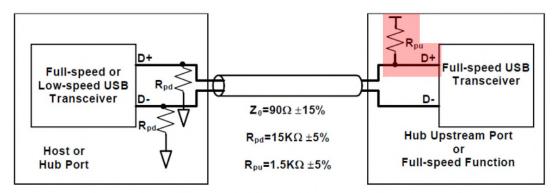

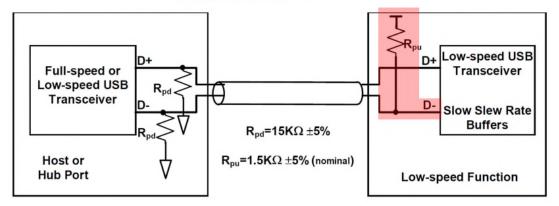

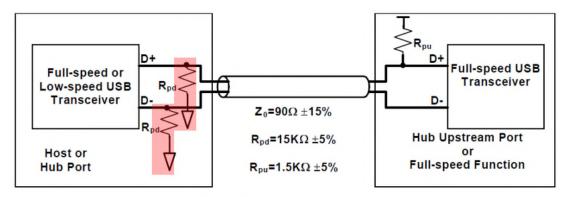

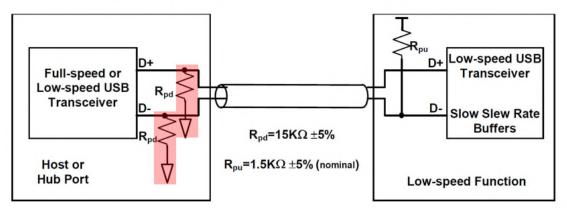

USB 1.1 discloses "Full-speed devices are terminated as shown in Figure 7-10 with the pull-up resistor on the D+ line." and "Low-speed devices are terminated as shown in Figure 7-11 with the pull-up resistor on the D- line." USB 1.1 at 113. These figures are annotated below to show that a pull-up resistor, labeled  $R_{pu}$ , on the D+ line indicates a "full-speed device" while a pull-up resistor, also labeled  $R_{pu}$ , on the D- line indicates a "low-speed device." Baker, ¶ 78.

Figure 7-10. Full-speed Device Cable and Resistor Connections

Figure 7-11. Low-speed Device Cable and Resistor Connections

USB 1.1 at 113 and 114 (annotated).

USB 1.1 also discloses that in the host or hub port "The pull-down terminators on downstream ports are resistors of  $15k\Omega$ +/-5% connected to ground." USB 1.1 at 113. These resistors are annotated below and labeled  $R_{pd}$ .

Figure 7-10. Full-speed Device Cable and Resistor Connections

Figure 7-11. Low-speed Device Cable and Resistor Connections

USB 1.1 at 113 and 114 (annotated); Baker, ¶ 79.

When no pull-up resistor,  $R_{pu}$ , is present on D+ and/or D- the corresponding line is pulled to ground through  $R_{pd}$ . Baker, ¶ 80. If both D+ and D- are at ground then no device is connected to the USB host or hub port. If D+ is pulled high and Dis at ground the connected device operates in full-speed. *Id.* If D+ is at ground and D- is pulled high the connected device operates in low-speed. If D+ and D- are to be used for communications by either full- or low-speed devices then their voltages should never intentionally be pulled high (above 0.8V) at the same time. *Id.* A summary of the relationship between the D+ and D- levels on a USB connector and the port configurations discussed in this section is shown below:

| D+   | D-   | Port configuration  |

|------|------|---------------------|

| Low  | Low  | No device connected |

| High | Low  | Full-speed          |

| Low  | High | Low-speed           |

| High | High | Abnormal condition  |

Baker, ¶ 83. As discussed in more detail below, the High/High signal on the data lines is also referred to in the art as an "SE1" signal. *See* Section VI.C; Baker, ¶ 80. A POSITA would have been aware of the effects of the SE1 signal on the data lines as disclosed by the USB 1.1 Specification. Baker, ¶¶ 80-84. Specifically, a POSITA would have understood that a device receiving this signal would terminate data communications and standby while receiving power across the V<sub>BUS</sub> line. *Id*.

For example, USB 1.1 states "Note: if both D+ and D- are high at this time, the hub may stay in the Disabled state and set the C\_PORT\_ENABLE bit to indicate that the hub could not determine the speed of the device." USB 1.1 at 252. Accordingly, a POSITA would have understood that this signal indicates that the speed of a connected device cannot be determined and thus communications between the host or hub and the connected device are not possible. Baker, ¶ 81.

Moreover, The USB 1.1 further states "After the device has been powered, it must not respond to any bus transactions until it has received a reset from the bus. After receiving a reset, the device is then addressable at the default address." USB 1.1 at 178. In other words, the connected device, after being powered-up through the connection to the USB port though a USB cable, won't process commands until it receives a reset. Baker, ¶ 82. However, if the connected device can't communicate (e.g., because communication has been disable by a High/High signal on the data lines) then the connected device can't receive a reset command and thus can't receive or process commands (to, for example, clear the set C\_PORT\_ENABLE bit which indicates the port speed can't be determined or to power-down). *Id.* Accordingly, the device simply continues to receive power via  $V_{BUS}$  and GND and wait for the reset command (which will not occur with both D+ and D- pulled high). *Id.*

#### **B.** Use of SE1 State in Various Contexts

Persons of ordinary skill in art quickly realized that USB devices could use a High/High signal on the D+ and D- lines for a number of purposes. *See e.g.*, Baker, ¶¶ 80-90. This is particularly the case because the signal is an "abnormal" condition that is outside the normal condition signals used by the Specification and thus will not be misread as being used for a specified purpose in the specification. Baker, ¶ 84. Indeed, of the four states available on a D+ and D- line (low/low, high/low, low/high, and high/high), the SE1 signal was the only state not already accounted for in the specification. Baker, ¶¶ 83-84. Accordingly, as noted below, a number of prior art references disclose using the signal for other purposes.

#### 1. US Patent 6,531,845 ("Kerai") (Ex. 1012)

U.S. Patent 6,531,845 was filed as Application No. 09/864,273 on May 25, 2001, claimed a priority date of May 26, 2000, and issued on March 11, 2003. Thus, Kerai is prior art under at least pre-AIA §102(e).

Kerai used a high state on USB D+ and D- for purpose of charging a system while disabling communications. Kerai, Fig 3, 5:43-51. Specifically, Kerai disclosed "A battery charging circuit . . . in which power is derived from a communications port such as a USB interface (22) and is supplied to a rechargeable battery of a communications device." Ex. 1012, Abstract. In its disclosure, Kerai notes that it was "well known" to pull both D+ and D- high when communications were inactive and that this was helpful for purposes of charging a device. *Id.* at 5:45-48 ("*As is well known*, the data lines of a serial connection (D+ and D- in the USB interface) are held high when the connection is inactive and will vary between a high and low state whilst communication over the ports takes place.") (emphasis added); Baker, ¶ 85.

#### 2. US Patent 6,625,738 ("Shiga") (Ex. 1013)

U.S. Patent 6,625,738 was filed as Application No. 09/454,621 on December 6, 1999, claimed a priority date of December 15, 1998, and issued on September 23, 2003. Thus, Shiga is prior art to the '550 patent under at least pre-AIA §102(e).

27

Shiga recognizes that, the existing USB standards accounted for three (D+, D-) signal line states representing three modes: (1) low-speed mode (D+ signal line is set to a low level ("L") and D- line is set to a high level ("H")); (2) full-speed mode (D+ is high and D- is low); and (3) unconnected mode (both D+ and D- are low). These three states are shown in Shiga's Table 1 seen below. Shiga, 5:38-60; Baker, ¶ 86-87.

| TABLE 1  |                      |               |                      |

|----------|----------------------|---------------|----------------------|

|          | Low Speed            | Full Speed    | Unconnected          |

| D+<br>D- | L (Hi-Z)<br>H (Hi-Z) | H<br>L (Hi-Z) | L (Hi-Z)<br>L (Hi-Z) |

|          |                      |               |                      |

In contrast to these three USB standard modes, Shiga also explains that the "fourth mode" signal, which is when both D+ and D- are in the H level state (an SE1 condition), is "not a USB standard state" and can therefore "be easily distinguished from USB standard data signals." Shiga, 5:60-62, 6:48-58; Baker, ¶ 87. Shiga discloses transmitting this fourth mode signal from a USB apparatus (*e.g.*, keyboard) to a host computer to wake up the computer. Shiga, Abstract, 6:35-47; Baker, ¶ 87. Accordingly, in 1999, using a signal state that is not a USB standard mode (*i.e.*, in which both D+ and D- are in the H state) was well-known. Shiga, 5:60-62; 6:48-50; Baker, ¶ 87.

### 3. US Patent Application Publication US20030135766 ("Zyskowski") (Ex. 1014)

U.S. Patent App. Publication No. 2003/0135766 was filed as Application No. 09/453,656 on December 3, 1999 and issued on July 17, 2003. Thus, Zyskowski is prior art to the '550 patent under at least pre-AIA §102(e).

Zyskowski is another example of prior art that discloses an SE1 condition (with D+ and D- being set at 5 V) being used by a host device (*e.g.*, computer) to signal its full power state to a connected device (*e.g.*, mass storage device, consumer electronic device). Ex. 1014, ¶ 19; Baker, ¶ 88.

### 4. US Patent 6,625,790 ("Casebolt") (Ex. 1015)

U.S. Patent 6,625,790 was filed as Application No. 09/409,683 on October 1, 1999, claimed a priority date of July 8, 1998, and issued on September 23, 2003 to Mark W. Casebolt and Lord Nigel Featherston. Thus, Casebolt is prior art to the '550 patent under at least pre-AIA §102(e).

Casebolt discloses that an SE1 condition could be used as a special signaling mode in which the D+ and D- data lines would be connected to Vcc (+5V) to signal the presence of a PS/2 adapter (a 6-pin connector used in older computer keyboards and mice). Ex. 1015 (Casebolt) at 7:40-54; Baker, ¶ 89. Indeed, the SE1 state for USB is shown in Casebolt's Table 1 below. *Id*.

| I/O<br>State | D+/CLK | D-/DAT | USB                                    | PS/2                        |

|--------------|--------|--------|----------------------------------------|-----------------------------|

| 0            | L      | L      | SEO<br>(Single<br>Ended O)<br>or Reset | Host<br>Inhibit             |

| 1            | L      | н      | J, Idle                                | Host<br>Inhibit             |

| 2            | н      | L      | K, Xmit<br>Resume                      | Host Xmit                   |

| 3            | н      | Н      | SE1<br>(Single<br>Ended 1)             | Idle,<br>Confirm<br>Connect |

TABLE 1

Ex. 1015, Table 1, see also 6:55-7:8.

### 5. Cypress Semiconductor enCoReUSB Datasheet (Ex. 1016)

Knowledge regarding the use of a state in which D+ and D- are both high was so common that Cypress Semiconductor integrated it into its enCoReUSB product in 2000. Ex. 1016 (Cypress enCoReUSB), 24-25; Baker, ¶ 90.

### C. USB 2.0 Specification

The USB 2.0 Specification (USB 2.0) was published on April 27, 2000. Ex. 1011 (USB 2.0). It is prior art to the '550 Patent under at least 35 U.S.C. § 102(a). Moreover, the USB 2.0 Specification would have been part of the knowledge of a POSITA as of the priority date of the '550 Patent. Baker, ¶ 76.

As the USB 2.0 Specification notes, it is fully backwards compatible with devices built with previous versions of the specification, such as USB 1.1. USB 2.0

at 11. The majority of the disclosures of USB 1.1 are also contained in the USB 2.0 Specification. Baker, ¶ 76.

Given the prevalence of the use of the SE1 signal discussed above, the USB 2.0 Specification specifically addresses the SE1 signal. *See e.g.*, USB 2.0 at 123 ("SE1 is a state in which both the D+ and D- lines are at a voltage above  $V_{OSE1}$  (min), which is 0.8 V.") Among other things, the USB 2.0 Specification discloses that the signal should not be used for devices seeking to utilize data communications over the USB connection (either low-speed or full-speed). *Id.* ("Low-speed and full-speed USB drivers must never "intentionally" generate an SE1 on the bus."). As noted above, however, persons of ordinary skill in the art understood that the signal could be used for various purposes, including to disable communications for purposes of charging. Baker, ¶ 80-84.

#### **D.** Overview of Morita

Japanese Patent Application No. 2000-165513A ("Morita"), titled "Charger," was filed on November 30, 1998. Morita is prior art under at least §102(b). A certified translation of Morita is attached here to as Exhibit 1007. Morita was not considered during prosecution.

Morita discloses a charger with the ability to charge a mobile phone and connect the mobile phone to a computer. The charger comprises a "first coupling means for coupling to a mobile phone" and a "second coupling means for coupling

31

to an external device." Ex. 1007 (Morita) at Abstract. Morita discloses that the provided "coupling means" may be USB connections. *Id.* at [Claim 2]. Figure 1 of Morita discloses several of the key components:

Morita at Figure 1 (annotated); Baker, ¶¶ 102-105. As evidenced in Figure 1, the charger of Morita draws power from an outlet (22) to provide to the mobile device through the USB connection (21). *Id.* at column 3 (Embodiment of Invention) (disclosing a "power supply connection unit such as an outlet"); *id.* at [0014] ("A power supply voltage supplied from a power supply source is supplied from the charging control unit 23 to the USB hub control unit 27 and the second USB port 21"). Accordingly, as a POSITA would understand from the USB Specifications, the "first coupling" (21) provided by Morita is a "high powered" USB port that provides a *minimum* of 500mA to the mobile device. Baker, ¶¶ 117-118. Moreover,

unlike the existing high-power hubs discussed by the patentee in the '021 Application, Morita does not disclose any means for automatically terminating charging when the current supplied to the mobile device exceeds "700mA-800mA." Ex. 1008 ('021 Application) at 22; Baker, ¶ 120.

A POSITA would have understood that, although the charger of Morita can be simultaneously connected to an external computer, there will be situations in which no such active device is connected. In such situations the device acts merely as a charger for the phone. Baker,  $\P$  122.

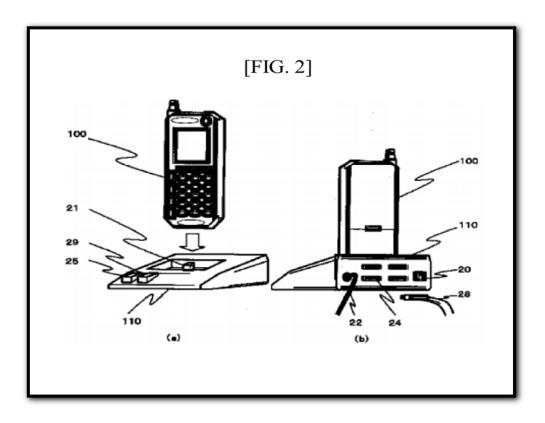

Morita at Figure 2.

#### E. Overview of Dougherty

U.S. Patent No. 7,360,004 ("Dougherty") is titled "Powering a Notebook Across a USB interface." Dougherty's effective filing date is June 30, 2000, which predates even the '550 Patent's earliest claimed priority date of March 1, 2001. Accordingly, Dougherty constitutes prior art to each of the challenged claims under at least pre-AIA 35 U.S.C. § 102(e).

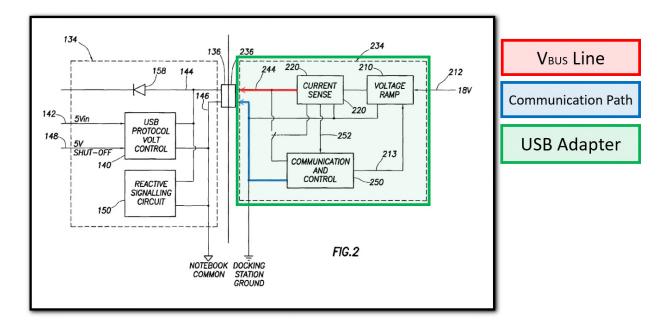

Dougherty discloses a docking station that powers a laptop using a USB connection. Ex. 1006 (Dougherty) at 2:55-58 (disclosing "a laptop computer and related docking station adapted to supply power from the docking station to the laptop computer across the USB connection."); *see id.* at Figure 2. Dougherty refers to the lines in the connection as "USB power rails" and "serial communication conductors." *See e.g., id.* at Abstract ("A laptop computer and mating docking station where the docking station provides power to the laptop computer over the power rails of the Universal Serial Bus (USB) interface.") and 5:26-37; Baker, ¶¶ 109-110. As a POSITA would have recognized by reference to a USB connection, the dock of Daugherty includes a USB V<sub>BUS</sub> line and a USB communication path. Baker, ¶ 108.

Ex. 1006 (Dougherty) at Figure 2 (annotated).

In order to power the laptop, the system of Dougherty disregards a number of the conditions associated with the USB Specification. *See e.g., id.* at 2:55-3:10; *id.* at 6:1 (disclosing that the system "breaks with standard USB protocol"); Baker, ¶¶ 109-110. Among other things, the 5V typically supplied by the output USB connection of the laptop is disengaged and, instead, the port receives power at 18.5 volts from the docking station on that connection. *Id.* at 2:58-64 ("To accomplish this, the laptop computer is modified to have circuitry which is capable of being detected across USB power rails by the docking station and also capable of turning off the five volts typical supplied by the laptop onto the USB port, and instead, receiving power at 18.5 volts, from the docking station across the USB connections."). Baker, ¶¶ 109-110. This means that the dock is supplying power at

its upstream port, which is inconsistent with the USB 1.1 Specification. See e.g., USB 1.1 at 135 ("No device shall supply (source) current on the VBUS at its upstream port at any time."); Baker, ¶ 109.

As a result of this connection, the dock supplies current to the laptop over the USB connection that exceeds the maximum amounts permitted by the USB Specification. Baker, ¶110. Specifically, Dougherty discloses that dock may supply 2.5 amps of current to the laptop. *Id.* at 7:47-51 ("When the dock station 200 provides power for full operation of the laptop computer 100, as many as 2.5 amps of current may flow from the dock station 200 to the laptop computer 100 across the USB connectors 136,236."). As noted above, this is more than five times the maximum amount that a device is to consume/draw under the USB Specification. *See e.g.*, USB 1.1 at 134-134; Baker, ¶110.

Because the dock supplies all the power required by the laptop, no other power adapter is required. Dougherty at 3:4-6 ("Thus, a laptop user need only plug the laptop into the docking station via the USB port, even if the battery for the laptop computer is drained."); Baker, ¶ 110.

#### VII. CLAIM CONSTRUCTION

Claim construction is only necessary to the extent it is required to resolve disputes presented in the Petition. *Nidec Motor Corp. v. Zhongshan Broad Ocean Motor Co. Ltd.*, 868 F.3d 1013, 1017 (Fed. Cir. 2017). Petitioners submit that, other

than the terms addressed below, no terms need to be construed to resolve the issues presented by this Petition and the claims should be afforded their plain and ordinary meaning in view of the '550 Patent's specification and prosecution history, as would have been understood by a POSITA. If Patent Owner attempts to create a claim construction dispute in its preliminary response, Petitioners reserve the right to address the issue in a reply to that preliminary response. If the Patent Owner attempts to create a claim construction issue in its post-institution response, Petitioners will address such issues in their reply.

The Board construes claims in an IPR in accordance with *Phillips v. AWH Corp.*, 415 F.3d 1303, 1312–13 (Fed. Cir. 2005) (*en banc*). 83 Fed. Reg. 51340, 51340-44 (Oct. 11, 2018). Under the *Phillips* standard, "words of a claim are generally given their ordinary and customary meaning." *Phillips*, 415 F.3d at 1312-13 (internal quotations omitted).

### A. "at least one associated condition specified in a USB specification" (claim 1) and "at least one USB Specification imposed limit" (claim10)

The PTAB has already construed each of these phrases. *See ZTE (USA) Inc. et al. v. Fundamental Innovation System International LLC*, IPR2018-00111 at Paper 62 (Final Written Decision) at 7-13. Specifically, the PTAB held that the "at least one associated condition specified in a USB specification" (Claim1) and the "at least one USB Specification imposed limit" must be conditions/limits that affect the supply of current on the  $V_{BUS}$  line. *Id*.

In adopting this construction, the PTAB adopted patent owner's argument that there were a number of current-related conditions/limits set forth in the USB Specification, including, for example, the amount of the current, the direction of the current flow, and the time limit for providing current. Id. at 10 ("Patent Owner persuasively demonstrates, however, that the USB specification specifies multiple conditions that are associated with the supply of current on the V<sub>BUS</sub> line, including 'a current limit,' a condition on the 'current flow direction,' and a time limit for providing current."); see IPR2018-00111, Exhibit 2011 (Fernald Declaration) at 48-51. Patent owner explained, for example, that engaging in the "enumeration" process prior to supplying more than the 100 mA minimum amount of current over the interface was a condition that could satisfy this limitation. IPR2018-00111, Exhibit 2011 (Fernald Declaration) at ¶ 50 ("A POSA would understand that the condition that a USB device must participate in enumeration before drawing '5 unit loads' is an 'associated condition' to supplying current on the  $V_{BUS}$  line . . . .").

Accordingly, for purposes of this IPR Proceeding, Petitioner adopts the Board's prior construction which encompasses conditions/limitations related the supply of current, including at least: the amount of current supplied, the amount of current supplied prior to enumeration, and the direction in which current is supplied.

#### **B.** "abnormal data condition" (claims 4, 6, 7, 13, 15, and 16)

In previous litigations, Patent Owner has contended that the phrase "abnormal data condition" in claims 4, 6, 7, 13, 15 and 16 should be construed as "condition detected at the USB communication path that is not defined as a valid (or legal) data condition by the USB specification." Ex. 1023. For the limited and sole purpose of this IPR proceeding only, Petitioner adopts Patent Owner's proposal for the construction of this claim phrase. *Id.; Toyota Motor Corp.*, IPR2016-00422, \*26.

#### VIII. ANALYSIS

### A. Morita In View Of Knowledge of a POSITA Renders The Subject Matter Of Claims 1-18 Obvious.

As noted above and herein, Morita expressly discloses a mobile device charger that provides a USB port for charging the mobile device. *See e.g.*, Ex. 1007 (Morita) at [Claim 1], [Claim 2], [0010]-[0011], and [0016]. As also discussed above, a POSITA would have been aware of the USB Specifications that existed as of the priority date of the '550 Patent. This includes the USB 1.1 and USB 2.0 Specifications. *See* Section IV.C; Baker, ¶ 68.

### 1. Claim 1

### a. 1[a]. An adapter comprising

To the extent the preamble of claim 1 is limiting, it is disclosed by Morita. Baker, ¶¶ 111-112. Morita discloses a charger with a USB port for charging a mobile phone. *E.g.*, Morita at Claim 1 ("A charger capable of charging a mobile phone . . . comprising: first coupling means for coupling to a mobile phone") and Claim 2 ("The charger according to claim 1, wherein the first coupling means . . . are configured from a USB format."); *id.* at [0016] ("In FIG. 2, the mobile videophone device 100 is connected to the USB port 21 of the charger 110. . ."); *see also id.* at [0010]-[0011]. A POSITA would have understood Morita's charger 110 to be a "an adapter." Baker, ¶¶ 111-112.