U.S. Patent No. 6,651,134 Petition for *Inter Partes* Review

#### UNITED STATES PATENT AND TRADEMARK OFFICE

#### **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

ADVANCED MICRO DEVICES, INC., Petitioner

v.

MONTEREY RESEARCH, LLC, Patent Owner.

#### PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 6,651,134

## **TABLE OF CONTENTS**

# **TABLE OF CONTENTS**

| I.    | INTRODUCTION                            |                                                                                                                |    |  |

|-------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|----|--|

| II.   | MANDATORY NOTICES UNDER 37 C.F.R. §42.8 |                                                                                                                |    |  |

| III.  | FEE AUTHORIZATION                       |                                                                                                                |    |  |

| IV.   | GRO                                     | GROUNDS FOR STANDING4                                                                                          |    |  |

| V.    | PREC                                    | CISE RELIEF REQUESTED                                                                                          | 4  |  |

| VI.   | THE                                     | CHALLENGED PATENT                                                                                              | 6  |  |

| VII.  | PATENT PROSECUTION HISTORY              |                                                                                                                |    |  |

| VIII. | LEVEL OF ORDINARY SKILL IN THE ART11    |                                                                                                                |    |  |

| IX.   | CLAI                                    | M CONSTRUCTION                                                                                                 | 11 |  |

|       | A.                                      | "non-interruptible" (claims 1, 16, 17)                                                                         | 12 |  |

|       | В.                                      | "means for reading data / means for generating a predetermined number of said internal address signals" (claim | 10 |  |

|       | C                                       | 16)                                                                                                            |    |  |

|       | C.                                      | "external address signal" (claims 1, 13, 15-17) "burst" (claim 2)                                              |    |  |

|       | D.                                      |                                                                                                                |    |  |

|       | E.                                      | "internal address signal" (claims 1, 2, 12, 15-17)                                                             |    |  |

|       | F.                                      | "logic circuit" (claims 1, 12)                                                                                 | 16 |  |

|       | G.                                      | "predetermined number of [said] internal address signals"<br>(claims 1-4, 12, 15-17)                           | 16 |  |

|       | H.                                      | "memory" (claims 1, 8-9, 14, 17)                                                                               | 17 |  |

|       | I.                                      | "address signal" (claims 1-4, 10-13, 16-17)                                                                    |    |  |

| X.    | SPECIFIC EXPLANATION OF GROUNDS         |                                                                                                                |    |  |

|       | A.                                      | Ground 1: Claims 1-3, 8, 12-13, 16, and 17 are anticipated by US 6,115,280 ("Wada")                            | 17 |  |

|       |                                         | 1. Wada                                                                                                        | 17 |  |

## TABLE OF CONTENTS (continued)

|    | 2.                                                                                                                                                  | Independent Claim 1                                                                                                                                    | 24 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 3.                                                                                                                                                  | Dependent Claim 2                                                                                                                                      | 30 |

|    | 4.                                                                                                                                                  | Dependent Claim 3                                                                                                                                      | 32 |

|    | 5.                                                                                                                                                  | Dependent Claim 8                                                                                                                                      | 33 |

|    | 6.                                                                                                                                                  | Dependent Claim 12                                                                                                                                     | 34 |

|    | 7.                                                                                                                                                  | Dependent Claim 13                                                                                                                                     | 36 |

|    | 8.                                                                                                                                                  | Independent Claim 16                                                                                                                                   | 39 |

|    | 9.                                                                                                                                                  | Independent Claim 17                                                                                                                                   | 46 |

| B. |                                                                                                                                                     | nd 2: Claims 1-4, 8, 12-14, 16, and 17 are obvious over<br>a in view of the knowledge of a POSITA                                                      | 47 |

|    | 1.                                                                                                                                                  | Independent Claims 1 and 16                                                                                                                            | 47 |

|    | 2.                                                                                                                                                  | Dependent Claims 2-3, 8, 12-13, and 17                                                                                                                 | 48 |

|    | 3.                                                                                                                                                  | Dependent Claim 4                                                                                                                                      | 48 |

|    | 4.                                                                                                                                                  | Dependent Claim 14                                                                                                                                     | 49 |

| C. | obvio                                                                                                                                               | nd 2a: Claims 1-4, 8, 12-14, 16, and 17 are rendered<br>ous by the combination of Wada and US 5,584,033<br>rett") in view of the knowledge of a POSITA | 50 |

|    | 1.                                                                                                                                                  | Barrett                                                                                                                                                | 50 |

|    | 2.                                                                                                                                                  | Claims 1-4, 8, 12-14, 16, and 17                                                                                                                       | 53 |

| D. | Ground 3: Claims 4-7, and 18-20 are rendered obvious by the combination of Wada and U.S. 6,185,149 ("Fujioka") in view of the knowledge of a POSITA |                                                                                                                                                        |    |

|    | 1.                                                                                                                                                  | Fujioka                                                                                                                                                |    |

|    | 2.                                                                                                                                                  | Dependent Claim 4                                                                                                                                      |    |

|    | 3.                                                                                                                                                  | Dependent Claim 5                                                                                                                                      |    |

|    | 4.                                                                                                                                                  | Dependent Claim 6                                                                                                                                      |    |

|    | 5.                                                                                                                                                  | Dependent Claim 7                                                                                                                                      |    |

|    | 6.                                                                                                                                                  | Dependent Claim 18                                                                                                                                     |    |

# TABLE OF CONTENTS (continued)

|     | 7.                                                                                                                                                              | Dependent Claim 19                                                                                                                                              | 59 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 8.                                                                                                                                                              | Dependent Claim 20                                                                                                                                              | 60 |

| E.  | comb                                                                                                                                                            | nd 3a: Claims 4-7, and 18-20 are rendered obvious by the<br>bination of Wada, Barrett, and Fujioka in view of the<br>bledge of a POSITA.                        | 60 |

| F.  | comb                                                                                                                                                            | nd 4: Claims 9-10, 14, and 21 are rendered obvious by the bination of Wada and US 6,226,755 ("Reeves") in view of nowledge of a POSITA                          | 60 |

|     | 1.                                                                                                                                                              | Reeves                                                                                                                                                          | 60 |

|     | 2.                                                                                                                                                              | Dependent Claim 9                                                                                                                                               | 63 |

|     | 3.                                                                                                                                                              | Dependent Claim 10                                                                                                                                              | 63 |

|     | 4.                                                                                                                                                              | Dependent Claim 14                                                                                                                                              | 64 |

|     | 5.                                                                                                                                                              | Dependent Claim 21                                                                                                                                              | 65 |

| G.  | the co                                                                                                                                                          | nd 4a: Claims 9-10, 14, and 21 are rendered obvious by<br>ombination of Wada, Barrett, and Reeves in view of the<br>rledge of one of ordinary skill in the art  | 65 |

| H.  | comb                                                                                                                                                            | nd 5: Claims 11 and 15 are rendered obvious by the<br>bination of Wada and US 5,784,331 ("Lysinger") in view<br>e knowledge of one of ordinary skill in the art | 65 |

|     | 1.                                                                                                                                                              | Lysinger                                                                                                                                                        | 65 |

|     | 2.                                                                                                                                                              | Dependent Claim 11                                                                                                                                              | 69 |

|     | 3.                                                                                                                                                              | Dependent Claim 15                                                                                                                                              | 69 |

| I.  | Ground 5a: Claims 11 and 15 are rendered obvious by the combination of Wada, Barrett, and Lysinger in view of the knowledge of one of ordinary skill in the art |                                                                                                                                                                 |    |

| CON | CLUS                                                                                                                                                            | ION                                                                                                                                                             | 72 |

XI.

# LIST OF EXHIBITS

| Ex-1001 | U.S. Patent No. 6,651,134                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------|

| Ex-1002 | Declaration of Dr. R. Jacob Baker                                                                                       |

| Ex-1003 | Curriculum Vitae of Dr. R. Jacob Baker                                                                                  |

| Ex-1004 | Prosecution History of U.S. Patent No. 6,651,134                                                                        |

| Ex-1005 | U.S. Patent No. 6,115,280 ("Wada")                                                                                      |

| Ex-1006 | U.S. Patent No. 6,185,149 ("Fujioka")                                                                                   |

| Ex-1007 | U.S. Patent No. 5,900,021 ("Tiede")                                                                                     |

| Ex-1008 | U.S. Patent No. 6,226,755 ("Reeves")                                                                                    |

| Ex-1009 | U.S. Patent No. 5,748,331 ("Lysinger")                                                                                  |

| Ex-1010 | U.S. Patent No. 5,584,033 ("Barrett")                                                                                   |

| Ex-1011 | Order 29 Construing Claims, Inv. No. 337-TA-792, U.S.I.T.C<br>(February 9, 2012)                                        |

| Ex-1012 | Order Construing Claims, Cypress Semiconductor Corp. v. GSU<br>Tech., Inc., 13-cv-02013-JST (N.D. Cal.) (July 29, 2014) |

| Ex-1013 | Commission Opinion, Inv. No. 337-TA-792, U.S.I.T.C. (June 28, 2013)                                                     |

| Ex-1014 | U.S. Patent No. 5,360,992 ("Lowrey")                                                                                    |

#### I. INTRODUCTION

Advanced Micro Devices, Inc. ("Petitioner") requests *inter partes* review ("IPR") of Claims 1-21 of U.S. Patent No. 6,651,134 ("the '134 Patent") (Ex-1001), currently assigned to Monterey Research, LLC ("Patent Owner").

The '134 Patent discloses neither a new memory circuit design, a new memory addressing technique, nor a new data transfer technique. Indeed, the patent admits that conventional memories can be accessed in both single address mode and in "burst" mode, wherein multiple data locations are accessed in response to a single initial address. Ex-1001 at 1:14-16. The claims of the '134 Patent merely combine techniques and memory architectures already well known in the art.

The claimed improvement of the '134 Patent is to read and write data from a memory using a burst of internal address signals wherein the generation of internal address signals is "non-interruptible." Specifically, the '134 Patent notes that while conventional systems employing static random access memory (SRAM) can operate in a burst mode that can be started and stopped in response to a control signal (*Id.* at 1:16-18), conventional systems employing dynamic random access memory (DRAM) are required to periodically interrupt burst transfers in order to refresh the charge on the memory cells, which slowly leaks away. *Id.* at 1:19-24. Nevertheless, the claims of the '134 Patent are written to encompass not only

DRAM systems, configured to hide refresh cycles behind burst reads of other memory partitions, but also SRAM systems, which do not need to be interrupted because they do not require refresh. *Compare, e.g.*, claims 1, 8, and 9. So it is not surprising that the claims were rejected multiple times during prosecution over prior art disclosing generating internal addresses in a continuous burst. The applicant finally overcame those rejections after filing an appeal brief and arguing that while the primary prior art reference did disclose continuous burst transfers using internally generated addresses, it also disclosed that there was a way for a burst to be terminated, so it was not non-interruptible. *See, e.g.*, Ex-1004 (File History) at 115.

Prior art presented in this Petition, which was not considered during prosecution, teaches an apparatus and method for generating a predetermined number of internal address signals for reading from and writing to memory wherein the burst of internal address signals is non-interruptible. The primary reference, Wada, anticipates the independent claims, disclosing memory burst transfers that are not interrupted. Nevertheless, because of the patentee's narrowing arguments during prosecution, Petitioners also present the combination of Wada and Barrett, which expressly teaches bursts that are non-interruptible. Thus, for the reasons set forth in this Petition, Claims 1-21 of the '134 Patent are unpatentable. These grounds are likely to prevail, and this Petition should be

granted and the challenged claims cancelled.

#### II. MANDATORY NOTICES UNDER 37 C.F.R. §42.8

<u>**Real Parties-in-Interest</u>**: Petitioner Advanced Micro Devices, Inc. and ATI Technologies ULC are the real parties-in-interest. ATI Technologies ULC is an indirect, wholly owned subsidiary of Advanced Micro Devices, Inc.</u>

#### **Related Matters**:

- Patent Owner has asserted the '134 Patent against Petitioner in Monterey Research, LLC v. Advanced Micro Devices, Inc., No. 1:19cv-02149-CFC (D. Del.).

- The '134 Patent was previously asserted in the International Trade Commission in *In the Matter of Certain Static Random Access Memories and Products Containing the Same*, Inv. No. 337-TA-792 (U.S.I.T.C., hereinafter the "792 Investigation") and in District Court in *Cypress Semiconductor Corp. v. GSI Tech., Inc.*, No. 13-cv-02013-JST (N.D. Cal).

#### Lead and Back-Up Counsel:

Lead Counsel: Ryan K. Yagura (Reg. No. 47,191), O'Melveny & Myers LLP, 400 S. Hope Street, Los Angeles, CA 90071. (Telephone: 213-430-6000; Fax: 213-430-6407; Email:

ryagura@omm.com)

Backup Counsel: Nicholas J. Whilt (Reg. No. 72,081), Vincent Zhou (Reg. No. 63,366), Brian M. Cook (Reg. No. 59,356), O'Melveny & Myers LLP, 400 S. Hope Street, Los Angeles, CA 90071. (Telephone: 213-430-6000; Fax: 213-430-6407; Email:

nwhilt@omm.com, vzhou@omm.com, bcook@omm.com)

<u>Service Information</u>: Petitioner consents to electronic service by email to <u>OMMAMDMONTEREY@omm.com</u>. Please address all postal and hand-delivery correspondence to lead counsel at O'Melveny & Myers LLP, 400 S. Hope Street, Los Angeles, CA 90071, with courtesy copies to the email address identified above.

#### **III. FEE AUTHORIZATION**

Pursuant to 37 C.F.R. §42.15(a) and §42.103(a), the PTO is authorized to charge \$34,400 (or other fees required for this filing) to Deposit Account No. 50-0639.

#### **IV. GROUNDS FOR STANDING**

Under 37 C.F.R. §42.102(a)(2), §42.104(a), Petitioner certifies that the '134 Patent is available for IPR, this Petition is timely filed, and Petitioner is not barred or estopped from requesting IPR review on the grounds presented.

#### V. PRECISE RELIEF REQUESTED

Petitioner respectfully requests review and cancellation of all 21 claims of

the '134 Patent under 35 U.S.C. §102 and/or §103 based on the following grounds:

**Ground 1:** Claims 1-3, 8, 12-13, 16, and 17 are anticipated by US 6,115,280 ("Wada");

**Ground 2:** Claims 1-4, 8, 12-14, 16, and 17 are rendered obvious by Wada in view of the knowledge of a person of ordinary skill in the art ("POSITA");

**Ground 2a:** Claims 1-4, 8, 12-14, 16, and 17 are rendered obvious by Wada and US 5,584,033 ("Barrett") in view of the knowledge of a POSITA;

**Ground 3:** Claims 4-7, and 18-20 are rendered obvious by Wada and U.S. 6,185,149 ("Fujioka") in view of the knowledge of a POSITA.

**Ground 3a:** Claims 4-7, and 18-20 are rendered obvious by Wada, Barrett, and Fujioka in view of the knowledge of a POSITA

**Ground 4:** Claims 9-10, 14, and 21 are rendered obvious by Wada and US 6,226,755 ("Reeves") in view of the knowledge of a POSITA;

**Ground 4a:** Claims 9-10, 14, and 21 are rendered obvious by Wada, Barrett, and Reeves in view of the knowledge of a POSITA;

**Ground 5:** Claims 11 and 15 are rendered obvious by Wada and US 5,784,331 ("Lysinger") in view of the knowledge of a POSITA; and

**Ground 5a:** Claims 11 and 15 are rendered obvious by Wada, Barrett, and Lysinger in view of the knowledge of one a POSITA.

None of the references relied upon in this Petition was cited by the Examiner

during prosecution of the '134 Patent. Ex-1001, 1.

#### VI. THE CHALLENGED PATENT

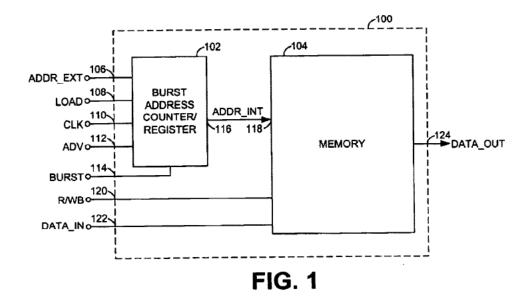

The '134 Patent is directed to a system and method for addressing a memory circuit with a burst of internal address signals that may be non-interruptible. Ex. 1001 at Abstract. A device reads data from memory by asserting an address and receiving data from the memory location specified by that address. In "burst" mode, however, a controller asserts a single address, and memory circuit logic generates a series of internal addresses, typically offset from the initial address as address+0, address+1, address+2, etc., and returns data from multiple memory locations specified by those internal addresses in response to one external addresses. Ex-1002 ¶35.

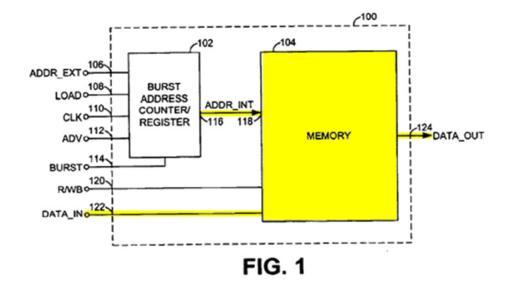

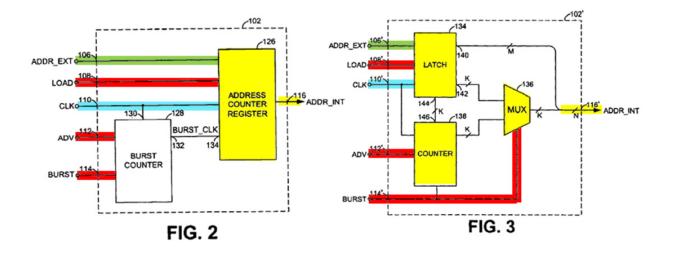

An embodiment of the alleged invention is "configured to transfer a fixed number of words of data with each access (e.g., read or write)." Ex-1001 at 2:28-30. An array of memory cells may be addressed by a "burst address counter" circuit that receives an external address (ADDR\_EXT), a clock (CLK), and control signals (*e.g.*, LOAD, ADV) and that outputs a burst of internal addresses ADDR\_INT that access the memory cells. *See id.* at 2:31-46. Figure 1, for example, depicts "Burst Address Counter / Register" 102, which latches in external address ADDR\_EXT when the LOAD signal is asserted. *Id.* at 3:14-19. When ADV is asserted, a fixed number of internal addresses (ADDR\_INT) are generated in response to the CLK signal. *Id.* at 3:19-24. "Once the circuit 102 has started generating the fixed number of addresses, the circuit 102 will generally not stop until the fixed number of addresses has been generated (*e.g.*, a non-interruptible burst)." *Id.* at 3:25-29.

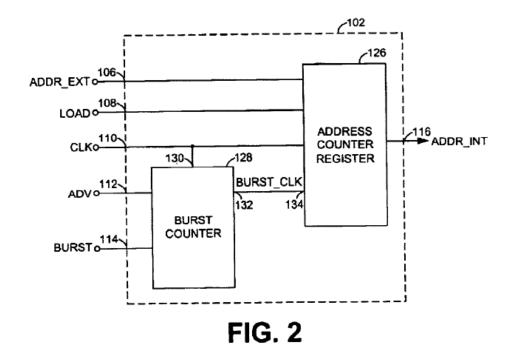

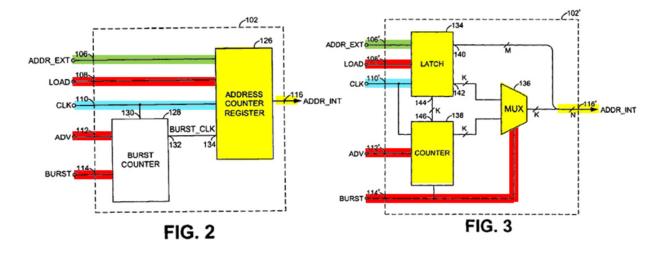

The '134 Patent discloses two embodiments of the "Burst Address Counter" 102, depicted in Figures 2 and 3. In Fig. 2, below, an initial address (ADDR\_EXT) is latched into the address counter register 126 when LOAD is asserted. *Id.* at 4:6-8. When ADV is asserted, the BURST\_CLK signal is generated in response to CLK and increments the address in the address counter register 126 to produce a predetermined number of internal address values ADDR\_INT (116). *Id.* at 4:6-14.

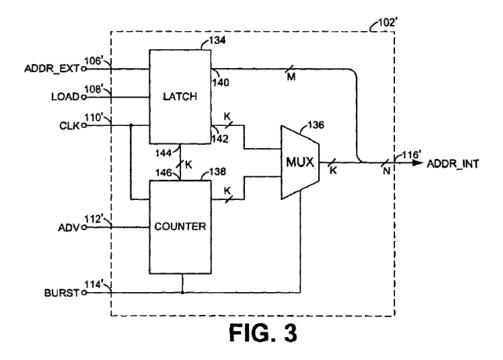

In Figure 3, an n-bit external address (ADDR\_EXT) is divided into an m-bit portion and a k-bit portion. *Id.* at 4:18-25. The k-bit portion is sent to counter (138) and is incremented by the CLK signal when ADV is asserted. *Id.* at 4:28-33. A multiplexer (136) selects either the latched k-bit portion of the external address (142) or the k-bit output of the counter (138) and concatenates it with the latched m-bit portion of the address to create the internal addresses (ADDR\_INT) that are used to address the memory array. *Id.* at 4:34-39; Ex-1002 ¶¶35-38

#### VII. PATENT PROSECUTION HISTORY

The application that became the '134 Patent was repeatedly rejected during prosecution and eventually allowed after the Examiner did not file a response to the applicant's appeal brief.

On 10/1/2001, the Examiner rejected the 17 pending claims, rejecting dependent claims 6 and 15 (which recite that the burst length is programmed by "bond options") under 35 U.S.C. §112 paragraph 1 because the specification did not sufficiently support that concept. Ex. 1004 (File History) at 42. All claims were also rejected as anticipated by Yip (U.S. 6,289,138). *Id.* at 42-44. The applicant responded on 2/4/2002, and with respect to the Section 112 rejections, stated:

Support for claims 5 and 15 may be found on page 8, lines 3-8 of the specification. Furthermore, bond options are well known in the art and, therefore, one skilled in the art would understand how to make and/or use bond options. Copies of U.S. patents 6,188,636 (issued February 13, 2001), 5,900,021 (issued May 4, 1999) and 5,360,992 (issued November 1, 1994) from the USPTO web site (www.uspto.gov) are attached as evidence of bond options being well known in the art.

*Id.* at 62. Regarding the 102 rejections, the applicant argued that Yip did not disclose "the generation of a predetermined number of internal address signals that is non-interruptible, as presently claimed." *Id.* at 63. Specifically, the patentee argued that Yip discloses a write burst "can be interrupted when there is a cycle request from a higher priority port..." *Id.* at 64. The applicant added three additional claims.

On 4/25/2002, the Examiner rejected claims 1-20 as anticipated by Cowles (US 5,729,504). *Id.* at 70-73. The applicant responded on 6/26/2002, arguing the internal address bursts were not non-interruptible, and added an additional claim. *Id.* at 83. The applicant asserted that "Cowles teaches that a low to high transition of the WE\* signal within a burst write access to the memory array 112 will *terminate* the burst access, preventing further writes from occurring . . . ." *Id.* at 84 (emphasis original).

On 10/22/2002, the Examiner repeated and made final the Cowles rejection. *Id.* at 89. In response, the applicant argued that Cowles did not teach that the burst memory accesses were non-interruptible. *Id.* at 115. The Examiner rejected those

arguments in an Advisory action, and the applicant appealed, raising the same arguments on appeal. *Id.* at 14-16. The Examiner filed no responsive brief but instead issued a Notice of Allowance, conceding that Cowles disclosed "to terminate a continuous burst read operation, the WE signal merely has to transition high prior to a falling edge of the CAS signal (see, for example, Cowles). [T]hus prior art of record does not teach or fairly suggest the <u>non-interruptible</u> generation of a predetermined number of internal address signals." *Id.* at 172 (emphasis original); Ex-1002 ¶¶39-42.

#### VIII. LEVEL OF ORDINARY SKILL IN THE ART

At the time the '134 Patent was filed, a person of ordinary skill in the art would have had a bachelor's degree in electrical or computer engineering, applied physics, or a related field, and at least two years of experience in design, development, and/or testing of memory circuits, related hardware design, or the equivalent, with additional education substituting for experience and vice versa. Ex-1002 ¶43.

#### IX. CLAIM CONSTRUCTION

Petitioner interprets the '134 Patent's claims according to *Phillips*. 83 Fed. Reg. 51340, 51340-44 (Oct. 11, 2018); *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005). Certain terms of the '134 Patent were previously construed in the 792 Investigation (Order No. 29, Feb. 9, 2012) and in *Cypress Semiconductor*

*Corp. v. GSI Tech., Inc.*, No. 13-cv-02013-JST (N.D. Cal July 29, 2014), attached hereto as Exhibits Ex-1011 and Ex-1012, respectively. The construction of the following claim terms may be relevant to this proceeding.

#### A. "non-interruptible" (claims 1, 16, 17)

The '134 Patent specification defines "non-interruptible" as follows:

Once the circuit 102 has started generating the fixed number of addresses, the circuit 102 *will generally not stop* until the fixed number of addresses has been generated (e.g., *a non-interruptible burst*).

Ex. 1001 ('134 Patent) at 3:3:36-28.<sup>1</sup> During prosecution, however, the applicant distinguished prior art disclosing a *generally continuous* address burst, arguing that any disclosure describing the possibility of terminating a burst rendered that burst not "non-interruptible," as was discussed above in the summary of the file history, suggesting a narrower construction. In the 792 Investigation, the parties agreed that "non-interruptible" means "cannot be stopped or terminated once initiated until the fixed number of internal addresses has been generated." Ex-1011 at 12-13.

Nevertheless, the Board need not resolve that issue here, as the prior art applied to the claims discloses this limitation under the narrower construction (cannot be stopped). Ex-1002  $\P$ 44-46.

<sup>&</sup>lt;sup>1</sup> Emphasis is added unless stated otherwise.

# B. "means for reading data . . . / means for generating a predetermined number of said internal address signals" (claim 16)

During prosecution, the applicant agreed that claim 16 (then claim 12) should be construed as means-plus-function under pre-AIA 35 U.S.C. §112(6), although the applicant did not identify the claimed function or corresponding structure. Ex. 1004 (File History) at 129, 131, 146, 167. Claim 16 includes two "means" clauses: (a) "means for reading data from and writing data to a plurality of storage elements in response to a plurality of internal address signals," and (b) "means for generating a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal, and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible."

The function recited in element (a) is "reading data from and writing data to a plurality of storage elements in response to a plurality of internal address signals." The corresponding disclosed structure is the memory array 104 depicted in Figure 1 (annotated below) and described as "a static random access memory (SRAM), a dynamic random access memory (DRAM), or other appropriate memory to meet the design criteria of a particular implementation." Ex. 1001 ('134 Patent) at 2:34-38. The memory array 104 includes an address input 118 that receives a plurality of internal address signals, and a DATA OUT line 124, and a

DATA\_IN line 122 for reading data from and writing data to the memory. *Id.* at 2:44-29.

The function in element (b) is "generating a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal, and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible." The corresponding structure is the "burst address counter/register 102" implemented either as shown in (1) Figure 2, described at 3:62-4:14 or (2) Figure 3, described at 4:15-39, or their equivalents. In annotated Figures 2 and 3 below, the logic blocks highlighted in yellow generate a predetermined number of internal address signals (ADDR INT) in response to (i) an external address signal (green) (ii) a clock signal (blue) and (iii) one or more control signals (red). While Figure 2 uses a counter that increments the entire n-bit address, Figure 3 splits the address into two parts and increments only the bottom k bits, concatenating them with the m top bits to generate the n-bit internal address signals. Ex-1002 ¶¶47-49.

#### C. "external address signal" (claims 1, 13, 15-17)

In the 792 Investigation, the parties agreed that "external address signal" means "an address signal that originates outside of the circuit." Ex-1011 at 12. Petitioner applies the prior art here consistent with that construction. Ex-1002 ¶50.

#### D. "burst" (claim 2)

In the 792 Investigation, the parties agreed that "burst" means "a number of words transferred as a group." Ex-1011 at 13. Petitioner applies the prior art here consistent with that construction. Ex-1002 ¶51.

#### E. "internal address signal" (claims 1, 2, 12, 15-17)

In the 792 Investigation, the ALJ construed this term to mean "an address signal that is generated within the circuit claimed by the preamble." *Id.* at 15. The order was referring to claim 1, in which the preamble reads "a circuit comprising." Thus, the "internal address signal" is generated within the circuit, as opposed to arriving from outside. Petitioner applies the prior art here consistent with that

construction. Ex-1002 ¶53.

#### F. "logic circuit" (claims 1, 12)

In the 792 Investigation, the ALJ construed this term to mean "a circuit that is designed to perform one or more logic operations or to represent logic functions." Petitioner applies the prior art here consistent with that construction. Ex-1002 ¶53.

#### G. "predetermined number of [said] internal address signals" (claims 1-4, 12, 15-17)

In the 792 Investigation, the ALJ construed this term to mean "a fixed number of internal address signals for a burst access." The Commission later affirmed a narrower reading by the ALJ, finding that a prior-art reference fixing the burst length before a data transfer by using a mode register did not disclose a "predetermined number" because it could be programmed. Ex-1013 at 24-25. This implied construction appears overly narrow, given that dependent claim 5 requires that "the fixed burst length is programmable." The ITC's construction limits the claims to programming at manufacture time, such as by bond options or voltage levels (*see* claims 6 and 7). However, the Board need not resolve this issue, as Petitioner relies on prior art disclosing "predetermined number" under the narrower interpretation adopted by the ITC (fixed or programmable at manufacture time using bond options or voltage levels). Ex-1002 ¶54.

#### H. "memory" (claims 1, 8-9, 14, 17)

In the *Cypress* District Court litigation, this term was construed to mean "addressable storage." Ex-1012 at 3, 8. Petitioner applies the prior art here consistent with that construction. Ex-1002 ¶55.

#### I. "address signal" (claims 1-4, 10-13, 16-17)

In the *Cypress* District Court litigation, this term was construed to mean "a signal for determining the address location in the memory array from which data is read to [*sic*] or to which data is written." Ex-1012 at 4, 8. Petitioner applies the prior art here consistent with that construction. Ex-1002 ¶56.

#### X. SPECIFIC EXPLANATION OF GROUNDS

# A. Ground 1: Claims 1-3, 8, 12-13, 16, and 17 are anticipated by US 6,115,280 ("Wada")

#### 1. Wada

Wada was filed April 4, 1997 and issued September 5, 2000, qualifying as prior art under at least pre-AIA 35 U.S.C. §102(e). Ex-1005 (Wada) at 1.

Wada is entitled "Semiconductor memory capable of burst operation." *Id.* at 1. Wada discloses numerous embodiments of "a semiconductor memory operating in burst mode" comprising "a semiconductor memory comprising a memory cell array, a plurality of output registers, an output register selecting circuit, a counter circuit, a data output pin, and an output data transfer circuit." *Id.* at 5:67, 6:14-17. "This makes it possible to output a plurality of target data items in burst mode

#### without interruption therebetween." Id. at 6:59-61.

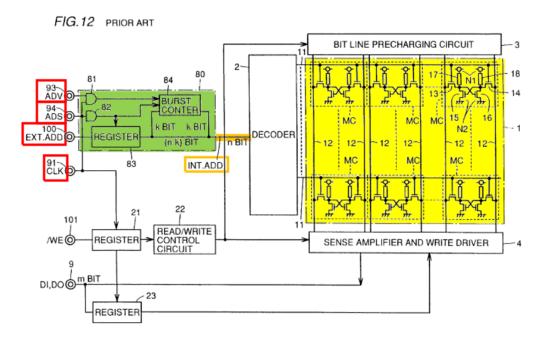

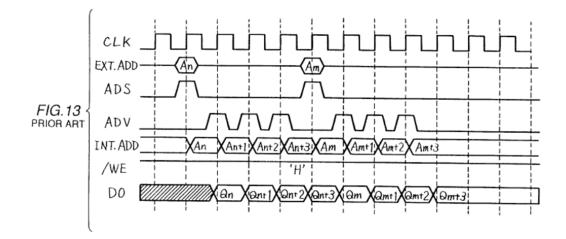

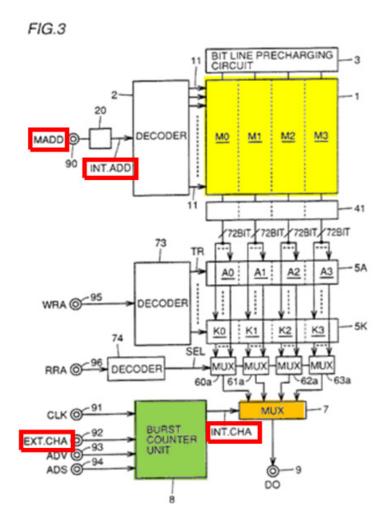

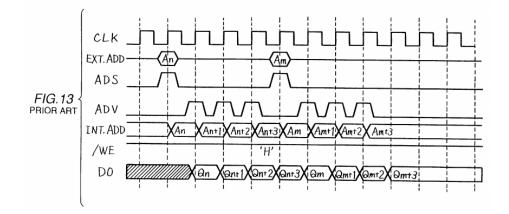

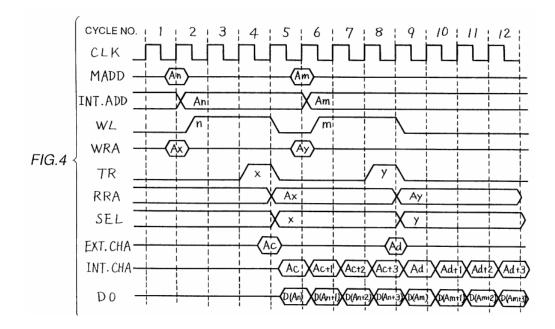

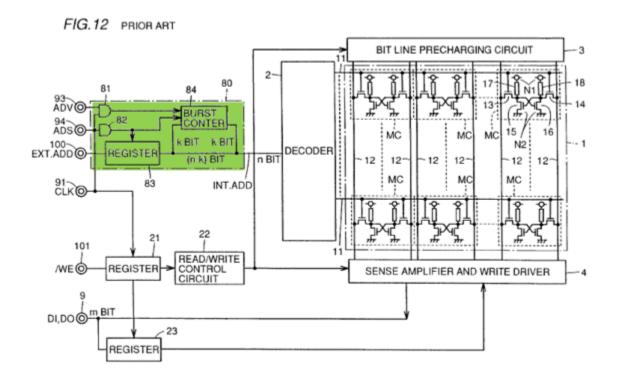

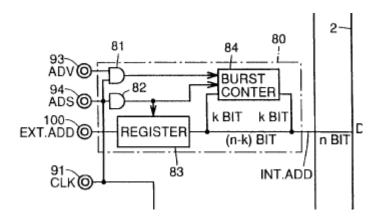

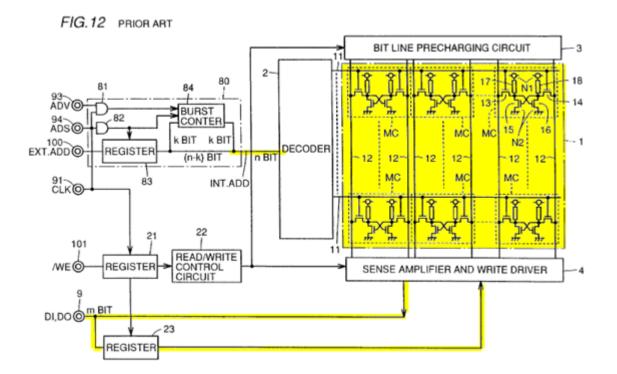

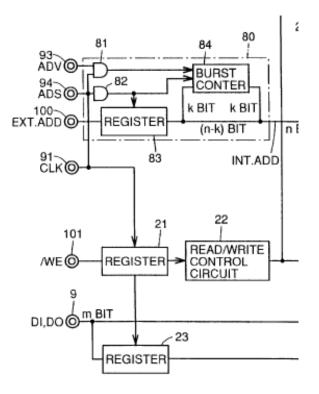

Wada discloses "a typical conventional SRAM operating in burst mode." Id. at 1:22-23; Figs. 12-14. Figure 12 (annotated below) includes a "memory cell array 1" with a "plurality of memory cells" (yellow) (*id.* at 1:28-32), addressed by an internal address signal INT.ADD (orange). Id. at 2:58-61. The internal address signals are generated by a "burst counter unit 80" (green) that latches in an external address (EXT.ADD 100) (id. at 2:16-17) and increments the lower k bits in a burst counter (84) to generate the burst of internal addresses. Id. at 2:22-28. Other inputs to "burst counter unit 80" include clock signal CLK (91) and control signals ADV (93) and ADS (94). Id. at 1:65-67. "[W]hen the advance signal ADV is brought High, the address on the burst counter 84 is incremented *every time a leading edge of the clock signal CLK is encountered*. As the internal address signal INT.ADD is incremented in this manner, the decoder selects different word lines 11 successively." Id. at 2:55-61.

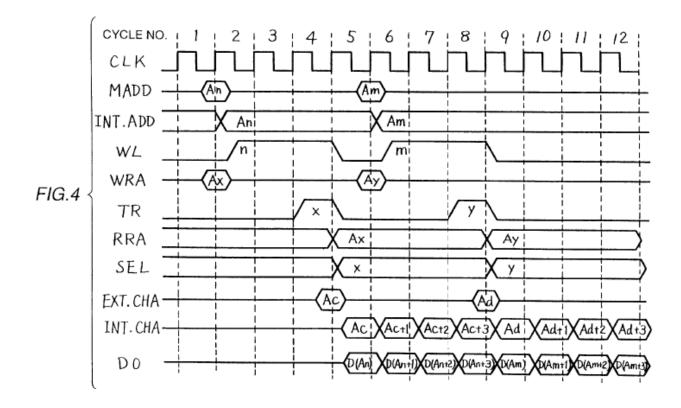

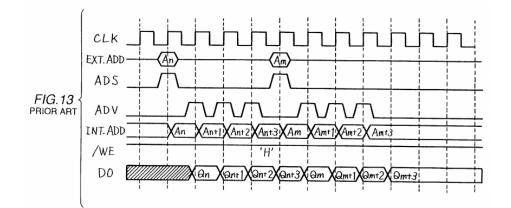

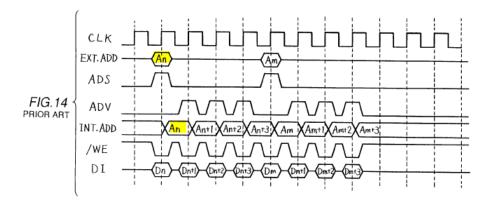

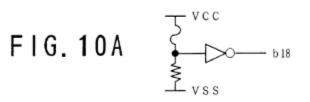

Figure 13 (below) is a timing diagram showing a burst read operation using the system of Wada's Figure 12. The external address An is latched when ADS goes high. Thereafter, "*every time* the clock signal CLK is at a leading edge and the advance signal ADV is High, the address indicated by the internal address signal INT.ADD based on the address An given by the external address EXT.ADD *is incremented by the burst counter* 84." *Id.* at 3:5-9.

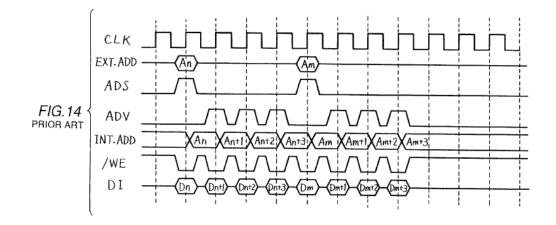

Figure 14 (below) depicts a burst write operation. "In the write operation, the internal address INT.ADD based on the address An designated by the external address signal EXT.ADD varies in the same manner as in the read operation." *Id.* at 3:27-30. Ex-1002 ¶¶57-61.

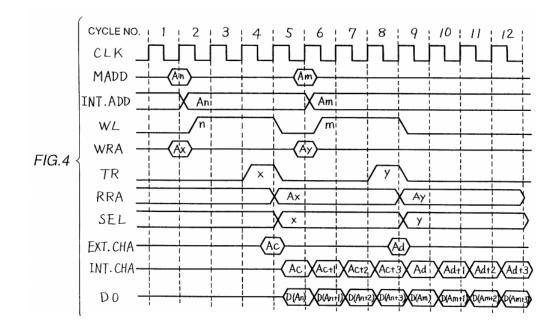

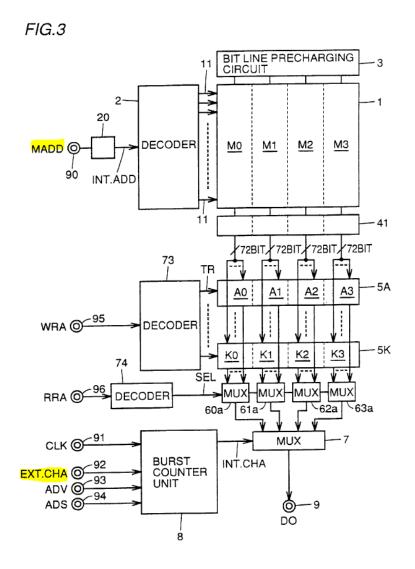

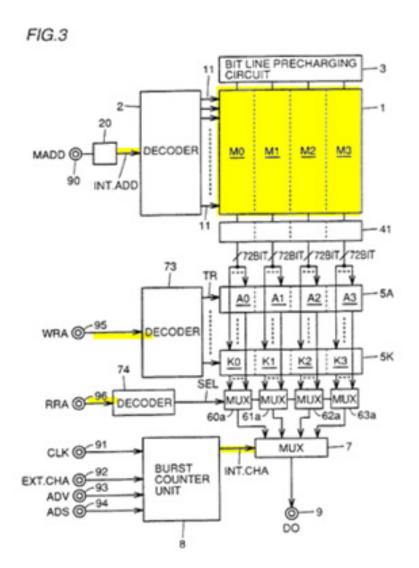

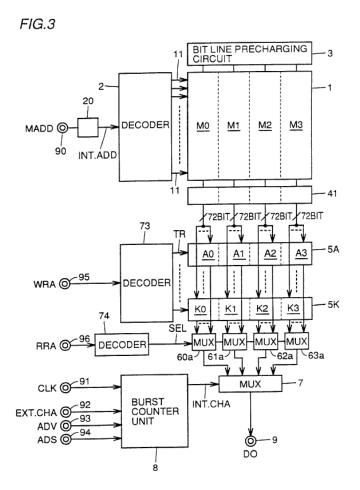

Wada discloses a "second embodiment of the invention and capable of operating in burst mode." Ex-1005 at 14:58-59; Figs. 3-4. Highlighted in yellow below, "[t]he memory cell array 1 has a plurality of memory cells . . . divided into a plurality (e.g., four) memory blocks M0 through M3. . . ." *Id.* at 3:48-50. (Note that like elements appearing in Figure 3 are described with respect to Figures 1 and/or 15. *Id.* at 12:32-35; 14:59-62.) External memory address MADD and external chunk address EXT.CHA are input to the circuit. *Id.* at 3:56-62; 4:14-16. Register 20 latches MADD to present internal address INT.ADD to a decoder, where it is used to simultaneously read data from memory blocks M0 through M3 at the addressed word line. *Id.* at 3:58-62; 4:1-5. External chunk address

EXT.CHA is presented to a burst counter 8 (green). "The burst counter unit 8 is identical in structure to the burst counter unit 80 in Figure 12, except that the external address EXT.ADD of Figure 12 is replaced by the external chunk address EXT.CHA." *Id.* at 4:17-21. The "burst counter unit 8 admits an address AC stemming from the external chunk address signal EXT.CHA." *Id.* at 4:60-62. Then, "the internal chunk address signal varies in the sequence of Ac, Ac+1, Ac+2, etc." *Id.* at 4:64-65. "Given the internal chunk address signal INT.CHA sent from the burst counter unit 8, the multiplexer 7 [orange] successively transfers to the data input/output pin 9 the data fed from the multiplexers 60a through 63a. This allows the data input/output pin 9 to output the data in burst mode." *Id.* at 15:66-16:3.

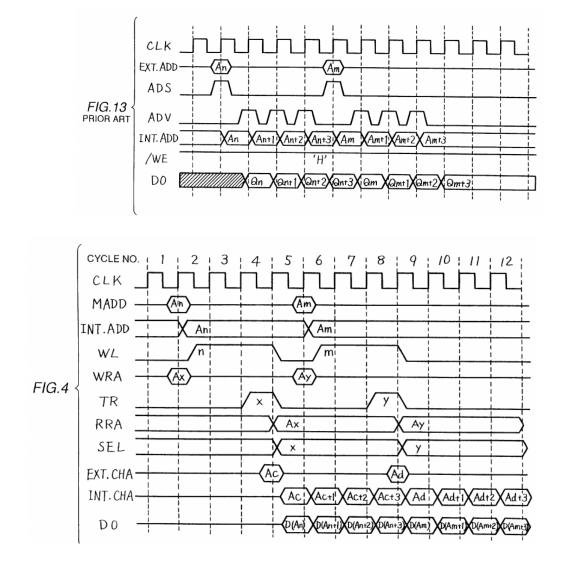

Thus, INT.ADD, latched from external memory address MADD, acts as the top n-2 bits of a memory address, transferring four modules worth of data to registers. The burst counter then increments external chunk address EXT.CHA from 0 to 4 at each CLK edge, providing the bottom 2 bits of the data address that pull the corresponding data from the registers by successively connecting each input of multiplexer 7 to its output. *Id.* at 14:54-16:55. The exemplary selection of four memory blocks (M0 - M3) and a four-input multiplexer (7) fix the burst length at four.

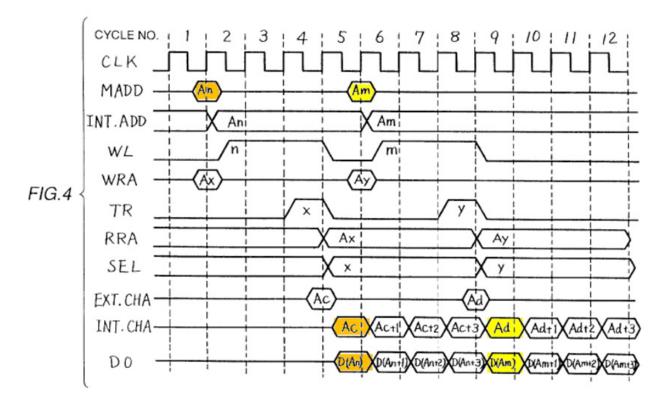

Figure 4 shows operation of embodiment 2. External address An is latched in from MADD and held as INT.ADD. External chunk address Ac is the incremented to form a burst of addresses on INT.CHA of Ac, Ac+1, Ac+2, and Ac+3. These addresses fetch data corresponding to offsets from the address An latched in from MADD, namely, D(An), D(An+1), D(An+2), and D(An+3). *Id.* ar Fig. 4 (Do line). This is repeated with the next address Am. "In response to these addresses, the above-described actions are carried out *continuously*. This allows the data corresponding to the address Am to be *output uninterrupted in burst*

*mode*." *Id*. at 16:7-10. "This constitution provides one advantage identical to that of the first embodiment, i.e., the ability to *execute data burst output in uninterrupted fashion*." *Id*. at 16:14-15; Ex-1002 ¶¶62-64.

Wada discloses multiple embodiments, including two it calls "conventional" and an additional six it refers to as the first through sixth embodiments. Ex-1005 at 11:43-12:23. All of these embodiments are similar, and Petitioner discusses two of them in the analysis that follows: a "conventional" embodiment illustrated in Figures 12-14, and the "second embodiment" illustrated in Figures 3-4. However, Wada's other embodiments also anticipate or render obvious claims of the '134 Patent, and Petitioner reserves the right to rely on them. Ex-1002 ¶65.

#### 2. Independent Claim 1

#### a. 1[pre]: A circuit comprising:

**Conventional Embodiment:** Wada discloses "Fig. 12 is a block diagram of the conventional SRAM capable of operating in burst mode." Ex-1005 at 12:10-11; Figs. 12-14.

**Second Embodiment:** Wada discloses "FIG. 3 is a block diagram of an SRAM practiced as a second embodiment of the invention and capable of operating in burst mode." *Id.* at 11:49-51; Figs. 3-4.

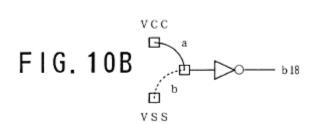

Wada's first, third through sixth, and second conventional embodiments all operate similarly to the second embodiment, have common structure described with reference to one another, and also disclose claim 1 of the '134 Patent. *See* Ex-1005 (Wada) at 3:37-5:64, Figs. 15-16 (second conventional embodiment); 12:49-14:52, Figs. 1-2 (first embodiment); 16:51-19:6, Figs. 5-6 (third embodiment); 19:7-34, Figs. 7-8 (fourth embodiment); 19:35-20:60, Figs. 9-10 (fifth embodiment); 20:61-21:38. Fig. 11 (sixth embodiment). Thus, Petitioner reserves the right to rely on those additional embodiments disclosed in Wada to the extent they operate similarly or provide additional insight into the operation of the embodiments discussed in detail herein. Ex-1002 ¶¶66-67.

#### b. 1[a]: a memory comprising a plurality of storage elements each configured to read and write data in response to an internal address signal; and

#### Conventional Embodiment: Wada discloses an SRAM comprising "a

memory cell array" that is "addressable storage," as construed in the Cypress

litigation, which is read from or written to in response to "internal address signal

INT.ADD." Ex-1005 at 1:22-32. See also 3:5-15:

Thereafter, every time the clock signal CLK is at a leading edge and the advance signal ADV is High, the address indicated by the internal address signal INT.ADD based on the address An given by the external address signal EXT.ADD is incremented by the burst counter 84. The incremented address occurs as An, An+1, An+2, etc. This causes a different word line 11 to be selected in each cycle of the clock signal CLK. As a result, the output data DO varies in the sequence of Qn, Qn+1, Qn+2, etc. This in turn allows data to be output in burst mode from memory cells MC, MC, etc. in the memory cell array 1.

See also id. at 3:26-28 ("In the write operation, the internal address INT.ADD

based on the address An designated by the external address signal EXT.ADD

varies in the same manner as in the read operation."). The address signals, as

described above, determine the address location in the memory array from which

data is read or to which data is written.

**Second Embodiment:** Wada discloses a memory array of addressable storage (Fig. 3, element 1) read from and written to using internal addresses INT.ADD and INT.CHA, created internal to the circuit:

Given the internal chunk address signal INT.CHA sent from the burst counter unit 8, the multiplexer 7 successively transfers to the data

input/output pin 9 the data fed from the multiplexers 60a through 63a. This allows the data input/output pin 9 to output the transferred data in burst mode.

*Id.* at 15:66-16:3. *See also id.* at 16:46-50 ("[C]ontrol is made possible by externally supplying the memory with the write register address signal WRA and the read register address signal RRA."); 17:9-24 (describing read/write control signal R/WRC). *See also id.* at 3:37-5:64, 12:49-14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16; Ex-1002 ¶¶69-70.

c. 1[b]: a logic circuit configured to generate a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) one or more control Signals, wherein said generation of said predetermined number of internal address signals is noninterruptible.

**Conventional Embodiment:** Wada's conventional embodiment discloses a circuit designed to perform logic operations (Fig. 12, circuit 80) configured to generate a predetermined number of internal address signals. The number of address signals is fixed at manufacture time by selecting the number of bits split off from the address. For example, Wada discloses a k-bit-wide portion of the address is split off and used by the burst counter (Fig. 12, element 84), which increments the k-bit subaddress that is tacked onto an (n-k)-bit MSB portion to create internal address INT.ADD. Thus, the predetermined number of internal

address signals is 2<sup>k</sup>, and those internal address signals are generated within the

circuit (80) by the burst counter (84). See Ex-1005 at 2:18-28:

The n-bit address admitted into the register 83 is separated into a k-bit address and an (n-k)-bit address.

The burst counter 84 is a binary counter that receives the output signals of the AND gates 81 and 82, and the k-bit address following the address separation. In operation, the burst counter 84 loads the k-bit address by responding to the output signal of the AND gate 82, and increments the value of the k-bit address in reply to the output signal of the AND gate 81.

The internal addresses are generated in response to an external address

signal EXT.ADD (100), which originates outside of the circuit. Id. at 2:15-19; Fig.

12. They are also generated in response to a clock signal CLK (91). Id. at 1:64-65

("An input pin 91 admits a clock signal CLK from the outside"); 2:57-60 ("the

address on the burst counter 84 is incremented every time a leading edge of the

clock signal CLK is encountered."). And they are also generated in response to

one or more control signals. Id. at Fig. 12, e.g., ADV (93), ADS(94); 2:56-61

("when the advance signal ADV is brought High, the address on the burst counter

84 is incremented every time a leading edge of the clock signal CLK is

encountered."); see also 3:21-36, 3:56-4:40.

The address burst is non-interruptible, or "cannot be stopped once initiated," as previously construed: "The conventional SRAM of the above constitution typically works as follows: when the advance signal ADV is brought High, the address on the burst counter 84 is incremented every time a leading edge of the

*clock signal CLK is encountered*. As the internal address signal INT.ADD is incremented in this manner, the decoder 2 selects different word lines 11 *successively*." *Id.* at 2:55-61. *See also id.* at Fig. 13 (continuous generation of INT.ADD values):

*See also id.* at 6:3-8 ("It is another object of the present invention to provide a semiconductor memory working in burst mode for a high-speed read operation irrespective of the operating speed of its memory cell array and *without causing data output interruptions.*"). Unlike the prior art considered during prosecution (*see* Section VII, above), Wada discloses no method of terminating a burst before it has completed. Ex-1002 ¶¶71-73.

**Second Embodiment:** Wada's second embodiment discloses a circuit designed to perform logic operations (Fig. 3, circuit 8) configured to generate a fixed number of internal address signals. Internal address "INT.CHA," generated by circuit 8 of Figure 3, selects one of four inputs of multiplexer 7 to sequentially

extract data from four stored memory locations. Thus, the burst length is fixed by the choice of a four-input multiplexer and the choice of dividing the memory into four blocks (M0-M3). Figure 4 show signal INT.CHA takes on four values, Ac through Ac+3, for the first external addresses An (arriving as signal MADD from outside the circuit) and Ac (arriving as signal EXT.CHA from outside the circuit), and then take on the four values Ad through Ad+3 for the next external address Am (MADD) and Ad (EXT.CHA):

The address burst is generated in response to external address signals MADD and EXT.CHA (which arrive from outside the circuit) and clock signal CLK. Ex-1005 at 15:37-40 ("Referring to FIG. 4, the address An designated by the memory address signal MADD is admitted into the internal register 20 at a first leading edge of the clock signal CLK in the second cycle."); 4:17-21 ("burst counter unit 8 admits an address AC stemming from the external chunk address

signal EXT.CHA."). It is also generated in response to one or more control

signals. Id. at Fig. 3 (e.g., ADV(93), ADS(94), RRA(96), WRA(95), TR); 12:60-

65 (TRA transfers data to/from output registers); 2:55-3:15 (ADV enables

incrementing of burst counter); 1:64-2:13 (ADS address strobe latches in external

address); 14:57-15:36 (RRA causes multiplexers to designate a register from which

to read data; WRA causes multiplexer to designate registers to receive data.)

Wada discloses that the address burst is non-interruptible. Id. at 16:5-10:

In the sixth cycle, the address Am designated by the memory address signal MADD and the address signal Ay designated by the write register address signal WRA are admitted. In response to these addresses, the above-described actions *are carried out continuously*. This allows the data corresponding to the address Am to be o*utput uninterrupted in burst mode*.

See also id. at 3:37-5:64, 12:49-14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16; Ex-

1002 ¶¶74-76.

- 3. Dependent Claim 2

- a. 2: The circuit according to claim 1, wherein said predetermined number of internal address signals is determined by a fixed burst length.

In the 792 Investigation, the parties agreed that "burst" means "a number of words transferred as a group." In other words, burst length is the number of internal address signals generated in response to an external address. Ex-1002 ¶77.

Conventional Embodiment: Wada discloses a predetermined number of

internal address signals determined by a fixed burst length: For example, a k-bit-

wide portion of the address is split off and used by the burst counter, which

increments the k-bit subaddress that is tacked onto the (n-k)-bit MSB portion of the

internal address. In other words, the predetermined number of internal address

signals is 2<sup>k</sup>, which is the limit of a k-bit counter, and the burst length. See Ex-

1005 (Wada) at 2:18-28:

The n-bit address admitted into the register 83 is separated into a k-bit address and an (n-k)-bit address.

The burst counter 84 is a binary counter that receives the output signals of the AND gates 81 and 82, and the k-bit address following the address separation. In operation, the burst counter 84 loads the k-bit address by responding to the output signal of the AND gate 82, and increments the value of the k-bit address in reply to the output signal of the AND gate 81.

*See also id.* at 1:22-2:61, 3:5-15, 3:20-36; Ex-1002 ¶78.

**Second Embodiment:** Wada discloses a predetermined number of internal address signals set to four, which is a fixed value corresponding to the length of each burst. Ex-1005 (Wada) at 3:48-50. For example, in Figure 3, the "INT.CHA" internal address selects one of four inputs of MUX 7 to sequentially extract data from four stored memory locations corresponding to memory blocks M0 to M3. *Id.* at 15:66-16:3; *see also id.* at 14:57-15:29, 15:44-65, 16:4-50. Figure 4 shows INT.CHA takes on four values Ac through Ac+3 for a first burst and Ad through Ad+4 for a second burst. *See also id.* at 3:37-5:64, 12:49-14:52, 16:51-21:38; Figs.

1-2, 5-10, 15-16; Ex-1002 ¶79.

## 4. Dependent Claim 3

a. 3: The circuit according to claim 1, wherein said predetermined number of internal address signals is at least 4.

Applying the ITC's prior construction, a "predetermined number of internal address signals" to mean "a fixed number of internal address signals for a burst access," Wada discloses claim 3.

**Conventional Embodiment:** Wada illustrates generating a burst using k-bit counter 84 of Figure 12 (see claim 2 above), and the corresponding waveforms. Figure 13 shows that the burst length is set to 4 (*i.e.*, k=2). *Id.* at 2:16-28; 2:58-61. *See also id.* at 2:6-14, 2:29-65; 3:5-36. Figure 13 shows internal address signal INT.ADD takes on four values per burst: An to An+3:

**Second Embodiment:** Wada's "INT.CHA" internal address takes on four values to output data extracted from four memory blocks M0 to M3. *Id.* at 15:66-16:3; *see also id.* at 14:56-15:36, 15:44-65; Fig. 3 (M0-M3). Thus, the burst length

is set to four by configuring the memory as four blocks. Figure 4 shows INT.CHA takes on the values Ac through Ac+3 for a first burst and Ad through Ad+4 for a second burst. *Id.* at 4:64-65.

See also Wada's embodiments 1, 3-6, and second conventional embodiment, each of which use a fixed burst length of four. *Id.* at 3:37-5:64, 12:49-14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16; Ex-1002 ¶¶80-82.

#### 5. Dependent Claim 8

# a. 8: The circuit according to claim 1, wherein said memory comprises a static random access memory.

**Conventional Embodiment:** Wada discloses "FIG. 12 is a block diagram of a typical conventional *SRAM* capable of operating in burst mode." Ex-1005 at 1:22-23; 2:55-61; 12:10-11.

Second Embodiment: Wada discloses "FIG. 3 is a block diagram of an

*SRAM* practiced as a Second embodiment of the invention and capable of operating in burst mode." *Id.* at 11:49-51. Wada further discloses "FIG. 3 is a block diagram of an *SRAM* practiced as the Second embodiment of the invention and capable of operating in burst mode." *Id.* at 14:57-59. *See also* Wada's embodiments 1, 3-6, and second conventional embodiment, each of which uses SRAM. *Id.* at 11:41-12:22; 12:29-39, 14:5-11, 14:28-34, 14:57-67, 16:11-15, 16:56-63, 17:48-51, 18:53-63, 19:36-40, 19:52-55, 20:37-21:11, 21:33-38; Ex-1002 ¶83-84.

## 6. Dependent Claim 12

a. 12: The circuit according to claim 1, wherein said logic circuit comprises a counter configured to generate said predetermined number of internal address signals.

**Conventional Embodiment:** Wada discloses a k-bit burst counter that generates the predetermined number of internal address signals. *See, e.g.,* Ex-1005 at Fig. 12 (elements 80, 84) (green):

*See also id.* at 2:55-62 ("The conventional SRAM of the above constitution typically works as follows: when the advance signal ADV is brought High, the address on the burst counter 84 is incremented every time a leading edge of the clock Signal CLK is encountered. As the internal address signal INT.ADD is incremented in this manner, the decoder 2 selects different word lines 11 successively."); *see also id.* at 1:22-2:54; 4:17-28.

**Second Embodiment:** Wada discloses a burst counter in Figure 3 (element 8) that generates four internal address signals. *Id.* at 1:22-2:62; 4:17-23 ("The burst counter unit 8 is identical in structure to the burst counter unit 80 in FIG. 12, except that the external address signal EXT.ADD of FIG. 12 is replaced by the external chunk address signal EXT.CHA."). *See also id.* at 3:37-5:64, 12:49-

14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16; Ex-1002 ¶¶85-86.

# 7. Dependent Claim 13

a. 13: The circuit according to claim 1, wherein said external address signal comprises an initial address for data transfers to and from said memory.

**Conventional Embodiment:** External address EXT.ADD is latched into

register 83, as shown in the excerpt of Figure 12 below. Ex-1005 at 2:16-17. The bottom k bits of the EXT.ADD are incremented in burst counter 84 and concatenated with the upper (n-k) bits to form internal address INT.ADD. *Id.* at 2:22-28, 2:58-61. Thus, the initial address carried on INT.ADD is the external address.

Figure 14 shows initial EXT.ADD address An is also the first value of INT.ADD (compare shaded elements below). *Id.* at 2:58-61.

**Second Embodiment:** Figure 3 shows external address MADD and external chunk address EXT.CHA used to initiate the burst data transfer, as highlighted below.

When MADD is Am, for example, "the data corresponding to the address Am [is] output uninterrupted in burst mode." *Id.* at 16:43-10. Figure 4, annotated below, shows external address MADD set to An, and the initial value of the internal address set to select data corresponding to address An, *i.e.*, D(An). *Id.* at 3:56-62; 4:14-16. Similarly, when MADD is Am, the initial internal address selects data corresponding to address Am, *i.e.*, D(Am). *Id.*

See also id. at 3:37-5:64, 12:49-14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16;

Ex-1002 ¶¶87-91.

## 8. Independent Claim 16

a. 16[pre]: A circuit comprising:

See claim 1[pre] above.

## b. 16[a]: means for reading data from and writing data to a plurality of storage elements in response to a plurality of internal address signals; and

Wada discloses this means-plus-function element. As discussed above with respect to claim construction, the corresponding structure in the '134 Patent is shown in Figure 1, highlighted below:

**Wada Conventional Embodiment:** In Figure 12, highlighted below, Wada discloses a plurality of storage elements (1) from which data can be read and to which data can be written (DI, DO lines), in response to an internal address INT.ADD. *Id.* at 1:28-32; 2:58-61. The operation of these structures is mapped to the recited function in the discussion of claim element 1[a] above.

**Wada Second Embodiment:** In Figure 3, highlighted below, Wada discloses a plurality of storage elements (1) from which data can be read and to which data can be written (WRA, RRA control lines, "data *input/output* pin 9"). *Id.* at 15:66-16:2, 15:7-9, 15:15-16. The operation of these structures is mapped to the recited function in the discussion of claim element 1[a] above.

See also Wada's embodiments 1, 3-6 and conventional embodiment 2, id. at 3:37-

5:64, 12:49-14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16; Ex-1002 ¶¶92-95.

c. 16[b]: means for generating a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible.

Wada discloses this means-plus-function element. As discussed above with respect to claim construction, the corresponding structure in the '134 Patent is

either (1) the structure shown in Figure 2, or (2) the structure shown in Figure 3, highlighted below:

**Wada Conventional Embodiment:** Figure 12, excerpted below, shows the same structure shown in '134 Patent Figure 2. The control signal ADV (93) is logically ANDed with the CLK signal (91) to enable incrementing the address value EXT.ADD that is latched into register 83 by the ADS control signal. Ex-1005 at 1:64-2:28. Burst counter 84 increments the address in response to the CLK edges to produce output internal address signal INT.ADD. *Id.* at 2:29-61. This structure is identical to the '134 Patent's CLK / ADV signals that are combined into a BURST\_CLK signal that increments the address latched into the counter on the LOAD signal.

This structure performs the recited function, as described in detail above with respect to claim element 1[b].

Fig. 12 (excerpt)

**Wada Second Embodiment:** Wada's Figure 3, below, shows the equivalent structure of '134 Patent Figure 3. While Figure 3 of the '134 Patent uses a multiplexer to reassemble the lower bits of internal address before addressing the memory array, Wada's Figure 3 addresses four memory blocks and then uses the multiplexer to select which of the four words is indicated by the lower address bits. Thus Wada uses the same structural elements in an equivalent manner to perform the same function.

In Wada, the most significant bits of the external address are latched in by latch 20 and used to simultaneously address four memory modules M0 to M3. *Id.* at 15:66-16:3. The lowest significant bits enter the burst counter unit 8 as the

44

chunk address EXT.CHA and are incremented to address a MUX that successively pulls data from locations having the same base address MADD (INT.ADD). *Id.* at 4:60-65.

This structure is equivalent to Figure 3 of the '134 Patent. There, the M most significant bits of the ADDR\_EXT are latched into latch 134. The k least significant bits are input to a counter 138, and MUX 136 is switched from the base address (k bits from 142) to the incremented address (k bits from 138) to address the memory.

Although Wada pulls four blocks of data from memory using the MADD address and then uses a MUX to select between those blocks, while the '134 Patent uses the MUX to separately address the memory, the structure is equivalent because it achieves substantially the same result in substantially the same way, *i.e.*, by separating the address into parts, incrementing the lower address bits, and using a multiplexer to select the data corresponding to the full internal address.

The structure of Wada's Figure 3 performs the recited function as described above in detail with respect to claim 1[c].

See also id. at 3:37-5:64, 12:49-14:52, 16:51-21:38; Figs. 1-2, 5-10, 15-16. Thus, Wada anticipates claim 16 for the reasons described above and with respect to claim 1. Ex-1002 ¶¶96-102.

# 9. Independent Claim 17

# a. 17[pre]: A method of providing a fixed burst length data transfer comprising the steps of:

See discussion of claim element 1[pre] and claim 2, above, in Sections X.A.2.a and X.A.3.

# b. 17[a]: accessing a memory in response to a plurality of internal address signals; and

See discussion of claim element 1[a], above, in Section X.A.2.b.

c. 17[b]: generating a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) a control signal, wherein said generation of said predetermined number of internal address signals is noninterruptible.

See discussion of claim element 1[b], above, in Section X.A.2.c. Ex-1002

¶¶103-05.

# B. Ground 2: Claims 1-4, 8, 12-14, 16, and 17 are obvious over Wada in view of the knowledge of a POSITA

# 1. Independent Claims 1 and 16

Unlike the prior art distinguished during prosecution, Wada discloses no method of interrupting an address burst once it has been initiated. But to the extent Patent Owner argues Wada's control signals might be manipulated to terminate a burst (even though there is no such teaching), it would have been obvious to a POSITA not to do so and to keep the generation of internal address signals noninterruptible, because Wada teaches against interrupting a burst: "it is another object of the present invention to provide a semiconductor memory working in burst mode for a high speed read operation irrespective of the operating speed of its memory cell array and *without causing data output interruptions*." Ex-1005 (Wada) at 6:3-8. Thus, Wada renders claims 1 and 16 obvious. Ex-1002 ¶106.

#### 2. Dependent Claims 2-3, 8, 12-13, and 17

Dependent Claims 2-3, 8, 12-13, and 17 are rendered obvious by Wada in light of the discussion of claims 1 and 16 above, and the discussion in Section X.A above. Ex-1002 ¶107.

#### 3. Dependent Claim 4

## a. 4: The circuit according to claim 1, wherein said predetermined number of internal address signals is 8.

Wada discloses claim 1 in exemplary embodiments having a fixed burst length of four. Section X.A.4; Ex-1005 (Wada) at 3:48-51 ("memory cell array 1 has a plurality of memory cells . . . divided into a plurality (*e.g., four*) memory blocks M0 through M3."). When Wada was filed, it was well known in the prior art that memory systems commonly employed burst lengths of 2, 4, or 8. See, e.g., Ex-1008 (Reeves) at 2:15-17 ("Conventional SDRAMs can be programmed to read or write a burst of one, two, four, eight, or more bits."); Ex-1006 (Fujioka) at 15:7-8 ("the FCRAM with the burst length fixed to 4 or 8 can be obtained."); Ex-1014 (Ryan) at 6:4-6 ("Burst length options of 2, 4, 8 and full page... may be provided."). Because a longer burst transfers more data for a given read or write command, a POSITA would have been motivated to modify the exemplary embodiments of Wada to set a burst length of eight to further Wada's stated goal "to provide a semiconductor memory operating in burst at a sufficiently high speed

irrespective of the operating speed of its memory cell array." *Id.* at 5:66-6:2; Ex-1002 ¶108.

As discussed in Section A.3.a, the first conventional embodiment of Wada sets a burst length of 2<sup>k</sup>. *See* Ex-1005 (Wada) at 2:18-28. Thus, choosing k to be three would set the burst length to eight. Ex-1002 ¶108. Wada's Second embodiment could be modified to a burst length of eight by dividing the memory cells into eight banks (M0-M7) instead of four and selecting an 8-input, rather than 4-input, multiplexer. *See* Ex-1005 (Wada) at 3:48-55; 15:66-16:3; Ex-1002 ¶108. Thus Wada renders claim 4 obvious.

#### 4. Dependent Claim 14

# a. 14: A memory device according to claim 1, wherein said circuit is an integrated circuit.

Wada discloses a "semiconductor memory capable of operating in burst mode." Ex-1005 at 1:9-10. Wada further states "This eliminates the need for the memory to use illustratively the so-called *bipolar CMOS LSI technology*, an expensive process technique for enhancing the operation speed of the memory cell array 1. As a result, the invention allows semiconductor memories adopting *lowcost process techniques* to perform high-speed read operations." *Id.* at 14:47-53. One of ordinary skill would have understood these process technologies relate to integrated circuits. Ex. 1002 ¶110. Thus, Wada renders claim 14 obvious.

To the extent necessary, Wada and Reeves renders this claim obvious, as

discussed below in Ground 4.

# C. Ground 2a: Claims 1-4, 8, 12-14, 16, and 17 are rendered obvious by the combination of Wada and US 5,584,033 ("Barrett") in view of the knowledge of a POSITA

#### 1. Barrett

Barrett was filed November 7, 1994 and issued December 10, 1996, qualifying as prior art under at least pre-AIA 35 U.S.C. §102(b). Ex-1010 (Barrett) at 1.

Barrett is entitled "Apparatus and Method for Burst Data Transfer Employing a Pause At Fixed Data Intervals" and discloses a "plurality of devices attached to a communication bus observe a burst transfer protocol which allows pausing only at pre-determined, fixed intervals of n data words, where a word is the width of the bus." *Id.* at Abstract. Further, "system 100 may comprise multiple CPUs and *memory units* communicating with other units via system I/O bus 101." *Id.* at 4:46-48. Accordingly, "once burst transfer is initialized the sending device *transmits an uninterrupted stream* of n data words over the communications bus . . . ." *Id.* at Abstract. Indeed, "[t]he essential feature of burst communication is that the data transfer takes place at high speed and *without interruption*." *Id.* at 1:64-66.

Barrett's system operates as follows:

In the data transfer phase, the sender transmits 32 words of data in successive cycles, *without interruption*, at step 404. Each word is the

amount of data the bus can support in a single cycle, i.e. the number of parallel data lines in the bus.

Id. at 6:8-15. Furthermore, Barrett discloses:

In the preferred embodiment, the number of words in transferred in an *uninterrupted stream* before any pause can take place is fixed for a particular hardware and software release of computer system 100. In an alternative embodiment, it would be possible to dynamically vary the predetermined length n of the *uninterrupted data stream* from time to time.

*Id.* at 9:17-24. Barrett claims a system including "means for initializing a burst data transmission comprised of a plurality of *uninterruptible streams of n data transfer cycles*, where n is a predetermined integer greater than one . . . ." *Id.* at claim 1. *See also id.* at claims 2, 8, 13, 19, 24, and 27 (reciting "uninterruptible streams" or "uninterrupted streams"). Ex. 1002 ¶¶110-14.

#### a. Motivation to combine Wada and Barrett

As discussed above, Wada discloses that the generation of the predetermined number of internal address signals is non-interruptible. However, to the extent Patent Owner argues Wada's control signals could be manipulated (in some undisclosed manner) to terminate a burst data transfer, Wada could be combined with Barrett.

One of ordinary skill would have been motivated to combine Wada and Barrett because both are directed to achieving the same purpose. Wada discloses that "[i]t is another object of the present invention to provide a semiconductor

51

memory working in burst mode for a *high speed read* operation irrespective of the operating speed of its memory cell array and *without causing data output interruptions*." Ex-1005 (Wada at 6:3-7). And Wada's invention is directed to making it "possible to output a plurality of target data items in burst mode *without interruption* therebetween." *Id.* at 7:65-67. Specifically, Wada discloses "the data corresponding to the address Am [can] be *output uninterrupted in burst mode*." *Id.* at 16:5-10. And Wada notes that uninterrupted data transmission is an advantage: "This constitution provides one advantage identical to that of the first embodiment, i.e., the ability to *execute data burst output in uninterrupted fashion*." *Id.* at 16:12-15. Ex. 1002 ¶115-16.

Similarly, Barrett claims "a burst data transmission comprised of a plurality of *uninterruptible* streams of n data transfer cycles." Ex-1010 (Barrett) at claim 1. Barret further states, "In effect, allowing a pause at any point *defeats the purpose of burst transmission*, which is to send data as rapidly as possible in *an uninterrupted stream*." *Id.* at 2:39-41. A POSITA would realize that applying Barrett's teachings to Wada to render bursts uninterruptible would result in improved transmission efficiency by minimizing overhead associated with terminating and initiating packets. *See id.* at 2:20-22, 3:44-50; Ex. 1002 ¶117. Thus, to the extent Wada's disclosure leaves open any possibility that a burst data transmission could be interrupted, one of ordinary skill would have been motivated to apply the teachings of Barrett to achieve an *uninterruptible* data transmission stream.

### 2. Claims 1-4, 8, 12-14, 16, and 17

The combination of Wada and Barrett, ensuring that the generation of internal address signals cannot be interrupted once initiated, can be applied to render claims 1-4, 8, 12-14, 16, and 17 obvious for the same reasons discussed above with respect to Grounds 1 and 2. Ex. 1002 ¶118.

# D. Ground 3: Claims 4-7, and 18-20 are rendered obvious by the combination of Wada and U.S. 6,185,149 ("Fujioka") in view of the knowledge of a POSITA.

### 1. Fujioka

Fujioka is directed to "semiconductor integrated circuit memories" (Ex. 1006 at 1:6-7) read in burst mode without interruption: "when the burst length is equal to 4, the 4-bit parallel data read from the sense amplifiers are converted into serial data, so that data can be consecutively read and output without any interruption. *Id.* at 8:1-4. Fujioka notes "Recently, semiconductor memory devices such as DRAM (Dynamic Random Access Memory) devices have been required to input and output data at higher frequencies in accordance with speeding up of CPUs so that the data transmission rate can be increased." *Id.* at 1:10-15. And, "as the number of bits of data to be simultaneously read in parallel increases, the burst length increases." *Id.* at 3:65-67. To increase the data throughput,

Fujioka discloses that multiple memory cell blocks can be activated to transfer data

in longer bursts:

As described above, a plurality of memory cell blocks (banks) can be selectively activated in response to one read command. Hence, it is possible to select the memory cell blocks based on the burst length BL. When the burst length BL is equal to 8, two memory cell blocks (the memory cell block 12a of the bank-0 circuit 7 and the memory cell block 12a of the bank-1 circuit 8) are selectively activated...

*Id.* at 9:49-59. The burst length can be programmed late in the manufacturing

process by using laser-cut fuses to tie circuits to Vcc or ground or by using bond

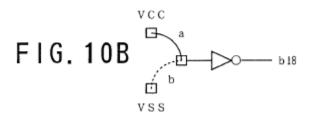

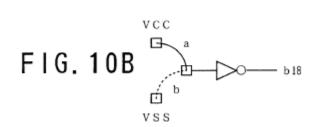

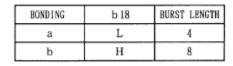

options: