# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD FLEX LOGIX TECHNOLOGIES, INC. Petitioner v. KONDA TECHNOLOGIES INC. Patent Owner Patent No. 10,003,553

PETITION FOR POST GRANT REVIEW OF U.S. PATENT NO. 10,003,553

# TABLE OF CONTENTS

| I.    | INTE                                       | RODU                                            | CTION                                                                               | 1  |  |

|-------|--------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------|----|--|

| II.   | MANDATORY NOTICES UNDER 37 C.F.R. § 42.8   |                                                 |                                                                                     | 2  |  |

|       | A.                                         | Real Parties-in-Interest                        |                                                                                     |    |  |

|       | B.                                         | Rela                                            | ted Matters                                                                         | 3  |  |

|       |                                            | 1.                                              | Lawsuit(s)                                                                          | 3  |  |

|       |                                            | 2.                                              | Related Applications                                                                | 3  |  |

|       |                                            | 3.                                              | Concurrently filed petitions                                                        | 4  |  |

|       | C.                                         | Cour                                            | nsel and Service Information                                                        | 4  |  |

| III.  | PAY                                        | MENT                                            | Γ OF FEES UNDER 37 C.F.R. § 42.15(a)                                                | 5  |  |

| IV.   | TIMI                                       | ΓIME FOR FILING UNDER 37 C.F.R. § 42.2025       |                                                                                     |    |  |

| V.    | GRO                                        | OUNDS FOR STANDING UNDER 37 C.F.R. § 42.204(a)5 |                                                                                     |    |  |

| VI.   | PRECISE RELIEF REQUESTED AND GROUND RAISED |                                                 |                                                                                     | 5  |  |

|       | A.                                         | Claims for Which Review is Requested5           |                                                                                     |    |  |

|       | B.                                         | Statu                                           | ntory Ground of Challenge                                                           | 6  |  |

| VII.  | LEV                                        | EL OF                                           | F ORDINARY SKILL IN THE ART                                                         | 7  |  |

| VIII. | BAC                                        | KGRO                                            | OUND                                                                                | 8  |  |

|       | A.                                         | The                                             | '553 Patent                                                                         | 8  |  |

|       | B.                                         | Mate                                            | erial Incorporated by Reference in the '553 Patent                                  | 13 |  |

| IX.   | PGR ELIGIBILITY17                          |                                                 |                                                                                     |    |  |

|       | A.                                         |                                                 | Two Pre-AIA Applications Do Not Support Switches figurable By a Flip Flop (Claim 9) | 19 |  |

| В.  |                |                                                                                                  | 21             |

|-----|----------------|--------------------------------------------------------------------------------------------------|----------------|

|     | 1.             | Claim 1                                                                                          | 23             |

|     | 2.             | Claim 2                                                                                          | 26             |

|     | 3.             | Claim 4                                                                                          | 28             |

|     | 4.             | Claims 11, 12, and 14                                                                            | 31             |

| C.  | AIA            | Applicability                                                                                    | 32             |

| CLA | IM CO          | ONSTRUCTION                                                                                      | 33             |

| EAR | LIEST          | EFFECTIVE FILING DATE OF THE '553 PATENT                                                         | 34             |

| DET | AILEI          | D EXPLANATION OF THE GROUND                                                                      | 34             |

| A.  | Grou           | and 1: Wong Anticipates Claims 1-7, 9-15, and 17-19                                              | 34             |

|     | 1.             | Claim 1                                                                                          | 34             |

|     | 2.             | Claim 2                                                                                          | 94             |

|     | 3.             | Claim 3                                                                                          | 95             |

|     | 4.             | Claim 4                                                                                          | 99             |

|     | 5.             | Claim 5                                                                                          | 100            |

|     | 6.             | Claim 6                                                                                          | 101            |

|     | 7.             | Claim 7                                                                                          | 102            |

|     | 8.             | Claim 9                                                                                          | 103            |

|     | 9.             | Claim 10                                                                                         | 106            |

|     | 10.            | Claim 11                                                                                         | 107            |

|     | 11.            | Claim 12                                                                                         | 124            |

|     | 12.            | Claim 13                                                                                         | 125            |

|     | C. CLA EAR DET | 11, 1  1. 2. 3. 4. C. AIA CLAIM CO EARLIEST DETAILEI A. Grou  1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. | 11, 12, and 14 |

# Petition for Post Grant Review Patent No. 10,003,553

|         | 13.    | Claim 14 | 126 |

|---------|--------|----------|-----|

|         | 14.    | Claim 15 | 127 |

|         | 15.    | Claim 17 | 128 |

|         | 16.    | Claim 18 | 128 |

|         | 17.    | Claim 19 | 129 |

| XIII CO | ONCLUS | SION     | 130 |

# TABLE OF AUTHORITIES

| Page                                                                                                | <b>(s)</b> |

|-----------------------------------------------------------------------------------------------------|------------|

| Cases                                                                                               |            |

| Allergan, Inc. v. Sandoz Inc.,<br>796 F.3d 1293 (Fed. Cir. 2015)                                    | 18         |

| Ariad Pharms., Inc. v. Eli Lilly and Co., 598 F.3d 1336 (Fed. Cir. 2010) (en banc)                  | 18         |

| Brown v. 3M,<br>265 F.3d 1349 (Fed. Cir. 2001)                                                      | im         |

| Cook Biotech Inc. v. Acell, Inc.,<br>460 F. 3d 1365 (Fed. Cir. 2006)                                | 14         |

| D Three Enters., LLC v. Sunmodo Corp.,<br>890 F.3d 1042 (Fed. Cir. 2018)                            | 15         |

| In re Gosteli,<br>872 F.2d 1008 (Fed. Cir. 1989)17,                                                 | 18         |

| Grunenthal GmbH v. Antecip Bioventures II LLC, PGR2018-00001, Paper 17 (May 1, 2018)                | .17        |

| In re Johnston,<br>435 F.3d 1381 (Fed. Cir. 2006)pass                                               | im         |

| LizardTech, Inc. v. Earth Resource Mapping, Inc.,<br>424 F.3d 1336 (Fed Cir. 2005)                  | 18         |

| Lockwood v. Am. Airlines, Inc.,<br>107 F.3d 1565 (Fed. Cir. 1997)                                   | 18         |

| MPHJ Tech. Invs., LLC v. Ricoh Ams. Corp., 847 F.3d 1363 (Fed. Cir. 2017)pass                       | im         |

| Nautilus, Inc. v. Icon Health & Fitness Inc., IPR2017-01408, 2018 WL 6318050 (PTAB Dec. 3, 2018)14. | 15         |

| Paice LLC v. Ford Motor Co.,<br>881 F.3d 894 (Fed. Cir. 2018)                               |

|---------------------------------------------------------------------------------------------|

| Phillips v. AWH Corp.,<br>415 F.3d 1303 (Fed. Cir. 2005) (en banc)33                        |

| PowerOasis, Inc. v. T-Mobile USA, Inc.,         522 F.3d 1299 (Fed. Cir. 2008)       17, 18 |

| Purdue Pharma L.P. v. Recro Tech., LLC,         694 F. App'x 794 (Fed. Cir. 2017)       16  |

| Toyota Motor Corp. v. Cellport Systems, Inc., IPR2015-00633, Paper 11 (August 14, 2015)     |

| <i>Trans Video Elecs., Ltd. v. Sony Elecs., Inc.,</i> 822 F. Supp. 2d 1020 (N.D. Cal. 2011) |

| Statutes                                                                                    |

| 35 U.S.C. § 102(a)(1)6                                                                      |

| 35 U.S.C. § 112                                                                             |

| Leahy-Smith America Invents Act, Pub. L. No. 112-29, 125 Stat. 284 (2011)                   |

| Regulations                                                                                 |

| 37 C.F.R. § 42.100(b)                                                                       |

| 37 C.F.R. § 42.2025                                                                         |

| 37 C.F.R. § 42.204(a)                                                                       |

# LIST OF EXHIBITS

| Ex. 1001 | U.S. Patent No. 10,003,553                                      |

|----------|-----------------------------------------------------------------|

| Ex. 1002 | Declaration of Jacob Baker, Ph.D., P.E.                         |

| Ex. 1003 | Curriculum Vitae of Jacob Baker, Ph.D., P.E.                    |

| Ex. 1004 | File History of U.S. Patent No. 10,003,553                      |

| Ex. 1005 | File History of U.S. Application No. 14/199,168                 |

| Ex. 1006 | Application Body As Filed of PCT Application No. PCT/US12/53814 |

| Ex. 1007 | File History of U.S. Provisional Application No. 61/531,615     |

| Ex. 1008 | U.S. Patent No. 6,940,308 ("Wong")                              |

| Ex. 1009 | RESERVED                                                        |

| Ex. 1010 | RESERVED                                                        |

| Ex. 1011 | U.S. Patent No. 8,270,400                                       |

| Ex. 1012 | PCT Application No. PCTUS0856064                                |

| Ex. 1013 | File History of U.S. Provisional Application No. 60/905,526     |

| Ex. 1014 | File History of U.S. Provisional Application. No. 60/940,383    |

| Ex. 1015 | U.S. Patent No. 8,170,040                                       |

| Ex. 1016 | PCT Application No. PCT/US08/64603                              |

| Ex. 1017 | File History of U.S. Provisional Application No. 60/940,387     |

| Ex. 1018 | File History of U.S. Provisional Application No. 60/940,390     |

| Ex. 1019 | U.S. Patent No. 8,363,649                                       |

| Ex. 1020 | PCT Application No. PCT/U08/64604                               |

| Ex. 1021 | File History of U.S. Provisional Application No. 60/940,389 |

|----------|-------------------------------------------------------------|

| Ex. 1022 | File History of U.S. Provisional Application No. 60/940,391 |

| Ex. 1023 | File History of U.S. Provisional Application No. 60/940,392 |

| Ex. 1024 | U.S. Patent No. 8,269,523                                   |

| Ex. 1025 | PCT Application No. PCT/US08/64605                          |

| Ex. 1026 | File History of U.S. Provisional Application No. 60/940,394 |

| Ex. 1027 | U.S. Pat. No. 8,898,611                                     |

| Ex. 1028 | PCT Application No. PCT/US10/52984                          |

| Ex. 1029 | File History of U.S. Provisional Application No. 61/252,603 |

| Ex. 1030 | File History of U.S. Provisional Application No. 61/252,609 |

| Ex. 1031 | File History of U.S. Application No. 14/329,876             |

| Ex. 1032 | U.S. Patent No. 9,509,634                                   |

| Ex. 1033 | File History of U.S. Provisional Application No. 61/846,083 |

| Ex. 1034 | File History of U.S. Application No. 12/601,275             |

| Ex. 1035 | U.S. Patent No. 9,374,322                                   |

| Ex. 1036 | RESERVED                                                    |

| Ex. 1037 | RESERVED                                                    |

| Ex. 1038 | RESERVED                                                    |

| Ex. 1039 | RESERVED                                                    |

| Ex. 1040 | U.S. Patent No. 3,358,269                                   |

|          |                                                             |

#### I. INTRODUCTION

Flex Logix Technologies, Inc. ("Petitioner") requests post grant review ("PGR") of claims 1-7, 9-15, and 17-19 ("the challenged claims") of U.S. Patent No. 10,003,553 ("the '553 patent") (Ex. 1001), which, according to PTO records, is assigned to Konda Technologies, Inc. ("Patent Owner" or "PO"). For the reasons below, the challenged claims should be found unpatentable and canceled.

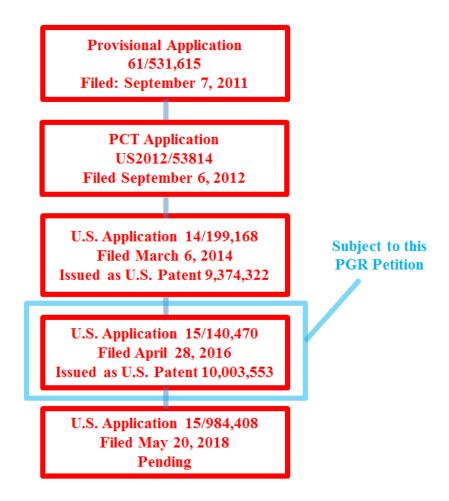

The '553 patent purports to be part of a family of applications based on U.S. Provisional Patent Application 61/531,615 ("the '615 provisional application") filed September 7, 2011. Prior to filing the '615 provisional application to which the '553 purports to claim priority, PO filed numerous patent applications concerning similar subject matter, and many of those earlier-filed applications are listed as related applications in the '553 patent. (Ex. 1001, 1:8-2:62.) During prosecution of applications claiming priority to the '615 provisional application, those earlier filed applications were relied on by the PTO for claim rejections.

In addressing those previous rejections based on its own earlier-filed subject matter, PO argued that the rejected claims included "rings" that were not disclosed in the earlier-filed applications. The claims of the '553 patent do not include any "rings," and as demonstrated in another concurrently-filed PGR petition, the challenged claims of the '553 patent are anticipated or rendered obvious by PO's

earlier-filed applications.

Similarly, during prosecution of an earlier-filed related application, PO added limitations to pending claims to overcome rejections based on *Wong*. However, the claims of the '553 patent do not include the features PO previously added in order to overcome *Wong*, and, as demonstrated below, *Wong* anticipates the challenged claims of the '553 patent.<sup>1</sup>

### II. MANDATORY NOTICES UNDER 37 C.F.R. § 42.8

#### A. Real Parties-in-Interest

Petitioner identifies Flex Logix Technologies, Inc. as the real party-ininterest.

Petitioner is also concurrently filing an additional petition for PGR of the '553 patent demonstrating that all the claims of the '553 patent are indefinite and fail to comply with the written description and enablement requirements under 35 U.S.C. § 112. However, to the extent the claims can be understood, the instant petition and another concurrently-filed prior art petition demonstrate that the claims are also unpatentable over the prior art. The additional prior art petitions are being filed out of an abundance of caution because of the statutory estoppel provisions.

# B. Related Matters

# 1. Lawsuit(s)

PO has asserted the '553 patent against Petitioner in *Konda Technologies Inc. v. Flex Logix Technologies, Inc.*, No. 5:18-cv-07581-LHK (N.D. Cal.). PO has also asserted U.S. Patent Nos. 8,269,523 ("the '523 patent"), 8,898,611 ("the '611 patent"), 9,529,958 ("the '958 patent"), and 10,050,904 ("the '904 patent") in the foregoing district court litigation.

# 2. Related Applications

The '553 patent is related to several patents and/or patent applications, as shown in the purported priority chain below:

# 3. Concurrently filed petitions

Petitioner is concurrently filing two other petitions for PGR of certain claims of the '553 patent.

## C. Counsel and Service Information

Lead counsel is Naveen Modi (Reg. No. 46,224), and Backup counsel are (1) Joseph E. Palys (Reg. No. 46,508), (2) Paul M. Anderson (Reg. No. 39,896), and (3) Quadeer A. Ahmed (Reg. No. 60,835). Service information is Paul Hastings LLP, 875 15th St. N.W., Washington, D.C., 20005, Tel.: 202.551.1700,

Fax: 202.551.1705, email: PH-FlexLogix-Konda-PGR@paulhastings.com. Petitioner consents to electronic service.

## III. PAYMENT OF FEES UNDER 37 C.F.R. § 42.15(a)

The PTO is authorized to charge all fees due at any time during this proceeding, including filing fees, to Deposit Account No. 50-2613.

#### IV. TIME FOR FILING UNDER 37 C.F.R. § 42.202

The '553 patent issued on June 19, 2018, and this Petition is being timely filed no later than the date that is nine months after the date of the grant of the '553 patent.

### V. GROUNDS FOR STANDING UNDER 37 C.F.R. § 42.204(a)

Petitioner certifies that the '553 patent is available for PGR and Petitioner is not barred or estopped from requesting PGR on the ground identified herein.

As discussed below in Section IX, the '553 patent is eligible for PGR because it has at least one claim that is not entitled to a pre-AIA filing date.

# VI. PRECISE RELIEF REQUESTED AND GROUND RAISED

## A. Claims for Which Review is Requested

Petitioner respectfully requests review of claims 1-7, 9-15, and 17-19 ("challenged claims") of the '553 patent, and cancellation of these claims as unpatentable.

#### **B.** Statutory Ground of Challenge

The challenged claims should be canceled as unpatentable on the following ground:

Ground 1: Claims 1-7, 9-15, and 17-19 are unpatentable under AIA 35 U.S.C. § 102(a)(1) as being anticipated by U.S. Patent No. 6,940,308 to Wong ("Wong") (Ex. 1008).

The earliest possible priority date for the '553 patent is September 7, 2011, which corresponds to the filing date of the '615 provisional application (Ex. 1007, 90). *Wong* issued on September 6, 2005. Thus, *Wong* is prior art at least under AIA 35 U.S.C. § 102(a)(1) with respect to the '553 patent.

Wong was considered by the Patent Office during prosecution, but Petitioner presents Wong in a new light never considered by the Office. (See infra Section XII.) For example, the prosecution history of the '553 patent does not include substantive discussion of Wong relating to patentability of the '553 patent claims, and Wong was not the basis for any claim rejections. (See generally Ex. 1004.) Here, Petitioner presents testimony from R. Jacob Baker, Ph.D., P.E. (Ex. 1002), an expert in the field of the '553 patent (Ex. 1002, ¶3-13, 18; Ex. 1003), who confirms that the relevant teachings of Wong disclose what is claimed by challenged claims 1-7, 9-15, and 17-19 of the '553 patent. (See Ex. 1002, ¶82-

221.)

Notably, a different Examiner relied upon *Wong* to reject claims in another patent application assigned to PO, namely U.S. Patent Application No. 12/601,275 ("the '275 application"), which eventually issued as U.S. Patent No. 8,269,523 ("the '523 patent). (*See* Ex. 1034, 76-103.) In response to the rejection, which concerned numerous features also recited in the clams of the '553 patent (*id.*, 78-79), PO presented arguments that mischaracterize the disclosure of *Wong* (*id.*, 48-50). (Ex. 1002, ¶83-87.) Moreover, PO amended the claims to include limitations that are not present in the claims of the '553 patent (Ex. 1035, 53-54), where the Examiner listed those features in the reasons for allowance of the amended claims in the '275 application (*id.*, 14). (Ex. 1002, ¶88-90.)

As such, consideration of *Wong* by the Patent Office during prosecution of the '553 patent should not preclude the Board from considering and adopting the ground in this petition.

#### VII. LEVEL OF ORDINARY SKILL IN THE ART

A person of ordinary skill in the art ("POSITA") at the time of the alleged invention of the '553 patent would have had a master's degree in electrical engineering or a similar field, and at least two to three years of experience with

integrated circuits and networks. (Ex. 1002, ¶18.) More education can supplement practical experience and vice versa. (*Id.*)

#### VIII. BACKGROUND

The '553 patent generally relates to switching networks that can be used to route signals between logic blocks included on an integrated circuit device such as an FPGA. (Ex. 1002, ¶¶20-50.)

#### A. The '553 Patent

The '553 patent, which matured from the U.S. Application No. 15/140,470 ("the '470 application"), acknowledges that multi-stage hierarchical networks were known and used in many applications at the time of the alleged invention, such as in "FPGA routing of hardware designs." (Ex. 1001, 2:66-3:1, 4:47-48.) The '553 patent states that known VLSI (very large scale integration) layouts for integrated circuits with such networks, such as the Benes network disclosed by *Wong* (Ex. 1008), are "inefficient and complicated." (*Id.*, 3:2-4, 3:30-36.) For instance, the '553 patent contends that prior art network layouts "require large area to implement the switches on the chip, large number of wires, longer wires, with increased power consumption, increased latency of the signal which effect the maximum clock speed of operation." (*Id.*, 3:43-48; Ex. 1002, ¶¶31-32 (citing Ex. 1040).)

The '553 patent alleges to disclose "[s]ignificantly optimized multi-stage networks, useful in wide target applications" where the "optimized multi-stage networks in each block *employ several rings* of stages of switches with inlet and outlet links." (Ex. 1001, 3:58-67 (emphasis added).) As discussed below, PO touted this concept of "rings" in the '553 patent family as an important distinction over PO's earlier patent applications, and, not surprisingly, the claims in the applications to which the '553 patent claims priority (and the originally filed claims in the '470 application itself) all include the "ring" concept. However, these "rings"—which (i) the '553 patent describes as an important aspect of the alleged optimizations to the prior art multi-stage hierarchical networks, and (ii) PO touted as an important distinction over PO's other applications—are not recited in the claims of the '553 patent. (Ex. 1002, ¶¶33-38.)

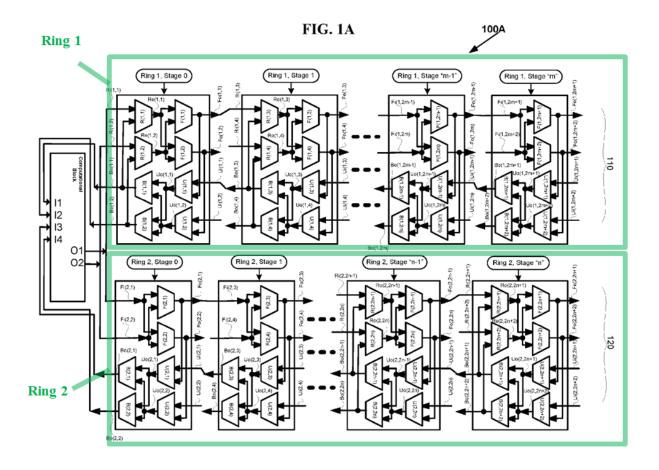

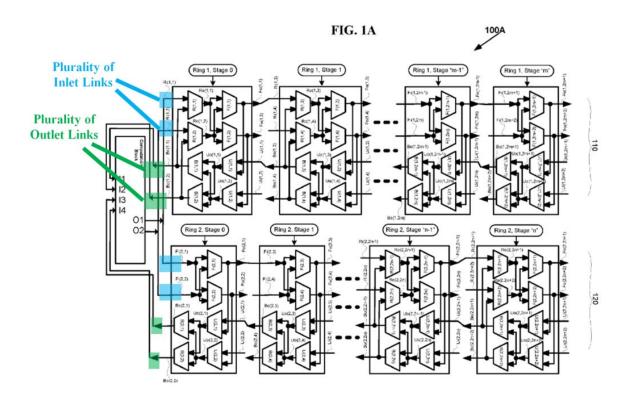

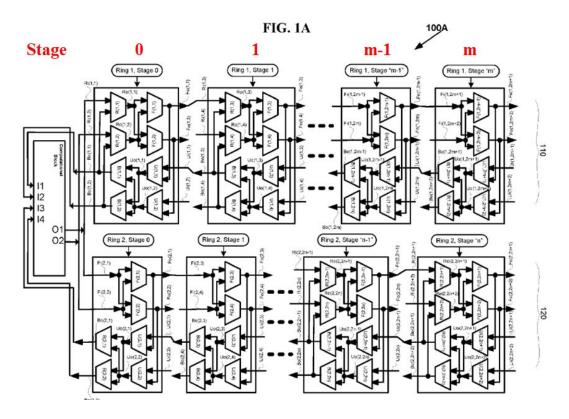

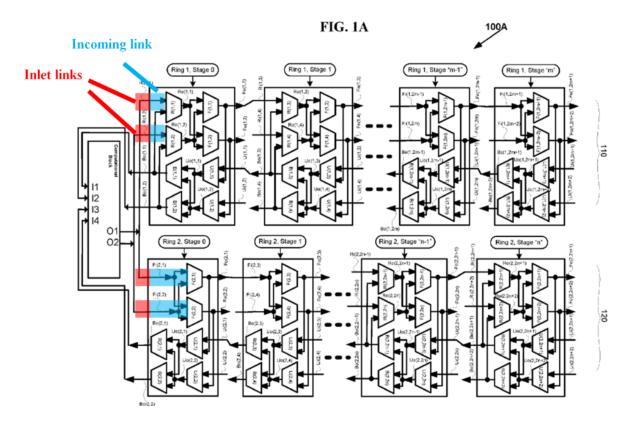

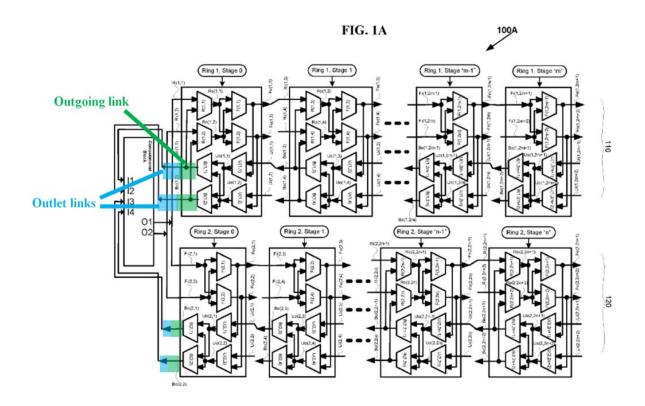

First, the '553 patent's disclosure emphasizes "rings." Each of figures 1-15 of the '553 patent illustrates, describes, or relates to the use of "rings" in a "multistage hierarchical network." (Ex. 1002, ¶33 (citing Ex. 1001, 4:42-6:22, FIGs. 1-15, 8:56-9:3, 33:26-48).) Annotated Figure 1 of the '553 patent below shows two such "rings":

(Ex. 1001, FIG.1 (annotated); Ex. 1002, ¶38.) Similarly, the figures that depict example "stages" in the '553 patent are described as illustrating portions of a "ring." (Ex. 1001, 4:56-5:3, 5:32-6:6, FIGs. 2A-2E, 9A-11C.)

Second, during prosecution of U.S. Application No. 14/199,168 ("the '168 application"), which issued as U.S. Patent No. 9,374,322 ("the '322 patent") (see supra Section II.B.2), PO explicitly defined "rings" and argued that the inclusion of such rings was a "key difference[]" with respect to PO's earlier alleged inventions disclosed in U.S. Patent No. 8,898,611 ("the '611 patent").

Current application discloses stages in rings where forward connecting links are feedback into backward connecting links through one or more multiplexers and also backward connecting links are feedback into forward connecting links through one or more multiplexers, where US Patent No. 8,898,611 discloses folded and butterfly fat tree networks where in each stage only forward connecting links are feedback into backward connecting links. . . . This is one of the key differences in the current invention which allows the total number of stages to be made small to route the same hardware circuit benchmark.

#### (Ex. 1005, 97-98 (emphases added).)

The ring concept disclosed in the current application is not a true ring, the term ring is used in the current invention since in each stage backward connecting links are feedback to forward connecting links and vice versa as opposed to only a U-turn in original multi-stage networks.

(*Id.*, 101; see also Ex. 1001, 2:33-38; Ex. 1002, ¶¶39-42.)

The claims of the '322 patent all include this "ring" concept. (Ex. 1035, 47:42-51:3.) Similarly, all of the claims of PCT Application No. PCT/US12/53814 ("the '814 PCT application") to which the '168 application claims priority also

include this "ring" concept. (Ex. 1006, 79-82 (1:3-4:23).)<sup>2</sup>.) Indeed, the originally filed claims in the '470 application also include "rings" (Ex. 1004, 286-292) and further include specific limitations consistent with the definition PO provided for a "ring" during prosecution of the '168 application. (*Id.*, 287 (82:13-18)<sup>3</sup>; Ex. 1002, ¶¶39-41.)

But in contrast to the originally filed claims in the '470 application, the issued claims in the '322 patent, and the claims in the 814 PCT application, new claims 21-40 that were added by amendment during prosecution of the '470 application and that issued as claims 1-20 in the '553 patent **do not** include "rings." (Ex. 1004, 77-84.)<sup>4</sup> In other words, issued claims 1-20 of the '553 patent

<sup>&</sup>lt;sup>2</sup> The '814 PCT application as filed had errors in pagination such that the section that includes the claims restarts the pagination at page 1. Therefore, citations to the '814 PCT application include both a page number for the exhibit as well as the page and line numbers printed on the page identified within the exhibit.

<sup>&</sup>lt;sup>3</sup> When appropriate, citations to the as-filed '470 application include page and line numbers corresponding to the application.

<sup>&</sup>lt;sup>4</sup> While the Examiner noted in an Interview Summary that the newly presented claims would be reviewed for their compliance with 35 U.S.C. § 112, the claims

are missing a feature that is not only highlighted in the specification as an alleged fundamental point of novelty, but was in fact touted by PO as a "key difference[]" between the disclosure of the '553 patent family and another patent family belonging to PO. (Ex. 1002, ¶42.)

#### B. Material Incorporated by Reference in the '553 Patent

The '553 patent attempts to incorporate by reference a list of more than 20 patents and patent applications. (Ex. 1001, 1:8-2:62; Ex. 1002, ¶37 (citing Exs. 1011-1034).) However, the incorporations by reference of these patents and applications provide no "detailed particularity [regarding] what specific material" they incorporate and do not "clearly indicate where that material is found" in the patents and applications. *Cook Biotech Inc. v. Acell, Inc.*, 460 F. 3d 1365, 1376 (Fed. Cir. 2006); *see also Paice LLC v. Ford Motor Co.*, 881 F.3d 894, 906-07 (Fed. Cir. 2018) ("To incorporate material by reference, the host document must identify with detailed particularity what specific material it incorporates and clearly indicate where that material is found in the various documents.") (internal

were subsequently allowed without any further rejections. (Ex. 1004, 51, 25-32.) The issued claims, however, do not comply with the requirements of 35 U.S.C. § 112, as demonstrated in the concurrently filed PGR petition.

citations and quotation marks omitted). Indeed, even when material is properly incorporated, "[i]t is not sufficient for purposes of the written description requirement of § 112 that the disclosure, when combined with the knowledge in the art, would lead one to speculate as to the modifications that the inventor might have envisioned, but failed to disclose." *D Three Enters., LLC v. Sunmodo Corp.*, 890 F.3d 1042, 1050 (Fed. Cir. 2018) (internal citation omitted).

The '553 patent simply identifies several patents and patent applications and states that the material is incorporated in its entirety without specifying any particular portions of the documents as being relevant. (Ex. 1001, 1:8-2:62) *Cook Biotech Inc.*, 460 F. 3d at 1376; *see also Nautilus, Inc. v. Icon Health & Fitness Inc.*, IPR2017-01408, 2018 WL 6318050, at \*20 (PTAB Dec. 3, 2018) (allowing incorporation by reference where the incorporating language provided detail regarding what was disclosed in the incorporated by reference). Moreover, many, if not all, of those incorporated patents and applications also incorporate by reference other patents and applications. (*See, e.g.*, Ex. 1007, 5-6; Ex. 1006, 1-3 (1:5-3:6).) Without providing sufficient particularity such that a POSITA would recognize what is being incorporated by reference, the material incorporated by

reference cannot be relied upon to remedy defects in the '553 patent, such as lack of written description of the claimed subject matter under 35 U.S.C. §112.<sup>5</sup>

Indeed, any such reliance would impermissibly require a POSITA to look at the different embodiments disclosed in the various patents and make unspecified combinations of elements without any guidance as to what should be combined or how such combinations should be accomplished. *D Three Enters., LLC*, 890 F.3d at 1050. Patentees' attempts to show written description support by relying on an unspecified combination of teachings from incorporated material and the disclosure of the patent have repeatedly been rejected. *Nautilus, Inc.*, IPR2017-01408, 2018 WL 6318050 at \*20-23 (rejecting PO's attempt to combine teachings from incorporated reference with disclosure of patent-at-issue in an effort to show

<sup>&</sup>lt;sup>5</sup> Elsewhere in the specification, the '553 patent describes certain prior art multistage networks disclosed in U.S. patents that were previously incorporated by reference. (Ex. 1001, 7:32-8:19.) But that portion of the specification simply notes that the alleged "optimization" techniques disclosed in the '553 patent may be implemented in certain prior art multi-stage networks, i.e., it does not rely on any concepts disclosed in the referenced U.S. patents for purposes of supporting the disclosure of the '553 patent. (*Id.*, 7:32-37.)

written description support for disputed claim limitation, noting that "obviousness is not the standard for written description"); Purdue Pharma L.P. v. Recro Tech., LLC, 694 F. App'x 794, 797 (Fed. Cir. 2017) (affirming Board's finding that claims lack written description support and stating that "[t]o the extent that Purdue contends that a person of skill in the art would isolate and combine aspects from various embodiments in the specifications (including patents incorporated by reference involving a different drug) to obtain the claimed invention [for written description support], Purdue relies upon the wrong test."); see also Lockwood v. Am. Airlines, Inc., 107 F.3d 1565, 1572 (Fed. Cir. 1997) ("It is not sufficient for purposes of the written description requirement of § 112 that the disclosure, when combined with the knowledge in the art, would lead one to speculate as to modifications that the inventor might have envisioned, but failed to disclose."); Ariad Pharms., Inc. v. Eli Lilly and Co., 598 F.3d 1336, 1352 (Fed. Cir. 2010) (en banc); Trans Video Elecs., Ltd. v. Sony Elecs., Inc., 822 F. Supp. 2d 1020, 1027 (N.D. Cal. 2011).

Therefore, in light of the lack of particularity provided by the limited description of the material incorporated by reference in the '553 patent, the patents and patent applications incorporated therein should not be considered in determining whether the claims comply with the requirements of 35 U.S.C. § 112.

Moreover, even if considered, the material incorporated by reference cannot cure the deficiencies identified herein. (*See, e.g., infra* Section IX.)

#### IX. PGR ELIGIBILITY

The PGR provisions of the Leahy-Smith America Invents Act, Pub. L. No. 112-29, 125 Stat. 284 (2011) ("AIA") apply to patents subject to the first inventor to file provisions of the AIA, i.e., patents having at least one claim with an effective filing date on or after March 16, 2013. *Grunenthal GmbH v. Antecip Bioventures II LLC*, PGR2018-00001, Paper 17 at 9-10 (May 1, 2018). A claim in a U.S. application is entitled to the benefit of the filing date of an earlier filed U.S. or PCT application if the subject matter of the claim is disclosed in the earlier filed application in accordance with the written description requirement. *PowerOasis, Inc. v. T-Mobile USA, Inc.*, 522 F.3d 1299, 1306 (Fed. Cir. 2008) (subject matter disclosed for first time in a continuation application does not receive benefit of the parent's filing date); *see also In re Gosteli*, 872 F.2d 1008, 1010–11 (Fed. Cir. 1989).

To comply with the written description requirement, the specification or earlier-filed application "must describe the invention sufficiently to convey to a person of skill in the art that the patentee had possession of the claimed invention at the time of the application, i.e., that the patentee invented what is claimed."

LizardTech, Inc. v. Earth Resource Mapping, Inc., 424 F.3d 1336, 1345 (Fed Cir. 2005); see also Lockwood, 107 F.3d at 1572; Allergan, Inc. v. Sandoz Inc., 796 F.3d 1293, 1308-09 (Fed. Cir. 2015). "The test requires an objective inquiry into the four corners of the specification from the perspective" of a POSITA. Ariad, 598 F.3d at 1351. Whether the added subject matter is an obvious variant of the disclosed subject matter is irrelevant. Lockwood, 107 F.3d at 1572.

The chart above in Section II.B.2 shows that the '553 patent relates to two applications filed prior to March 16, 2013, namely the '615 provisional application (Ex. 1007) and the '814 PCT application (Ex. 1006). The '553 patent is eligible for PGR because it has at least one claim that is not entitled to the filing date of either the '615 provisional application or the '814 PCT application ("the two pre-AIA applications"). In particular, at least claims 1, 2, 4, 9, 11, 12, and 14 of the '553 patent include subject matter that is not disclosed in the two pre-AIA applications. *PowerOasis, Inc.*, 522 F.3d at 1306; *In re Gosteli*, 872 F.2d at 1010–11. (Ex. 1002, ¶¶52-75.)

Claims 1, 2, 4, 9, 11, 12, and 14 are not entitled to a pre-March 16, 2013 filing date as discussed below, thereby confirming PGR eligibility. (Ex. 1002, ¶52.)

# A. The Two Pre-AIA Applications Do Not Support Switches Configurable By a Flip Flop (Claim 9)

Claim 9 of the '553 patent, which depends from claim 1, recites "each switch configurable by an SRAM Cell or a Flash Cell or a flip-flop." (Ex. 1001, 50:31-32 (emphasis added).) A "flip-flop" is never mentioned in the two pre-AIA applications. (See generally Exs. 1006-1007.)

The disclosure of the '814 PCT application (including the claims) is limited to describing switches as being configurable by an SRAM Cell or a Flash Cell. (Ex. 1002, ¶53.) For example, the '814 PCT application indicates that in the context of "programmable integrated circuit embodiments," switches or crosspoints that determine how inlet links and outlet links are connected can be controlled by a "programmable cell." (Ex. 1006, 75 (75:4-10).) Specifically, the '814 PCT application discloses:

In volatile programmable integrated circuit embodiments the programmable cell may be an *SRAM* (*Static Random Address Memory*) cell. In non-volatile programmable integrated circuit embodiments the programmable cell may be a *Flash memory cell*.

(Id., 75 (75:23-26) (emphases added).)

In other embodiments all the d \* d switches described in the current invention are also implemented using muxes

of different sizes controlled by *SRAM cells* or *flash cells* etc.

(*Id.*, 76 (76:4-6) (emphasis added); Ex. 1002, ¶53.)

Thus, the '814 PCT application does not disclose the "flip-flop" feature recited in claim 9. (Ex. 1002, ¶54.)

The '615 provisional application does not include any disclosure relating to a "flip-flop" and does not even describe configuring switches using SRAM and Flash cells. (See generally, Ex. 1007; Ex. 1002, ¶54.)

Thus, neither of the two pre-AIA applications conveys to a POSITA that the named inventor had possession of the features claimed at the relevant time. Neither mentions a "flip-flop" in any respect, let alone in the context of controlling a switch as recited in issued claim 9.6 Indeed, the first appearance of the term

<sup>&</sup>lt;sup>6</sup> While the two pre-AIA applications generally purport to incorporate a number of additional patents/patent applications by reference, neither pre-AIA application includes any explanation regarding the relevance of the incorporated material. Thus, as discussed above, Patent Owner cannot rely on such incorporated material in an effort to make up for the lack of disclosure in the as-filed application disclosures. (*Supra* Section VIII.B.) In any event, none of the material

"flip-flop" was in a new claim 29 (which issued as claim 9) added January 8, 2018 during prosecution of the '470 application. (Ex. 1004, 63, 69 ("2018 January 08"), 80.) Therefore, claim 9 is not entitled to an effective filing date earlier than the April 28, 2016 filing date of the '470 application.<sup>7</sup> (Ex. 1002, ¶¶55-56.)

# B. The Two Pre-AIA Applications Do Not Support Claims 1, 2, 4, 11, 12, and 14

Claim 4 of the '553 patent depends from claim 2, which in turn depends from claim 1. Similarly, claim 14 depends from claim 12, which in turn depends from claim 11. Each of claims 1, 2, 4, 11, 12, and 14 is not supported by the two pre-AIA applications, as discussed below. (Ex. 1002, ¶57-75.)

incorporated by reference supports the claimed "flip-flop" features. (Ex. 1002,  $\P55, \text{ n.6.}$ )

<sup>7</sup> The '168 application, which is a post-AIA application, includes essentially the same disclosure as the '814 PCT application and the '470 application. (Ex. 1002, ¶55.) Thus, the '168 application also does not disclose the "flip-flop" feature. (*Id.*)

Claim 1 of the '553 patent recites in part:

forward connecting links comprising ... zero or more cross links connected from a switch in a stage in a subnetwork to a switch in the same numbered stage in one or more other subnetworks ...

backward connecting links comprising ... zero or more cross links connected from a switch in a stage in a subnetwork to a switch in the same numbered stage in one or more other subnetworks

(Ex. 1001, 49:27-40 (emphases added).)

To the extent the claims can be understood, claim 1 includes forward and backward connecting links that include *cross links* between switches connected from a switch in a stage in a subnetwork to a switch in the *same numbered stage* in one or more other subnetworks. (*Id.*) Claim 2 adds that those *cross links* are implemented as vertical links only, or horizontal links only, or both vertical links and horizontal links. (Ex. 1001, 49:41-45.) Claim 4 further limits the *cross links* that are horizontal links to either being of "substantially of equal length in the entire two-dimensional grid of rows and columns" or being "of a *hop length h*" "where " $h \ge 0$ ." (*Id.*, 49:60-50:2.) Claim 4 also limits the cross links that are vertical links to either being of "substantially of equal length in the entire two-

dimensional grid of rows and columns" or being "of a hop length v" "where " $v \ge 0$ ." (Id.; Ex. 1002, ¶¶57-58.)

As set forth below, there is no disclosure of "forward connecting links" or "backward connecting links" that are "cross links" "connected from a switch in a stage in a subnetwork to a switch in the *same numbered stage* in one or more other subnetworks" in the two pre-AIA applications, let alone disclosure of any such links that have the additional features recited in claims 2 and 4. (Ex. 1002, ¶59.)

#### 1. Claim 1

The first appearance of a "cross link" "connected from a switch in a stage in a subnetwork to a switch in the same numbered stage in one or more other subnetworks" was on January 8, 2018 when claim 21 (which eventually issued as claim 1) was added during prosecution of the '470 application. (Ex. 1004, 69 ("2018 January 08"), 77-78; see also id., 61-62; Ex. 1001, 48:62-49:40.) But the two pre-AIA applications do not provide written description support for the "cross links" features of claim 1. (Ex. 1002, ¶60-61.)

For example, outside of the Abstract<sup>8</sup> and the material incorporated by reference<sup>9</sup> in the specification of the '814 PCT application, the only mention of "cross links" in the specification is in the "Summary of the Invention":

The optimized multi-stage networks with their VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in another sub-integrated circuit block or inlet links of switches in the another stage of a ring in the same sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice-versa.

(Ex. 1006, 5 (5:3-8) (emphases added); Ex. 1002, ¶62.)

<sup>&</sup>lt;sup>8</sup> The Abstract's referral to networks that "employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block" is substantively the same as that contained in the cited portion. (Ex. 1006, Abstract, 5:3-8.)

<sup>&</sup>lt;sup>9</sup> See supra n.6.

This isolated reference to "cross links" is limited to "cross links" connected "from switches in a stage" to switches in "another stage." <sup>10</sup> The same is true with respect to the "cross links" recited in the claims of the '814 PCT application, i.e., they recite "cross links connecting from a switch in a stage ... to a switch in another stage," where the cross links in the '814 PCT application are included in

<sup>&</sup>lt;sup>10</sup> To the extent that PO argues that "another stage" should be understood broadly such that it encompasses "a same stage" or "a different stage," such an argument would be inconsistent with the use of the "same" and "another" terms in the '553 patent and its family. For example, the '814 PCT application states "another stage" of a ring in the same or another sub-integrated circuit block" (Ex. 1006, 83 (1:14-15) (emphasis added)), thereby making clear that "another" is used to mean "a different" and not "the same or a different." The '814 PCT application further states the cross links "are connected to either inlet links of switches in the another stage of a ring in another sub-integrated circuit block or inlet links of switches in the another stage of a ring in the same sub-integrated circuit block." (Id., 5 (5:3-8) (emphases added).) Therefore, PO explicitly distinguishes between "same" and "another" in the context of the sub-integrated circuit blocks in the '553 patent and its family. (Ex. 1002, ¶63.)

forward and backward connecting links that connect "from switches in lower stage to switches in the *immediate succeeding higher stage*" and "from switches in higher stage to switches in the *immediate preceding lower stage*," respectively. (Ex. 1006, 80 (2:4-13) (emphasis added).) Thus, the '814 PCT application does not describe any "cross link" that is "connected from a switch in a stage in a subnetwork to a switch in the *same numbered stage* in one or more other subnetworks" as recited in claim 1. (Ex. 1002, ¶64.)

Outside of the material incorporated by reference, <sup>11</sup> the '615 provisional application does not include any disclosure relating to a "cross link." (*See generally* Ex. 1007; Ex. 1002, ¶65.)

Accordingly, claim 1 is not entitled to an effective filing date earlier than the April 28, 2016 filing date of the '470 application.<sup>12</sup> (Ex. 1002, ¶65.)

#### 2. Claim 2

Claim 2 depends from claim 1 and recites "said cross links between switches of stages in any two said subnetworks are connected as either vertical links only, or

<sup>&</sup>lt;sup>11</sup> See supra n.6.

<sup>&</sup>lt;sup>12</sup> The '168 application also does not disclose the "same numbered stage" feature of claim 1. (Ex. 1002, ¶64; *see also supra* n.7.)

horizontal links only, or both vertical links and horizontal links." (Ex. 1001, 49:41-45.) The first appearance of the above-noted features of claim 2 in conjunction with the "cross links" of claim 1 was in newly added claim 22 (which issued as claim 2) submitted January 8, 2018 during prosecution of the '470 application. (Ex. 1004, 69 ("2018 January 08"), 79; see also id., 62; Ex. 1001, 49:41-45; Ex. 1002, ¶67.)

As discussed above, no "cross links" having the characteristics recited in claim 1 are disclosed in the two pre-AIA applications. (*See supra* Section IX.B.1.) Thus, assuming the recitation of "said cross links" in claim 2 modifies the "zero or more cross links" recited in claim 1, it logically follows that these pre-AIA applications cannot support such "cross links" as further modified by claim 2. Therefore, claim 2 is not entitled to an effective filing date earlier than the April 28, 2016 filing date of the '470 application.<sup>13</sup> (Ex. 1002, ¶66.)

<sup>-</sup>

<sup>&</sup>lt;sup>13</sup> The '168 application also does not disclose the features of claim 2. (Ex. 1002, ¶66; *see also supra* n.7.)

#### 3. Claim 4

# a) The "Substantially of Equal Length" Feature Is Not Supported

Claim 4 depends from claim 2 and recites "said horizontal links between switches in two said stages are *substantially of equal length* and said vertical links between switches in two said stages are *substantially of equal length* in the entire two-dimensional grid of rows and columns." (Ex. 1001, 49:60-65.) The first appearance of the above-noted features of claim 4 in conjunction with the above-discussed features of claims 1 and 2 was in newly added claim 24 (which issued as claim 4) submitted January 8, 2018 during prosecution of the '470 application. (Ex. 1004, 69 ("2018 January 08"), 78; *see also id.*, 62; Ex. 1001, 49:60-50:2; Ex. 1002, ¶68.)

As discussed above, no "cross links" as recited in claim 1 or as further limited by claim 2 are disclosed in the two pre-AIA applications. (*See supra* Sections IX.B.1-2.) Thus, assuming the recitation of "said horizontal links" and "said vertical links" in claim 4 further modifies the horizontal and vertical links recited in claim 2, which in turn modify the "zero or more cross links" recited in claim 1, it logically follows that these pre-AIA applications cannot support such "cross links" as further modified by claim 4. Therefore, claim 4 is not entitled to

an effective filing date earlier than the April 28, 2016 filing date of the '470 application.<sup>14</sup> (Ex. 1002, ¶69.)

## b) The "Hop Length" Features Are Not Supported

Claim 4 also recites "said horizontal links between switches in two said stages are substantially of a *hop length* h and said vertical links between switches in two said stages are substantially of a *hop length* v where  $h \ge 0$  and  $v \ge 0$ ." (Ex. 1001, 49:60-50:2.) As is the case for the other features recited in claim 4, assuming this feature regarding "hop length" further modifies the "cross links" as recited in claim 1 and further limited by claim 2, no such cross links are disclosed in the two pre-AIA applications. (Ex. 1002, ¶70; see supra Section IX.B.1.)

Moreover, as discussed below, the claimed ranges of hop length " $h \ge 0$  and  $v \ge 0$ " are not supported by the two pre-AIA applications in any context. Indeed, prior to the filing of claim 24 during prosecution of the '470 application, there was no recitation of a hop length of "0" and only hop lengths  $\ge 1$  were previously described or claimed. (Ex. 1002, ¶71.)

<sup>&</sup>lt;sup>14</sup> The '168 application does not disclose the features of claim 4. (Ex. 1002, ¶69; see also supra n.7.)

The first appearance of a horizontal or vertical "hop length" "\geq 0" in relation to any link was in claim 24 (now claim 4) submitted January 8th, 2018 during prosecution of the '470 application. (Ex. 1004, 69 ("2018 January 08"), 79; Ex. 1001, 49:60-50:2.) But the specification of the '470 application explicitly states that each of the horizontal and vertical hop lengths is a positive number, therefore making a hop length of 0, which is included in the claimed ranges, outside the scope of the disclosure of the '470 application. (Ex. 1004, 253 (48:14-18) ("'Vx' denotes an external vertical hop wire ... with 'x' vertical hop length, where 'x' is a positive integer."), 256 (51:10-14) ("'Hx' denotes an external horizontal hop wire ... with 'x' horizontal hop length where 'x' is a positive integer."); 259 (54:6-8) ("In general the hop length of an external vertical hop wire can be any positive number. Similarly, the hop length of an external horizontal hop wire can be any positive number.") (emphases added).) Zero is not a positive number and therefore is not included in the disclosed ranges of hop-length. (Ex. 1002, ¶72.)

The same description of hop lengths being limited to positive numbers is present in the '814 PCT application (Ex. 1006, 47 (47:1-5), 49 (49:26-30), 52 (52:23-25)) and the '615 provisional application (Ex. 1007, 35 (31:9-13), 38 (34:5-9), 41 (37:3-5)). None of the applications as filed, including the '470 application

itself, mentions a "hop length" of "0," let alone such a hop length in the context of the "cross links" set forth in claim 1. (Ex. 1002, ¶73.)

Accordingly, claim 4 is not entitled to an effective filing date earlier than the April 28, 2016 filing date of the '470 application.<sup>15, 16</sup> (Ex. 1002, ¶74.)

### 4. Claims 11, 12, and 14

Claims 11, 12, and 14 recites features analogous to those discussed above with respect to claims 1, 2, and 4, respectively. For example, just like claim 1, claim 11 recites "zero or more cross links connected from a switch in a stage in a subnetwork to a switch in the same numbered stage in one or more other subnetworks." (Ex. 1001, 51:14-17, 51:25-28; *see also id.*, 49:30-33, 49:37-40.) Similarly, like claim 2, claim 12 recites that "zero or more cross links connected from a switch in a stage in a subnetwork to a switch in the same numbered stage in one or more other subnetworks." (*Id.*, 51:32-36; *see also id.*, 49:41-45.) And claim 14, like claim 4, recites cross links that are horizontal links are of "substantially of equal length in the entire two-dimensional grid of rows and

<sup>&</sup>lt;sup>15</sup> See supra n.6.

<sup>&</sup>lt;sup>16</sup> The '168 application does not disclose the features of claim 4. (Ex. 1002, ¶73; see also supra n.7.)

columns" or being "of a hop length h" "where " $h \ge 0$ ." (Id., 51:51-52:7; see also id., 49:60-50:2.) Claim 14, like claim 4, also recites that cross links that are vertical links are of "substantially of equal length in the entire two-dimensional grid of rows and columns" or being "of a hop length v" "where " $v \ge 0$ ." (Id., 51:51-52:7; see also id., 49:60-50:2; Ex. 1002, ¶75.) Thus, for at least the same reasons discussed above, neither of the two pre-AIA applications conveys to a POSITA that the inventor had possession of the above-noted features set forth in claims 11, 12, and 14 at the relevant time. Accordingly, claims 11, 12, and 14 are not entitled to an effective filing date earlier than the April 28, 2016 filing date of the '470 application. (Supra Sections IX.B.1-3; Ex. 1002, ¶75.)

## C. AIA Applicability

As discussed above, at least claims 1, 2, 4, 9, 11, 12, and 14 of the '553 patent include subject matter that is not disclosed by a pre-March-16-2013 application. As such, the '553 patent is eligible for PGR. Further, because at least claims 1, 2, 4, 9, 11, 12, and 14 are not entitled to a priority date prior to March 16,

<sup>&</sup>lt;sup>17</sup> See supra n.6.

<sup>&</sup>lt;sup>18</sup> The '168 application does not disclose the features of claims 11, 12, and 14. (Ex. 1002, ¶75; see also supra n.7.)

2013, every claim of the '553 patent is subject to the first-to-file provisions of § 102(a). See MPEP at § 2159.02.

#### X. CLAIM CONSTRUCTION

In a post grant review, claims are construed in accordance with the ordinary and customary meaning of such claims as understood by one of ordinary skill in the art and the prosecution history pertaining to the patent. 37 C.F.R. § 42.200(b). In particular, claim terms are generally given their "ordinary and customary meaning," that is, "the meaning that the term would have to a POSITA in question at the time of the invention, i.e., as the effective filing date of the patent application." *Phillips v. AWH Corp.*, 415 F.3d 1303, 1313 (Fed. Cir. 2005) (*en banc*). In the case that "the specification . . . reveal[s] a special definition given to a claim term by the patentee that differs from the meaning it would otherwise possess . . . . the inventor's lexicography governs." *Id.* at 1316 (internal citation omitted).

The Board only construes the claims when necessary to resolve the underlying controversy. *Toyota Motor Corp. v. Cellport Systems*, Inc., IPR2015-00633, Paper 11 at 16 (August 14, 2015). Petitioner submits that for purposes of this proceeding, no term requires construction. (Ex. 1002, ¶51.)

#### XI. EARLIEST EFFECTIVE FILING DATE OF THE '553 PATENT

As discussed above, the two pre-AIA applications and the post-AIA '168 application do not provide adequate written description support for at least the "same numbered stage" feature in independent claims 1 and 11. (Supra Sections IX.B.1, IX.B.4.) Claims 2-10 and 12-20 depend from independent claims 1 and 11, and consequently are also not supported by the two pre-AIA applications and the post-AIA '168 application.

Thus, for purposes of this proceeding, the challenged claims are not entitled to an effective filing date any earlier than the April 28, 2016 filing date of the '470 application.

#### XII. DETAILED EXPLANATION OF THE GROUND

A. Ground 1: *Wong* Anticipates Claims 1-7, 9-15, and 17-19 *Wong* discloses the features of claims 1-7, 9-15, and 17-19.

#### 1. Claim 1

Wong discloses each and every feature of claim 1. (Ex. 1002, ¶¶92-176.)

# a) "A network implemented in a non-transitory medium comprising"

To the extent the preamble is limiting, *Wong* discloses a network implemented in a non-transitory medium. (Ex. 1002, ¶¶92-100.) For example, *Wong* discloses a programmable network ("network") implemented in a Field

Programmable Gate Array (FPGA) integrated circuit ("non-transitory medium"). (Ex. 1008, 1:14-17, 1:59-61, 4:12-16.) (Ex. 1002, ¶92; see also id., ¶¶76-81.)

In particular, *Wong* discloses that "[t]he present invention relates to integrated circuit interconnections and, in particular, to the interconnection architecture of FPGA (Field Programmable Gate Array) integrated circuits." (Ex. 1008, 1:14-17.) *Wong* further discloses that "FPGAs are integrated circuits whose functionalities are designated by the users of the FPGA" where the "user programs the FPGA (hence the term, 'field programmable') to perform the functions desired by the user." (*Id.*, 1:18-21; Ex. 1002, ¶¶92-94.)

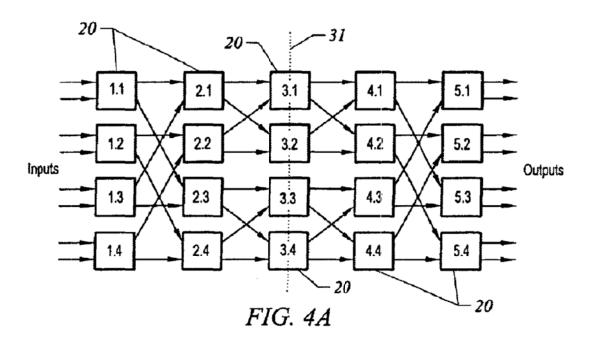

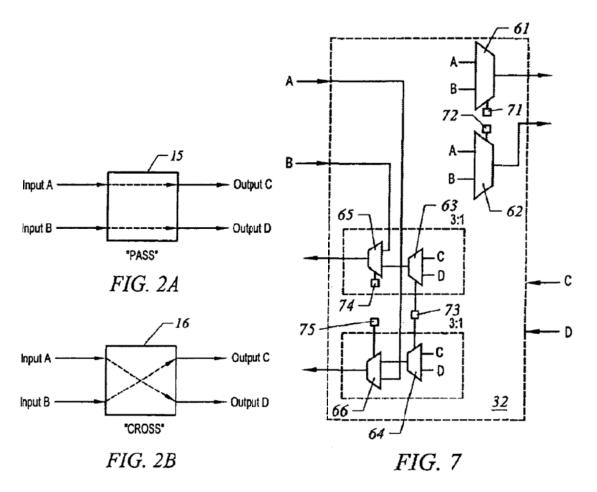

Wong's programmable networks include a plurality of programmable switches that are arranged in hierarchical levels. (Ex. 1008, 1:61-64, 2:7-8.) Figure 4A of Wong shows an 8x8 Benes network that is made up of a plurality of switches 20. (Id., 2:41-43, 5:4-6.)

(*Id.*, FIG. 4A; Ex. 1002, ¶95.)

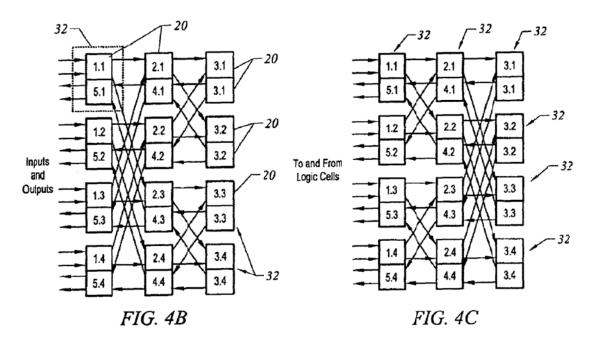

The 8x8 network shown in figure 4A can be folded in the middle (along dotted line 31 shown in figure 4A) to produce a folded Benes network, examples of which are shown in figures 4B and 4C. (Ex. 1008, 2:41-46, 6:58-67; Ex. 1002, ¶96.)

(Ex. 1008, FIGs. 4B (left), 4C (right, where the interconnections have been inverted by level); Ex. 1002, ¶96.)

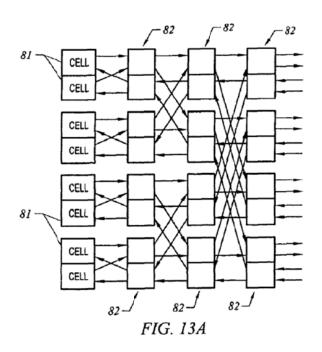

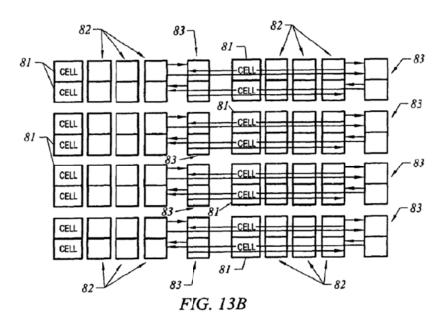

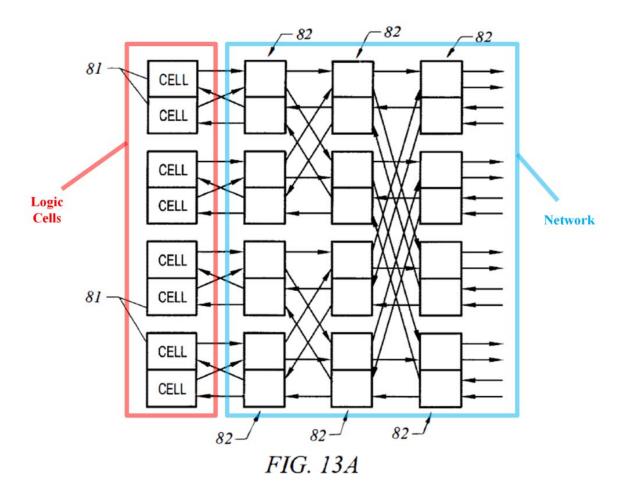

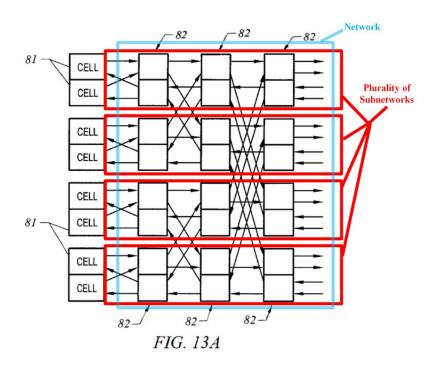

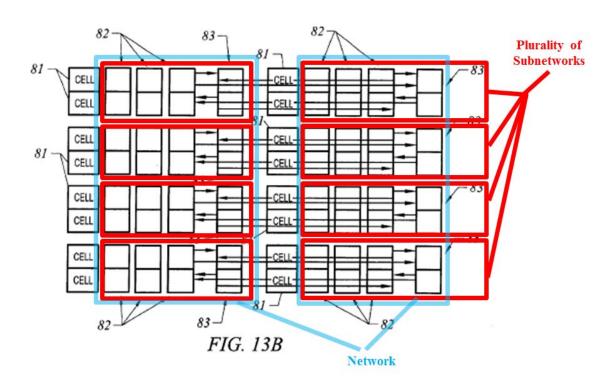

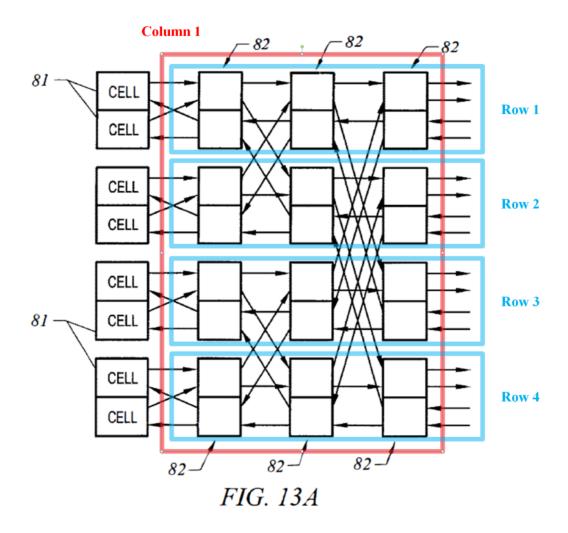

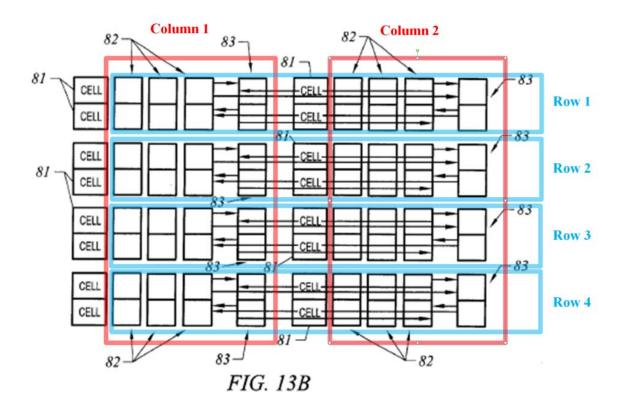

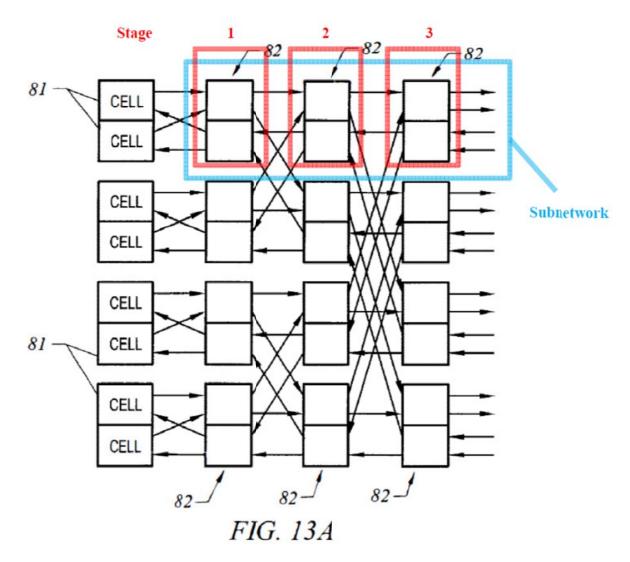

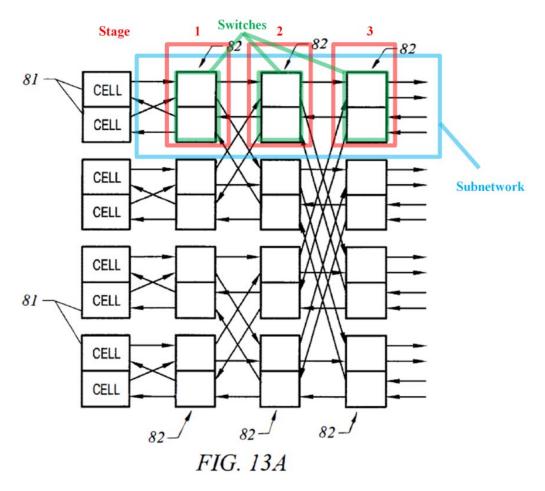

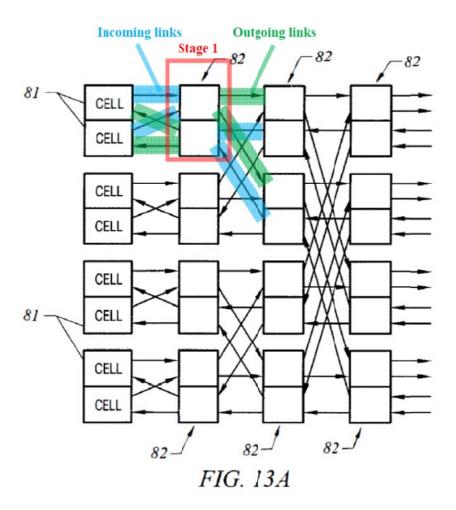

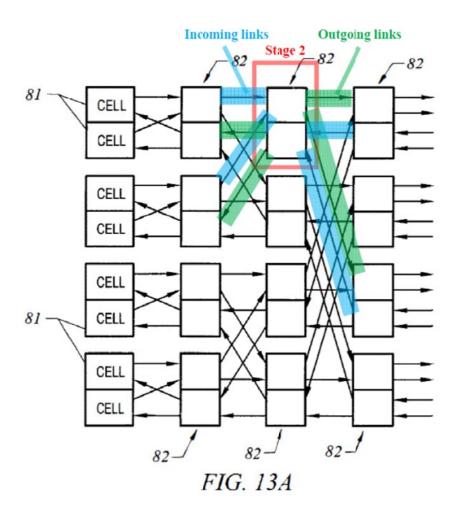

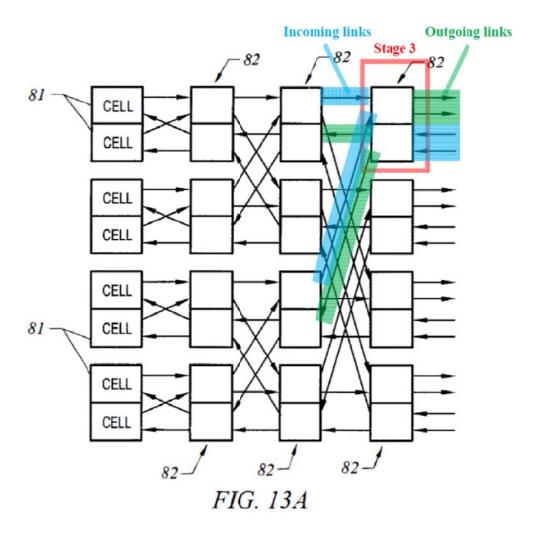

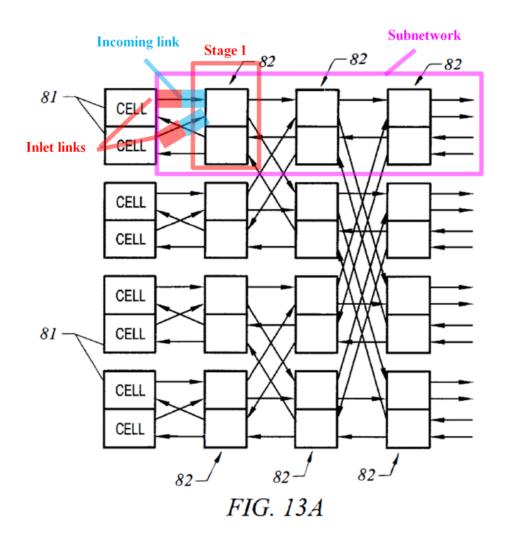

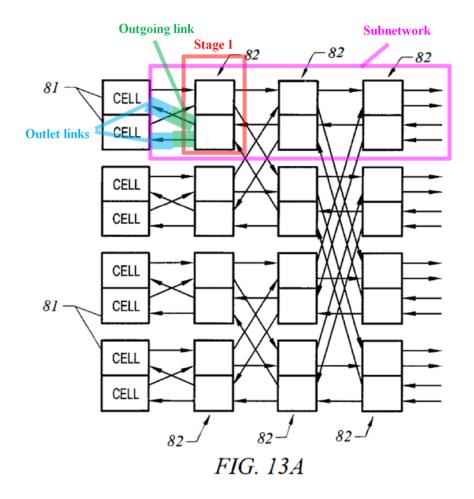

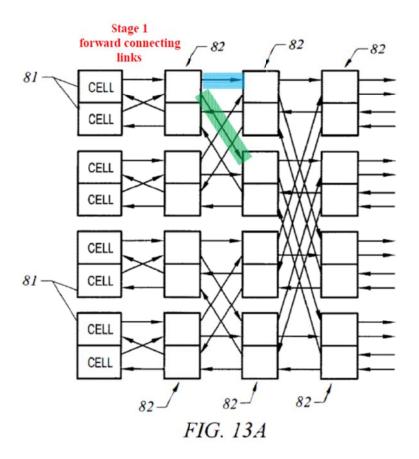

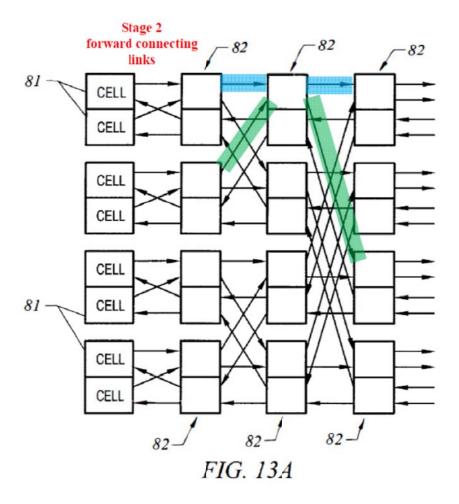

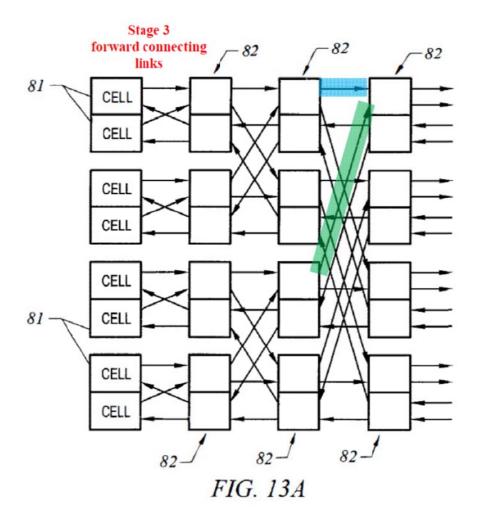

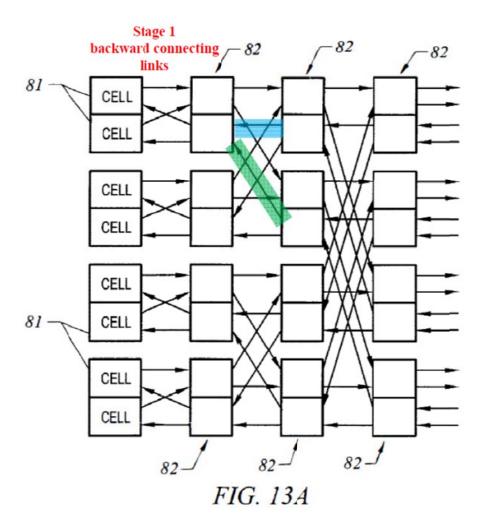

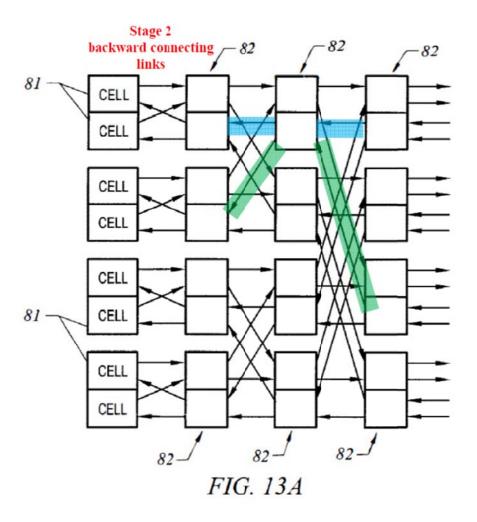

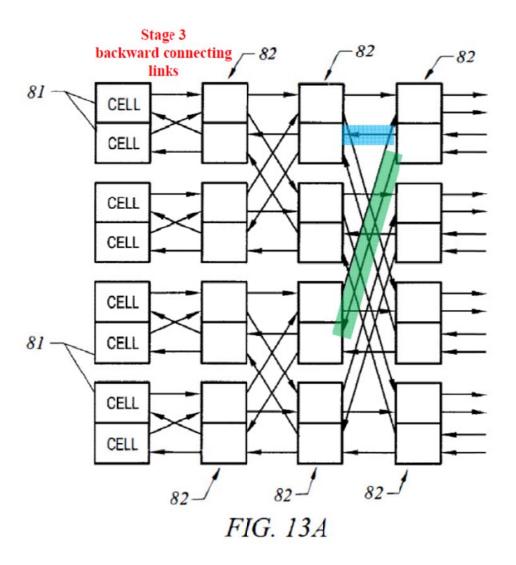

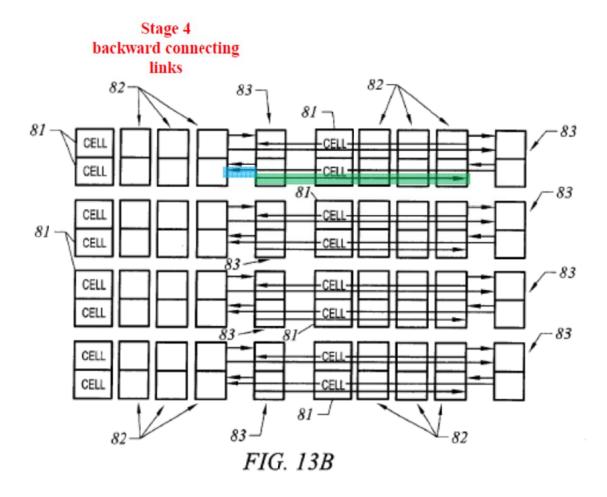

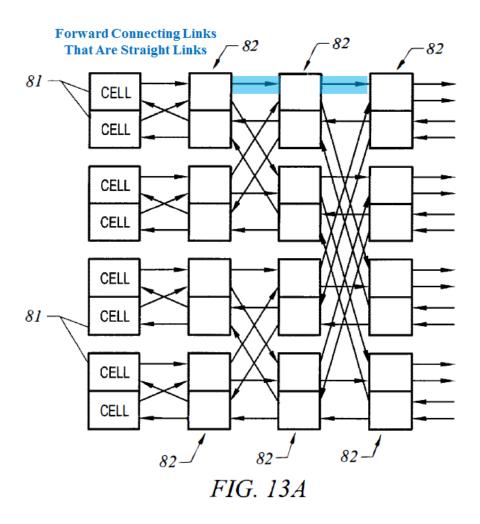

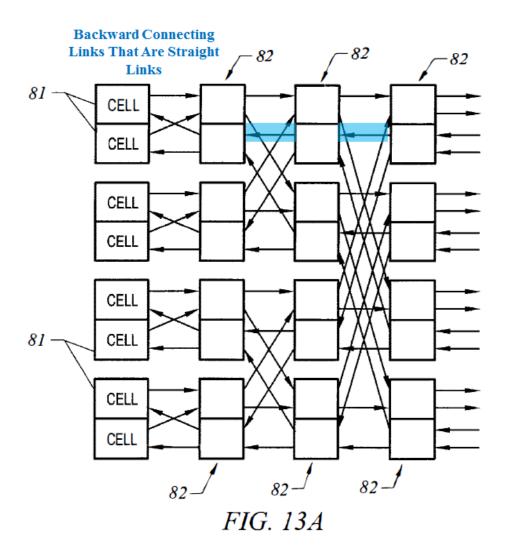

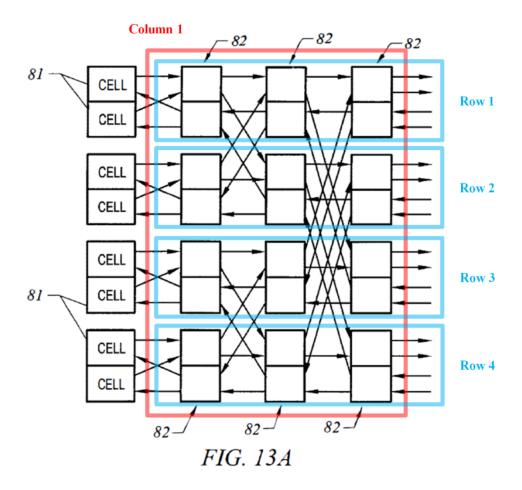

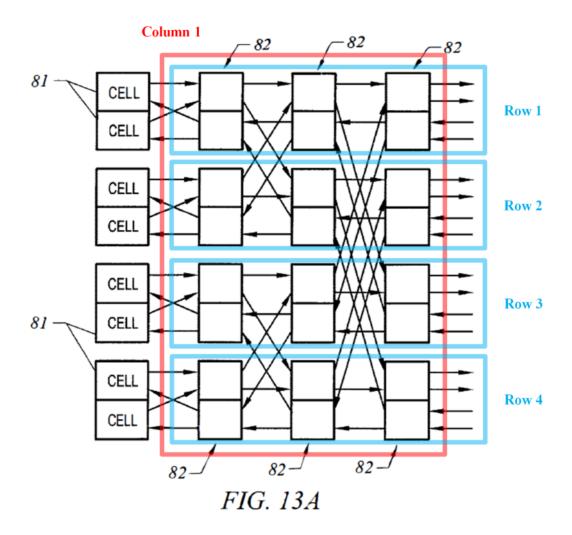

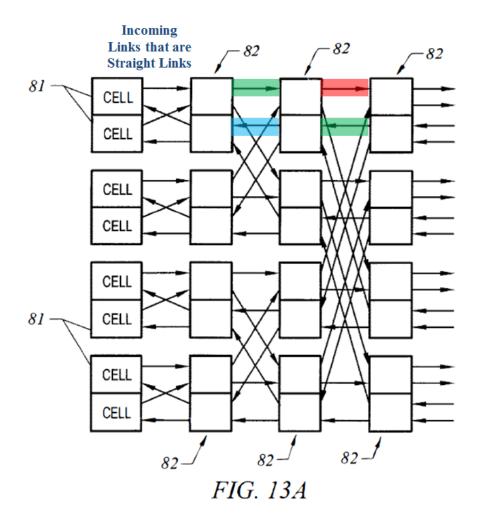

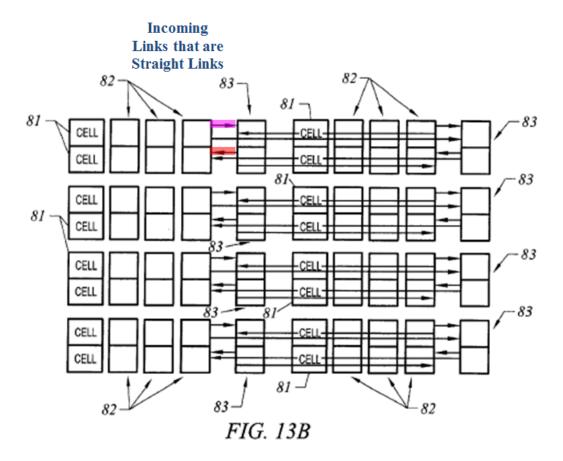

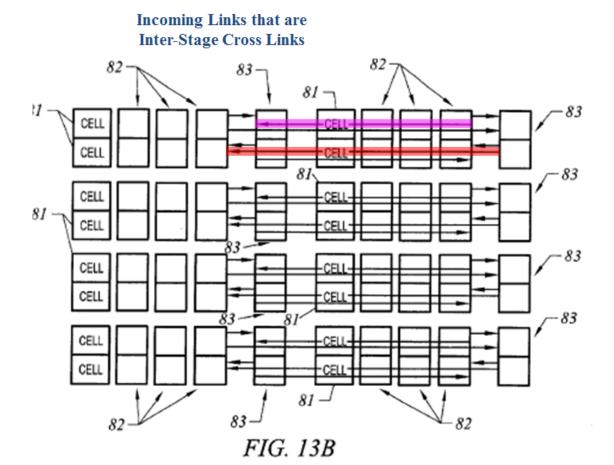

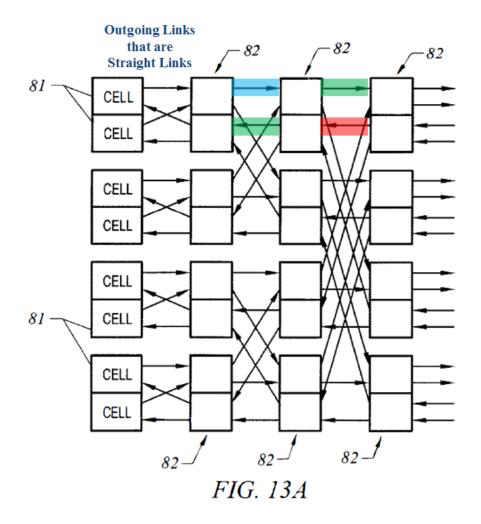

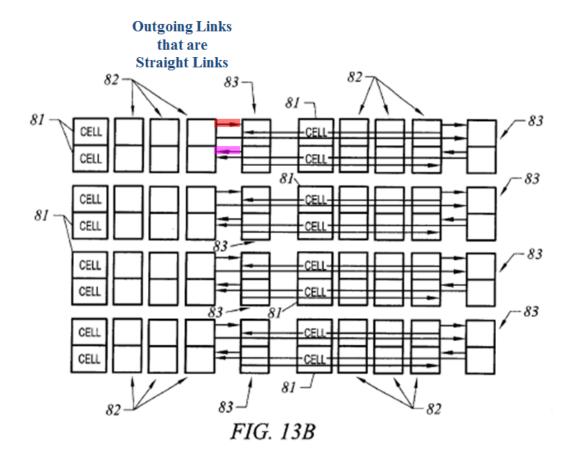

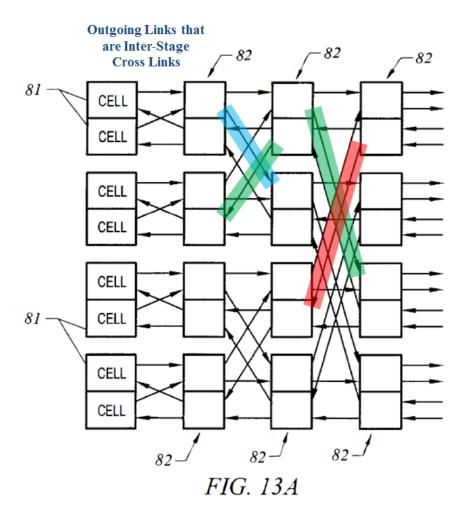

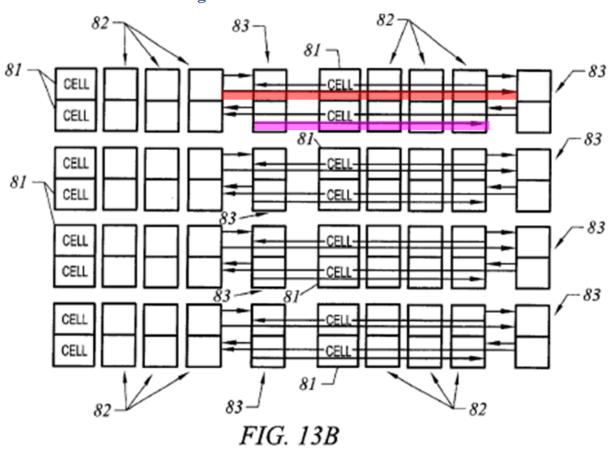

Figures 13A and 13B of *Wong* build on the disclosure corresponding to figure 4C and illustrate exemplary floorplan layouts of FPGAs that use the Benes network topology such as that shown in figure 4C. (Ex. 1008, 3:7-10, FIGs. 13A-13B.) For example, referring to Figure 13A, *Wong* discloses that "[w]ith the previous illustrations of the Benes interconnect network and columns of logic cells added, the layout is nearly completed." (*Id.*, 13:19-22; Ex. 1002, ¶97.)

(Ex. 1008, FIG. 13A.)

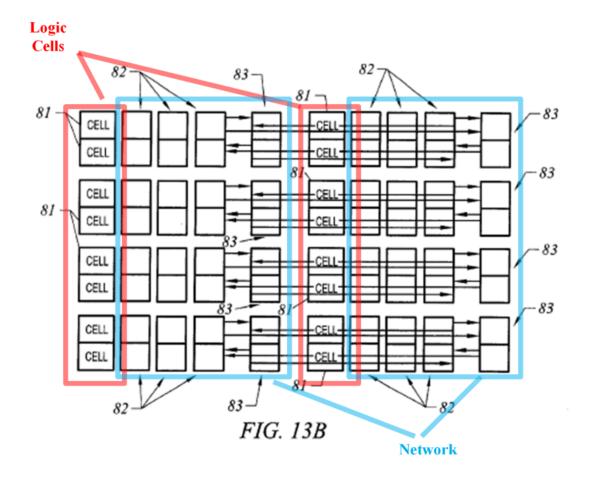

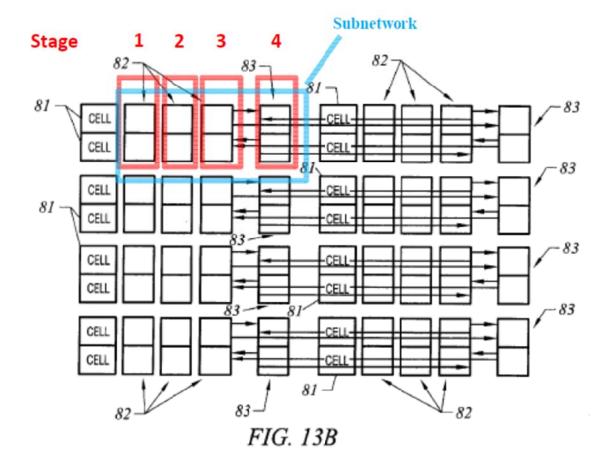

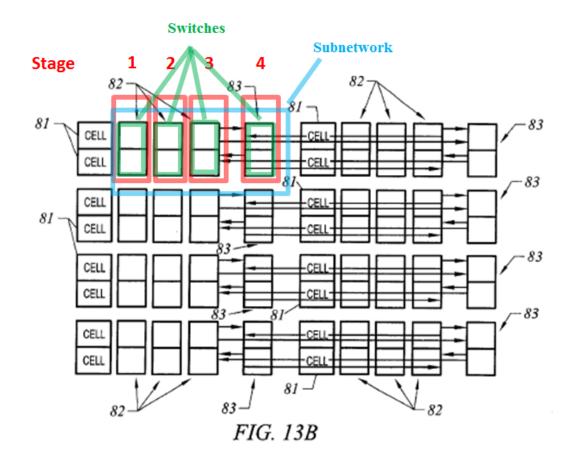

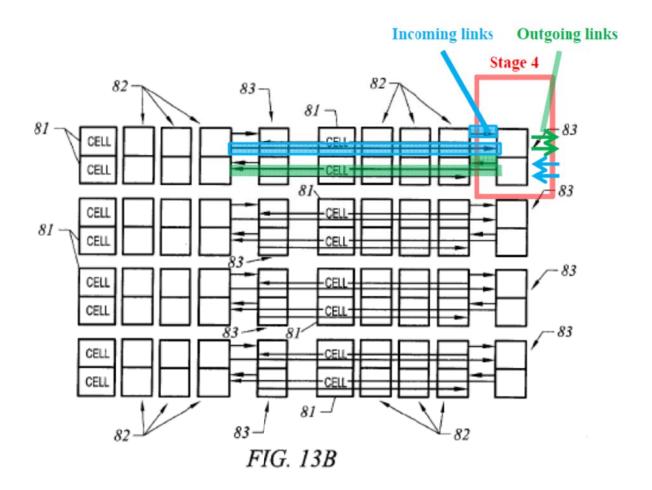

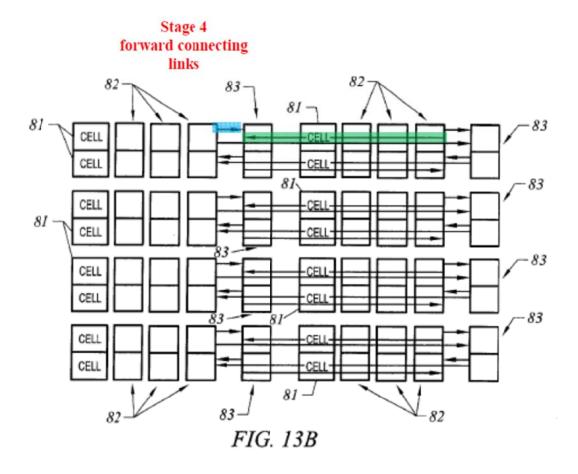

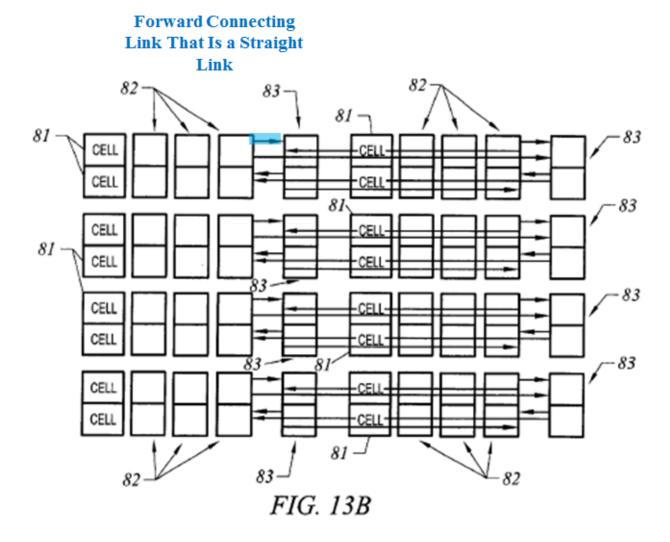

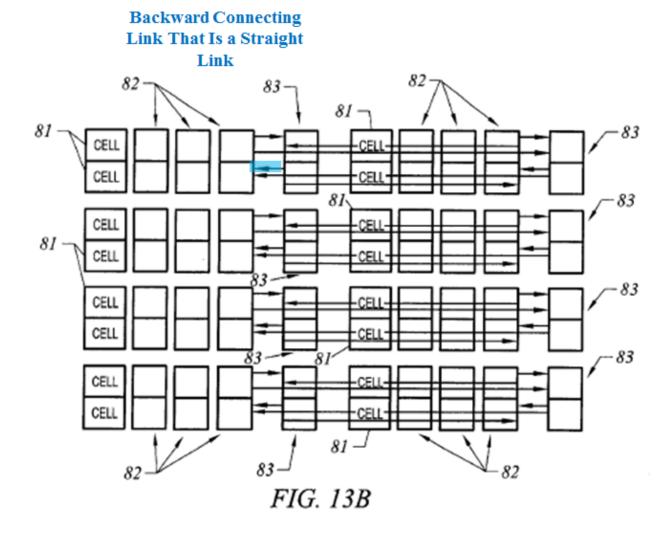

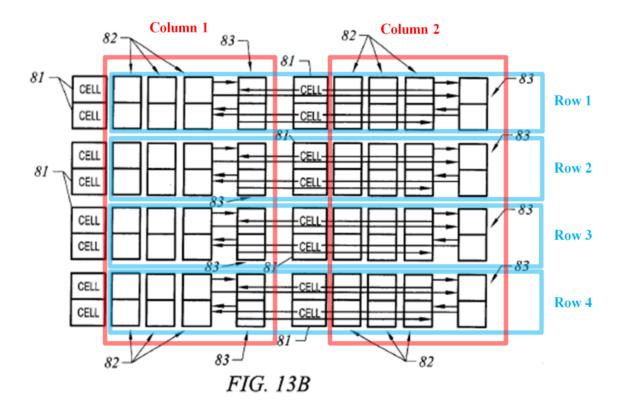

Figure 13B shows a multi-column embodiment that includes two instantiations of the layout shown in figure 13A. (*Id.*, 3:7-10; 13:36-38.)

(Id., FIG. 13B; Ex. 1002, ¶98.)

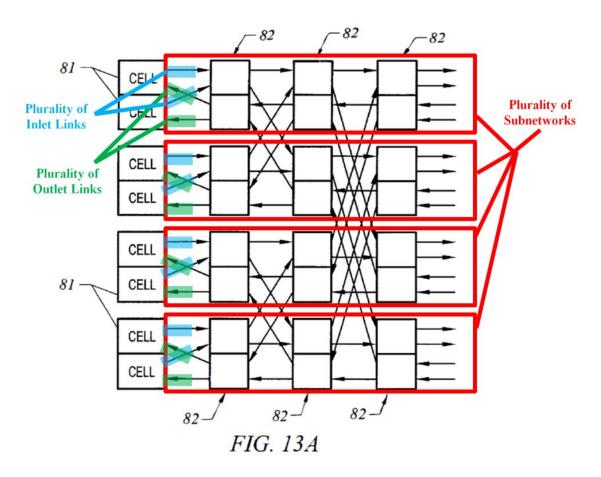

In figures 13A and 13B, logic cells 81 are included in the FPGA along with switch cells 82 and 83. (Ex. 1008, 13:22-23, 13:36-38.) An annotated version of Figure 13A below demonstrates one example of the interconnection between the logic cells 81 and the network made up of switches 82.

(Id., FIG. 13A (annotated); Ex. 1002, ¶99.)

Similarly, an annotated version of Figure 13B of *Wong* below illustrates the interconnection between the logic cells 81 and the network that includes switches 82 and 83.

(Ex. 1008, FIG. 13B (annotated); Ex. 1002, ¶100.)

Thus, *Wong* discloses a programmable network ("network") implemented in an FPGA integrated circuit ("non-transitory medium").

# b) "a plurality of subnetworks and a plurality of inlet links and a plurality of outlet links,"

### (1) a plurality of subnetworks

Wong discloses a plurality of subnetworks. (Ex. 1002, ¶101-102.) For example, Wong discloses that the network shown in figure 13A below includes a plurality of rows of switches 82 ("subnetworks"). Similarly, figure 13B of Wong includes a plurality of subnetworks. As shown below, each subnetwork in figure 13A includes a row of switches 82, while each subnetwork in figure 13B includes one more switch 83 in addition to the switches 82.

(Ex. 1008, FIG. 13A (annotated to show a plurality of subnetworks); Ex. 1002, ¶101.)

(Ex. 1008, FIG. 13B (annotated to show plurality of subnetworks); Ex. 1002, ¶102.)

# (2) a plurality of inlet links and a plurality of outlet links

Wong discloses a plurality of inlet links and a plurality of outlet links. (Ex. 1002, ¶¶103-109.) For example, as shown below in an annotated version of figure 13A, Wong discloses that its above-noted subnetworks include inputs ("plurality of inlet links") (highlighted in blue) that are coupled to inputs of the switches 82 in the first stage of the network and outputs ("plurality of outlet links") (highlighted

in green) that are coupled to outputs of the switches 82 in the first stage of the network.

(Ex. 1008, FIG. 13A (annotated to show inlet links (blue) and outlet links (green)); Ex. 1002, ¶103.)<sup>19</sup>

<sup>19</sup> The embodiment of figure 13B of *Wong* includes two instantiations of the network shown in figure 13A of *Wong* and therefore includes the same inlet links

Petition for Post Grant Review Patent No. 10,003,553

Indeed, the inlet links and outlet links in *Wong* are consistent with the disclosure of the '553 patent, which discloses that the outlet links correspond to the outputs of the rings and the inlet links correspond to the inputs of the rings. (Ex. 1001, 9:4-26, FIG. 1A.) Notably, as discussed below with respect to claim element 1[f], the inlet links and outlet links are connected to one or more of said incoming links of a switch in the network, and therefore the highlighted arrows shown in the diagrams of the '553 patent and *Wong* represent both the inlet links of the subnetwork and the incoming links of the switch. (*See infra* Section XII.A.1(f).)

and outlet links shown above with respect to figure 13A. (Ex. 1008, 13:36-38; Ex. 1002, ¶104.)

(Ex. 1008, FIG. 1A (annotated to show inlet links (blue) and outlet links (green); Ex. 1002, ¶104.)

# c) "said plurality of subnetworks arranged in a twodimensional grid of rows and columns; and"

Wong discloses the plurality of subnetworks arranged in a two-dimensional grid of rows and columns. (Ex. 1002, ¶¶110-116.) For example, figures 13A and 13B of Wong disclose the "plurality of subnetworks" identified above with respect to claim element 1[b](1), where the plurality of subnetworks are arranged in rows and columns. (Supra Section XII.A.1(b)(1); Ex. 1008, FIGs. 13A-13B.)

Figure 13A of *Wong* shows the subnetworks and logic cells arranged in four rows in one column.

(Ex. 1008, FIG. 13A (annotated); Ex. 1002, ¶110.)

While the claim recites "a two-dimensional grid of rows and columns," a POSITA would have understood the claim to encompass a two-dimensional grid where the subnetworks are only laid out in a single dimension (e.g., one row or one column). (Ex. 1002, ¶111.) Such an understanding is supported by claim 10,

which depends from claim 1 and recites "said plurality of subnetworks are implemented in a single dimension." (Ex. 1001, 50:49-50.) A POSITA would recognize in light of claim 10 that the scope of claim 1 would broadly encompass a two-dimensional grid where the subnetworks are laid out in a single dimension (e.g., one row or one column). (Ex. 1002, ¶111.) Therefore, Figure 13A, which shows subnetworks in multiple rows in a single column, discloses the subject claim element. (*Id.*)

Moreover, *Wong*'s Figure 13B embodiment discloses subnetworks arranged in multiple rows and multiple columns.

(Ex. 1008, FIG. 13B (annotated); Ex. 1002, ¶112.)

As shown, Figure 13B discloses an embodiment with subnetworks arranged in four rows and two columns. (Ex. 1008, 13:36-38; *see also id.*, 3:7-10; Ex. 1002, ¶113.) *Wong* also discloses further expansion of the network in both the column and row directions. (Ex. 1002, ¶114 (citing Ex. 1008, 13:38-40, 13:44-46).)

To the extent Patent Owner argues that that the "two-dimensional grid of rows and columns" corresponds to a physical layout of the subnetworks on an integrated circuit, *Wong*'s subnetworks in figures 13A-13B satisfy such a

requirement as they correspond to the physical arrangement of the subnetworks on the integrated circuit. (Ex. 1008, 13:13-16, 13:19-22; Ex. 1002, ¶¶115-116.)

d) "each subnetwork comprising y stages, where  $y \ge 1$ ; and"

Wong discloses each subnetwork comprising y stages, where  $y \ge 1$ . (Ex. 1002, ¶117-119.) For example, figures 13A and 13B of Wong disclose that each of the "plurality of subnetworks" identified above with respect to claim element 1[b](1) includes three or four stages (i.e.,  $y \ge 1$ ). (Supra Section XII.A.1(b)(1); Ex. 1008, FIGs. 13A-13B; Ex. 1002, ¶117-118.)

For example, in Figure 13A of *Wong*, each subnetwork includes three stages (each switch 82 corresponds to a "stage").

(Ex. 1008, FIG. 13A (annotated); Ex. 1002, ¶117.)

Similarly, as shown in Figure 13B, each subnetwork includes four stages.

(Ex. 1008, FIG. 13B (annotated); Ex. 1002, ¶118.)

Indeed, *Wong's* disclosure of the subnetworks including a plurality of stages is consistent with the disclosure of the '553 patent, which discloses a "partial multi-stage hierarchical network" where each ring (e.g., rings 110 and 120) consists of m+1 or n+1 stages, where "m" and "n" are positive integers. (Ex. 1001, 8:57-9:3; Ex. 1002, ¶119.)

(Ex. 1001, FIG. 1A (annotated); Ex. 1002, ¶119.)

e) "each stage comprising a switch of size  $d_i \times d_o$ , where  $d_i \ge 2$  and  $d_o \ge 2$  and each switch of size  $d_i \times d_o$  having  $d_i$  incoming links and  $d_o$  outgoing links; and"

Wong discloses this claim element. (Ex. 1002, ¶¶120-128.) As an initial matter, a POSITA would have understood this claim element to require that each stage includes a switch that has at least two incoming links and at least two outgoing links (e.g., at least a 2x2 switch with at least two inputs and two outputs). (Ex. 1002, ¶¶120-121.) This is because in the relevant art of integrated circuits, "a switch of size  $d_i \times d_o$ " in the context of "where  $d_i \geq 2$  and  $d_o \geq 2$  and each switch of

size d<sub>i</sub> x d<sub>o</sub> having d<sub>i</sub> incoming links and d<sub>o</sub> outgoing links" would have informed a POSITA about the input/output configuration of the switch, and not the actual area (i.e. physical size) of the switch. (*Id.*) As explained below, in the embodiments shown in figures 13A and 13B of *Wong*, each stage includes a switch that is 2x2 or larger, and therefore, *Wong* discloses this claim element.

First, as discussed above and illustrated below, each stage of *Wong's* subnetworks of figures 13A-13B includes a switch (e.g., switch 82 or 83). (*Supra* Sections XII.A.1(b)(1),(d).)

(Ex. 1008, FIG. 13A (annotated); Ex. 1002, ¶122.)

(Ex. 1008, FIG. 13A (annotated); Ex. 1002, ¶123.)

Each of the switches 82, 83 shown in figures 13A and 13B of *Wong* is at least a 2x2 switch that has at least 2 inputs and 2 outputs. (Ex. 1002, ¶124.) For instance, as shown in the annotated versions of figure 13A of *Wong* below, each switch cell 82 in each of stages 1-3 includes four inputs (" $d_i$  incoming links") and four outputs (" $d_o$  outgoing links").

(Ex. 1008, FIG. 13A (annotated to show incoming links (blue) and outgoing links (green) for stage 1); Ex. 1002, ¶125.)

(Ex. 1008, FIG. 13A (annotated to show incoming links (blue) and outgoing links (green) for stage 2); Ex. 1002, ¶125.)

(Ex. 1008, FIG. 13A (annotated to show incoming links (blue) and outgoing links (green) for stage 3); Ex. 1002, ¶125.)

Similarly, each switch in each of stages 1-4 of the subnetworks shown in figure 13B has four incoming links and four outgoing links as figure 13B includes two instantiations of figure 13A with the addition of another stage of switches 83. (Ex. 1008, 3:7-10; 13:36-38; Ex. 1002, ¶126.)

(Ex. 1008, FIG. 13B (annotated to show incoming links (blue) and outgoing links (green) for stage 4); Ex. 1002, ¶126.)<sup>20</sup>

<sup>&</sup>lt;sup>20</sup> The annotations add the incoming links and outgoing links corresponding to the primary I/O of the FPGA in Figure 13B (shown as blue and green arrows to the right of switch 83). (Ex. 1008, 13:42-43.) As such, switches 83 are also 4x4 switches that have four incoming links and four outgoing links. (Ex. 1002, ¶127.)

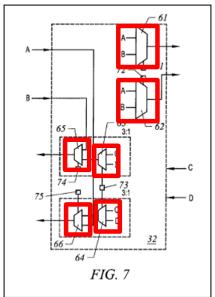

Furthermore, a POSITA would have understood that the 4x4 switches shown in figures 13A and 13B can be made up of sets of 2x2 switches such as those shown in figures 2A and 2B of *Wong* or can be a combined switch such as that shown in figure 7. (Ex. 1008, 5:4-6 ("The building block of the described Benes network is the 2x2 (2 input, 2 output) switch 20, having operations illustrated in FIGS. 2A and 2B."); 5:4-6, 5:26-29, 7:6-8, 8:10-15, 8:65-9:3, 13:19-22, 13:33-36.)

(Id., FIGs. 2A, 2B, 7; Ex. 1002, ¶128.)

f) "Said inlet links are connected to one or more of said incoming links of a said switch of a said stage of a said subnetwork, and said outlet links are connected to one of said outgoing links of a said switch of a said stage of a said subnetwork; and"

To the extent this claim element can be understood by a POSITA, *Wong* discloses the claim element. (Ex. 1002, ¶¶129-137.) For example, as discussed above, the inlet links correspond to the inputs to the subnetworks and the outlet links correspond to the outputs of the subnetworks in figures 13A-13B of *Wong*. (*Supra* Section XII.A.1(b)(2).)

As shown in annotated Figure 13A of *Wong* below, the inlet links corresponding to the inputs of the subnetworks are each connected to a corresponding incoming link of a switch 82 in the first stage of a subnetwork.

(Ex. 1008, FIG. 13A (annotated); Ex. 1002, ¶130.)

As shown in annotated figure 1A of the '553 patent below, the "inlet links" connected to the "incoming links" highlighted in figure 13A of *Wong* above are

consistent with the "inlet links" connected to the "incoming links" disclosed by the '553 patent.  $(Ex.1002, \$131.)^{21}$

\_

To the extent Patent Owner argues or the Board determines that the inlet links and outlet links are not included in the subnetworks, which is inconsistent with claim element 1[g](1), *Wong* provides the same disclosure as would be relied upon to support the inlet links and outlet links outside of the subnetwork in the '553 patent. For example, if Patent Owner argues that the "inlet links" correspond to the outputs (O1 and O2) of the computational block and the "outlet links" correspond to the inputs (I1-I4) shown on the left side of figure 1A of the '553 patent, *Wong* discloses the logic cells 81 have similar outputs and inputs that would constitute inlet links and outlet links. (Ex.1002, ¶136-137.)

(Ex. 1001, FIG. 1A (annotated); Ex. 1002, ¶131.)

Similarly, as shown in figure 13A of *Wong*, the outlet links corresponding to the outputs of the subnetworks are each connected to a corresponding outgoing link of a switch in the first stage of a subnetwork of the network.

(Ex. 1008, FIG. 13B (annotated); Ex. 1002, ¶132.)

As shown in annotated figure 1A of the '553 patent below, the "outlet links" connected to the "outgoing links" highlighted in figure 13A of *Wong* above are consistent with the "outlet links" connected to the "outgoing links" disclosed by the '553 patent. (Ex.1002, ¶133.)

(Ex. 1001, FIG. 1A (annotated); Ex. 1002, ¶133.)

While not explicitly shown in figure 13B, a POSITA would have understood that the connections between the logic cells and first-stage switches of the subnetworks are also present since figure 13B includes two instantiations of the circuitry and connections shown in figure 13A. (Ex. 1008, 13:36-38; Ex. 1002, ¶134.)

As demonstrated above, in the embodiments shown in figure 13A and 13B of *Wong*, each inlet link in the plurality of inlet links is coupled to an incoming link of a switch in the first stage of a subnetwork, and each outlet link in the plurality of

outlet links is coupled to an outgoing link of a switch in the first stage of a subnetwork. (Ex. 1002, ¶135.) Therefore, to the extent this claim feature can be understood, *Wong* discloses "said inlet links connected to one or more of said incoming links of a said switch of a said stage of a said subnetwork, and said outlet links are connected to one of said outgoing links of a said switch of a said stage of a said subnetwork." (*Id.*)

g) "each subnetwork of the plurality of subnetworks may or may not be comprising the same number of said inlet links and may or may not be comprising the same number of said outlet links; each subnetwork of the plurality of subnetworks may or may not be comprising the same number of said stages; each stage may or may not be comprising the same number of switches; and each switch in each stage may or may not be of the same size, each multiplexer in each stage may or may not be of the same size and"

Wong discloses this claim element. (Ex 1002, ¶138-151.) As an initial matter, this entire claim element does not further limit claim 1 because it simply recites several optional features. MPHJ Tech. Invs., LLC v. Ricoh Ams. Corp., 847 F.3d 1363, 1379 (Fed. Cir. 2017) ("As a matter of linguistic precision, optional elements do not narrow the claim because they can always be omitted.") (citing In re Johnston, 435 F.3d 1381, 1384 (Fed. Cir. 2006)). As discussed separately below, since each subpart of claim element 1[g] imposes an optional "may or may

not be" feature onto the network components such as number of inlet/outlet links, number of stages, number of switches, etc., *Wong* discloses this claim element regardless of the optional features imposed thereon. (Ex. 1002, ¶¶138-151.)

(1) each subnetwork of the plurality of subnetworks may or may not be comprising the same number of said inlet links and may or may not be comprising the same number of said outlet links;

Wong discloses claim element 1[g](1) as long as it discloses that each subnetwork of the plurality of subnetworks has some inlet links and some outlet links, since the claim does not require that each of the subnetworks have the "same number" of inlet and/or outlet links. (Ex. 1002, ¶139.) And since it has already been shown above that each subnetwork includes inlet and outlet links, Wong discloses this claim element. (Supra Section XII.A.1(b)(2).) Indeed, Wong discloses that its subnetworks in figures 13A-13B include the same number of inlet and outlet links. (Ex. 1002, ¶140.)

(2) each subnetwork of the plurality of subnetworks *may or may not be comprising* the same number of said stages;

Similarly, *Wong* discloses claim element 1[g](2) as long as it discloses that each subnetwork has a stage, since the claim does not require that each subnetwork have the "same number" of stages. (Ex. 1002, ¶141.) And since it has already

been shown above that each subnetwork includes a stage, *Wong* discloses this claim element. (*Supra* Section XII.A.1(d).) Indeed, *Wong* discloses that its subnetworks in figures 13A-13B include the same number of stages. (Ex. 1002, ¶¶142-143.)

# (3) each stage *may or may not be comprising* the same number of switches; and

Similarly, *Wong* discloses claim element 1[g](3) as long as it discloses that each stage has a switch, since the claim does not require that each stage have the "same number" of switches. (Ex. 1002, ¶144.) And since it has already been shown above that each stage includes a switch, *Wong* discloses this claim element. (*Supra* Sections XII.A.1(d)-(e).) Indeed, *Wong* discloses that each stage in figures 13A-13B includes the same number of switches. (Ex. 1002, ¶¶145-146.)

## (4) each switch in each stage *may or may not be* of the same size,

Similarly, *Wong* discloses claim element 1[g](4) as long as it discloses a switch in each stage, since the claim does not require that each switch have the "same size." (Ex. 1002, ¶147.) And since it has already been shown above that *Wong* discloses a switch in each stage, *Wong* discloses this claim element. (*Supra* Section XII.A.1(e).) Indeed, *Wong* discloses that each switch in figures 13A-13B is of the same size. (Ex. 1002, ¶148.)

### (5) each multiplexer in each stage *may or may not* be of the same size.

With respect to claim element 1[g](5), there is no antecedent basis for "each multiplexer." To the extent the claim element can be understood, this claim feature does not require each stage to include a multiplexer because nowhere in claim 1 is it specified that each stage includes any multiplexers. Therefore, this claim element is disclosed by Wong. (Ex. 1002, ¶149.) Claim 1 does not require each stage to include a multiplexer, and therefore Wong discloses this claim feature whether or not it discloses each stage including a multiplexer. For example, if there are no multiplexers in the stages, then "each multiplexer in each stage may or may not be of the same size" is true as no multiplexers are present and therefore the further condition applied to those non-existent multiplexers ("may or may not be of the same size") is also true. If there are multiplexers in each stage, then they are either "of the same size" or they are not, and the additional condition is also satisfied. (*Id*.)

In any event, even assuming the claim requires each stage to include a multiplexer, *Wong* discloses that each of its stages in figures 13A-13B includes a "multiplexer." (Ex. 1002, ¶150.) While it is irrelevant whether the multiplexer(s) in each stage are of the same size, *Wong* discloses that each of the subnetworks in

figures 13A and 13B includes switches of the same size and further discloses that multiplexers of the same size can be used for switches of the same size. (*Id.*, ¶151.) For at least these reasons, *Wong* discloses each multiplexer in each stage may or may not be of the same size. (Ex. 1002, ¶¶149-151.)

h) "Said incoming links and outgoing links in each switch in each stage of each subnetwork comprising a plurality of forward connecting links connected from switches in a stage to switches in another stage in same said subnetwork or another said subnetwork, and also comprising a plurality of backward connecting links connected from switches in a stage to switches in another stage in same subnetwork or another said subnetwork; and"