UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

KINGSTON TECHNOLOGY COMPANY, INC., Petitioner,

v.

MEMORY TECHNOLOGIES, LLC Patent Owner

Case No.: To Be Assigned U.S. Patent No. 8,307,180

# PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 8,307,180

Mail Stop "**Patent Board**" Patent Trial and Appeal Board United States Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

# **TABLE OF CONTENTS**

| I.    | INTRODUCTION AND STATEMENT OF RELIEF REQUESTED (37 C.F.R. §42.22(a)) |                                                                   |  |

|-------|----------------------------------------------------------------------|-------------------------------------------------------------------|--|

| II.   | MANDATORY NOTICES (37 C.F.R. §42.8(A)(1))1                           |                                                                   |  |

|       | A.                                                                   | Real Party-In-Interest (37 C.F.R. §42.8(b)(1))1                   |  |

|       | B.                                                                   | Identification of Related Matters (37 C.F.R. §42.8(b)(2))2        |  |

|       | C.                                                                   | Counsel and Service Information (37 C.F.R. §§42.8(b)(3) & (b)(4)) |  |

|       | D.                                                                   | Payment of Fees (37 C.F.R. §42.103)                               |  |

| III.  | REQ                                                                  | UIREMENTS FOR <i>INTER PARTES</i> REVIEW                          |  |

| IV.   | A PE                                                                 | RSON OF ORDINARY SKILL IN THE ART4                                |  |

| V.    | BAC                                                                  | KGROUND OF THE TECHNOLOGY4                                        |  |

| VI.   | OVERVIEW OF THE '180 PATENT                                          |                                                                   |  |

|       | A.                                                                   | Summary of the Claimed Subject Matter                             |  |

|       | B.                                                                   | The '180 Patent Prosecution History7                              |  |

| VII.  | CLA                                                                  | IM CONSTRUCTION10                                                 |  |

|       | A.                                                                   | Legal Overview10                                                  |  |

|       | B.                                                                   | Claim Terms                                                       |  |

|       |                                                                      | 1. "predefined access profile"11                                  |  |

|       |                                                                      | 2. "configuring access"                                           |  |

|       |                                                                      | 3. "usage"14                                                      |  |

| VIII. | SUM                                                                  | MARY OF THE PRIOR ART14                                           |  |

|       | A.                                                                   | CompactFlash14                                                    |  |

|     | B.  | Unite | ed States Patent No. 7,478,248 (Ziv)                                                                                   | 19  |

|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------|-----|

|     | C.  | Unite | ed States Patent No. 6,681,304 (Vogt)                                                                                  | 21  |

|     | D.  | Unite | ed States Patent No. 6,279,114 (Toombs)                                                                                | 21  |

|     | E.  | Unite | ed States Patent No. 7,409,489 (Sinclair)                                                                              | 23  |

|     | F.  |       | ed States Patent Publication No. 2006/00220054<br>(mias)                                                               | .26 |

| IX. | GRO | UNDS  | FOR CHALLENGE                                                                                                          | 26  |

|     | A.  |       | UND 1: Claims 1-3, 5, 16-19, 21, 32 and 35 are<br>tentable under 35 U.S.C. § 102 over <i>CompactFlash</i>              | .27 |

|     |     | 1.    | Independent Claim 1                                                                                                    | 27  |

|     |     | 2.    | Dependent Claim 2                                                                                                      | 38  |

|     |     | 3.    | Dependent Claim 3                                                                                                      | 40  |

|     |     | 4.    | Dependent Claim 5                                                                                                      | 40  |

|     |     | 5.    | Dependent Claim 16                                                                                                     | 41  |

|     |     | 6.    | Independent Claim 17                                                                                                   | .42 |

|     |     | 7.    | Dependent Claim 18                                                                                                     | .44 |

|     |     | 8.    | Dependent Claim 19                                                                                                     | .44 |

|     |     | 9.    | Dependent Claim 21                                                                                                     | .45 |

|     |     | 10.   | Dependent Claim 32                                                                                                     | 45  |

|     |     | 11.   | Independent Claim 35                                                                                                   | 46  |

|     | B.  |       | UND 2: Claims 1, 5, 16, 17, 21, 32, and 35 are tentable under 35 U.S.C. § 103(a) in view of <i>Ziv</i> and <i>Vogt</i> | .47 |

|     |     | 1.    | Independent Claim 1                                                                                                    | 48  |

|     |     | 2.    | Dependent Claim 5                                                                                                      | 58  |

|     |     |       |                                                                                                                        |     |

|    | 3.              | Dependent Claim 16                                                                                                            | 60 |

|----|-----------------|-------------------------------------------------------------------------------------------------------------------------------|----|

|    | 4.              | Independent Claim 17                                                                                                          | 61 |

|    | 5.              | Dependent Claim 21                                                                                                            | 63 |

|    | 6.              | Dependent Claim 32                                                                                                            | 63 |

|    | 7.              | Independent Claim 35                                                                                                          | 63 |

| C. |                 | OUND 3: Claims 2-3, and 18-19 are unpatentable under 35<br>C. § 103(a) in view of <i>Ziv</i> , <i>Vogt</i> , and <i>Toomb</i> | 65 |

|    | 1.              | Dependent Claim 2                                                                                                             | 65 |

|    | 2.              | Dependent Claim 3                                                                                                             | 68 |

|    | 3.              | Dependent Claim 18                                                                                                            | 69 |

|    | 4.              | Dependent Claim 19                                                                                                            | 69 |

| D. | unpa            | OUND 4: Claims 1-3, 5, 16-19, 21, 32, and 35 are tentable under 35 U.S.C. § 103(a) in view of <i>Sinclair</i> and <i>mbs</i>  | 69 |

|    | 1.              | Independent Claim 1                                                                                                           |    |

|    | 2.              | Dependent Claim 2                                                                                                             |    |

|    | 3.              | Dependent Claim 3                                                                                                             |    |

|    | 4.              | Dependent Claim 5                                                                                                             |    |

|    | 5.              | Dependent Claim 16                                                                                                            |    |

|    | 6.              | Independent Claim 17                                                                                                          |    |

|    | 7.              | Dependent Claim 18                                                                                                            |    |

|    |                 | 1                                                                                                                             |    |

|    | 8.              | Dependent Claim 19                                                                                                            | 81 |

|    |                 | Dependent Claim 19<br>Dependent Claim 21                                                                                      |    |

|    | 8.<br>9.<br>10. | Dependent Claim 19<br>Dependent Claim 21<br>Dependent Claim 32                                                                | 81 |

Х.

|     | 11.  | Independent Claim 35                                                                                                          | 81 |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| E.  |      | OUND 5: Claims 12, 13, 28, 29 are unpatentable under 35<br>C. § 103 in view of <i>CompactFlash</i> and <i>Elhamias</i>        | 82 |

|     | 1.   | Dependent Claim 12                                                                                                            | 82 |

|     | 2.   | Dependent Claim 13                                                                                                            | 85 |

|     | 3.   | Dependent Claim 28                                                                                                            | 85 |

|     | 4.   | Dependent Claim 29                                                                                                            | 85 |

| F.  |      | OUND 6: Claims 12, 13, 28, 29 are unpatentable under 35<br>C. § 103 in view of <i>Ziv</i> , <i>Vogt</i> , and <i>Elhamias</i> | 86 |

|     | 1.   | Dependent Claim 12                                                                                                            | 86 |

|     | 2.   | Dependent Claim 13                                                                                                            | 88 |

|     | 3.   | Dependent Claim 28                                                                                                            | 88 |

|     | 4.   | Dependent Claim 29                                                                                                            | 88 |

| CON | CLUS | SION                                                                                                                          | 89 |

# **Table of Authorities**

# <u>Cases</u>

| Crestron Electronics Inc. v. Intuitive Building Controls Inc.,<br>Case IPR2015-01460, slip op. (PTAB Jan. 14, 2016) | 16 |

|---------------------------------------------------------------------------------------------------------------------|----|

| Memory Technologies, LLC v. Kingston Technology Co., Inc.,<br>8:18-cv-00171 (C.D. Cal.)                             | 2  |

| Phillips v. AWH Corp.,<br>415 F.3d 1303 (Fed. Cir. 2005)                                                            |    |

# <u>Statutes</u>

| Code of Federal Regulations      |   |

|----------------------------------|---|

| Title 37 Section 42.10(b)        | 2 |

| Title 37 Section 42.103          |   |

| Title 37 Section 42.104(b)       |   |

| Title 37 Section 42.108(c)       |   |

| Title 37 Section 42.22(a)        |   |

| Title 37 Section 42.24(a)(1)(i)  |   |

| Title 37 Section 42.6(a)(2)(ii)  |   |

| Title 37 Section 42.6(a)(2)(iii) |   |

| Title 37 Section 42.8            |   |

| Title 37 Section 42.8(A)(1)      | 1 |

| Title 37 Section 42.8(b)(1)      |   |

| Title 37 Section 42.8(b)(2)      |   |

| Title 37 Section 42.8(b)(3)      |   |

| Title 37 Section 42.8(b)(4)      |   |

|                                  |   |

| United States Code      |        |

|-------------------------|--------|

| Title 35 Section 102    |        |

| Title 35 Section 102(a) | passim |

| Title 35 Section 102(b) | passim |

| Title 35 Section 102(e) |        |

| Title 35 Section 103    | passim |

| Title 35 Section 103(a) |        |

| Title 35 Section 112    |        |

| Title 35 Section 282(b) |        |

| Title 35 Section 318(b) |        |

|                         |        |

# **Other Authorities**

| Federal Register,           |    |

|-----------------------------|----|

| Volume 83, No. 197, 51340   | 10 |

|                             |    |

| http://www.compactflash.org |    |

| 1 1 5 8                     | ,  |

# LIST OF EXHIBITS

| Exhibit No. | Exhibit                                                                                                                                                                                                            |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1001        | U.S. Pat. No. 8,307,180 to Hyvönen et al.                                                                                                                                                                          |  |

| 1002        | Declaration of Dr. R. Jacob Baker                                                                                                                                                                                  |  |

| 1003        | CF+ and CompactFlash Specification Revision 3.0                                                                                                                                                                    |  |

| 1004        | U.S. Pat. No. 7,478,248 to Ziv et al.                                                                                                                                                                              |  |

| 1005        | U.S. Pat. No. 6,681,304 to Vogt et al.                                                                                                                                                                             |  |

| 1006        | U.S. Pat. No. 6,279,114 to Toombs et al.                                                                                                                                                                           |  |

| 1007        | U.S. Pat. No. 7,409,489 to Sinclair                                                                                                                                                                                |  |

| 1008        | U.S. Pat. Pub. No. 2006/00220054 to Elhamias                                                                                                                                                                       |  |

| 1009        | File History for U.S. Pat. No. 8,307,180                                                                                                                                                                           |  |

| 1010        | The MultiMediaCard System Specification, Version 3.31                                                                                                                                                              |  |

| 1011        | U.S. Pat. Publ. No. 2008/0080688 to Burgan et al.                                                                                                                                                                  |  |

| 1012        | U.S. Pat. No. 5,809,340 to Bertone et al.                                                                                                                                                                          |  |

| 1013        | U.S. Pat. Publ. No. 2006/0280077 to Suwa                                                                                                                                                                           |  |

| 1014        | U.S. Pat. No. 7,152,801 to Cuellar et al.                                                                                                                                                                          |  |

| 1015        | CompactFlash Association Announces Availability of Revision 3.0<br>of the CF+ & CompactFlash Specification; Revision 3.0 Increases<br>CF Interface Data Transfer Rate to 66MB/sec, BUSINESS WIRE<br>(Jan. 7, 2005) |  |

| 1016        | U.S. Pat. Publ. No. 2007/079015 to Royer, Jr. et al.                                                                                                                                                               |  |

| 1017        | U.S. Pat. No. 3,653,001 to Ninke                                                                                                                                                                                   |  |

| Exhibit No. | Exhibit                                                                                                                           |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| 1018        | Public Key Infrastructure: Implementation and Design, by Suranjan<br>Choudhury et al.                                             |  |

| 1019        | Assignment History for U.S. Pat. No. 7,478,248 to Ziv et al.                                                                      |  |

| 1020        | Assignment History for U.S. Pat. No. 6,279,114 to Toombs et al.                                                                   |  |

| 1021        | Assignment History for U.S. Pat. No. 7,409,489 to Sinclair et al.                                                                 |  |

| 1022        | Third Joint Claim Construction and Prehearing Statement (N.D. Cal. Patent L.R. 4-3), filed in the related matter on Nov. 16, 2018 |  |

| 1023        | Affidavit of Christopher Butler, Internet Archive                                                                                 |  |

| 1024        | Exhibit A to the Affidavit of Christopher Butler                                                                                  |  |

| 1025        | Declaration of Michael Asao                                                                                                       |  |

# I. <u>INTRODUCTION AND STATEMENT OF RELIEF REQUESTED (37</u> <u>C.F.R. §42.22(a))</u>

Kingston Technology Company, Inc. ("Petitioner" or "Kingston") hereby petitions to institute an *inter partes* review of Claims 1-3, 5, 12, 13, 16-19, 21, 28, 29, 32, and 35 (the "Challenged Claims") of U.S. Patent No. 8,307,180 (the "180 Patent") to Hyvonen *et al.* (Ex. 1001), and cancel those claims as unpatentable.

As discussed below, the prior art anticipates and/or renders obvious the Challenged Claims of the '180 Patent under 35 U.S.C. § 102 and/or § 103. Accordingly, there is a reasonable likelihood that Petitioner will prevail with respect to at least one challenged claim, and Petitioner respectfully requests that the Board institute a trial for *inter partes* review and cancel all Challenged Claims as unpatentable.

# II. <u>MANDATORY NOTICES (37 C.F.R. §42.8(A)(1))</u>

#### A. <u>Real Party-In-Interest (37 C.F.R. §42.8(b)(1))</u>

Petitioner Kingston Technology Company, Inc., is a real party-in-interest. Petitioner's parent company, Kingston Technology Corporation ("Kingston Holding"), is a holding company without any employees or operations. However, because Kingston Holding is the sole owner of Petitioner and shares some directors, Petitioner identifies Kingston Holding as an additional real party-ininterest.

# B. Identification of Related Matters (37 C.F.R. §42.8(b)(2))

Patent Owner Memory Technologies, LLC ("MTL") has asserted the Challenged Claims of the '180 Patent, as well as claims from seven other patents, against Kingston in a co-pending litigation, *Memory Technologies, LLC v. Kingston Technology Co., Inc.*, 8:18-cv-00171 (C.D. Cal.). MTL's original Complaint was filed on January 31, 2018, and served on Kingston, at the earliest, on February 1, 2018.

In addition to this Petition, Kingston has or will be filing petitions for *inter partes* review of the other seven patents that MTL has asserted against it.

#### C. <u>Counsel and Service Information (37 C.F.R. §§42.8(b)(3) & (b)(4))</u>

Petitioner designates the following Lead and Backup Counsel. Concurrently filed with this Petition is a Power of Attorney for appointing the following Lead and Backup Counsel, per 37 C.F.R. § 42.10(b). Service via hand-delivery may be made at the postal mailing addresses below. Petitioner consents to electronic service by e-mail at the following address: **Kingston-180ipr@pillsburylaw.com**.

| Lead Counsel                      | Back-Up Counsel                     |

|-----------------------------------|-------------------------------------|

| Robert C.F. Pérez                 | Christopher Kao                     |

| (Reg. No. 39,328)                 | (Pro hac vice motion to be filed)   |

|                                   | Brock S. Weber                      |

| PILLSBURY WINTHROP SHAW           | (Pro hac vice motion to be filed)   |

| PITTMAN LLP                       | PILLSBURY WINTHROP SHAW             |

| 1650 Tysons Boulevard, 14th Floor | PITTMAN LLP                         |

| McLean, VA 22101                  | Four Embarcadero Center, 22nd Floor |

| Telephone: 703.770.7900           | San Francisco, CA 94111             |

| Facsimile: 703.770.7901           | Telephone: 415.983.1000             |

|                                   | Facsimile: 415.983.1200             |

|                                   |                                     |

## D. <u>Payment of Fees (37 C.F.R. §42.103)</u>

Petitioner authorizes the Patent and Trademark Office to charge Deposit

Account No. 033975 for the petition fee and for any other required fees.

# III. <u>REQUIREMENTS FOR INTER PARTES REVIEW</u>

Pursuant to 37 C.F.R. § 42.104(b), Petitioner requests that the Challenged

Claims of the '180 Patent be cancelled as anticipated or obvious based on the

following grounds:

| Ground | '180 Patent Claims                            | <b>Basis for Rejection</b>                       |

|--------|-----------------------------------------------|--------------------------------------------------|

| 1      | 1, 3, 9, 10, 12, 19, 21, 27, 28,<br>and 30    | § 102 based on CompactFlash                      |

| 2      | 1, 5, 16, 17, 21, 32, and 35                  | § 103 based on Ziv and Vogt                      |

| 3      | 2, 3, 18, and 19                              | § 103 based on Ziv, Vogt, and Toombs             |

| 4      | 1, 2, 3, 5, 16, 17, 18, 19, 21, 32,<br>and 35 | § 103 based on <i>Sinclair</i> and <i>Toombs</i> |

| 5 | 12, 13, 28, 29 | § 103 based on <i>CompactFlash</i> and <i>Elhamias</i> |

|---|----------------|--------------------------------------------------------|

| 6 | 12, 13, 28, 29 | § 103 based on <i>Ziv, Vogt,</i> and <i>Elhamias</i>   |

The Declaration of R. Jacob Baker, Ph.D., P.E., filed herewith (Ex. 1002, "Baker Decl."), supports the challenge in this Petition that the Challenged Claims are invalid as anticipated and obvious.

## IV. <u>A PERSON OF ORDINARY SKILL IN THE ART</u>

Relative to the '180 Patent, a person of ordinary skill in the art ("POSITA") is a person having at least a bachelor's degree in electrical engineering, computer engineering, or equivalent training, with at least two years of academic or industry experience in the field of memory system design. Ex. 1002 at ¶65. However, a higher level of education could make up for less experience, and vice versa. *Id*.

## V. <u>BACKGROUND OF THE TECHNOLOGY</u>

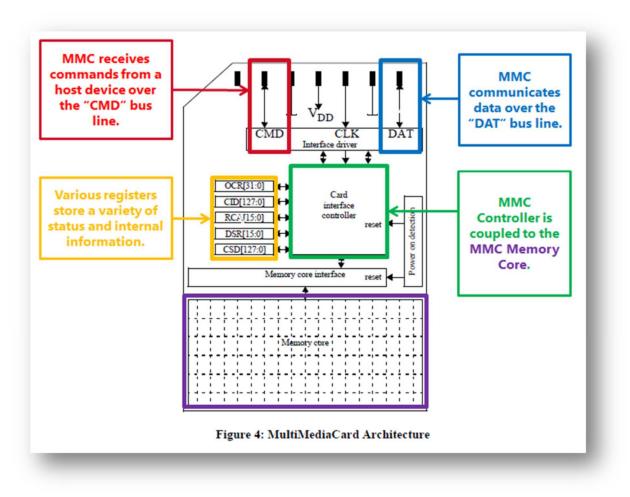

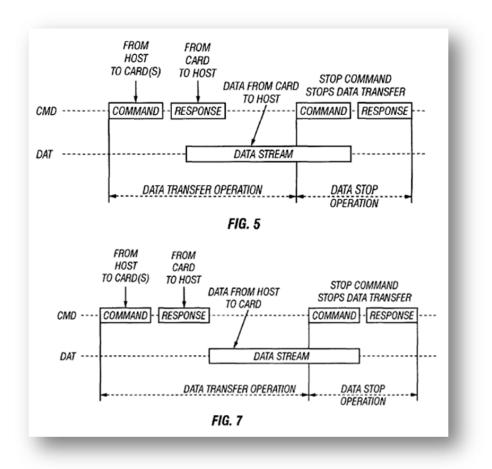

A memory device is used to store electronic data. Ex. 1002 at ¶¶68-71. By 2008, several types of memory devices that use flash or EEPROM memory were in existence, including MultiMediaCard ("MMC") and CompactFlash ("CF"). *Id.* at ¶71. A memory device can communicate with a host device. Ex. 1010 at 19. As depicted below, for example, an MMC receives commands from a host device over a "CMD" bus and communicates data over the "DAT" bus line. Ex. 1002 at ¶74; *see* Ex. 1010 at 142.

Ex. 1010 at Fig. 4 (annotated).

A MMC also includes a group of registers that can store information about the memory card. *Id.* at 19. For example, the MMC device's CSD (Card Specific Data) register provides information on how to access the memory card, including data format, data transfer speed, etc. *Id.* at 68, Table 22.

#### VI. OVERVIEW OF THE '180 PATENT

The '180 Patent issued on November 6, 2012 from U.S. Patent Application No. 12/039,672 ('672 Application) filed on February 28, 2008.

### A. <u>Summary of the Claimed Subject Matter</u>

The Challenged Claims generally relate to access profiles. An access profile "governs the current access operations to the memory device." Ex. 1001 at 4:57-58. The Challenged Claims, in particular, relate to activating an access profile and configuring a memory device in accordance with an access profile, so that the device is effective for a usage in accordance with the activated profile.

The access profiles are stored in a register of the memory and correspond to memory access operations, such as "a read, a write, an erase, and a modify attribute operation." *Id.* at 1:62-64, 5:1-3, 6:17-21, 7:4-13. An access profile can be stored elsewhere. *Id.* at 5:14-17.

The '180 Patent specification describes the invention as applicable "in any stand-alone or embedded system that comprises or accesses a memory device." *Id.* at 5:24-27. When connected to such a system, the memory device can "receive one or more commands . . . for activating a particular access profile." *Id.* at 4:29-32. The portion of the system that issues commands to the memory device is referred to as a "host." *Id.* at 2:59-63.

The '180 Patent specification also describes configurations that may correspond to access profiles. For instance, in a "burst profile mode [an access profile], corresponding to fast, contiguous data access," the memory device is configured so that "after receiving all the data" to be written from a host, it may

"indicate 'exit busy' and set the transfer mode to 'transfer state,' thus facilitating faster execution of subsequent accesses by the host." *Id.* at 7:18-21.

Other access profiles may cause the device to configure itself such that a particular profile is "associated with different partitions of the memory device," including either "logical or physical partitions." *Id.* at 7:36-37. Similarly, a profile may result in a device configuration such that access operations are "map[ped] ... to certain sections of the physical memory with special characteristics." *Id.* at 7:49-52. Finally, some access profiles may result in a configuration such that the device postpones "management" or "background operations" until after the data transfer. Ex. 1001 at 3:61-64, 4:43-49.

#### B. <u>The '180 Patent Prosecution History</u>

Before issuance of the '180 Patent, the Applicant responded to three office actions and submitted a notice of appeal and a pre-appeal brief. Ex. 1009 at 327, 393, 406, 440. The resulting '180 Patent issued on Nov. 6, 2012.

The first office action rejected the claims as anticipated by *Burgan. Id.* at 443. *Burgan* teaches smart phones with various profiles, such as a work profile and a family profile, that are accessed in response to caller ID information of a received call. Ex. 1011 at ¶¶5-6.

Applicant's response to the first office action is relevant to the "command" claim element. According to Applicant, "*[a] command in the context of the*

*various embodiments of the present application*, and in any other context for that matter, *suggests some type of authoritative direction or instruction to do/not to do something." Id.* at 427 (emphasis supplied). Using this definition, Applicant submitted that a POSITA would not equate the received Caller ID information in *Burgan* with an actual "command," because a Caller ID is a "passive" identifier. Ex. 1009 at 427.

Unconvinced by the Applicant's argument, the Patent Office subsequently issued a final rejection on July 6, 2011, maintaining the rejection. *Id.* at 408. In response, Applicant repeated its arguments in a Reply to the Final Office Action. *Id.* at 399-401. Applicant thereafter filed a notice of appeal and a pre-appeal brief. *Id.* at 382, 393-96. The Pre-Appeal Panel decided to withdraw the rejection and issue a new office action. *Id.* at 357.

The Examiner then rejected the claims over *Suwa* and *Bertone*. *Id*. at 329. Applicant made substantial amendments to the claims to distinguish *Suwa* and *Bertone* by further limiting a predefined access profile and the received one or more commands. *Id*. at 259-268. For example, the amendments to Claim 17 are shown below:

17. (Currently Amended) A memory device, comprising:

one or more registers for storing one or more predefined access profiles associated with said memory device, said predefined access profiles being effective for determining how access to said memory device is configured for at least one usage;

receiving means <u>a controller</u> for receiving one or more commands <u>related to</u> <u>said at least one usage of said memory device, said one or more commands</u> for activating <u>said</u> one or more <u>predefined</u> access profiles associated with said memory device, <u>said controller</u> <u>also</u>

<del>; and</del>

*Id.* at 261.

Applicant also clarified the claim limitation, "configuring access to said memory device." Applicant argued that, unlike the claim requiring "configuring access to said memory device," the memory device in *Bertone* only configures the memory device according to "timing characteristics to control the speed performance of the memory module." Ex. 1009 at 266-67. Applicant argued that merely changing an operating speed for the memory device *does not* constitute an access configuration.

Ex. 1012 at Fig. 5 (annotated).

Applicant also contended that *Suwa* does not configure an access profile, because the switcher in *Suwa* "automatically completes necessary changes to use

the selected mode" upon activation. *Id.* at 266. Applicant argued that the claimed invention requires that the *activation* of an access profile *occurs separately* from the *access configuration* of the memory device.

A Notice of Allowance subsequently issued. Ex. 1009 at 244.

#### VII. CLAIM CONSTRUCTION

#### A. <u>Legal Overview</u>

The Patent Office has adopted a rule by which claims are construed in accordance with "the standard used in federal courts, in other words, the claim construction standard that would be used to construe the claim in a civil action under 35 U.S.C. 282(b), which is articulated in *Phillips v. AWH Corp.*, 415 F.3d 1303 (Fed. Cir. 2005)." 83 FR 51340. Under this standard, claim construction begins with the language of the claims. *Phillips*, 415 F.3d at 1312-14. The "words of a claim are generally given their ordinary and customary meaning," which is "the meaning that the term would have to a person of ordinary skill in the art in question at the time of the invention, i.e., as of the effective filing date of the patent application." Id. at 1312-13. The specification is "the single best guide to the meaning of a disputed term and . . . acts as a dictionary when it expressly defines terms used in the claims or when it defines terms by implication." Id. at 1321 (internal quotation marks omitted). The prosecution history is another source of intrinsic evidence. Id. at 1317.

All claim terms of Challenged Claims of the '180 Patent have been accorded their plain and ordinary meaning as understood by POSITA and consistent with the intrinsic record. Petitioner's interpretation of the claim terms in the '180 Patent is further explained for each claim limitation in relation to the prior art discussed in the proposed grounds for invalidity, below, in Grounds 1-6.

Under the *Phillips* standard and for clarity, Petitioner provides the following specific constructions.<sup>1</sup>

#### B. <u>Claim Terms</u>

## 1. <u>"predefined access profile"</u>

The Challenged Claims describe "access profiles" in several different ways. An access profile may be a mode, setting, control, or logic for an access operation, each of which is disclosed in the specification. The Board should construe "predefined access profile" to mean a "mode, setting, control, or logic defined in advance for reading, writing, modifying, deleting, or changing the attributes of data." Ex. 1002 at ¶127-129

<sup>&</sup>lt;sup>1</sup> Petitioner reserves the right to address any claim construction positions taken by the Patent Owner in its Preliminary Response, if any, including under 37 C.F.R. § 42.108(c). Petitioner further reserves its ability to show that claims of the '180 Patent are invalid under 35 U.S.C. §112 in the co-pending litigation, despite offering explicit and implicit claim constructions herein.

For example, the '180 Patent discloses that a profile can be a mode: "one profile may be defined as a burst profile **mode**, corresponding to a fast, contiguous data access **mode.**" Ex. 1001 at 7:15-18 (emphasis added); *see also id.* at Claim 18 (reciting predefined access profiles that "correspond to at least one of a random and a sequential mode of access"); *id.* at 4:44-52 (random mode profile).

The specification also describes that profiles can be a control or setting: "the access profile associated with a media device may be adapted to comprise different **control and/or setting** profiles that are associated with different partitions of the memory device." *Id.* at 7:33-36 (emphasis added). Lastly, the specification states that "an access profile may be implemented as a binary file that further comprises the required **logic** to implement an access profile." *Id.* at 5:14-19 (emphasis added).

#### 2. <u>"configuring access"</u>

The Challenged Claims provide that the "predetermined access profiles" configure access to the "memory device." The Board should construe "configuring access" to mean "setting the memory device for reading, writing, modifying, deleting, or changing the attributes of data." Ex. 1002 at ¶¶130-132.

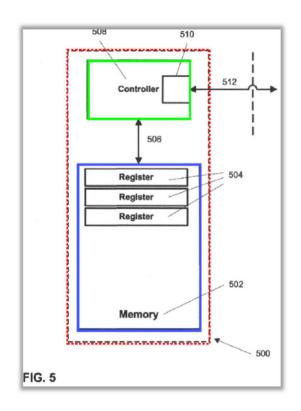

In Fig. 5 of the '180 Patent, the "memory device" (red box) includes many components. Ex. 1001 at Fig. 5; 4:26-42. For example, as depicted below, memory device 500 contains a "memory" 502 (blue box), "controller" 508 (green

box), an interface (506) through which communications between the controller and the memory may be conducted, and another interface (512) for communications with a host device.

# Id. at Fig. 5.

Thus, the proposed construction provides that the predefined access profiles can also configure data on the controller (green box) or other components of the "memory device" (red box), as indicated by the intrinsic evidence. Ex. 1002 at ¶¶130-132.

#### 3. <u>"usage"</u>

The Challenged Claims provide that the term "usage" is associated with use of the claimed memory device by the host. The Board should construe the term "usage" to mean "host activity in accordance with the predefined access profile." Ex. 1002 at ¶¶133-134.

For example, the Challenged Claims provide that the memory device "<u>receives</u> one or more commands <u>related to a least one usage of said memory</u> device and that the predefined access profiles" determine <u>how access</u> is configured for said at least one <u>usage</u>. Ex. 1001 at 2:39-67, Claim 1 (emphasis added). Because the commands are "received" for a usage "of the memory device" and the "access is configured" for the usage, it is clear that "usage" refers to host activity, as that is where the commands can originate and the device that is accessing the memory card. This is also clear from the specification. Specifically, the '180 Patent states that an access profile "governs the current access operations to the memory device" by the host device. Ex. 1001 at 4:52-59.

#### VIII. SUMMARY OF THE PRIOR ART

## A. <u>CompactFlash</u>

A CompactFlash device is a flash memory mass storage device. Ex. 1002 at ¶136. SanDisk first manufactured a CompactFlash device in 1994. Ex. 1014 at 1:56-59. CompactFlash quickly became the go-to portable mass storage device for electronic devices. Ex. 1002 at ¶137. CompactFlash remains popular and is supported by many devices. *Id*.

In 1995, the CompactFlash Association was formed by a group of international companies with the goal of creating an industry standard for flash-based mass storage. *Id.* at ¶138. The CompactFlash specification establishes the methods, processes, and practices for both the CompactFlash device and a host interacting with the device. *Id.* at ¶136.

On December 23, 2004, the CompactFlash Association released CompactFlash Specification Revision 3.0 (*CompactFlash*). Ex. 1003 at 1; Ex. 1025 at ¶7 (Declaration of Michael Asao, consultant for the CompactFlash Association). *CompactFlash* was made publicly available to any interested member of the public free of charge prior to 2008, as, for example, the CompactFlash Association publicly announced on January 6, 2005 that *CompactFlash* "is available to download free from the CFA website at http://www.compactflash.org." Ex. 1024 at 9; Ex. 1023 at ¶6 (authenticating page 9 of Ex. 1024 as an accurate representation of the January 6, 2005 announcement by the CompactFlash Association); *see also* Ex. 1015 (Jan. 7, 2005 article stating that "[t]he CF Specification Revision 3.0 is available to download free from the CFA web site at http://www.compactflash.org"); Ex. 1016 at ¶3 (describing an

exemplary hard drive that utilizes a CompactFlash interface "as described in the CF+ and CompactFlash Specification Revision 3.0, published by the CompactFlash Association, Palo Alto, Calif., Dec. 23, 2004, http://www.compactflash.org.") (published on Apr. 5, 2007).

Moreover, CompactFlash was freely and publicly available online from the CompactFlash website as of at least January 13, 2005. Ex. 1025 at ¶7; Ex. 1024 at 2-3 (displaying the CompactFlash homepage indicating that *CompactFlash* "is now available to download" on Jan. 13, 2005); *Id.* at 6 (displaying the registration form that once submitted included a link for a free download for *CompactFlash*); Ex. 1023 at ¶6 (authenticating pages 2-3 of Ex. 1024 as an accurate representation of the CompactFlash Association website on Jan. 13, 2005 and page 6 of Ex. 1024 as an accurate representation of the CompactFlash registration form on January 27, 2005). See Crestron Electronics Inc. v. Intuitive Building Controls Inc., Case IPR2015-01460, slip op. at 12-22 (PTAB Jan. 14, 2016) (Paper 14). Accordingly, CompactFlash qualifies as prior art at least under pre-AIA 35 U.S.C. §§ 102(a) and 102(b). *CompactFlash* was not previously presented to the PTO in the context of the '180 Patent.

The CompactFlash Association made improvements to direct memory access (DMA) data transfer in Revision 3. A DMA data transfer occurs directly

between the hardware subsystem and the memory device, rather than involving the host's CPU as an intermediary. Ex. 1002 at ¶143. In this manner, transfer speeds are boosted and the CPU is freed to work on other tasks while the transfer occurs. *Id.* Starting with Revision 3.0, "UltraDMA" was introduced, which boosted DMA transfer speed four-fold from the prior "MultiWord DMA" transfer. Ex. 1015 ("Ultra DMA 33 and UltraDMA66 [sic] interface modes will increase the CompactFlash interface data transfer rate to 66 MB/sec.").

*CompactFlash* also introduced several Ultra DMA modes. Ex. 1003 at 137. A CompactFlash controller configures a CompactFlash device to perform the Ultra-DMA transfer according to a protocol based on the mode selected. When a host sets an Ultra DMA mode, the memory device automatically disables any enabled MultiWord DMA mode. *Id.* at 158. In response, the memory device sets the selected Ultra DMA mode in a task file register. *Id.* at 120.

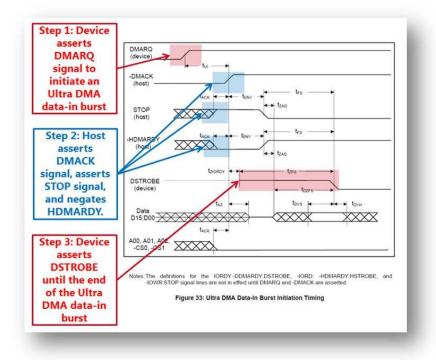

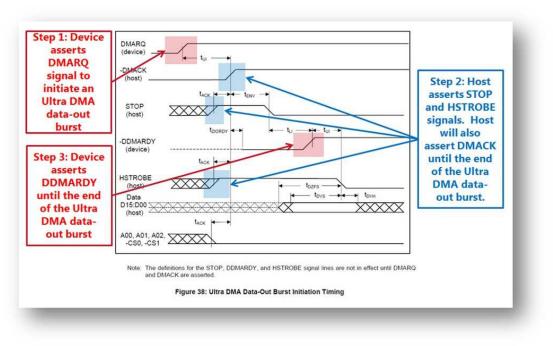

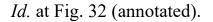

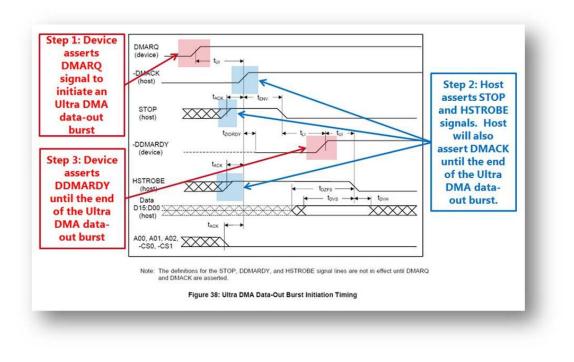

The host may subsequently communicate a READ DMA or WRITE DMA command to transfer data to the device. *Id.* at 52. The CompactFlash device, in response, will begin the Ultra DMA-specific initiation protocol to configure the memory device for an Ultra DMA transfer. *Id.* at 68-70. As illustrated for a data-in burst in Fig. 33 and a data-out burst in Fig. 38 (both shown below), the controller starts the initiation phase of the Ultra DMA burst by asserting a

DMARQ signal. *Id.* at 75-76, 81-82. After the host responds by asserting and/or negating several signals, the controller will assert either a DSTROBE signal or DDMARDY signal until the end of the burst. *Id.* at 75-76, 81-82. Finally, unlike

the older MultiWord DMA modes, the device will calculate a CRC value to ensure the accuracy of the data transferred in the Ultra DMA modes. *Id.* at 90. If the memory device detects errors, an Error Register is updated to reflect the error. *Id.* at 90.

Id. at Fig. 33 (annotated).

Id. at Fig. 38 (annotated).

# B. United States Patent No. 7,478,248 (Ziv)

*Ziv* was filed November 27, 2002, and published on May 27, 2004. *Ziv* is prior art under at least pre-AIA 35 U.S.C. §§ 102(a), (b), and (e). *Ziv* was not previously presented to the PTO in the context of the '180 Patent.

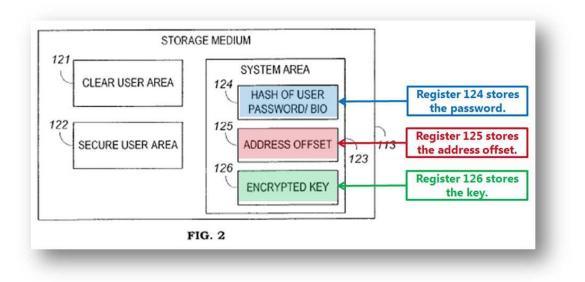

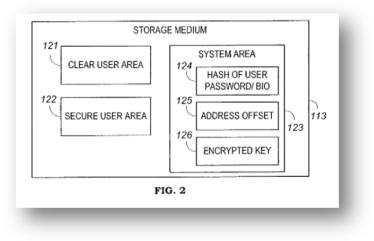

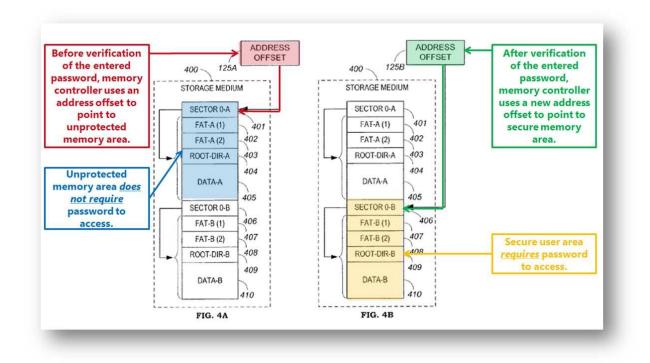

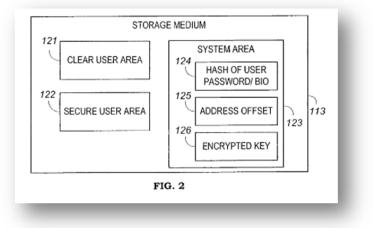

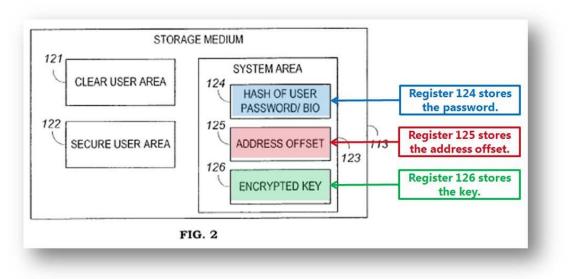

*Ziv* discloses a memory controller that allows profile-based access to an encrypted partition of memory. Ex. 1004 at Abstract. A user first selects a password that is hashed and stored in a register. *Id.* at 4:15-20. The system also generates a cryptographic key, which is used with a stored address offset for accessing the secure area. *Id.* at 5:14-15.

Id. at Fig. 2 (annotated).

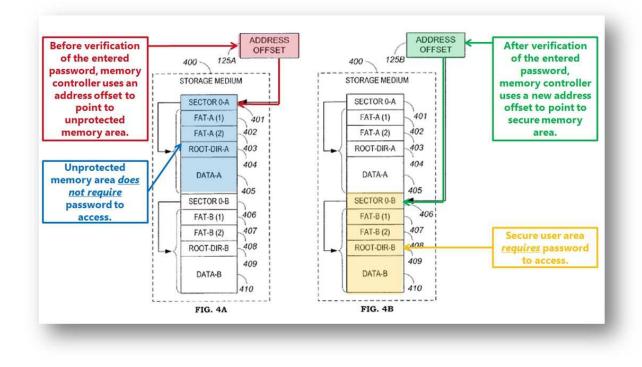

The secure memory area is activated when the host transmits a valid password to the controller. *Id.* at 6:15-22. Then the memory controller remounts the memory by using the stored address offset in the register to point to the secure partition (as illustrated in Fig. 4B). *Id.* at 6:42-49, Fig. 4B (shown below).

Id. at Figs. 4A-B (annotated).

## C. United States Patent No. 6,681,304 (Vogt)

*Vogt* was filed June 30, 2000 and issued on January 20, 2004. *Vogt* is prior art under at least pre-AIA 35 U.S.C. §§ 102(a), (b), and (e). *Vogt* was not previously presented to the PTO in the context of the '180 Patent.

*Vogt* teaches a "password verify" command to access hidden storage in a memory device. Ex. 1005 at 6:35-37, 8:11-30, 11:53-55.

#### D. <u>United States Patent No. 6,279,114 (*Toombs*)</u>

Toombs was filed November 4, 1998, and issued on August 21, 2001.

*Toombs* is prior art under at least pre-AIA 35 U.S.C. §§ 102(a), (b), and (e).

Toombs was not previously presented to the PTO in the context of the '180 Patent.

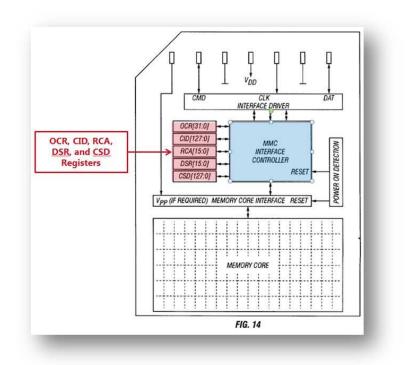

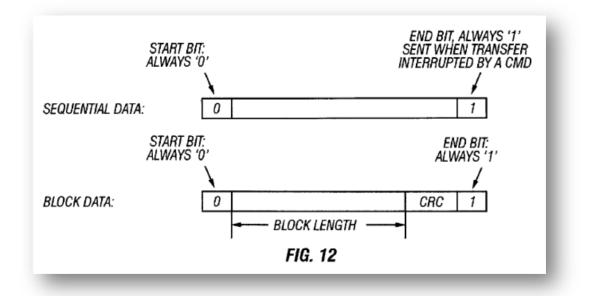

*Toombs* teaches a MultiMediaCard having parameters stored in various registers as shown in Fig. 14 below. Ex. 1006 at 1:9-14, 6:18-38, 10:22-33, Fig. 14.

Id. at Fig. 14 (annotated).

*Toombs* also teaches two types of data transfer processes. *Id.* at 8:34-34. One type involves sequential data transfer commands, which initiate a sequential, "continuous data stream." *Id.* at 8:35-37; Fig. 5, 7 (shown below); Ex 1002 at ¶191. The sequential data transfer commands reduce command overhead to a minimum, because data is transferred sequentially in a DAT line. Ex. 1006 at 8:39-43.

## Id. at Figs. 5, 7.

#### E. <u>United States Patent No. 7,409,489 (Sinclair)</u>

*Sinclair* was filed on October 25, 2005, claims priority to U.S. Provisional App. No. 60/705,388 filed on August 3, 2005, and was published on February 8, 2007. *Sinclair* is prior art under at least pre-AIA 35 U.S.C. §§ 102(a), (b), and (e). *Sinclair* was not previously presented to the PTO in the context of the '180 Patent.

*Sinclair* discloses selectable reclaim operation modes that provide optimizations to the rate that memory reclaim operations (*i.e.*,

background/management operations) occur. Ex. 1007 at Abstract. Reclaim

operations convert memory containing obsolete data into writeable memory. *Id.* at 2:9-11. An exemplary reclaim operation mode is the Reclaim Normal mode, which can be activated by the host sending a "Reclaim\_normal" command to the memory controller. *Id.* at 23:27-30, 23:47-51. This changes the configuration of the memory device to interject reclaim operations between write commands received from the host. *Id.* at 23:47-51, 2:50-57. The device calculates an optimal interleave ratio of reclaim operations to write commands such that the memory card will run out of writeable memory only when no reclaimable memory remains. *Id.* at 2:50-57.

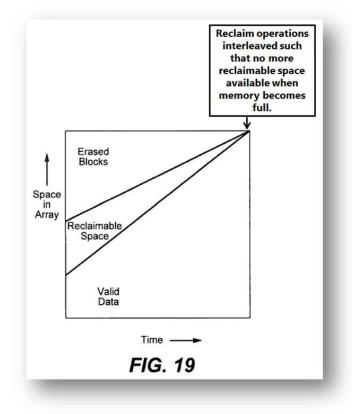

*Id.* at Fig. 19 (displaying a time graph illustrating an optimal interleave of reclaim operations to write operations) (annotated).

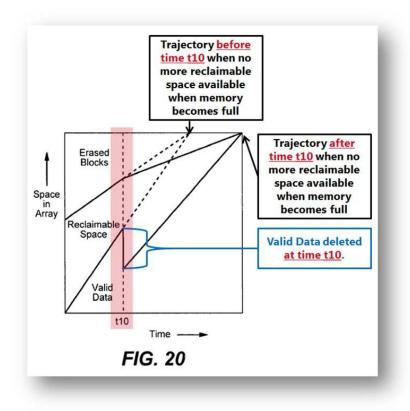

The interleave ratio can be recalculated periodically or when triggered by a host command. *Id.* at 18:17-26. As shown in Fig. 20, when host issues a delete command to the memory device at time t10, the system alters the interleave ratio such that the time when no more reclaimable space is available shifts to the newly anticipated time when the memory will be filled to capacity. *Id.* at 18:12-26.

Id. at Fig. 20 (annotated).

*Sinclair* also describes other reclaim modes selectable by the host, such that that "the host may have commands to select the appropriate reclaim mode based on present host activity or expected host activity." *Id.* at 23:27-30, 23:36-59.

#### F. United States Patent Publication No. 2006/00220054 (*Elhamias*)

*Elhamias* was filed on July 28, 2004 and was published on February 2, 2006. *Elhamias* is prior art under at least pre-AIA 35 U.S.C. §§ 102(a), (b), and (e). *Elhamias* was not previously presented to the PTO in the context of the '180 Patent.

*Elhamias* discloses a memory card that adapts its operation according to the application to which it is applied or the conditions under which it is operated. Ex. 1006 at¶8. *Elhamias* further discloses that the "maximum rate of data transfer between the host and the card is limited by the number of parallel data paths that are used." *Id.* at ¶22. Thus, the memory card is able to receive data in parallel for its storage and send data to the host in parallel from the memory. *Id.*

#### IX. GROUNDS FOR CHALLENGE

*Inter partes* review of Claims 1-3, 5, 12-13, 16-19, 21, 28-29, 32, and 35 of the '180 Patent is requested as follows.

# A. <u>GROUND 1: Claims 1-3, 5, 16-19, 21, 32 and 35 are unpatentable</u> <u>under 35 U.S.C. § 102 over *CompactFlash*</u>

As shown below, CompactFlash anticipates Claims 1-3, 5, 16-19, 21, 32 and 35 of the '180 Patent under 35 U.S.C. § 102. *See also* Ex. 1002 at ¶¶203-265.

## 1. <u>Independent Claim 1</u>

# (i) <u>A method for configuring access to a memory device,</u> <u>comprising</u>:

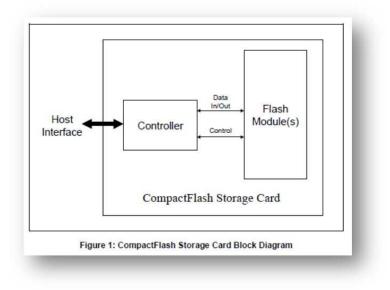

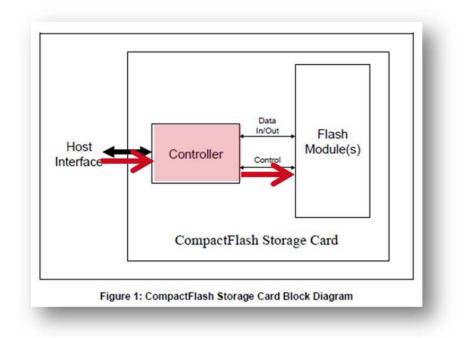

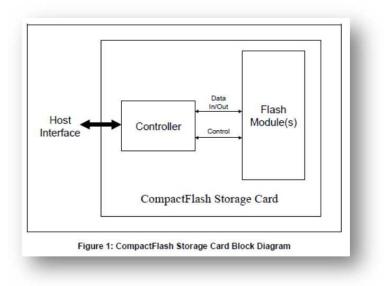

A CompactFlash device is a memory device and contains a "controller and flash memory module(s)." Ex. 1003 at 19; Ex. 1002 at ¶203.

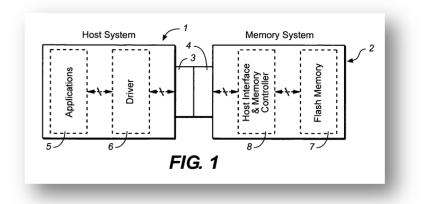

Ex. 1003 at Fig. 1 (annotated).

Furthermore, CompactFlash discloses a method for improvements to direct memory access (DMA) data transfer. Ex. 1003 ("Ultra DMA 33 and UltraDMA66 [sic] interface modes will increase the CompactFlash interface data transfer rate to 66 MB/sec."); Ex. 1002 at ¶204.

#### (ii) <u>receiving one or more commands related to at least</u> <u>one usage of said memory device</u>,

CompactFlash has a CompactFlash controller, which receives a SET FEATURES command from the host. The SET FEATURES command is communicated from the host to the CompactFlash controller to select one of the MultiWord or Ultra DMA modes. *Id.* at 15, 156-57. The SET FEATURES command instructs the controller to set the DMA mode to the selected MultiWord DMA mode or Ultra DMA mode for subsequent DMA access operations (*i.e.*, the usage), such as READ DMA and WRITE DMA. *Id.* at 15, 157-58.

*Id.* at Fig. 1 (annotated). Thus, *CompactFlash* discloses this element. Ex. 1002 at ¶¶205-206.

# (iii) <u>said one or more commands for activating one or</u> <u>more predefined access profiles associated with said</u> <u>memory device</u>,

CompactFlash discloses MultiWord and Ultra DMA modes stored in a

register on the CompactFlash device. As shown in Table 53, below, various

MultiWord DMA and Ultra DMA modes are supported, each of which constitutes

a pre- defined access profile.

| Mode                            | Bits (7:3) | Bits (2:0) |

|---------------------------------|------------|------------|

| PIO default mode                | 00000b     | 000b       |

| PIO default mode, disable IORDY | 00000b     | 001b       |

| PIO flow control transfer mode  | 00001b     | Mode       |

| Reserved                        | 00010b     | N/A        |

| Multiword DMA mode              | 00100b     | Mode       |

| Ultra DMA Mode                  | 01000b     | Mode       |

| Reserved                        | 10000b     | N/A        |

*Id.*, at 158 (equating MultiWord DMA and Ultra DMA "Mode[s]" as "transfer mode number[s]"). For example, the following Ultra DMA Modes are possible:

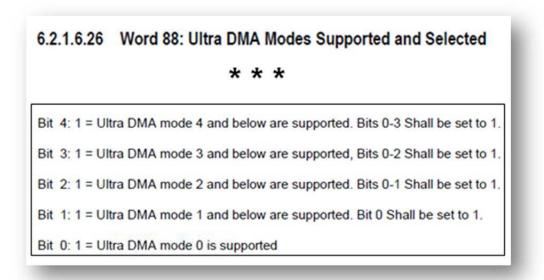

*Id.* at 132-33; 137.

Each DMA mode is an access profile, because the selected mode is used to determine the memory device configuration for the subsequent DMA access operations to the memory device. *See* Ex. 1001 at 3:56-58 ("*This profile*, which may be any one of the supported predefined profiles, *governs the current access operations to the memory device*.") (emphasis supplied); Ex. 1002 at ¶¶206-211. For instance, if an Ultra DMA mode is activated (unlike MultiWord DMA modes) the device configures itself to perform a CRC check calculation after the data transfer. Ex. 1003 at 90 ("CRC errors are detected and reported only while operating in Ultra mode."). In addition, unlike the MultiWord DMA modes, each

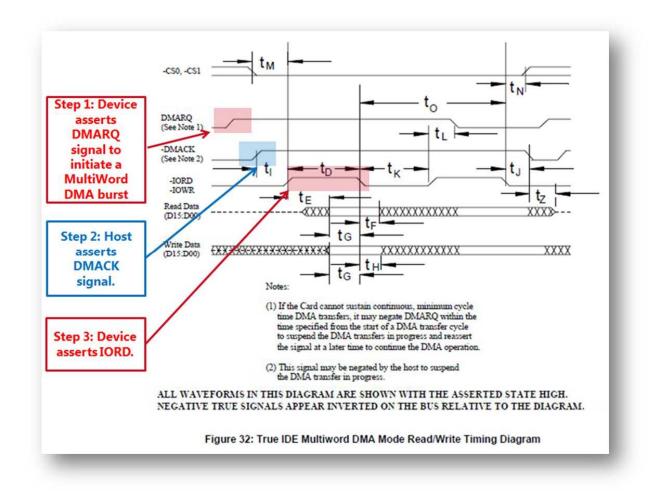

Ultra DMA mode uses both the rising and falling edge of the clock signal to transfer data and utilizes HDMARDY, DDMARDY, and DSTROBE signals, which are not part of a MultiWord DMA access operation. Ex. 1002 at ¶211; Ex. 1003 at 44, Fig. 32 (illustrating the MultiWord DMA transfer initialization process).

Furthermore, each Ultra DMA mode is different. As an example, after a pause in an Ultra DMA data burst, a memory device will be prepared to receive up to two additional data words for Ultra DMA Modes 0-2 and up to three additional data word for DMA Modes 3-5. *Id.* at 70. Finally, each mode is associated with different maximum transfer rates. *Id.* at Tables 21-22; Ex. 1002 at ¶233.

Each MultiWord and Ultra DMA mode is effective for determining access configuration for the usage. Specifically, the controller configures the CompactFlash device for an access operation according to the host-selected DMA mode. *Cf.* Ex. 1007 at Fig. 32 with Ex. 1007 at Figs. 32, 38 (illustrating the difference in initialization process between a MultiWord DMA transfer and an Ultra DMA transfer). For example, enabling an Ultra DMA mode causes the controller to initiate the Ultra DMA protocol (rather than the MultiWord DMA protocol) when receiving a READ DMA or WRITE DMA command (*i.e.,* at least one usage of the memory device) from the host. Ex. 1003 at 68. Similarly,

31

enabling a MultiWord DMA mode causes the controller to initiate the MultiWord DMA protocol (rather than the Ultra DMA protocol) when receiving a READ DMA or WRITE DMA command (*i.e.*, usage) from the host. Ex. 1003 at 68; Ex. 1002 at ¶¶209-11.

These DMA modes are access profiles because use of each DMA Mode requires the use of a specific DMA *protocol*, not merely the selection of particular timing characteristics. Ex. 1003 at 68 ("[T]he *Ultra DMA protocol* shall be used instead of the *Multiword DMA protocol*.... This protocol applies to the Ultra DMA data burst only."). *See* Ex. 1009 at 266-67. Moreover, in the example of Ultra DMA, "[s]everal signal lines are redefined to provide different functions during an Ultra DMA burst." *Id.* at 68.

Furthermore, unlike the Applicant's argument in the Prosecution History that changing the operating speed does not affect an access operation, the DMA modes *directly affect* access operations. Ex. 1009 at 266-67. The selected DMA mode dictates the specific DMA protocol that the memory device utilizes. Moreover, the selection of an Ultra DMA profile rather than a MultiWord DMA profile requires the device to perform a CRC comparison to ensure the accuracy of the data transferred. Ex. 1003 at 90 ("CRC errors are detected and reported *only while operating in an Ultra mode.*") (emphasis supplied); Ex. 1002 at ¶210.

32

With respect to the commands for activating one or more predefined access profiles, the SET FEATURES command sent from the host activates a selected MultiWord DMA mode or Ultra DMA mode (*i.e.*, a predefined access profile) from among the available modes supported by the device. Ex. 1003 at 157, Table 53 (indicating bits representing a host-selected DMA mode) (shown below).

| Mode                            | Bits (7:3) | Bits (2:0) |

|---------------------------------|------------|------------|

| PIO default mode                | 00000b     | 000b       |

| PIO default mode, disable IORDY | 00000b     | 001b       |

| PIO flow control transfer mode  | 00001b     | Mode       |

| Reserved                        | 00010b     | N/A        |

| Multiword DMA mode              | 00100b     | Mode       |

| Ultra DMA Mode                  | 01000b     | Mode       |

| Reserved                        | 10000b     | N/A        |

Ex. 1003 at Table 53 (annotated).

For example, for Ultra DMA modes, the Set transfer mode subcommand (using the transfer mode values in Table 53) in the SET FEATURES command allows "a host to select the Ultra DMA mode at which the system operates." *Id.* at 69.

Thus, *CompactFlash* discloses this element. Ex. 1002 at ¶207-211.

# (iv) <u>said predefined access profiles being effective for</u> <u>determining how access to said memory device is</u> <u>configured for said at least one usage; and</u>

As discussed above, *CompactFlash* discloses that each MultiWord and Ultra DMA mode (*i.e.*, predefined access profile) is effective for determining how access to the memory device is configured for a usage. *See supra* Section IX.A.1(ii); Ex. 1002 at ¶212-213.

The "usage" in *CompactFlash* relates to the host activity in accordance with the selected DMA mode (*e.g.*, a READ DMA or WRITE DMA operation). Ex. 1003 at 68. Specifically, the controller configures the CompactFlash device for a host- initiated access operation according to the host-selected DMA mode. *Cf.* Ex. 1003 at Fig. 32 *with id.* at Figs. 32, 38 (illustrating the difference in initialization process between a MultiWord DMA transfer and an Ultra DMA transfer). For example, enabling an Ultra DMA mode causes the controller to initiate the Ultra DMA protocol (rather than the MultiWord DMA protocol) when receiving a READ DMA or WRITE DMA command from the host. *Id.* at 68. Similarly, enabling a MultiWord DMA mode causes the controller to initiate the MultiWord DMA protocol (rather than the Ultra DMA protocol) when receiving a READ DMA or WRITE DMA command from the host. *Id.* at 68. Similarly, enabling a MultiWord DMA mode causes the controller to initiate the MultiWord DMA protocol (rather than the Ultra DMA protocol) when receiving a READ DMA or WRITE DMA command from the host. *Id.* at 68.

#### (v) <u>configuring access to said memory device in</u> <u>accordance with at least one of said access profiles so</u>

# that said memory device is effective for said at least one usage.

The CompactFlash controller configures the access to the memory device according to the selected DMA mode (*i.e.*, one of the MultiWord or Ultra DMA modes), so that the CompactFlash device is effective to perform a DMA access operation (*i.e.*, usage) using the selected DMA mode. Ex. 1002 at ¶¶214-215.

After a host communicates a READ DMA or WRITE DMA command following the selection of a DMA mode, the controller will begin the DMAspecific initiation protocol to configure access to the memory device for either a MultiWord DMA transfer or an Ultra DMA transfer in the selected mode. *Id.* at Figs. 32-33, 38.

For example, in a MultiWord DMA mode, the controller starts the initiation phase of the MultiWord DMA burst by asserting a DMARQ signal (Step 1 of Fig. 32). The host, in response, asserts a DMACK signal (Step 2 of Fig. 32), and, in turn, the controller responds by asserting the IORD signal (Step 3 of Fig. 32).

As another example, when an Ultra DMA mode is activated, the controller starts the initiation phase of the Ultra DMA burst by asserting a DMARQ signal (Step 1 of Fig. 33). Ex. 1003 at 76. The host then asserts a DMACK signal (Step 2 of Fig. 33). *Id.* at Fig. 33. Only at that point do the other signal lines become effective, permitting the transfer. *Id.* ("The definitions for the …DSTROBE… and - IOWR:STOP signal lines are not in effect until DMARQ and -DMACK are

asserted). The device will assert a DSTROBE signal line to start the data-in burst (Step 3 of Fig. 33). *Id.* at Fig. 33.

Id. at Fig. 33 (annotated).

For a data-out burst, the device will wait to negate any signal until generating a STROBE edge (*see* Step 3 of Fig. 38). *Id.* at 70. At this point, the memory device is now configured for usage (*i.e.*, to perform a data transfer under the selected Ultra DMA mode).

Id. at Fig. 38 (annotated).

- 2. <u>Dependent Claim 2</u>

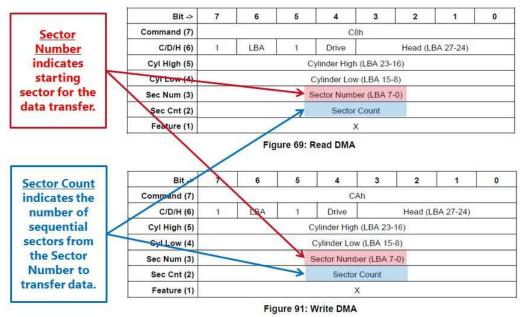

- (i) <u>The method of claim 1, wherein said one or more</u> <u>access profiles correspond to at least one of a random</u> <u>and a sequential mode of access</u>.

*CompactFlash* discloses a READ DMA and WRITE DMA command under one of the MultiWord or Ultra DMA modes (*i.e.*, a predefined access profile) that corresponds to a sequential mode of access. Ex. 1003 at 145 ("[The Read DMA] command uses DMA mode *to read from 1 to 256 sectors as specified in the Sector Count* register.... *The transfer begins at the sector specified in the Sector Number* Register"), 164 ("[The Write DMA] command uses DMA mode *to write from 1 to 256 sectors as specified in the Sector Count* register.... *The transfer begins at*

the sector specified in the Sector Number Register.") (emphasis added). The

CompactFlash device performs read and write access operations by accessing the starting place of the transfer in the memory (*i.e.*, the Sector Number) and continuing for a number of sequential sectors (*i.e.*, the Sector Count). *Id.* at 145, 164; Ex. 1002 at ¶¶216-27.

Ex. 1003 at Figs. 69, 91 (annotated).

Accordingly, READ and WRITE DMA operations correspond to a sequential mode of access. *See id.* at 145; Ex. 1002 at ¶226. Both start at a specified Sector Number and continue to access (*i.e.*, read or write) in sequence the number sectors indicated in the Sector Count. Ex. 1003 at 145, 164; Ex. 1002 at ¶218-25.

# 3. <u>Dependent Claim 3</u>

# (i) <u>The method of claim 2, wherein said access profiles</u> <u>correspond to at least one of a read, a write, an erase,</u> <u>and a modify attribute operation</u>.

In *CompactFlash*, the various DMA profiles correspond to and support READ DMA (*i.e.*, a read operation) and WRITE DMA (*i.e.*, a write operation). Ex. 1003 at 145, 164; Ex. 1002 at ¶¶228-230.

# 4. <u>Dependent Claim 5</u>

# (i) <u>The method of claim 1, wherein said one or more</u> <u>access profiles are adapted to produce an optimized</u> <u>performance associated with said memory device</u>.

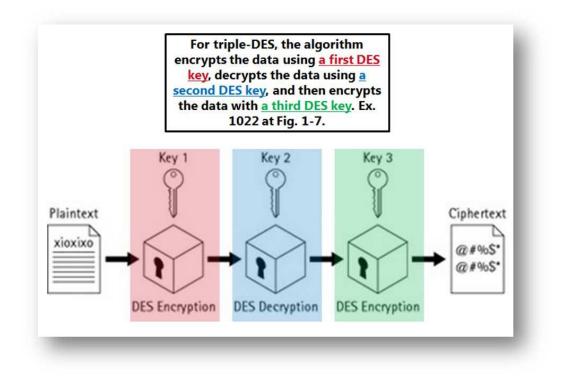

For purposes of the Petition, Petitioner applies Patent Owner's proposed construction in the above-identified related matter of the claim term "adapted to produce an optimized performance associated with said device" in Claim 21 to mean "designed to produce an improved memory device performance with higher reliability, increased speed, increased lifetime, or reduced energy consumption, than compared to the same memory device not implementing said one or more access profiles." Ex. 1022 at 21. *CompactFlash* discloses this subject matter. Ex. 1002 at ¶231-233.

Each DMA mode is designed to produce an improved memory device performance with increased speed (*i.e.*, higher throughput). Ex. 1002 at ¶233; *see*, *e.g.*, Ex. 1015 ("Ultra DMA … modes will increase the CompactFlash interface

data transfer rate[.]"). Each DMA mode is an optimization as it "reduces the processor power required to manage the CompactFlash data transfers." *Id.* Moreover, at the time of *CompactFlash*, the Ultra DMA modes provided the maximum read and write speed available to CompactFlash devices. *Id.*

In addition, in reading and writing data in an Ultra DMA transfer, the host device and the memory controller perform error detection. Ex. 1003 at 90 ("CRC errors are detected and reported only while operating in Ultra mode."). The host device may select a slower Ultra DMA mode if excessive errors are encountered, thereby improving the reliability of the memory device performance. *Id.*

## 5. <u>Dependent Claim 16</u>

# (i) <u>The method of claim 1, further comprising a default</u> <u>access profile that is used to configure said memory</u> <u>device upon power up</u>.

When executing a power-on or hardware reset, *CompactFlash* discloses that the device may revert to a default non-Ultra DMA mode, like a MultiWord DMA mode. Ex. 1003 at 69. As discussed above, each MultiWord DMA mode may be an access profile. *See supra* IX.A.1(iii); Ex. 1002 at ¶234.

## 6. <u>Independent Claim 17</u>

# (i) <u>A memory device, comprising</u>:

A CompactFlash device is a memory device and contains a "controller and flash memory module(s)." Ex. 1003 at 19; Ex. 1002 at ¶203.

Ex. 1003 at Fig. 1 (annotated).

# (ii) <u>one or more registers for storing one or more</u> <u>predefined access profiles associated with said</u> <u>memory device</u>,

The predefined profiles are stored in the card and are available via the "IDENTIFY DEVICE data [which] indicate support of the Ultra DMA feature and the Ultra DMA modes the device is capable of supporting." Ex. 1003 at 69, 128 ("Table 47 specifies ... data returned by the Identify Device Command"), 132-33. The IDENTIFY DEVICE data also indicates support of certain MultiWord DMA modes. *Id.* at 132-33.

For instance, Word 88 of the Identify Device Information "identifies the Ultra DMA transfer modes supported by the device and indicates the mode that is currently selected." *Id* at 137. This data is stored in a portion of memory (*i.e.*, a register) in the device, and is made available to the host via a "buffer" (*i.e.*, register), which the host can access, in response to an IDENTIFY DEVICE command. Ex. 1002 at ¶240; Ex. 1003 at 128 ("The parameter words in the buffer have the ... meanings defined in Table 47[.]").

Moreover, when the host selects a supported profile, the selected access profile is stored in a register in the CompactFlash device. Ex. 1002 at ¶¶235-240. For example, the host may use the "Set transfer mode subcommand" (designated "Feature 03h") which is part of the "SET FEATURES" command to "select the Ultra DMA mode at which the system operates." Ex. 1003 at 69, 156-58. When invoking this subcommand, the selected MultiWord or Ultra DMA mode is identified by storing a value corresponding to the selected access profile "in the Sector Count *register."* Ex. 1003 at 157 (emphasis supplied).

With respect to storing one or more predefined access profiles associated with said memory devices, *CompactFlash* discloses this subject matter. *See* Section above at IX.A.1(iii); Ex. 1002 at ¶¶235-247.

43

# (iii) <u>said predefined access profiles being effective for</u> <u>determining how access to said memory device is</u> <u>configured for at least one usage;</u>

See Section above at IX.A.1.(iv).

(iv) <u>a controller for receiving one or more commands</u> related to said at least one usage of said memory <u>device</u>,

See Section above at IX.A.1.(ii).

# (vi) <u>said one or more commands for activating said one or</u> <u>more predefined access profiles associated with said</u> <u>memory device,</u>

See Section above at IX.A.1.(iii).

(viii) <u>said controller also for configuring access to said</u> <u>memory device in accordance with at least one of said</u> <u>predefined access profiles so that said memory device</u> <u>is effective for said at least one usage</u>.

*See* Section above at IX.A.1.(v).

- 7. <u>Dependent Claim 18</u>

- (i) <u>The memory device of claim 17, wherein said one or</u> <u>more access profiles correspond to at least one of a</u> <u>random and a sequential mode of access</u>.

*See* Section above at IX.A.2.(i).

- 8. <u>Dependent Claim 19</u>

- (i) <u>The memory device of claim 18, wherein said access</u> profiles correspond to at least one of a read, a write, an erase, and a modify attribute operation.

See Section above at IX.A.3.(i).

# 9. <u>Dependent Claim 21</u>

# (i) <u>The memory device of claim 17, wherein said one or</u> <u>more access profiles are adapted to produce an</u> <u>optimized performance associated with said memory</u> <u>device</u>.

See Section above at IX.A.4.(i).

#### 10. Dependent Claim 32

## (i) <u>The memory device of claim 17, further comprising a</u> <u>default access profile that is used to configure said</u> <u>memory device upon power up</u>.

See Section above at IX.A.5.(i)..

# 11. <u>Independent Claim 35</u>

## (i) <u>A computer program product embodied on a non-</u> transitory computer-readable medium, comprising:

A CompactFlash device is a memory device and contains a "controller and flash memory module(s)." Ex. 1003 at 19; Ex. 1002 at ¶203.

Ex. 1003 at Fig. 1 (annotated).

To the extent this preamble is limiting, which it is not, the disclosed "controller" in *CompactFlash* is a part of a computing system that manages the operations to be carried out from a computer or software program. Ex. 1002 at ¶¶260-61. Furthermore, a POSITA would understand that the operations and functionality disclosed in CompactFlash as shown in this Ground 1 would necessarily be carried out by a computer program embodied on a non-transitory

computer-readable medium (i.e., as instructions carried out in memory). Ex. 1002

at ¶261.

# (ii) <u>a computer code for receiving one or more commands</u> related to at least one usage of a memory device,

See Section above at IX.A.1.(ii).

# (iii) <u>said one or more commands for activating one or</u> <u>more predefined access profiles associated with said</u> <u>memory device</u>,

See Section above at IX.A.1.(iii).

# (iv) <u>said predefined access profiles being effective for</u> <u>determining how access to said memory device is</u> <u>configured for said at least one usage; and</u>

See Section above at IX.A.1.(iv).

(v) <u>a computer code for configuring access to said</u> <u>memory device in accordance with at least one of said</u> <u>access profiles so that said memory device is effective</u> <u>for said at least one usage</u>.

*See* Section above at IX.A.1.(v).

# B. <u>GROUND 2: Claims 1, 5, 16, 17, 21, 32, and 35 are unpatentable</u> under 35 U.S.C. § 103(a) in view of *Ziv* and *Vogt*.

As shown below, Ziv and Vogt render obvious Claims 1, 5, 16, 17, 21, 32,

and 35 of the '180 Patent under 35 U.S.C. § 103. See also Ex. 1002 at ¶¶266-326.

# 1. <u>Independent Claim 1</u>

# (i) <u>A method for configuring access to a memory device,</u> <u>comprising</u>:

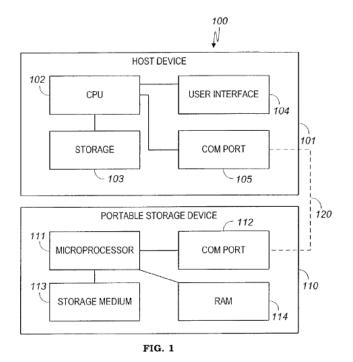

Ziv discloses a memory device, such as a portable storage device that

includes storage memory. Ex. 1004 at 3:48-55, Fig. 2; Ex. 1002 at ¶¶276-77.

Id. at Fig. 2.

Furthermore, *Ziv* discloses at least a method for securing data on a portable storage device and thus configuring access to a memory device, as shown below. Ex. 1004, *Title* and *Abstract*; Ex. 1002 at ¶¶276.

# (ii) <u>receiving one or more commands related to at least</u> <u>one usage of said memory device</u>,

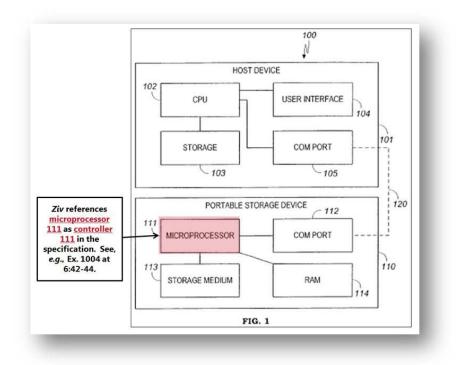

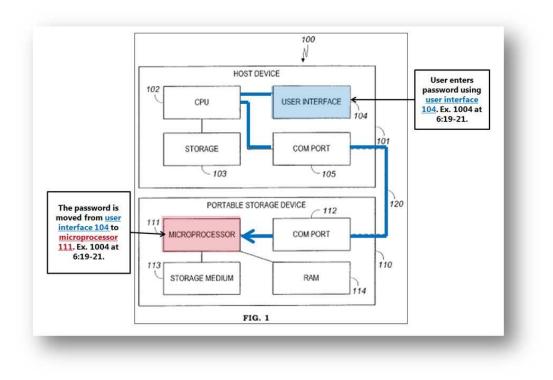

*Ziv* discloses a controller (microprocessor) in the memory device that receives a command indicating the password entered to gain access the secure area. Ex. 1004 at 6:42-44 ("*[C]ontroller 111* dismounts and remounts portable storage

device 110[.]") (emphasis added). A POSITA would understand the

microprocessor to be a controller. Ex. 1002 at ¶279.

# Ex. 1004 at Fig. 1 (annotated).

The controller receives a command indicating the password entered. *Id.* at 6:19-30 ("If the password has been entered ... via user interface 104, then in step 702 this password is moved to microprocessor 111.... [T]he hashed entered password is then compared to the hashed stored password in register 124."), Fig. 1 (below). In other words, the host system instructs (*i.e.*, sends a command to) the controller (microprocessor) to use the entered password to gain access to the secure memory area (*i.e.*, the usage). Ex. 1002 at ¶280.

To the extent the Board disagrees that an instruction to use the entered password to gain access to the secure memory area in *Ziv* teaches the claimed "command," it would have been obvious nevertheless to use the command-based password authentication method in *Vogt* in the memory device of *Ziv*. In particular, *Vogt* discloses a "password verify" command that communicates the entered password to the flash device, like a MMC card. Ex. 1005 at 6:36-38 ("The OS sends a 'password verify' command to the flash. *The command* ... *includes the entered password*.") (emphasis supplied). The "password verify" command instructs the internal processor to "compare[] the entered password with the stored password value." Ex. 1005 at 6:30-32.

It would have been obvious to combine the teachings of *Ziv* and *Vogt* to form a memory controller that receives the "password verify" command in *Vogt* for the following reasons. Ex. 1002 at ¶¶266-275.

#### Simple Substitution of One Known Element for Another

*Ziv*'s memory device differs from the claimed device at most by the "command" element. Ex. 1002 at ¶266. Commands, especially commands communicating a password, were well-known in the art to be a fundamental approach to communicating information between devices. *Id.* at ¶¶266, 270; Ex. 1005 at 6:36-38. A POSITA could have substituted one known element (a controller receiving a password) for the other (a controller receiving a command containing the password) and the results would have been predictable (a controller receiving a command containing the password). Ex. 1002 at ¶¶266-69.

Moreover, those predictable results would have included the known advantages of *Ziv*'s memory device, which provides access to a secure memory area, and the known advantages of a command, which include reliably and efficiently communicating a password from the host system to memory device. Ex. 1004 at 6:19-23; Ex. 1005 at 3:23-24; Ex. 1002 at ¶269.

51

#### Analogous Art

A POSITA would have been motivated to look to the teachings of the prior art due to the similar field, technology, and time frame of *Vogt* and *Ziv*. Ex. 1002 at ¶270. Both patents concern securing data using non-volatile memory in the early 2000s. Ex. 1004 at 3:48-55; Ex. 1005 at 1:13-15. In addition, both patents describe a solution to a similar problem–improving security of portable flash drives using a secure memory and password. Ex. 1004 at 1:60-63 ("[A] portable storage device for securing data stored in the device in a way that will be both convenient and secure."); Ex. 1005 at 2:5-12 ("Techniques for implementing hidden storage in a non-volatile memory storage," where "[t]he hidden storage area cannot be accessed without a valid password.").

#### Known Technique to a Known Device to Yield Predictable Results

**Base system:** *Ziv* discloses a memory device, such as a SecureDigital or CompactFlash device, that receives an entered password from the host system. Ex. 1004 at 6:19-30; Ex. 1002 at ¶273.

**Known technique:** As shown by *Vogt*, receiving a command containing a password was well-known. Ex. 1005 at 6:36-38.

Predictable results and improved system: A POSITA would have recognized that implementing *Vogt*'s structured communication protocol of the

"password verify command" in *Ziv*'s memory device would yield the predictable result of a memory device that receives an entered password through a structured command, like the password verify command. Ex. 1002 at ¶274.

As such, using *Vogt*'s password-command implementation of communicating a password was an obvious design choice to implement *Ziv*'s teaching of communicating a password. *Id.* at ¶¶266-75.

# (iii) <u>said one or more commands for activating one or</u> <u>more predefined access profiles associated with said</u> <u>memory device</u>,

The password hash, address offset, and key in *Ziv* constitutes a predefined access profile that governs the access operations to the memory. *See* Ex. 1001 at 3:56-58 ("*This profile*, which may be any one of the supported predefined profiles, *governs the current access operations to the memory device*.") (emphasis added). Additionally, each of these components forms an access profile. Ex. 1002 at ¶283.

Access to the secure user data is only available when a hash of an entered password matches the password hash stored in the register. Ex. 1004 at 4:11-12 ("[A] secure area 122 that contains secure user data [is] accessible only upon the provision of a password[.]"). In addition, the address offset governs access operations to the memory. After entering the proper password, the memory device uses the stored address offset to properly view the secure memory area. Ex. 1004

at 6:46-48 ("[H]ost 101 will seek 'sector 0' of the remounted device, controller 111 will use offset 125B to point at 'sector 0-B' 406[.]"). Without the address offset, the secure area will not be properly mounted (*i.e.*, accessible). *Id.*; Ex. 1002 at ¶284.

Ex. 1004 at Fig. 4A-4B (illustrating the use of the address offset to access the secure area) (annotated).

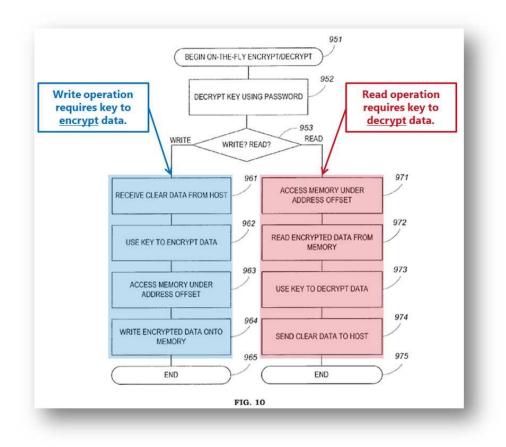

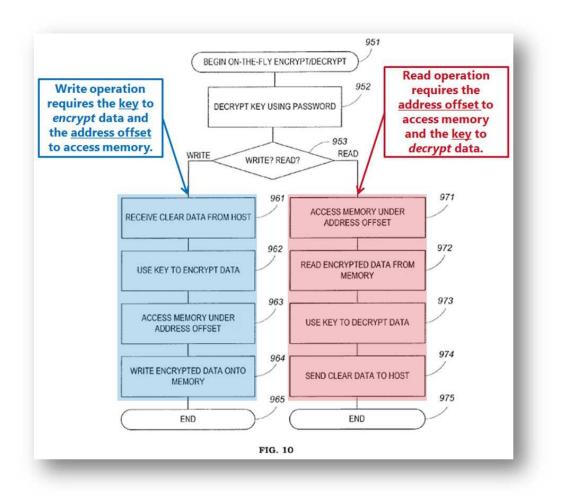

Moreover, the key governs the access operations to the memory. The key is the "permanent encryption key for all data stored in the secure memory." *Id.* at 7:7-9. Without the key, a user cannot read or write to the secure area. *Id.* at 7:7-9, 7:36- 46 (instructing the controller to decrypt data being read from and encrypt

data being read to the secure memory area using the key), Fig. 10 (shown below);

Ex. 1002 at ¶285.

Ex. 1004 at Fig. 10 (annotated).

As disclosed above, the command is the entering of the password from a host system to the memory controller. *Ziv* further discloses that a password entry from the host triggers several activation procedures associated with the predefined access profile. The entered password in *Ziv* activates a comparison of a hash of the entered password with the stored password hash. Ex. 1004 at 6:28-30; Ex. 1002 at  $\P$ 287.

Additionally, the password in *Ziv* activates the decryption of the stored key. Ex. 1002 at ¶288. When the entered password matches the stored password, the microprocessor decrypts the key of the predefined access profile. Ex. 1004 at 7:32-35.

The communication of a proper password also activates the remounting of the memory according to the address offset. Ex. 1002 at ¶289. After remounting, the stored address offset is used to point to the secure memory area. Ex. 1004 at 6:44-46 ("[W]hen remounting device 110, controller 111 will use an address offset[.]").