#### DOCKET NO.: 0107131.00562US3

Filed on behalf of Intel Corp.

By: Jason Kipnis, Reg. No. 40,680

David Cavanaugh, Reg. No. 36,476

Joseph F. Haag, Reg. No. 42,612

Wilmer Cutler Pickering Hale and Dorr LLP

950 Page Mill Road

Palo Alto, CA 94304

Tel: (650) 858-6000

Email: Jason.Kipnis@wilmerhale.com

#### UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

Intel Corporation Petitioner

v.

Qualcomm Incorporated Patent Owner

Case IPR2018-01295

PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 9,535,490 CHALLENGING CLAIMS 16-17 AND 22-24

# **TABLE OF CONTENTS**

| I.   | INTF                                       | RODUCTION1                                 |  |  |  |

|------|--------------------------------------------|--------------------------------------------|--|--|--|

| II.  | MANDATORY NOTICES1                         |                                            |  |  |  |

|      | A.                                         | Real Party-in-Interest1                    |  |  |  |

|      | B.                                         | Related Matters1                           |  |  |  |

|      | C.                                         | Counsel2                                   |  |  |  |

|      | D.                                         | Service Information2                       |  |  |  |

| III. | CER                                        | ERTIFICATION OF GROUNDS FOR STANDING       |  |  |  |

| IV.  | OVERVIEW OF CHALLENGE AND RELIEF REQUESTED |                                            |  |  |  |

|      | A.                                         | Prior Art Patents and Printed Publications |  |  |  |

|      | B.                                         | Grounds for Challenge4                     |  |  |  |

| V.   | TEC                                        | TECHNOLOGY BACKGROUND4                     |  |  |  |

|      | A.                                         | Processor-To-Processor Communications4     |  |  |  |

|      | B.                                         | Communication Bus Power-Saving States6     |  |  |  |

|      | C.                                         | Data Buffering7                            |  |  |  |

| VI.  | THE                                        | '490 PATENT9                               |  |  |  |

|      | A.                                         | Alleged Problem of the Prior Art10         |  |  |  |

|      | B.                                         | Purported Solution of the '490 Patent11    |  |  |  |

|      | C.                                         | Prosecution History of the '490 Patent16   |  |  |  |

| VII. | CLAIM CONSTRUCTION18                       |                                            |  |  |  |

# U.S. Patent No. 9,535,490 Petition for *Inter Partes* Review

|       | А.                                         | "trigg                                                                                                          | gered by" / "triggers"                  | 19 |  |  |

|-------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|--|--|

| VIII. | OVERVIEW OF PRINCIPAL PRIOR ART REFERENCES |                                                                                                                 |                                         |    |  |  |

|       | A.                                         | U.S.                                                                                                            | Patent No. 9,329,671 To Heinrich et al  | 20 |  |  |

|       | B.                                         | U.S.                                                                                                            | Patent No. 8,160,000 to Balasubramanian | 23 |  |  |

|       | C.                                         | U.S.                                                                                                            | Patent No. 8,112,646 to Tsai            | 27 |  |  |

| IX.   | SPECIFIC GROUNDS FOR PETITION              |                                                                                                                 |                                         |    |  |  |

|       | A.                                         | Ground 1: Claims 16, 22, 23, and 24 Are Rendered<br>Obvious By Heinrich In View Of Balasubramanian              |                                         |    |  |  |

|       |                                            | 1.                                                                                                              | Claim 16                                | 29 |  |  |

|       |                                            | 2.                                                                                                              | Claim 22                                |    |  |  |

|       |                                            | 3.                                                                                                              | Claim 23                                | 66 |  |  |

|       |                                            | 4.                                                                                                              | Claim 24                                | 67 |  |  |

|       | B.                                         | Ground 2: Claim 17 is Rendered Obvious by the<br>Combination of Heinrich and Balasubramanian in View<br>of Tsai |                                         |    |  |  |

|       |                                            | 1.                                                                                                              | Claim 17                                | 68 |  |  |

| X.    | CON                                        | CLUS                                                                                                            | ION                                     | 72 |  |  |

#### I. INTRODUCTION

Intel Corporation ("Petitioner") respectfully submits this Petition for *Inter Partes* Review of claims 16-17 and 22-24 of U.S. Patent No. 9,535,490 (the "'490 patent") (Ex-1201). The '490 patent discloses a device comprising two processors that communicate over a bus using a trigger protocol. *See* Ex-1201, claims 16-17, 22-24. However, there was nothing inventive about the claimed device as of the earliest priority date of the '490 patent, and the claimed concepts had been wellknown long before the '490 patent's earliest priority date. Thus, claims 16-17 and 22-24 of the '490 patent should be canceled.

# II. MANDATORY NOTICES

#### A. Real Party-in-Interest

Intel Corporation is the real party-in-interest and submits this *inter partes* review petition for review of certain claims of U.S. Patent No. 9,535,490. Petitioner also identifies Apple Inc. ("Apple") as a real party-in-interest.

# **B.** Related Matters

Qualcomm Incorporated ("Qualcomm" or "Patent Owner") has asserted the '490 patent against Apple in *Certain Mobile Elec. Devices and Radio Frequency Components Thereof*, Inv. No. 337-TA-1065 (Int'l Trade Comm'n) currently pending before the International Trade Commission. Qualcomm also has asserted the '490 patent against Apple in *Qualcomm Inc. v. Apple. Inc.*, Case No. 3:17-cv-01375-DMS-MDD (S.D. Cal.).

Concurrently with this *inter partes* review petition, Petitioner is also filing *inter partes* review petitions for claims 1-6 and 8 of the '490 patent (IPR2018-01293) and claim 31 of the '490 patent (IPR2018-01261). Petitioner requests that these petitions be assigned to the same panel.

#### C. Counsel

Lead Counsel: Jason Kipnis (Registration No. 40,680)

Backup Counsel: David L. Cavanaugh (Registration No. 36,476)

Backup Counsel: Joseph F. Haag (Registration No. 42,612)

Petitioner also plans to file pro hac vice applications for Joseph Mueller,

Nina Tallon, and Todd Zubler, each counsel of record in the pending litigation.

#### **D.** Service Information

Email: Jason.Kipnis@wilmerhale.com; David.Cavanaugh@wilmerhale.com;

Joseph.Haag@wilmerhale.com.

Post and hand delivery: Wilmer Cutler Pickering Hale and Dorr LLP

950 Page Mill Road

Palo Alto, CA 94304

Telephone: 650-858-6000 Facsimile: 650-858-6100

Petitioner consents to service by email.

#### III. CERTIFICATION OF GROUNDS FOR STANDING

Petitioner certifies pursuant to Rule 42.104(a) that the patent for which review is sought is available for *inter partes* review and that Petitioner is not barred or estopped from requesting an *inter partes* review challenging the patent claims on the grounds identified in this Petition.

#### IV. OVERVIEW OF CHALLENGE AND RELIEF REQUESTED

Pursuant to Rules 42.22(a)(1) and 42.104(b)(1)-(2), Petitioner challenges claims 16-17 and 22-24 of the '490 patent (Ex-1201).

#### A. Prior Art Patents and Printed Publications

Petitioner relies upon the following patents and printed publications:

- U.S. Patent No. 9,329,671 to Heinrich et al. ("Heinrich") (Ex-1204), which was filed January 29, 2013 and issued May 3, 2016, is prior art to the '490 patent at least under post-AIA 35 U.S.C. § 102(a)(2).

- U.S. Patent No. 8,160,000 to Balasubramanian ("Balasubramanian") (Ex-1205), which was filed October 3, 2006 and issued April 17, 2012, is prior art to the '490 patent at least under post-AIA 35 U.S.C. § 102(a)(1).

- U.S. Patent No. 8,112,646 to Tsai ("Tsai") (Ex-1217), which was filed September 11, 2008 and issued February 7, 2012, is prior art to the '490 patent at least under post-AIA 35 U.S.C. § 102(b).

# **B.** Grounds for Challenge

Petitioner requests cancellation of claims 16-17 and 22-24 as unpatentable under 35 U.S.C. § 103. This Petition, which is supported by the Declaration of Dr. Bill Lin ("Lin") (Ex-1202), demonstrates a reasonable likelihood that Petitioner will prevail with respect to at least one challenged claim and that each challenged claim is unpatentable for the reasons cited herein. *See* 35 U.S.C. § 314(a).

The grounds for challenge based on the foregoing prior art references include the following:

|    | Grounds | Reference(s)                                                   | Challenged Claims |

|----|---------|----------------------------------------------------------------|-------------------|

| 1. | § 103   | Combination of Heinrich and<br>Balasubramanian                 | 16, 22-24         |

| 2. | § 103   | Combination of Heinrich and<br>Balasubramanian in view of Tsai | 17                |

# V. TECHNOLOGY BACKGROUND

#### A. Processor-To-Processor Communications

The '490 patent generally relates to communications between two processing nodes within a computing device—(1) a modem processor, which typically manages the transmission and reception of data over a network (*e.g.*, over a cellular or Wi-Fi network) and (2) an application processor, which typically runs applications on the device (*e.g.*, email, text messaging, and web browsing programs). Lin-¶28.

For example, when a mobile device user composes a text message using a software application running on the device's application processor, the application processor transmits the text data to a modem processor. After processing the data to allow it to be transmitted wirelessly, the modem processor manages transmission of the data to the relevant network. Similarly, when a network transmits data to the mobile device (*e.g.*, data for a voice call or a requested web page), the modem processor processes the incoming data and then sends it to the application processor. The relevant application on the application processor can use the data (*e.g.*, a phone application can play received voice data or a web browser application can display received web page data). Lin-¶29.

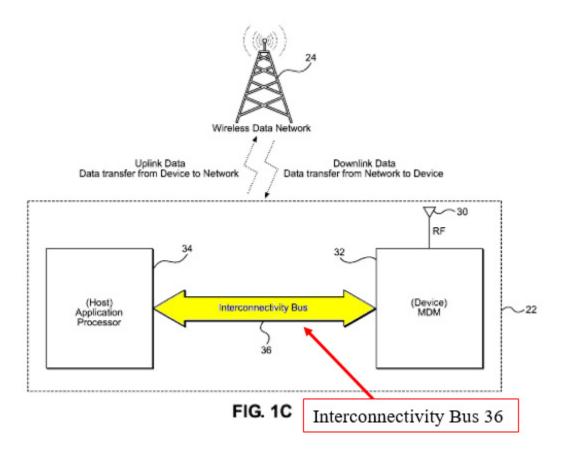

These processor-to-processor communications typically occur over a wire or set of wires commonly known as a communication "bus." For instance, Figure 1C of the '490 patent below shows application processor 34 and mobile device modem ("MDM") 32 connected by interconnectivity bus 36:

Ex-1201, Fig. 1C (annotations added). As shown in the figure, the '490 patent refers to data sent from the application processor to the modem processor and then to the wireless data network as "uplink data", and it refers to data sent from that network to the modem processor and then to the application processor as "downlink" data. Lin-¶30.

# **B.** Communication Bus Power-Saving States

Like other electronic components, a communication bus must be powered for electrical signals to flow across it. But maintaining a bus in an "active" state consumes power. Therefore, buses are often designed to have one or more powersaving ("low power") states, during which the bus or components attached to the bus are powered down (partially or fully) such that data cannot flow across the bus. Ex-1201, 8:6-19 ("In conventional mobile terminals that have a PCIe interconnectivity bus (i.e., the interconnectivity bus 36), the PCIe standard allows the interconnectivity bus 36 to be placed into a sleep mode . . . . This problem is not unique to the PCIe interconnectivity bus 36."). Lin-¶31.

If a processor has data to transmit to another processor, the data can be sent right away if the bus connecting them is already in an active state. However, if the bus is in a low power state at the time, the bus must transition to the active state before the processor can send the data. As the '490 patent notes, these bus transitions themselves require power. Ex-1201, 8:9-12 ("While placing the interconnectivity bus 36 in a sleep mode generally saves power, such sleep modes do have a drawback in that they consume relatively large amounts of power as they transition out of the sleep mode."). Lin-¶32.

#### C. Data Buffering

A first processor may have data to send to a second processor, but the communication bus between them, or the second processor itself may be inactive, thus preventing the transmission of the data. The first processor could wake the bus whenever it has data to send, but frequent transitions of the bus from a low power state to a high power state can waste power. The first processor could simply discard the data—but that would result in lost or incomplete data. Lin-¶33.

7

Given these obvious drawbacks, it has long been known that processor-toprocessor data can be held in a "buffer" (a temporary, short-term memory) during periods when the bus (or receiving processor) is in a low power state. Lin-¶34. *See, e.g.*, Ex-1205, 5:47-51, 6:40-43, and 9:4-7; Ex-1204, 8:21-64. Collecting multiple data packets over time and sending them together after the bus transitions to an active state—rather than waking the bus from a low power state each time the processor receives a data packet—saves power by reducing the number of bus power state transitions. Lin-¶34.

Buffers, however, have limitations. Once a buffer is filled with data, additional incoming packets cannot be stored. Moreover, if a buffer stores data for too long, the data may become too old to be useful (*i.e.*, stale), or the delay may negatively affect applications expecting to receive the data. For example, in a realtime phone conversation, if voice data is held in a buffer too long, users can experience unpleasant gaps in communication. Therefore, a processor must typically send buffered data before the buffer fills up and before the data becomes stale. Lin-¶35.

The prior art describes many ways to determine when to send buffered data. One example is a "timer," which tracks how long data has been held in a buffer; when the timer expires, the buffered data is sent. *See*, *e.g.*, Ex-1204, 9:22-24; Ex-1205, 1:66-2:2; 6:55-65; 9:7-9. Another example is a "counter," which can track

<sup>8</sup>

the number of data packets or bytes held in the buffer or count a number of specified events that occur. *See*, *e.g.*, Ex-1205, 2:3-8; 6:55-65; 9:7-9. When the counter reaches a predefined threshold (*e.g.*, a predefined number of packets, data, or events), the buffered data is sent. *Id.* Such timers and counters can be used together to ensure that (1) the buffer does not hold data for too long and (2) the buffer does not fill up. Lin-¶36.

#### VI. THE '490 PATENT

The application leading to the '490 patent (Ex-1201) was filed as U.S. Application No. 14/568,694 on December 12, 2014. The '490 patent claims priority to U.S. Provisional Application No. 61/916,498, filed December 16, 2013, and U.S. Provisional Application No. 62/019,073, filed June 30, 2014.<sup>1</sup>

The '490 patent is directed to systems and methods that claim to conserve power by limiting the number of transitions of a device between an active state and a low power state.

<sup>&</sup>lt;sup>1</sup> For purposes of this Petition, Petitioner treats December 16, 2013 as the effective filing date, but does not take any position regarding whether the claims in the '490 patent are enabled by or have written description support in the '498 and/or '073 provisional applications.

#### A. Alleged Problem of the Prior Art

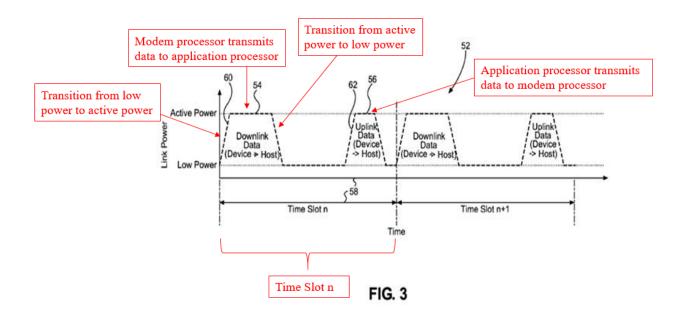

The '490 patent admits that, for prior art mobile devices containing an application processor and modem processor coupled via a communication bus, it was known that power-savings could be achieved by putting the bus into a low power state during certain periods of time. Ex-1201, 8:6-10 ("In conventional mobile terminals that have a PCIe interconnectivity bus . . ., the PCIe standard allows the interconnectivity bus 36 to be placed into a sleep mode. . . . [P]lacing the interconnectivity bus 36 in a sleep mode generally saves power. . . ."). According to the '490 patent, however, these prior art devices wasted power by transitioning power states too frequently, because they: (1) transitioned the bus from a low power state to an active state to transmit downlink data, and (2) separately performed the same bus transition again at a later time to transmit uplink data—as shown in Figure 3 below:

#### U.S. Patent No. 9,535,490 Petition for *Inter Partes* Review

Ex-1201, Fig. 3 (annotations added); *id.*, 8:35-40 (stating that "two transitions (i.e., 60, 62) from low power to active power [] each time slot 58 ... [will] consume substantial amounts of power and reduce the battery life of the mobile terminal 22"); *id.*, 8:10-12 ("[S]uch sleep modes do have a drawback in that they consume relatively large amounts of power as they transition out of the sleep mode.").

#### B. Purported Solution of the '490 Patent

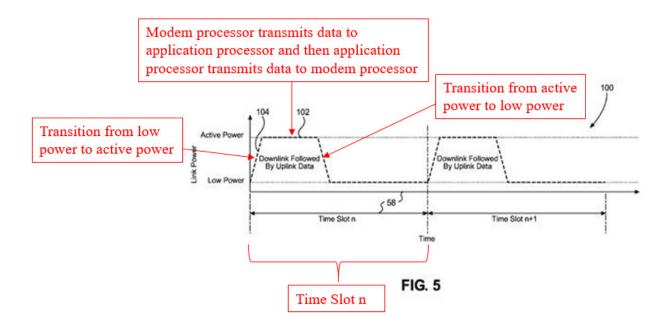

To address this supposed "problem," the '490 patent does not claim to invent a new type of processor, a new type of communication bus, or a new type of bus power-saving state. Instead, the patent claims to improve power-savings merely by transmitting buffered downlink data followed by buffered uplink data during the *same active period of the communications bus*—as shown in Figure 5 below:

Ex-1201, Fig. 5 (annotations added); *id.*, 10:40-45 ("Thus, by consolidating the data into a single active period 102, the overall time that is spent in low power may be increased, thus resulting in power savings. Additionally, power spent transitioning from a low power to active power state is reduced by elimination of the second transition 62.").

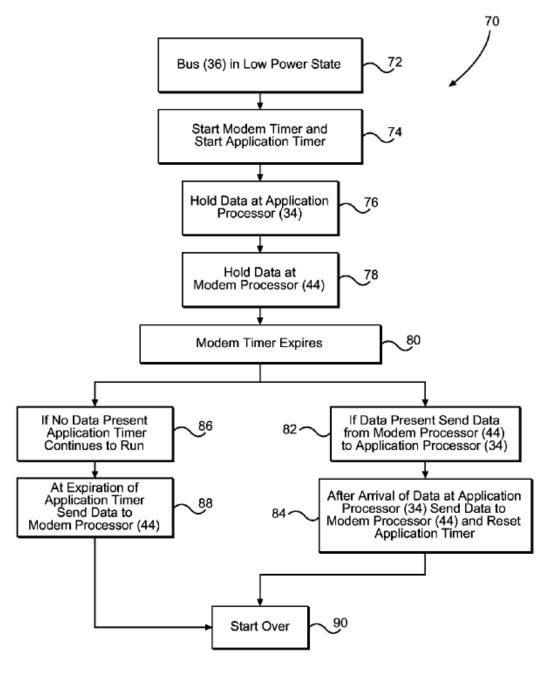

The '490 patent discusses an "exemplary" embodiment using this single bus transition scheme as shown below in Figure 4:

# FIG. 4

Ex-1201, Fig. 4. At step 72 the bus is in a "low power" state during which data cannot be transmitted over the bus. *Id.*, 9:22-23. At step 74, a timer starts at both the modem processor and application processor. *Id.*, 9:23-27. While the bus is

inactive and the timers are running, the application processor 34 holds any data that applications generate for sending to the modem processor (step 76) and the modem processor 44 holds any data that it receives from the network for sending to the application processor (step 78). *Id.*, 9:27-32 ("Data is generated by the application processor 34 and data is received from the network 12 by the modem processor 44. The application data is held at the application processor 34 (block 76) and the modem data is held at modem processor 44 (block 78) while the timers are running.").

When the modem timer expires at step 80, if the modem processor has buffered data, the bus transitions from a low power state to an active state—after which modem processor 44 sends its buffered data to application processor 34 over the communication bus (at step 82). *Id.*, 9:37-40. After receiving all the buffered data from the modem processor, the application processor treats the receipt of that data as a "trigger" that causes the application processor to send any data that it has buffered to modem processor 44 before the bus transitions back to a low power state (at step 84). *Id*.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> For steps 86 and 88 of Figure 4, the patent explains that if the modem processor has not buffered any data when the modem timer expires, the application

As detailed further below, transmitting all accumulated downlink and uplink data during the same active state was known—long before the claimed priority date of the '490 patent—as a common sense and predictable way to reduce the power consumed by a computing system. *See, e.g.*, Ex-1205, 6:63-7:6 ("[T]he transceiver 110 *then transmits the queued uplink packets over the communication link 116*. Advantageously, the queued packets may be grouped for transmission such that *all of the packets are transmitted* during *a single wake state of the transceiver 110*. For example, as discussed above the transceiver 110 may send the queued packets in relative close succession (e.g., back-to-back) over the communication link 116. As represented by block 210, during the *same single wake state the transceiver 110 also receives any downlink packets queued in the*

# network interface 112.").

Also well-known was the specific scheme disclosed in the '490 patent for how to transmit all buffered downlink and uplink data during the same active state: namely, using the receipt of buffered data from a first processing node as a "trigger" for a second processing node to send its buffered data. For example, nearly a decade before the '490 patent was filed, Balasubramanian disclosed a

processor will send any data that it has buffered to the modem processor when the application timer later expires. Ex-1201, 10:4-10.

15

system in which receipt of data from a first processing node "trigger[ed]" the transmission of data from a second processing node. *Id.*, 7:6-8 ("For example, the network interface 112 may use the *receipt* of an uplink packet as a *trigger* to transmit any downlink packets in its queue.").

# C. Prosecution History of the '490 Patent

U.S. Application No. 14/568,694 ("the '694 application), which issued as the '490 patent, was filed on December 12, 2014. The original application was filed with 29 claims, including 9 independent claims. On April 27, 2015, the Applicant added two more claims via preliminary amendment. Ex-1203 [April 27, 2015 Preliminary Amendment], 8.

Initially, all claims of the '490 patent were rejected over the prior art. The Examiner allowed the application only after the Applicant amended most of the claims to include the "trigger" limitation—which requires a second processor to be triggered to send held data to a first processor in response to receiving data from the first processor. In particular, on June 10, 2016, the Examiner rejected all pending claims over PCT Publication No. WO 2009/039034 ("the Intel PCT") (Ex-1206) and U.S. Patent No. 6,021,264 ("Morita") (Ex-1207). *See* Ex-1203 [6/10/2016 Office Action], 3-9. In response to this rejection, the Applicant amended claim 15 (which issued as claim 16) to include the "trigger" limitation as shown below:

15. (Currently Amended) A method of controlling power consumption in a computing device, comprising:

holding data received by a modem processor from a remote network until expiration of a downlink timer;

passing the data received by the modem processor to an application processor over an interconnectivity bus; and

holding application data generated by an application associated with the application processor until receipt of the data from the modem processor or expiration of an uplink timer, whichever occurs first,

wherein receipt of the data from the modem processor triggers passing the data received by the application processor to the modem processor over the interconnectivity bus before the interconnectivity bus transitions from an active power state to a low power state.

Ex-1203 [8/24/2016 Response], 2. The Applicant similarly amended original independent claims 1, 20, and 24-28 to include a "trigger" limitation. *Id.*, 14 (commenting on the amendment to claim 1 and explaining that "[i]ndependent claims 15, 20, and 24-29 have been amended to recite similar features and are therefore allowable for at least the same reasons as claim 1....").

17

The Applicant argued that Morita does not disclose that the transmission of data from the application processor to the modem processor is "triggered by" receipt of data from the modem processor. *Id.* Instead, the Applicant argued, Morita discloses "delay[ing]" transmission of data "by a predetermined time length." *Id.* As a result, the Applicant argued, that transmission could not be "triggered by" or "responsive to" receipt of data from the modem processor because the data is held for a "predetermined time length," which, by its definition, is a length of time determined in advance of receiving any data. *Id.* The Applicant did not separately argue that the Intel PCT fails to disclose any of the other limitations. *Id.*, 13-15.

The Examiner subsequently allowed the claims as amended.<sup>3</sup>

#### **VII. CLAIM CONSTRUCTION**

Petitioner has set forth below its proposed constructions of certain terms of the '490 patent and its support for the constructions. 37 C.F.R. 42.100(b) states that claims must be given their broadest reasonable construction in light of the specification ("BRC standard"). On May 8, 2018, the USPTO proposed rulemaking that would change the standard for construing claims from the BRC

<sup>&</sup>lt;sup>3</sup> The claims were re-ordered such that original claims 15, 20, and 24-29 became issued claims 16, 22, and 26-31, respectively.

standard to the Phillips standard. In anticipation that the rule change will apply to these proceedings, Petitioner construes the claims based on the standard set forth in Phillips. Petitioner is not aware of any difference in how the claims would be construed under the BRC standard. The scope of the challenged claims could not be broader under the proposed Phillips construction than it could be under the BRC standard. Therefore, the challenged claims would also be unpatentable under the BRC standard.

A person of ordinary skill in the art ("POSA") of the '490 patent would have had a Master's degree in Electrical Engineering, Computer Engineering, or Computer Science plus at least two years of experience in mobile device architecture and multiprocessor systems, or alternatively a Bachelor's degree in one of those fields plus at least four years of experience in mobile device architecture and multiprocessor systems.

#### A. "triggered by" / "triggers"

As used in the '490 patent, a POSA would have understood the phrase "triggered by" to mean "initiated in response to". The '490 patent does not specifically define the term "trigger," but implies that "triggering" occurs when an action is taken in response to a stimulus. *See* Ex-1201, 2:3-6 ("On receipt of the data from the modem processor, the application processor sends data held by the application processor to the modem processor over the PCIe interconnectivity

19

bus."); see also id., 11:15-18, 11:39-46. This understanding of "trigger" is supported by the claims themselves. For example, claim 1 states that the application processor is "triggered by the receipt of" data from the modem processor, and suggests that this is synonymous with being "responsive to the receipt of' data from the modem processor. See id., claim 1. The prosecution history also supports this understanding of "triggered by." See Ex-1203 [8/24/2016 Response], 14 ("[T]here is no disclosure or suggestion that the 'predetermined time length' is even capable of being 'triggered by' or otherwise 'responsive to the receipt of the modem processor to application processor data,' as required by claim 1."). And, this understanding of "triggered by" is also supported by various dictionaries. See Ex-1212 [Heritage Dictionary], 1444 ("trigger[:]... 1. to set off; initiate"); Ex-1213 [Oxford Dictionary], 1541 ("trigger ... cause to happen or exist"); Ex- 1214 [Merriam-Webster's Dictionary], 1337 ("trigger[:]... to initiate, actuate, or set off by a trigger").

#### **VIII. OVERVIEW OF PRINCIPAL PRIOR ART REFERENCES**

#### A. U.S. Patent No. 9,329,671 To Heinrich et al.

U.S. Patent No. 9,329,671 to Heinrich et al. was filed January 29, 2013 and issued May 3, 2016. Heinrich is therefore prior art under at least 35 U.S.C. § 102(a)(2).

20

#### U.S. Patent No. 9,535,490 Petition for *Inter Partes* Review

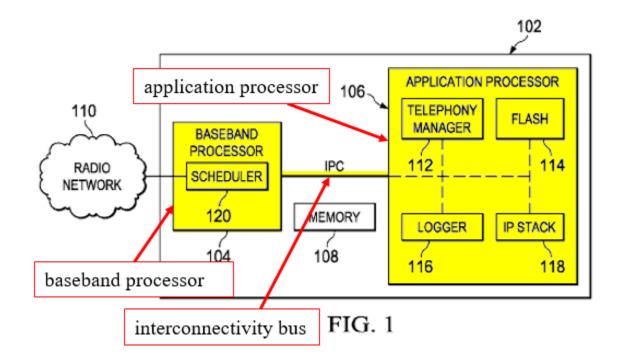

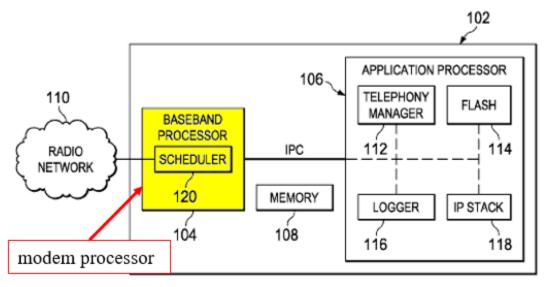

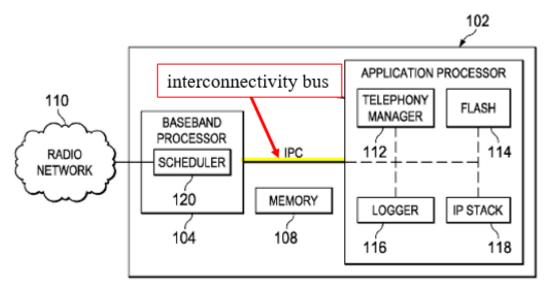

As shown below, Heinrich discloses a device with a baseband processor 104 and an application processor 106 that communicate with each other over an interconnectivity bus:

Ex-1204, Fig. 1 (annotations added); *id.*, 4:26-46 ("FIG. 1 shows . . . a *baseband processor 104* . . ., an *application processor (AP) 106*. . . , [and] a physical interface configured for communicating IPC activities between the baseband processor 104 and the application processor 106.").

In Heinrich, data communications over the interconnectivity bus—referred to as "IPC [inter processor communication] activities"—are buffered so that transmission to the application processor can be delayed. *Id.*, 7:65-8:1 ("IPC activities that are not real-time sensitive . . . can be *delayed* until it is deemed profitable to run them."); 8:14-15 ("Those IPC activities which are not real-time sensitive can be *delayed*."). A scheduler implemented as software in the baseband processor includes "timers" that, upon expiration, trigger transmission of the buffered data over the bus to the application processor. *Id.*, 7:7-17 ("[T]here is a *centralized scheduler 120* which is associated with the baseband processor 104... "); 9:2-6 ("[T]he scheduler 120 allocates a respective *timer*, herein referred to as a *'lazy timer'*, to each of the non real-time sensitive IPC activities identified in step S302...."); 9:14-16 ("*When one of the lazy timers fires this causes the respective IPC activity to be communicated on the IPC interface to the application processor 106*, ...").

Each data communication ("IPC activity") is assigned a timer. *Id.*, 9:2-6. When any one of the assigned timers expires ("fires"), the baseband processor sends the buffered data over the bus to the application processor. *Id.*, 9:11-21. Heinrich explains that, by grouping together the transmissions, the processor can reduce the number of times that the application processor enters and exits sleep mode, thereby reducing the power consumption of the computer system. *Id.*, 4:6-12.

Heinrich also discloses that the same technique—buffering data and sending it all at once upon expiration of a timer—can be used to control transmissions from the application processor over the bus to the baseband processor. *Id.*, 12:52-55 ("A *scheduler may implement the same scheduling techniques* as those described above, but configured to schedule IPC activities *from the application processor 106 to the baseband processor 104.*").

Heinrich also discloses that the scheduler of its baseband processor can detect that the physical IPC interface is in an active state, and the application processor is awake, when the baseband processor transmits data to the application processor. *Id.*, 9:43-46 ("In a second example, the scheduler 120 can deduce that the application processor 106 will be in the awake mode by determining that realtime sensitive IPC activities are being sent to the application processor 106 . . . . "); 9:54-62 ("The scheduler 120 can perform the determination that the application processor 106 is in the awake mode by receiving a notification that the physical IPC interface is in an active state. . . . [N]on real-time sensitive IPC activities are sent to the application processor 106 at a time when the application processor 106 is in the awake mode due to the communication of a previous real-time sensitive IPC activity.").

# B. U.S. Patent No. 8,160,000 to Balasubramanian

U.S. Patent No. 8,160,000 to Balasubramanian was filed October 3, 2006 and issued April 17, 2012. Balasubramanian is therefore prior art under at least 35 U.S.C. § 102(a)(1).

23

#### U.S. Patent No. 9,535,490 Petition for *Inter Partes* Review

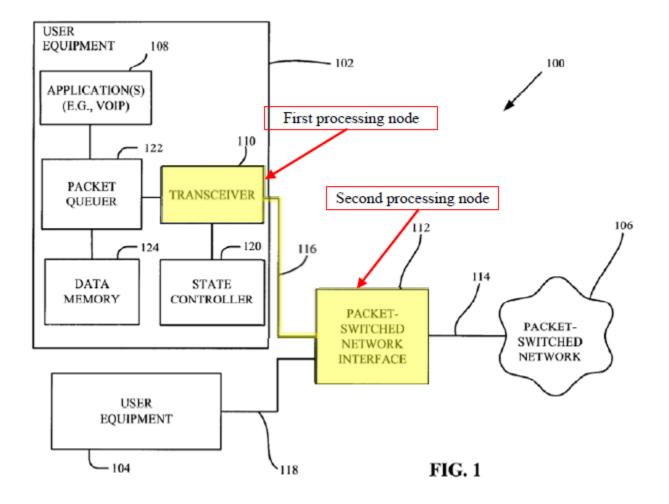

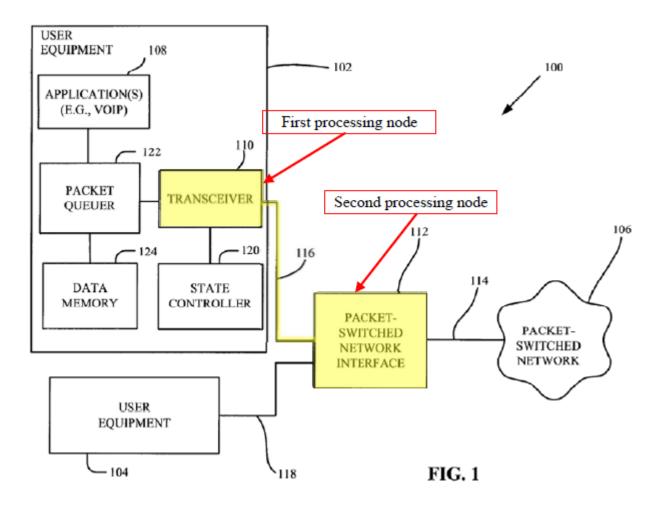

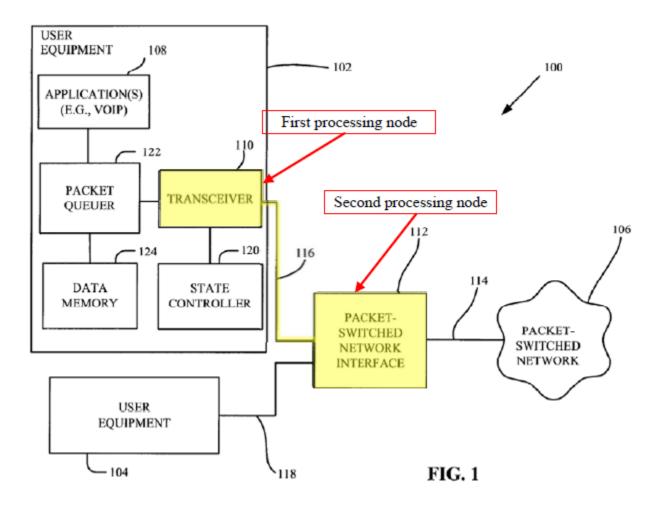

Balasubramanian describes a system where two processing nodes—for example, a transceiver 110 in a user device such as a cell phone, and a network interface 112 to a packet-switched network—communicate with each other over a communication link 116, which can be a wired connection:

Ex-1205, Fig. 1 (annotations added).

Balasubramanian discloses a scheme to synchronize transfers over the communication link 116, in which the transceiver 110 sends packets to the network interface 112, which *triggers* the network interface 112 to send any buffered

packets back to the transceiver 110 during the same active state of the transceiver 110. *Id.*, 6:63-7:8 ("[T]he transceiver 110 *then transmits the queued uplink packets over the communication link 116*. Advantageously, the queued packets may be grouped for transmission such that *all of the packets are transmitted* during a single wake state of the transceiver 110.... As represented by block 210, during the *same single wake state the transceiver 110 also receives any downlink packets queued in the network interface 112*. For example, the network interface 112 may use the *receipt of an uplink packet as a trigger* to transmit any downlink packets in its queue."); *see also id.*, 2:23-24.

Balasubramanian discloses two processing nodes communicating over a wired link, like the bus in Heinrich. *Id.*, 4:50-54 ("[T]he subnetwork [which includes the transceiver 110 and the network interface 112] may communicate via some other protocol (e.g. a wire-based protocol or a wireless-based protocol) over communication links 116 and 118."). Lin-¶61.

Like Heinrich and the '490 patent, Balasubramanian is directed to conserving power by reducing the number of transitions from a low power mode to an active mode. Balasubramanian explains that a "transceiver" must transition from a "suspend" (low power) state to an "active" state to allow the transceiver to transmit its buffered data to the network interface. According to Balasubramanian, reducing the number of times the transceiver transitions from a suspend state into an active state reduces power consumption. Ex-1205, 5:55-61 ("Here, *power may be conserved* by not transitioning the transceiver 110 from the suspended state to the active state every time a packet has been generated for transmission . . . . Accordingly, power savings may be achieved by rescheduling the packet traffic into groups of traffic.").

In order to reduce the number of power state transitions, Balasubramanian uses the same technique as the '490 patent—buffering data intended for another processor during periods when the communication bus or other processor is inactive, and then later transmitting the buffered data from both processors during the same active state. *Id.*, 5:65-6:4 ("[T]he user equipment 102 may include a packet queued component 122 that facilitates queuing and temporarily *storing the packets*.... When the transceiver 110 is transitioned to an active state, the queued packets may be provided to the transceiver 110 for transmission to the network 106 (via interface 112)."); *id.*, 6:65-67 ("Advantageously, the queued packets may be grouped for transmission such that *all of the packets are transmitted during a single wake state* of the transceiver 110.").

In addition to the "trigger" mechanism described above, Balasubramanian also uses a timer to determine when to transmit packets from the transceiver 110 to the network interface 112 (similar to Heinrich and the '490 patent). *Id.*, 9:33-34 (describing a "*timer*/counter 426 to determine when to make the packets in the

<sup>26</sup>

packet queue 422 available. . . . "); *id.*, 6:48-49 ("[T]he packets may be queued for configurable amount of time."); *id.*, 6:55-60 ("[O]nce the *configurable amount of time has elapsed* or the configurable number of packets have been queued, the *transceiver 110 transitions* to an active (e.g., wake) state..., and *establish communications with the network interface 112*."); *id.*, 9:7-9 ("[P]ackets may be queued for a configurable amount of time ....").

#### C. U.S. Patent No. 8,112,646 to Tsai

U.S. Patent No. 8,112,646 to Tsai was filed September 11, 2008 and issued February 7, 2012. Tsai is therefore prior art under at least 35 U.S.C. § 102(b).

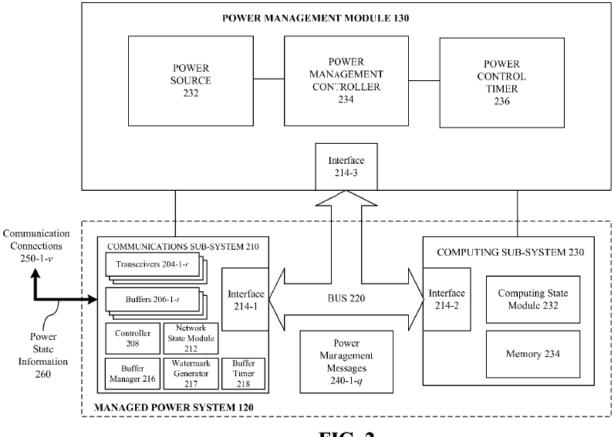

As shown below, Tsai describes a device in which a communications subsystem 210 communicates with a computing sub-system 230 over a bus 220.

FIG. 2

Tsai explains that communications sub-system 210 includes a baseband processor (Ex-1217, 5:59-6:5) and that computing sub-system 230 includes its own processor (*id.*, 7:33-44). Tsai further teaches that communication bus 220 can be implemented using a variety of protocols, "includ[ing] without limitation

Peripheral Component Interconnect (PCI) [and] PCI Express (PCIe)...."). Id., 8:16-30.

#### IX. SPECIFIC GROUNDS FOR PETITION

Pursuant to Rule 42.104(b)(4)-(5), the following sections describe in detail how the prior art discloses each and every limitation of the challenged claims of the '490 patent, and how the prior art renders these claims obvious. *See also* Lin-¶¶ 74-145.

# A. Ground 1: Claims 16, 22, 23, and 24 Are Rendered Obvious By Heinrich In View Of Balasubramanian

1. Claim 16

# a) [16a] Preamble: "[a] method of controlling power consumption in a computing device"

Heinrich discloses "[a] method of controlling power consumption in a computing device." Heinrich discloses a computing device that can be "a mobile phone, a tablet, a laptop computer or other embedded device able to connect to the network." See Ex-1204, 4:18-43. Heinrich teaches that "[i]t is beneficial to minimize the power consumed by the computer system." Id., 1:54-2:8. To minimize power consumption. Heinrich teaches buffering data that is not real-time sensitive and sending it all at once to reduce the number of times the bus and/or processors transition from a low power or sleep mode into a high power or active mode. *Id.*, 4:6-11 ("By grouping the non real-time sensitive IPC activities together and scheduling them for communicating to the second processor during a period in which the second processor is continuously in the first [active] mode, the number of times that the second processor enters and exits the second mode (e.g. sleep mode) is reduced."). Thus, Heinrich discloses a computing device that performs "[a] method of controlling power consumption in a computing device." Lin-¶75.

# b) [16b] "holding data received by a modem processor from a remote network until expiration of a downlink timer"

Heinrich discloses "holding data received by a modem processor from a

remote network until expiration of a downlink timer."

As shown in Figure 1, Heinrich discloses a mobile communication system

that includes a "baseband processor 104":

| F | IC | Ĵ. | 1 |

|---|----|----|---|

| _ | _  |    |   |

Ex-1204, Fig. 1 (annotations added); Lin-¶77.

Heinrich discloses that baseband processor 104 is a "modem" processor that communicates with a network. *Id.*, 4:30-36 ("The baseband processor 104 acts as a Radio Frequency (RF) *modem* to process data for *communication between the user device 102 and the network 110*.... [T]he baseband processor 104 is implemented at the user device 102 for *communicating with the radio network*  *110*."). The modem processor of Heinrich—*i.e.*, baseband processor 104—

communicates with and receives data from a remote network (*e.g.*, network 110). *Id.*

As the '490 patent explains, a "downlink timer" is a "modem timer" that, upon expiration, triggers the transmission of held data from the modem processor to the application processor. Ex-1201, 10:37-40 ("The modem timer expires (block 80). If modem data is present, the modem data is released by the modem processor 44 through the interconnectivity bus 36 to the application processor 34 (block 82)."); 10:13 ("the downlink timer (i.e., the modem timer)"), 11:32-33 ("the downlink timer (i.e., the modem timer)"). Thus, the lazy timer on the baseband processor in Heinrich is a downlink timer that, upon expiration, triggers the transmission of baseband data from the baseband processor to the application processor over the bus. Heinrich teaches that baseband processor 104 delays sending certain data to the application processor 106 over the IPC interface, and transmits such data upon expiration of a downlink timer. Id., 7:65-8:1 ("[T]he scheduler 120 identifies IPC activities that . . . can be *delayed* until it is deemed profitable to run them."). These transactions are aggregated for later transmission. *Id.*, 9:5-13 ("Each IPC activity is sent on the IPC interface when its respective lazy timer fires.... However, when one of the registered timers fires, *all registered* timers expire at the same time, causing all the aggregated IPC activities to be

*served at the same time*."). Heinrich also explains that buffering communications and sending them all at once when a timer expires results in "fewer transitions between the sleep and awake modes" and thereby "reduce[s] the power consumed." *Id.*, 10:44-51. A POSA would understand that such delayed and "aggregated IPC activities" would include "data received by a modem processor from a remote network" that would have to be held (i.e., buffered) until the baseband processor determines that it is time to transmit the held data to the application processor, such as when the timer expires. *See also id.*, 11:57-58 ("In order to delay file write accesses they are stored in a cache memory of the baseband subsystem."); Lin-¶79.

Heinrich describes "baseband memory" where baseband data is buffered. *Id.*, 11:58-66 ("The scheduler 120 schedules the file write accesses as described above such that a group of them may be retrieved from the cache memory of the baseband subsystem together and sent to the application processor 106 on the IPC interface as a group.... These files may be cached in *baseband memory* with no user impact.").

It would have been obvious to a POSA that the baseband processor in Heinrich can hold data received from a remote network in its own memory on the same chip as the processor circuitry. A processor can hold data in two known ways, on-chip or off-chip. Both well-known ways of holding data are discussed,

<sup>32</sup>

for example, in Panda et al., "On-Chip vs. Off-Chip Memory: The Data Partitioning Problem in Embedded Processor-Based Systems," Ex-1211 [Panda, ACM Transactions on Design Automation of Electronic Systems, Vol. 5, No. 3, July 2000], 682-704.

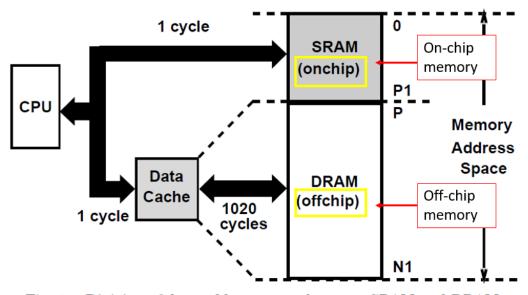

*First*, the processor could hold the data in its own memory—*i.e.*, on the same chip that includes the processor circuitry, such as in on-chip SRAM. Ex-1211, 683 ("The types of on-chip memory commonly integrated with the processor on the same chip are instruction cache, data cache, and on-chip SRAM. . . . [I]t is possible to incorporate *embedded DRAMs* along with a processor core in the same chip. . . . ").

*Second*, the data could be held on a separate or external chip—such as a memory chip. *Id.*, 683 ("[A]ccess to an off-chip memory (usually DRAM) requires relatively longer access times."). *See also id.*, 686 (Fig. 2 (annotations added), showing offchip DRAM storage and onchip SRAM and data cache storage):

U.S. Patent No. 9,535,490 Petition for *Inter Partes* Review

Fig. 2. Division of data address space between SRAM and DRAM.

A POSA would have been motivated to use "on-chip" memory to store data on the baseband processor in Heinrich for at least two reasons. *First*, using "onchip" memory to store a processor's data requires less physical space than using a separate chip dedicated to memory. *See id.*, 682-683. This allows for fewer chips in a device, reducing cost. *Id.*, 683. *Second*, accessing data from "on-chip" memory is much faster than accessing data from another chip over a separate connection, which improves device operation. *Id.* Because using on-chip memory to hold data was well-known in systems like Heinrich, a POSA would have reasonably expected the design to succeed. Lin-¶84. "When there is a design need or market pressure to solve a problem and there are a *finite number of identified*, *predictable solutions*, a person of ordinary skill has good reason to pursue the known options within his or her technical grasp." *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 421 (2007).

# c) [16c] "passing the data received by the modem processor to an application processor over an interconnectivity bus"

Heinrich discloses "passing the data received by the modem processor to an application processor over an interconnectivity bus." As shown in Figure 1, Heinrich discloses an interconnectivity bus labeled "IPC" ("inter processor communication") that couples the baseband processor 104—*i.e.*, modem processor—to the application processor 106 and allows for communication between the two processors:

FIG. 1

Ex-1204, 4:44-46 ("There is a physical interface *configured for communicating IPC activities* between the baseband processor 104 and the application processor 106."); *id.*, Fig. 1(annotations added).

The IPC bus in Heinrich is a "physical interface" that can be any one of many industry-standard buses. *Id.*, 4:46-50 ("The physical interface may, for example, be one of: (i) a Universal Serial Bus (USB) interface, (ii) a Mobile Industry Processor Interface (MIPI), such as a High-Speed Synchronous Interface (HSI), (iii) a Serial Peripheral Interface (SPI), or (iv) a shared memory.").

The baseband processor of Heinrich receives data from the network. *Id.*, 4:30-33 ("The baseband processor 104 acts as a Radio Frequency (RF) modem to process data for communication between the user device 102 and the network 110. . . . . "). The baseband processor then passes the data received from the network to the application processor over the IPC bus. *Id.*, 4:65-5:11 ("Communication between the two sub-systems (i.e. communication between the processors 104 and 106) is referred to as Inter Processor Communication (IPC). 'IPC activities' are communications between the two processors 104 and 106. The IPC activities convey various types of information. . . ., including . . . data, (e.g. Internet Protocol (IP) data for transmission between the user device 102 and another node of the radio network 110, which may be processed by the IP stack module 118) . . . . "); Lin-¶87.

# d) [16d] "holding application data generated by an application associated with the application processor until receipt of the data from the modem processor or expiration of an uplink timer, whichever occurs first"

Heinrich in view of Balasubramanian discloses "holding application data generated by an application associated with the application processor until receipt of the data from the modem processor or expiration of an uplink timer, whichever occurs first."

#### "holding application data generated by an application associated with the

*application processor*." The combination of Heinrich and Balasubramanian discloses "holding application data." As discussed above, Heinrich discloses that data is buffered prior to being sent over the bus from the baseband [modem] processor to the application processor. *See* claims [16b], [16c]. Heinrich further explains that the same methods used to transmit data from the baseband [modem] processor to the application processor—*i.e.*, buffering data and sending it all at once—can be used to transmit data from the application processor to the baseband [modem] processor. Ex-1204, 12:52-55 ("A scheduler may implement the *same scheduling techniques* as those described above [for scheduling IPC activities from the baseband processor 104 to the application processor 106], but configured to schedule IPC activities *from the application processor 106 to the baseband processor 104*."); Lin-¶89.

It would have been obvious to a POSA to construct Heinrich's application processor to hold data for the same reasons described in claim [16b]. While Heinrich does not expressly specify where such data is held, it would have been obvious to a POSA that the application processor in Heinrich can hold its data *i.e.*, the application data generated by an application associated with the application processor—in its own memory on the same chip as the processor circuitry.

As explained above in claim limitation [16b], a POSA would have understood that there were two well-known ways for data to be buffered: (1) on the same chip that includes the processor circuitry; or (2) on a separate or external chip. *See* Ex-1211, 683, 686 (Fig. 2); Lin-¶91. As with the baseband processor, a POSA would have been motivated to use "on-chip" memory to store data on the application processor in Heinrich for at least the two reasons identified above regarding claim limitation [16b].

Heinrich further discloses "data generated by an application associated with the application processor." In particular, Heinrich discloses that the application processor generates data from various multimedia applications, including, for example, applications that generate Internet Protocol data intended for communication over the remote network via the IP stack module. Ex-1204, 1:35-39; 4:51-56; 4:67-5:11 ("IPC activities' are communications between the two processors 104 and 106. The IPC activities convey various types of information ..., including ... data, (e.g. Internet Protocol (IP) data for transmission between the user device 102 and another node of the radio network 110, which may be processed by the IP stack module 118) ....."). Lin-¶92.

To the extent the Patent Owner argues that Heinrich does not explicitly disclose "data generated by an application associated with the application processor," a POSA would have understood the limitation to be inherent in Heinrich's disclosure of an application processor that includes an IP stack module. The IP stack module in Heinrich is used to process IP data transmitted between user device 102 and another node of the radio network 110. *Id.* It would have been obvious to a POSA that, in order to generate such IP data intended for transmission over the network, an *application* processor—as its name implies—would execute an application. Lin-¶93.

Thus, Heinrich in combination with Balasubramanian discloses "holding application data generated by an application associated with the application processor."

#### "until receipt of the data from the modem processor:"

The combination of Balasubramanian and Heinrich discloses holding application data "until receipt of the data from the modem processor."

Heinrich teaches various techniques to determine when to send data from the application processor to the baseband processor. These techniques include (1) a

timer that triggers transmission of data when the timer expires or (2) more generally, upon any other determination that informs the application processor that the baseband processor is in an "awake mode" and can therefore receive data. Ex-1204, 9:22-26 ("In general, each lazy timer is configured to fire in response to the earlier of: (i) the expiry of a respective deadline provided to the lazy timer before which it is expected to fire, or (ii) a determination that the application processor 106 is in the awake mode.").<sup>4</sup>

Heinrich also discloses that the scheduler of its baseband processor can detect that the physical IPC interface is in an active state, and the application processor is awake, when the baseband processor transmits data to the application processor. *Id.*, 9:50-62 (emphasis added) ("In order to determine that *real-time sensitive IPC activities are being sent to the application processor 106*, the scheduler 120 registers to the underlying physical IPC interface in order to receive notifications of state changes of the IPC interface. The *scheduler 120 can perform the determination that the application processor 106 is in the awake mode by*

<sup>&</sup>lt;sup>4</sup> The quoted portion of Heinrich describes the transmission of data from the baseband processor. However, as explained above, Heinrich discloses that the same techniques can be used to control transmission of data from the application processor to the baseband processor. Ex-1204, 12:52-55.

*receiving a notification that the physical IPC interface is in an active state*. When the IPC interface enters an active state the scheduler 120 deems it appropriate to fire all registered lazy timers. In this way the non real-time sensitive IPC activities are sent to the application processor 106 at a time when the application processor 106 is in the awake mode due to the communication of a previous real-time sensitive IPC activity."). Because Heinrich notes that the scheduling techniques described with respect to the baseband processor are also applicable to the application processor (*see id.*, 12:52-55), Heinrich teaches that its application processor can include a scheduler that can detect that the physical IPC interface is in an active state, and the baseband processor is awake. *Id.*, 9:50-62, 12:47-64. Lin-¶97

While Heinrich does not explicitly disclose holding data intended for transmission to another processor until receipt of data from the other processor, Balasubramanian discloses such a technique. In particular, Balasubramanian discloses holding (*e.g.*, queuing), at a second processing node (*e.g.*, network interface 112), data (*e.g.*, downlink packets) to be sent to a first processing node (*e.g.*, transceiver 110) until "trigger[ed]" by "receipt" of data (*e.g.*, uplink packets) from the first processing node over a bus (*e.g.*, communication link 116):

41

Ex-1205, Fig. 1 (annotations added); *id.*, 6:63-7:8 ("As represented by block 208, the *transceiver 110 then transmits the queued uplink packets over the*

*communication link 116*. Advantageously, the queued packets may be grouped for transmission such that *all of the packets are transmitted* during a single wake state of the transceiver 110.... As represented by block 210, during the same single wake state the transceiver 110 also receives any downlink packets queued in the network interface 112. For example, the *network interface 112* may use the

*receipt* of an *uplink* packet as a *trigger* to transmit any *downlink* packets in its queue.").

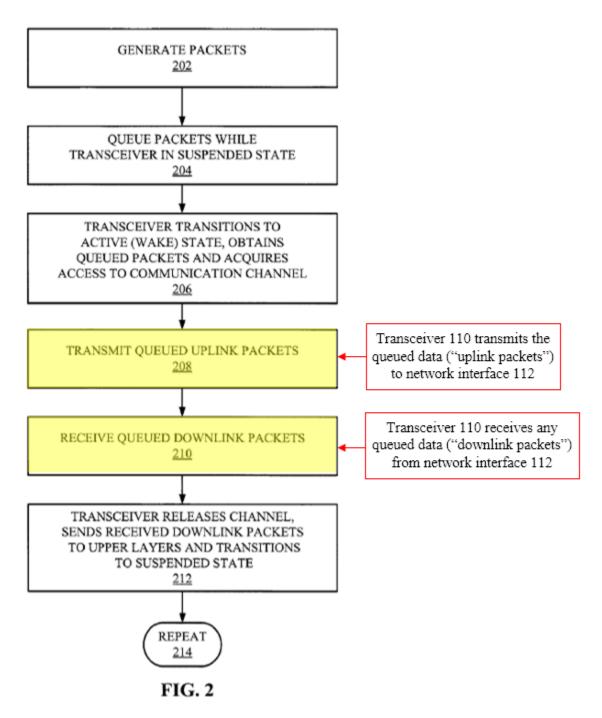

Figure 2 of Balasubramanian also discloses this feature. Consistent with the disclosure in Balasubramanian, column 6, line 63 through column 7, line 8, Figure 2 discloses that at step 208, the transceiver 110 transmits all its queued packets over the communication link 116 to the network interface 112. In response, as seen in step 210, the network interface 112 will transmit its queued packets to the transceiver 110.

Ex-1205, Fig. 2 (annotations added); *id.*, 6:63-7:8.

Accordingly, Balasubramanian discloses that the "trigger" for the

transmission of data from the second processing node (network interface 112) to

the first processing node (transceiver 110) is the reception at the second processing node of the queued packets from the first processing node. Lin-¶100. Thus, the combination of Heinrich and Balasubramanian teaches the claim limitation "until receipt of the data from the modem processor."<sup>5</sup>

### "holding application data ... until ... expiration of an uplink timer":

Heinrich discloses holding application data until a timer—referred to as a "lazy timer"—expires. *See, e.g.*, Ex-1204, 8:14-15 ("Those IPC activities which are not real-time sensitive can be delayed."); 9:2-5 ("[T]he scheduler 120 allocates a respective timer, herein referred to as a 'lazy timer', to each of the non real-time sensitive IPC activities identified in step S302."); 12:55-59. When the timer expires, the application processor sends the held data to the modem processor. *Id.*, 9:11-13 ("[W]hen one of the registered timers fires, all registered timers expire at the same time, causing all the aggregated IPC activities to be served at the same time."); 12:52-55 ("A scheduler may implement the same scheduling techniques as those described above, but configured to schedule IPC activities *from the application processor 106 to the baseband processor 104.*"); Lin-¶101.

<sup>&</sup>lt;sup>5</sup> This Petition sets forth reasons why a POSA would combine Heinrich and Balasubramanian in the section immediately below.

As the '490 patent explains, an "uplink timer" is an "application timer" that, upon expiration, triggers the transmission of held data from the application processor to the modem processor. Ex-1201, 10:7-9 ("At the expiration of the application timer, the application processor 34 sends any held data to the modem processor 44 through the interconnectivity bus 36...."); 10:11-12 ("the uplink timer (i.e., the application timer)"), 11:30-31 ("the uplink timer (i.e., the application timer)"). Thus, the lazy timer on the application processor in Heinrich is an uplink timer that, upon expiration, triggers the transmission of application data from the application processor to the baseband processor over the bus. Lin-¶102.

*<u>"whichever occurs first"</u>* As described above, Heinrich in view of Balasubramanian teaches two trigger mechanisms that result in sending data from the application processor to the modem processor: (1) receipt of previously stored data from the modem processor; and (2) expiration of an uplink timer at the application processor.

A POSA would have understood that since both trigger mechanisms result in the transmission of held data from the application processor, whichever trigger occurs first causes transmission of the data over the bus. In fact, Heinrich itself acknowledges that when an action can be triggered by two different events, it will be triggered in response to the first to occur of those two events. Ex-1204, 9:22-26

46

U.S. Patent No. 9,535,490 Petition for *Inter Partes* Review

("In general, each lazy timer is configured to fire in response to *the earlier of*: (i) the expiry of a respective deadline provided to the lazy timer before which it is expected to fire, or (ii) a determination that the application processor 106 is in the awake mode."). Lin-¶104.

e) [16e] "wherein receipt of the data from the modem processor triggers passing the data received by the application processor to the modem processor over the interconnectivity bus before the interconnectivity bus transitions from an active power state to a low power state"

Heinrich in view of Balasubramanian discloses that "receipt of the data from the modem processor triggers passing the data received by the application processor to the modem processor over the interconnectivity bus before the interconnectivity bus transitions from an active power state to a low power state."

For the reasons described above, the combination of Heinrich and Balasubramanian discloses that "receipt of the data from the modem processor triggers passing the data received by the application processor to the modem processor over the interconnectivity bus." *See* claim [16d]. Element [16e] further requires that the transmission of data from the application processor to the modem processor must occur "before the interconnectivity bus transitions from an active power state to a low power state." Heinrich teaches that one can use various techniques to determine when to send data from the application processor to the baseband processor. These techniques include a timer that triggers transmission of data (1) when the timer expires or (2) more generally, upon any other determination that informs the application processor that the baseband processor is in an "awake mode" and can therefore receive data. Ex-1204, 9:22-26 ("In general, each lazy timer is configured to fire in response to the earlier of: (i) the expiry of a respective deadline provided to the lazy timer before which it is expected to fire, or (ii) a determination that the [application] processor 106 is in the awake mode.").<sup>6</sup> More generally, Heinrich discloses waiting until the "best possible time to trigger" transmission of data from one processor to another. *Id.*, 7:65-8:6 ("[T]he scheduler 120 identifies IPC activities that are not real-time sensitive and which can be

<sup>6</sup> The quoted portion of Heinrich describes the transmission of data from the baseband processor. However, as explained, Heinrich discloses that the same techniques can be used to control transmission of data from the application processor to the baseband processor. Ex-1204, 12:52-55 ("A scheduler may implement the same scheduling techniques as those described above, but configured to schedule IPC activities from the application processor 106 to the baseband processor 104.").

delayed until it is deemed profitable to run them. The identified IPC activities are aggregated by a software framework that allows registering non-urgent requests to communicate with the remote processor, (e.g. the application processor 106). In some embodiments, the scheduler 120 *finds the best possible time to trigger* all pending non real-time sensitive IPC activities.").

Balasubramanian discloses that one such best possible time to "trigger" transmission of data from a second processing node (*e.g.*, an application processor) to a first processing node (*e.g.*, a modem/baseband processor) is upon receipt of data from the first processing at the second processing node. Ex-1205, 7:6-8 ("For example, the network interface 112 [at a second processing node] may use the *receipt* of an uplink packet as a *trigger* to transmit any downlink packets in its queue."). Balasubramanian's teaching of transmitting data from a second processing node upon receipt of data from a first processing node means that the first processing node is awake and therefore able to receive data over the bus. Lin-¶108.

This transmission from the second processing node to the first processing node upon receiving data from the first processing node occurs during a "single wake state" of the first processing node (i.e., transceiver). Ex-1205, 7:4-6 ("[D]uring the *same single wake state* the transceiver 110 also receives any downlink packets queued in the network interface 112."). In Balasubramanian, a "single wake state" refers to a period of time where the transceiver, and its associated bus, are in an active power state (such that data can be transmitted over the bus) and before the bus transitions back into a low power state. Lin-¶109.

This approach is consistent with Heinrich's goal of reducing the number of transitions between a processor (or bus) in a sleep or low power mode and an active or high power mode. *See* Ex-1204, 8:37-42 ("In this way, the non real-time sensitive IPC activities are aggregated and sent to the application processor 106 *during one awake phase* of the application processor 106. This *reduces the number of times that the application processor 106 is woken up* from its sleep mode for processing the IPC activities."); 8:50-55 ("It can therefore be seen that there is provided a setup . . . that optimizes system power consumption by scheduling non real-time sensitive IPC activities in a way that *minimizes the number of times the remote processor is woken up* from a sleep mode."). Lin-¶110.

While Heinrich describes the power conservation technique primarily for processors, Heinrich explains that the same power conservation functionality occurs in the bus connecting the baseband and application processors. In particular, Heinrich discloses that the bus over which the processors communicate can be a USB bus. Ex-1204, 4:44-48 ("There is a physical interface configured for communicating IPC activities between the baseband processor 104 and the

application processor 106. The physical interface may, for example, be . . . a Universal Serial BUS (USB) interface, . . . "); Lin-¶111.

Heinrich explains that—like the processors—the bus can transition from a sleep or low power mode to an active or high power mode. Specifically, each processor in Heinrich includes a "USB interface" that can transition from sleep to active mode to place the bus into sleep (*i.e.*, low power) or active (*i.e.*, high power) mode. Ex-1204, 3:37-40 ("For example, a Universal Serial Bus (USB) interface typically requires at least one second of idle time before switching to a USB suspend state (or "sleep mode")."); id., 11:38-40 ("For some IPC interfaces, such as a USB interface, sending logging information every second would cause the USB interface to remain in an *active mode*."). Heinrich explains that the USB interface—and, as a result, the USB bus—transitions back to a sleep mode after the application processor finishes its data transmission. Id., 13:61-62 ("Time to set IPC (USB) interface to sleep mode after last IPC packet"); see also id., 14:26-27 ("AP [application processor] inactivity timer fires; USB selective suspend state occurs [*i.e.*, sleep mode]; both AP and BB [baseband] enter low power mode"); Lin-¶112.

#### **Obviousness**

<u>Combination of Heinrich and Balasubramanian</u>: It would have been obvious for a POSA to substitute the "trigger" scheme from Balasubramanian into the processor-to-processor communication system of Heinrich in order to form the claimed combination. For example, as set forth above, Heinrich discloses the "modem processor," "downlink timer," "application processor," and "interconnectivity bus" limitations from claim 16. Balasubramanian teaches a very similar architecture as Heinrich—including a first processing node (transceiver 110), a timer (Ex-1205, 12:3-10), a second processing node (network interface 112), and a wired communication link connecting the first and second processing nodes (an "interconnectivity bus"). Moreover, Balasubramanian teaches the "trigger" scheme of claim 16, as set forth above. Accordingly, substituting the "trigger" scheme from Balasubramanian into the processor-to-processor communication system of Heinrich results in the claimed combination.

## **Motivation to Combine**

A POSA would have been motivated to combine Heinrich and Balasubramanian for at least four reasons.

*First*, Heinrich and Balasubramanian are in the same field (communications between processing nodes) and are concerned with the same issues—power consumption when transitioning from low power-to-high power states. Ex-1204, 4:6-11 ("By grouping the non real-time sensitive IPC activities together and scheduling them for communicating to the second processor during a period in which the second processor is continuously in the first [active] mode, *the number*

of times that the second processor enters and exits the second mode (e.g. sleep mode) is reduced."); Ex-1205, 5:55-61 ("Here, power may be conserved by not transitioning the transceiver 110 from the suspended state to the active state every time a packet has been generated for transmission . . . . Accordingly, power savings may be achieved by rescheduling the packet traffic into groups of traffic." (emphasis added)). Further, as set forth above, both Heinrich and Balasubramanian teach similar architectures that include two processing nodes coupled by a bus, buffering data on both sides of the bus to allow for power savings states, and the use of a timer in one or both processing nodes to determine when to send queued data to the other processing node. Therefore, it would be natural for a POSA to look to Balasubramanian when considering the power consumption issues of Heinrich. Lin-¶115.

*Second*, Heinrich and Balasubramanian both solve the power consumption problem in the same way: minimizing the number of transitions from low powerto-high power states. Thus, a POSA would have been motivated to use the techniques taught by Balasubramanian to address the same issues described in Heinrich. Lin-¶116.

*Third*, a POSA would realize that Heinrich is open to modification in that it discloses the detection of the state of the physical IPC interface in making decisions about when to transmit data. For instance, Heinrich notes that the

53

scheduling techniques described with respect to its baseband processor are also applicable to the application processor (see Ex-1204, 12:52-55), and therefore Heinrich teaches that its application processor can include a scheduler that can detect that the physical IPC interface is in an active state, and the baseband processor is awake. Id., 9:50-62, 12:47-64. Because Heinrich's application processor can have a scheduler that can detect when the physical IPC interface is in an active state, it would have been obvious to a POSA that the application processor in Heinrich could detect that the IPC interface and baseband processor are in an active state due to the reception of data from the baseband processor, upon which the application processor would transmit its data to the baseband processor over the IPC interface. Balasubramanian teaches just that—its network interface 112 detects that the transceiver 110 is in an active state upon receiving data from the transceiver 110, which triggers the network interface 112 to transmit its held data to the transceiver 110 over the communication link 116. Balasubramanian also discloses that its teachings and techniques are not limited to a particular application. Ex-1205, 7:24-28. Lin-¶117.

*Fourth*, Heinrich recognizes that it is beneficial to transmit data from one processor—*e.g.*, an application processor—to a destination processor—*e.g.*, a baseband processor—when the destination processor is already awake/active. Ex-1204, 9:14-21 ("When one of the lazy timers fires, this [wakes] up the application

processor 106. Therefore, this is a good time to schedule all the other pending, aggregated IPC activities to be sent to the application processor 106 because . . . the application processor 106 is in awake mode."); 10:32-37 ("As described above, if the scheduler 120 can determine whether the application processor 106 is in a sleep mode, IPC activities may be scheduled without waking the application processor 106 from sleep mode by scheduling the IPC activities for times when the application processor 106 is already awake."). The same principle applies to the trigger scheme of Balasubramanian, which teaches that the network interface 112 transmits packets to the transceiver 110 upon receiving packets from the transceiver 110-*i.e.*, when the transceiver 110 and communication link 116 are already awake. Therefore, consistent with the goals of Heinrich, a POSA would have been motivated to piggyback the transmission from the application processor back to the baseband processor during the same "active" mode time period and right after data is sent from the baseband processor to the application processor, reducing the number of times the processor enters and exits the active mode. See id., 4:6-11 ("By grouping the non real-time sensitive IPC activities together and scheduling them for communicating to the second processor during a period in which the second processor is continuously in the first [active] mode, the number of times that the second processor enters and exits the second mode (e.g. sleep mode) is reduced."). Such a combination would have entailed merely

incorporating a known technique (using the receipt of data from a processor as a way of determining that the other processor is awake) for a known purpose (to trigger a transmission to a processor upon receipt of data from the processor) with an expected result (fewer bus transitions between active mode and sleep mode). Lin-¶118.

<u>Reasonable Expectation of Success</u>: A POSA would have had a reasonable expectation of success in combining Balasubramanian's "trigger" scheme with the processor-to-processor communications system of Heinrich.

Heinrich discloses a system where an application processor can transmit held data to a baseband processor upon the occurrence of various triggering events. For example, Heinrich discloses a system where an application processor transmits held data to a baseband processor upon expiration of a timer. Ex-1204, 9:5-14 ("Each IPC activity is sent on the IPC interface when its respective lazy time fires. ... However, when one of the registered timers fires, all registered timers expire at the same time, causing all aggregated IPC activities to be served at the same time."). As another example, Heinrich discloses a system where an application processor transmits held data to a baseband processor when the application processor determines that the baseband processor is in an "active" or "awake" mode. *Id.*, 9:22-26 ("In general, each lazy timer is configured to fire in response to the earlier of: (i) the expiry of a respective deadline provided to the lazy timer before which it is expected to fire, or (ii) a determination that the application processor 106 is in the awake mode."). Heinrich describes various techniques for determining that the other processor is awake, including: (1) receiving a notification that the bus has been placed in an awake mode (*Id.*, 9:54-58); (2) receiving a notification via a hardware connection that the other processor is active (*id.*, 10:1-6); and (3) receiving a notification via a shared memory that the other processor is active (*id.*, 10:24-21). Thus, Heinrich discloses various techniques that trigger the transmission of data from one processor to another processor. Lin-¶120.

A POSA would expect that one could successfully use the receipt of data from one processing node to trigger a return transmission of data from another processor node, as disclosed in Balasubramanian. Viewed from the perspective of the disclosure in Heinrich, Balasubramanian's technique is simply another way for one processor to determine that the other processor and bus are awake. A POSA would therefore understand that using Balasubramanian's trigger scheme would work as expected in the processor-to-processor communications system of Heinrich. Lin-¶121. In fact, Heinrich discloses that the "scheduler"—which determines when to transmit previously stored data from one processor to another—can detect when the baseband processor is active and trigger transmission of data from the application processor (or vice versa). Ex-1204, 10:15 ("In another example, the scheduler 120 can be notified when the remote application processor 106 is active. In this way the scheduler 120 performs the determination that the application processor 106 is in the awake mode by receiving a direct notification of such."); *see also id.*, 9:43-49 ("[T]he scheduler 120 can deduce that the application processor 106 will be in the awake mode by determining that real-time sensitive IPC activities are being sent to the application processor 106, and on that basis can schedule the non real-time sensitive IPC activities to be communicated to the application processor 106 to make use of the awake mode of the application processor 106."). Heinrich discloses that this notification "can be achieved through various means." *Id.*, 10:5-6. A POSA would recognize that one such "means" is the trigger scheme described in Balasubramanian. Lin-¶121.

Thus, Heinrich in combination with Balasubramanian discloses this limitation.

#### 2. Claim 22

#### a) [22a] Preamble: "[a] mobile terminal"

The '490 patent describes the claimed "mobile terminal" as a smart phone, cell phone, tablet, or similar device. Ex-1201, 6:37-41 ("The mobile terminal 22 may be a smart phone, . . . a cellular telephone, a tablet, a laptop, or other mobile computing device.").

Heinrich teaches this limitation by disclosing a "user device" that can be "a mobile phone, a tablet, a laptop computer or other embedded device able to connect to the network 110." Ex-1204, 4:21-23; *see also id.*, Fig. 1 (showing user device 102).

# b) [22b] "a modem processor"

For the same reasons discussed above for claim [16b], Heinrich discloses the "modem processor" of claim 22. *See supra* Section IX.A.1.b); Lin-¶125.

# c) [22c] "an application timer"

For the same reasons discussed above for the "uplink timer" of claim [16d],

Heinrich discloses the "application timer" of claim 22. See supra Section

IX.A.1.d); Lin-¶126.<sup>7</sup>

## d) [22d] "an application processor,"

For the reasons discussed above for claim [16c], Heinrich discloses the "application processor" of claim 22. *See supra* Section IX.A.1.c); Lin-¶127.

e) [22e] "the application processor configured to hold application processor to modem processor data until expiration of the application timer"

For the reasons discussed above for claim [16d], Heinrich discloses the holding of "application processor to modem processor data [i.e., the "application

# <sup>7</sup> The '490 patent uses "application timer" and "uplink timer" synonymously. See

Ex-1201, 11:30-34 ("uplink timer (*i.e.*, the application timer)").

data" of claim 16] until expiration of the application timer" of claim 22. *See supra* Section IX.A.1.d); Lin-¶128.

It would have been obvious to a POSA, for the same reasons discussed above for claim [16d], that the application processor in Heinrich could hold data *i.e.*, the "application processor to modem processor data"—in its own memory on the same chip as the processor circuitry. *See supra* Section IX.A.1.d); Lin-¶129.

# f) [22f] "an interconnectivity bus communicatively coupling the application processor to the modem processor"