# UNITED STATES PATENT AND TRADEMARK OFFICE

## PATENT TRIAL AND APPEAL BOARD

UNITED MICROELECTRONICS CORP., UMC GROUP (USA), SEMICONDUCTOR MANUFACTURING INTERNATIONAL CORP., SEMICONDUCTOR MANUFACTURING INTERNATIONAL (SHANGHAI) CORP., SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP., and SMIC, AMERICAS Petitioner

v.

LONE STAR SILICON INNOVATIONS LLC Patent Owner

> CASE: IPR2017-01513 U.S. PATENT NO. 5,973,372

PETITION FOR INTER PARTES REVIEW

### **Mail Stop PATENT BOARD**

Patent Trial and Appeal Board United States Patent and Trademark Office PO Box 1450 Alexandria, Virginia 22313–1450

# **Table of Contents**

# Page

| MANDATORY NOTICES (37 C.F.R. § 42.8) vii |                           |                                                                                                                                                                                                                             |  |  |  |  |

|------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                          | A.                        | Real Parties-In-Interest vii                                                                                                                                                                                                |  |  |  |  |

|                                          | B.                        | Related Mattersviii                                                                                                                                                                                                         |  |  |  |  |

|                                          | C.                        | Lead and Backup Counsel and Serviceix                                                                                                                                                                                       |  |  |  |  |

| I.                                       | INTR                      | ODUCTION1                                                                                                                                                                                                                   |  |  |  |  |

| II.                                      | TECH                      | INOLOGICAL BACKGROUND                                                                                                                                                                                                       |  |  |  |  |

|                                          | A.                        | Overview of Technology                                                                                                                                                                                                      |  |  |  |  |

|                                          | B.                        | The Migration to Shallow Junction Transistors                                                                                                                                                                               |  |  |  |  |

|                                          | C.                        | Silicide Formation with Amorphous Silicon                                                                                                                                                                                   |  |  |  |  |

|                                          | D.                        | Epitaxial Silicon Growth                                                                                                                                                                                                    |  |  |  |  |

| III.                                     | U.S. PATENT NO. 5,973,372 |                                                                                                                                                                                                                             |  |  |  |  |

|                                          | A.                        | '372 Patent Overview                                                                                                                                                                                                        |  |  |  |  |

|                                          | B.                        | Prosecution History of the '372 Patent                                                                                                                                                                                      |  |  |  |  |

|                                          | C.                        | The Petition Relies on Previously Unapplied Prior Art12                                                                                                                                                                     |  |  |  |  |

| IV.                                      | GRO                       | UNDS FOR STANDING (37 C.F.R. § 42.104(a))13                                                                                                                                                                                 |  |  |  |  |

| V.                                       | PAYN                      | MENT OF FEES (37 C.F.R. §§ 42.15 AND 42.103)                                                                                                                                                                                |  |  |  |  |

| VI.                                      | PERS                      | RSON OF ORDINARY SKILL IN THE ART                                                                                                                                                                                           |  |  |  |  |

| VII.                                     | CLAIM CONSTRUCTION        |                                                                                                                                                                                                                             |  |  |  |  |

|                                          | A.                        | "metal silicide layer disposed adjacent the shallow junction"<br>and "epitaxial silicon layer disposed between said upper<br>silicon surface and said lower surface of metal silicide and<br>adjacent the shallow junction" |  |  |  |  |

| VIII. |    |    |      | F THE PRECISE RELIEF REQUESTED AND THE REFOR (37 C.F.R. §§ 42.22(a) AND 42.104(b)) | 22 |

|-------|----|----|------|------------------------------------------------------------------------------------|----|

|       | A. |    |      | Claims 1 and 4-6 Are Unpatentable Under 35 U.S.C.<br>Obvious over <i>Saito</i>     | 23 |

|       |    | 1. | Over | view of the Prior Art of Ground 1                                                  | 23 |

|       |    |    | a.   | Saito's FIG. 6 Technique                                                           | 24 |

|       |    |    | b.   | Saito's FIG. 1 Technique                                                           | 26 |

|       |    | 2. | Spec | ific Identification of Challenge                                                   | 29 |

|       |    |    | a.   | Claim 1                                                                            | 30 |

|       |    |    | i.   | Saito FIGS. 1(a)-1(e)                                                              | 30 |

|       |    |    | ii.  | <i>Saito</i> FIGS. 6(a)-6(e)                                                       | 35 |

|       |    |    | b.   | Claim 4                                                                            | 39 |

|       |    |    | i.   | Saito FIGS. 1(a)-1(e)                                                              | 39 |

|       |    |    | ii.  | <i>Saito</i> FIGS. 6(a)-6(e)                                                       | 39 |

|       |    |    | c.   | Claim 5                                                                            | 40 |

|       |    |    | i.   | Saito FIGS. 1(a)-1(e)                                                              | 40 |

|       |    |    | ii.  | <i>Saito</i> FIGS. 6(a)-6(e)                                                       | 41 |

|       |    |    | d.   | Claim 6                                                                            | 41 |

|       |    |    | i.   | Saito FIGS. 1(a)-1(e)                                                              | 41 |

|       |    |    | ii.  | <i>Saito</i> FIGS. 6(a)-6(e)                                                       | 41 |

|       | B. |    |      | Claims 1 and 4-5 Are Unpatentable Under 35 U.S.C.<br>Obvious over <i>Yu</i>        | 42 |

|       |    | 1. | Over | view of the Prior Art of Ground 2                                                  | 42 |

|       |    |    | a.   | Yu                                                                                 | 42 |

|       |    |    |      |                                                                                    |    |

# IPR2017-01513 U.S. Patent No. 5,973,372

|    | 2. | Spec  | rific Identification of Challenge                                                               | 44 |

|----|----|-------|-------------------------------------------------------------------------------------------------|----|

|    |    | a.    | Claim 1                                                                                         | 44 |

|    |    | b.    | Claim 4                                                                                         | 47 |

|    |    | C.    | Claim 5                                                                                         | 48 |

| C. |    |       | Claims 1 and 4-6 Are Unpatentable Under 35 U.S.C.<br>Obvious over <i>Chau</i> and <i>Rodder</i> | 48 |

|    | 1. | Over  | rview of the Prior Art of Ground 3                                                              | 49 |

|    |    | a.    | Chau                                                                                            | 49 |

|    |    | b.    | Rodder                                                                                          | 50 |

|    | 2. | Mot   | ivation to Combine                                                                              | 51 |

|    | 3. | Spec  | ific Identification of Challenge                                                                | 52 |

|    |    | a.    | Claim 1                                                                                         | 52 |

|    |    | b.    | Claim 4                                                                                         | 55 |

|    |    | C.    | Claim 5                                                                                         | 56 |

|    |    | d.    | Claim 6                                                                                         | 56 |

| D. |    |       | Claims 1 and 4-6 Are Unpatentable Under 35 U.S.C.<br>Obvious over <i>Rodder</i>                 | 57 |

|    | 1. | Over  | rview of the Prior Art of Ground 4                                                              | 57 |

|    |    | a.    | Rodder                                                                                          | 57 |

|    | 2. | First | Specific Identification of Challenge                                                            | 57 |

|    |    | a.    | Claim 1                                                                                         | 57 |

|    |    | b.    | Claim 4                                                                                         | 60 |

|    |    | C.    | Claim 5                                                                                         | 60 |

# IPR2017-01513 U.S. Patent No. 5,973,372

|      |      | d.    | Claim 6                                                                                       | 61 |

|------|------|-------|-----------------------------------------------------------------------------------------------|----|

| E.   |      |       | Claims 1 and 4-6 Are Unpatentable Under 35 U.S.C.<br>Obvious over <i>Ogasawara</i>            | 61 |

|      | 1.   | Over  | view of the Prior Art of Ground 5                                                             | 61 |

|      |      | a.    | Ogasawara                                                                                     | 61 |

|      | 2.   | First | Specific Identification of Challenge                                                          | 62 |

|      |      | a.    | Claim 1                                                                                       | 62 |

|      |      | b.    | Claim 4                                                                                       | 65 |

|      |      | C.    | Claim 5                                                                                       | 65 |

|      |      | d.    | Claim 6                                                                                       | 66 |

| F.   |      |       | Claim 6 is Unpatentable Under 35 U.S.C. § 103(a) as ver <i>Yu</i> in view of <i>Ogasawara</i> | 66 |

|      | 1.   | Moti  | vation to Combine                                                                             | 66 |

|      | 2.   | Spec  | ific Identification of Challenge                                                              | 67 |

|      |      | a.    | Claim 6                                                                                       | 67 |

| SECO | ONDA | RY C  | ONSIDERATIONS                                                                                 | 68 |

| CON  | CLUS | ION   |                                                                                               | 68 |

IX.

X.

#### **List of Exhibits**

- Ex. 1001: U.S. Patent No. 5,973,372 ("372 Patent").

- Ex. 1002: Declaration of R. Jacob Baker, Ph.D., P.E.

- Ex. 1003: *Curriculum vitae* of R. Jacob Baker, Ph.D., P.E.

- Ex. 1004: Prosecution History of U.S. Patent No. 5,973,372.

- Ex. 1005: English-Language Translation of Japanese Patent Publication

No. JP08-204187, Japanese-Language Version of Japanese Patent

Publication No. JP08-204187, and Translation Certification ("Saito").

- Ex. 1006: PCT Application No. WO 96/20499 ("Chau").

- Ex. 1007: U.S. Patent No. 5,409,853 to Yu ("Yu").

- Ex. 1008: U.S. Patent No. 4,998,150 to Rodder et al. ("*Rodder*").

- Ex. 1009: English-Language Translation of Japanese Patent Publication No. JP08-018049, Japanese-Language Version of Japanese Patent

Publication No. JP08-018049, and Translation Certificate

("Ogasawara").

- Ex. 1010: R. Jacob Baker, Harry W. Li and David. E. Boyce, CMOS Circuit Design, Layout, and Simulation (IEEE Press, 1997).

- Ex. 1011: Robert H. Dennard, Fritz H. Gaensslen, Hwa-Nien Yu, V. Leo

Rideout, Ernest Bassous, and Andre R. LeBlanc, *Design of Ion- Implanted MOSFETs with Very Small Physical Dimensions*, IEEE

V

Journal of Solid-State Circuits, Oct. 1974, at 256.

- Ex. 1012: R. W. Mann, L. A. Clevenger, P. D. Angello, and F. R. White, *Silicides and Local Interconnections for High-Performance VLSI Applications*, IBM Journal of Research Development, Vol. 39, July 1995, at 403.

- Ex. 1013: S. Wolf and R.N. Tauber, *Silicon Processing for the VLSI Era* (Lattice Press, 1986)<sup>1</sup>.

- Ex. 1014: Lone Star Silicon Innovation LLC's Preliminary Claim ConstructionsPursuant To P.R. 4-2(a) from Case No. 2:16-cv-01170-JRG-RSP(LEAD CASE).

<sup>&</sup>lt;sup>1</sup> Throughout this petition, citations to this exhibit will refer to the original textbook page number.

# MANDATORY NOTICES (37 C.F.R. § 42.8)

# A. Real Parties-In-Interest

The following entities are the real parties in interest:

- United Microelectronics Corporation, located at No. 3 Li-Hsin Road II, Hsinchu Science Park, Hsinchu City, Taiwan, Republic of China;

- UMC Group (USA), located at 488 De Guigne Drive, Sunnyvale, CA 94085-3903;

- Semiconductor Manufacturing International Corporation, located at 18 Zhangjiang Road, Pudong New Area, Shanghai, 201203, People's Republic of China;

- Semiconductor Manufacturing International (Shanghai) Corporation, located at 18 Zhangjiang Road, Pudong New Area, Shanghai, 201203, People's Republic of China;

- Semiconductor Manufacturing International (Beijing) Corporation, located at 18 Wenchang Avenue, Economic-Technological Development Area, Beijing 100176, People's Republic of China; and

- SMIC, Americas 1732 N. 1st Street, Suite 200, San Jose, California 95112.

## **B.** Related Matters

Patent Owner Lone Star Silicon Innovations LLC ("PO" or "Lone Star") is presently asserting U.S. Patent No. 5,973,372 ("'372 Patent") against United Microelectronics Corporation and UMC Group (USA) in the Eastern District of Texas in Case No. 2:16-cv-01216-JRG-RSP. PO is also presently asserting the <sup>•</sup>372 Semiconductor Manufacturing International Patent against Corp., Semiconductor Manufacturing (Shanghai) Corp., Int'l. Semiconductor Manufacturing Int'l. (Beijing) Corp., and SMIC, Americas in the Eastern District of Texas in Case No. 2:16-cv-01276-JGR-RSP.

| Lead Counsel                     | Backup Counsel                     |

|----------------------------------|------------------------------------|

| Benjamin E. Weed                 | Jay C. Chiu                        |

| Reg. No. 65,939                  | Reg. No. 47,308                    |

| K&L Gates LLP                    | K&L Gates LLP                      |

| 70 W. Madison Street, Suite 3100 | 1 Park Plaza, Twelfth Floor,       |

| Chicago, IL 60602                | Irvine, CA 92614                   |

| benjamin.weed.PTAB@klgates.com   | jay.chiu@klgates.com               |

| T: (312) 781-7166                | T: (949) 253-0900                  |

| F: (312) 827-8152                | F: (949) 253-0902                  |

|                                  |                                    |

|                                  | Tina Thomas                        |

|                                  | Reg. No. 75,089                    |

|                                  | K&L Gates LLP                      |

|                                  | 70 W. Madison Street, Suite 3100   |

|                                  | Chicago, IL 60602                  |

|                                  | tina.thomas@klgates.com            |

|                                  | T: (312) 807-4283                  |

|                                  | F: (312) 827-2497                  |

|                                  | Jeffrey L. Johnson                 |

|                                  | Reg. No. 53,078                    |

|                                  | Orrick, Herrington & Sutcliffe LLP |

|                                  | 1301 McKinney Street, Suite 4100   |

|                                  | Houston, TX 77010-3096             |

|                                  | 3j6ptabdocket@orrick.com           |

|                                  | T: (713) 658-6450                  |

|                                  | F: (713) 658-6401                  |

# C. Lead and Backup Counsel and Service

Petitioner consents to electronic service by email.

### I. INTRODUCTION

United Microelectronics Corporation, UMC Group (USA), Semiconductor Manufacturing International Corporation, Semiconductor Manufacturing International (Shanghai) Corporation, Semiconductor Manufacturing International (Beijing) Corporation, and SMIC, Americas (collectively, "Petitioner") request *Inter Partes* Review ("IPR") of claims 1 and 4-6 of U.S. Patent No. 5,973,372 ("372 Patent") (Ex. 1001) under 35 U.S.C. §§ 311–319.

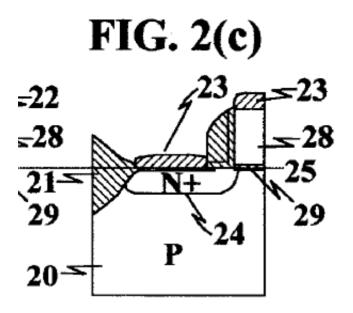

The '372 Patent describes a method of forming "a metal silicide at a shallow junction in a single crystal substrate without encroaching on the shallow junction." (Ex. 1001, Abstract). As part of this process, the '372 Patent requires a titanium silicide layer to be formed by thermally annealing amorphous silicon deposited over a titanium film. (Ex. 1001, Abstract). The '372 Patent, however, acknowledges that during this anneal, "titanium silicide 23 is formed by reacting the titanium 22 with the amorphous silicon 26 *and slightly with the silicon substrate* ....." (Ex. 1001, 4:38-41; emphasis added). To ensure that the silicide remains above the original surface of the silicon substrate, the '372 Patent discloses that after the first anneal to form titanium silicide, an epitaxial layer is formed *between* the silicide and the underlying substrate:

[w]ith a thick amorphous silicon layer 26, which is sufficiently thick so as to not be totally consumed by the silicidation, silicon atoms from the amorphous silicon layer migrate through the titanium silicide 23 and to the single crystal silicon substrate and, in accordance with the device structure of the present invention, form a solid phase epitaxy layer as shown in the vicinity of the silicide and the N+ boundary in FIG. 2(c).

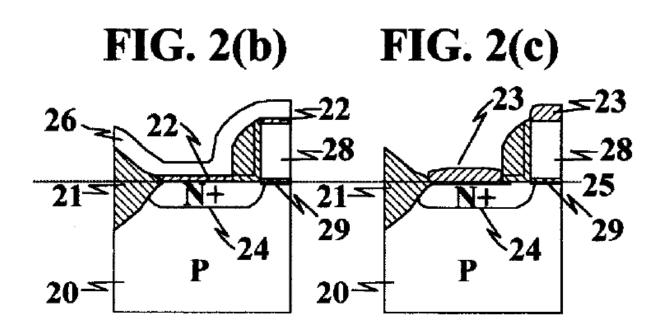

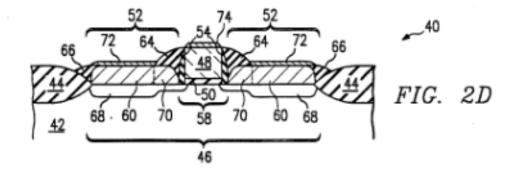

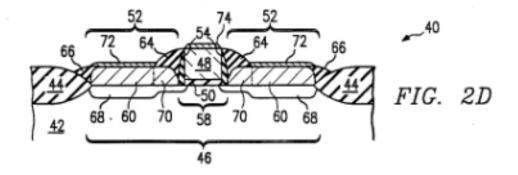

(Ex. 1001, 4:62-5:3; Ex. 1002, ¶¶34-36). FIGS. 2(b) and 2(c) of the '372 Patent illustrate this result (albeit without a clear illustration of the "solid phase epitaxy layer") and are reproduced below:

(Ex. 1001, FIGS. 2(b) and 2(c); Ex. 1002, ¶¶34-36).

Notwithstanding the fact that the '372 Patent focuses on an allegedly novel *manufacturing method*, the challenged claims of the '372 Patent are apparatus claims directed to an "integrated circuit" having a shallow junction for each of a source and drain, a metal silicide layer, and an epitaxial silicon layer between the

shallow junctions and the metal silicide layer. (Ex. 1001, 7:41-8:9). As explained herein, the *structure* of the integrated circuit is far from novel—several references unconsidered during examination disclose the recited structure. Moreover, even if certain manufacturing steps are interpreted as part of the claims (as should be the case here under the applicable district court claim construction standard), the prior art (including a Japanese patent publication referred to herein as *Saito*, Ex. 1005) plainly discloses achieving the known apparatus using the same process disclosed in the '372 Patent. Either way, the claims of the '372 Patent are invalid.

#### II. TECHNOLOGICAL BACKGROUND

#### A. Overview of Technology

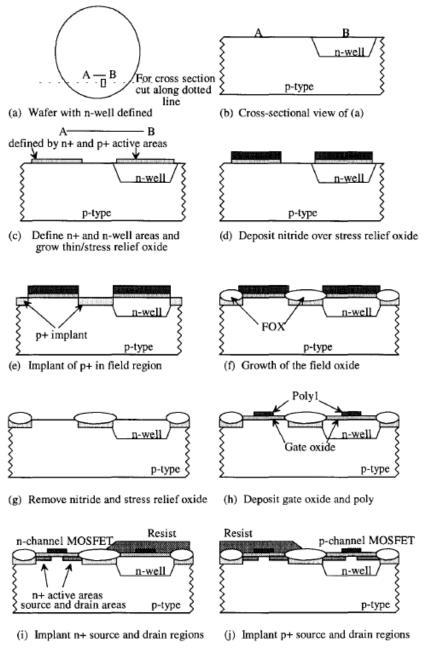

The '372 Patent relates to integrated circuit fabrication and, in particular, to reducing the resistance associated with terminals of integrated transistors. (Ex. 1002, ¶19; Ex. 1001, 1:12-19). Understanding the basic technology flow for CMOS transistor formation is therefore useful; the diagram below, from a prior art textbook titled *CMOS Circuit Design, Layout, and Simulation* (Ex. 1010), summarizes this flow:

Figure 4.10 Sequence of events used in MOSFET formation.

(Ex. 1010, Figure 4.10; Ex. 1002, ¶¶20-21). An n-channel MOSFET ("NMOS") is depicted in the left of each figure and a p-channel MOSFET ("PMOS") is depicted on the right of each figure. (*Id.*). As Figure 4.10(c) suggests, the fabrication process begins when an n+ and n- well area is formed and a thin stress relief oxide

is grown on top of the active areas of the p-substrate and n-well. (*Id.*). Next, nitride is deposited on top of the stress relief oxide and areas not covered by the nitride are implanted using a p-field implant. (*Id.*). Not shown in Figure 4.10 are the steps involved in forming an n-field implant. (Ex. 1002,  $\P$ 22). After the field implants are in place, field oxide is grown and the nitride and stress relief oxides are removed. (Ex. 1010, Figure 4.10). Next, gate oxide and polysilicon are deposited and a resist is also deposited over the n-well region in order to mask the n-well region. (*Id.*). The n+ region is then implanted with dopants. (*Id.*). Next, the resist is removed from the n-well region, and the n+ region is covered with the resist in order to mask the n+ region. The wafer is again implanted with dopants. (*Id.*).

Typically, the sheet resistances for polysilicon are on the order of 20  $\Omega$ /square. (Ex. 1002, ¶23). In order to lower the sheet resistance of the polysilicon, a refractory metal and polysilicon mixture called silicide is deposited on top of the polysilicon. (*Id.*). This silicide/polysilicon sandwich is referred to as a polycide gate. The typical sheet resistances of polycide gates are 2-3  $\Omega$ /square. (*Id.*).

# **B.** The Migration to Shallow Junction Transistors

The concept of scaling down the size of transistors is generally understood to have been first introduced in 1974. (*See* Ex. 1011, Fig. 1; Ex. 1002, ¶24). The

5

problems associated with this scaling, including an increase in sheet resistance due to a shorter channel length, also became known at this time. (Ex. 1002,  $\P$ [24-25). The higher resistance of these junctions caused an increase in the resistance in series with the MOSFET. (*Id.*). When the MOSFET was used as a switch, the increase in resistances lead to slower circuits. (*Id.*). This was highly undesirable. (*Id.*).

In order to improve issues caused by the higher sheet resistance of the source and drain, a refractory metal and polysilicon mixture could be deposited on top of the polysilicon, as well as on the source/drain regions. (Ex. 1002,  $\P$ 26). The substrate is then annealed, resulting in the formation of titanium silicide (TiSi<sub>2</sub>). (*Id.*). This layer is frequently referred to as a self-aligned silicide or simply as a *salicide*. (*Id.*).

#### C. Silicide Formation with Amorphous Silicon

When a silicide is formed as described above, the titanium consumes the underlying silicon as part of the reaction that leads to silicide formation; in this process, after formation, the silicide generally sits below the top edge/surface of the silicon wafer due to the consumption of a portion of the silicon wafer to form the silicide. (Ex. 1002, ¶27). As MOSFETs scale to smaller dimensions, this consumption of the thinner and thinner substrate becomes undesirable. (*Id.*). One

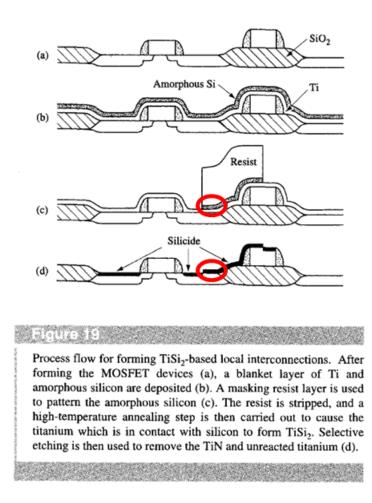

solution to this problem is detailed in the below figure, which is taken from a survey paper published by IBM in July 1995:

(Ex. 1012, 412; emphasis added).

After MOSFET formation, as shown above in Figure 19 of Ex. 1012, a layer of titanium is deposited over the devices, followed by a layer of amorphous silicon. (*Id.*). Next, a resist layer is used to mask portions of the amorphous silicon, patterning the amorphous silicon as in Figure 19(c). (*Id.*). Next, the resist is

removed and the substrate is annealed to form TiSi<sub>2</sub> (silicide). (*Id.*). Figure 19(d) demonstrates what those of skill in the art generally understand: that the titanium forms a silicide with the amorphous silicon layered above more quickly than the crystalline silicon below. (Ex. 1012, 412; Ex. 1002; ¶28). In the resulting structure, the titanium silicide does not extend as deeply into the source/drain region, as much less of the silicon substrate is consumed in formation of the titanium silicide. (*Id.*). Thus, shallower junctions can be formed when upper amorphous silicon is used to form the silicide layer. (Ex. 1002, ¶27). This technique was well known in the art at least as early as 1995 (two years before the filing of the '372 Patent). (Ex. 1002, ¶28).

#### **D.** Epitaxial Silicon Growth

In semiconductor processing, epitaxial growth of silicon refers to a process for growing silicon on another silicon material. (Ex. 1002,  $\P$ 29). In this process, the grown silicon has the same crystalline orientation as the underlying silicon. (*Id.*). In other words, if a single crystalline epitaxial layer is grown, that means the underlying substrate is also single crystalline silicon.

Those of skill in the art understand that, given the ubiquity of epitaxial silicon formation in semiconductor fabrication, drawings of fabrication processes often do not illustrate the formation of epitaxial layers. (Ex. 1002, ¶¶29-30). That is, while epitaxial layers are often necessarily formed, it is very common for those

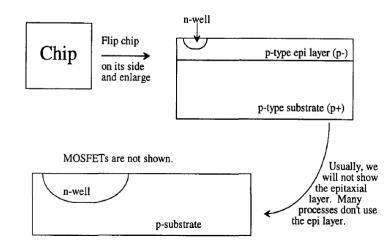

layers not to be illustrated in drawings of semiconductor fabrication processes. (*Id.*). As illustrated below, the use of the epitaxial layer does not affect the overall function of the device, but instead it simply allows a higher impurity p-type substrate to be used. (Ex. 1010, Figure 2.1; Ex. 1002,  $\P$ 30).

Figure 2.1 Illustration of the top and side view of a die.

#### (Ex. 1010, Figure 2.1; Ex. 1002, ¶30).

Those of skill in the art, therefore, are generally not surprised to read about epitaxial layer formation without seeing an illustration of such a layer in images summarizing semiconductor fabrication processes. (Ex. 1002, ¶¶29-30).

### **III. U.S. PATENT NO. 5,973,372**

#### A. '372 Patent Overview

The '372 Patent, which was filed on December 6, 1997, discusses how to fabricate an integrated circuit that has a metal silicide layer formed on top of a shallow junction. (Ex. 1001, 1:64-67; Ex. 1002, ¶31). It purports to solve

problems associated with shrinking dimensions: as "the shallow junction becomes ever more shallow and the result is degrading of the integrity of the shallow junction." (Ex. 1001, 4:16-18; Ex. 1002, ¶32).

To address these problems, the '372 Patent discloses that, after junctions are formed, deposition of a refractory metal, such as titanium, is performed on the surface of the substrate. (Ex. 1001, 5:50-58; Ex. 1002, ¶32). Next, a layer of silicon-containing material, preferably amorphous silicon, is deposited on top of the titanium layer. (Ex. 1001, 5:58-65; Ex. 1002, ¶32). The substrate is then annealed at a temperature of about 650C, which initiates a silicidation process, creating a layer of titanium silicide. (Ex. 1001, 6:19-26; Ex. 1002, ¶32). The amorphous silicon is of a thickness so that the majority of the refractory metal reacts with the amorphous silicon and only a small amount of the silicon substrate is consumed during the silicide reaction. (*Id.*).

The '372 Patent states that the titanium silicide will reach the correct phase, phase C54, only after two annealing processes have been conducted. (Ex. 1001, 6:26-33; Ex. 1002, ¶33). Further, in one embodiment of the '372 Patent (illustrated in FIGS. 2(b) and 2(c)), silicon atoms from the remaining amorphous silicon (following completion of the TiSi<sub>2</sub> formation process) migrate through the newly created titanium silicide to the single crystal silicon substrate and form a solid phase epitaxy layer in the vicinity of the N+ boundary. (Ex. 1001, 4:62-5:3; Ex. 1002, ¶33).

#### **B.** Prosecution History of the '372 Patent

The application that issued as the '372 Patent was filed on December 6, 1997. (Ex. 1004, 3). Petitioner is unaware of any patent term adjustments or extensions that apply to the term of the '372 Patent, so Petitioner believes that the '372 Patent will expire on December 6, 2017, during the pendency of this proceeding.

The Examiner issued a non-final office action on July 29, 1998, rejecting the pending claims under 35 U.S.C. §§ 112 and 102(b). (Ex. 1004, 70-72). The prior art rejection under 35 U.S.C. § 102(b) relied on U.S. Patent No. 5,225,896 to Van Roozendaal et al. (*Id.*). In response to this rejection, Applicant attempted to distinguish the pending claims from the prior art by arguing that the prior art disclosed an epitaxial layer that was part of the starting substrate, not one formed from amorphous silicon. (Ex. 1004, 84). Further, Applicant argued that its claims were distinguishable because in the prior art all of the amorphous silicon was consumed during the formation of titanium silicide; therefore, no amorphous silicon remained to create the epitaxial layer. (*Id.*).

In response, the Examiner allowed pending claim 5, and rejected the remaining claims under newly cited U.S. Patent No. 5,416,034 to Bryant.

(Ex. 1004, 86). The Applicant conducted an Examiner interview and thereafter further amended the claims and argued for patentability. (Ex. 1004, 89-97). Specifically, Applicant argued that:

[T]he Bryant reference was discussed and the Examiner stated that if Claim 1 recited that the metal silicide and epitaxial layer structure were adjacent the shallow junctions of both a source and drain of an [sic] field effect transistor, this would patentable distinguish [the pending claims] over the Bryant reference. Further, if original Claim 5 to a bipolar transistor was written in independent form, the Examiner stated that such a claim would be patentable distinct from the Bryant reference.

(Ex. 1004, 95). The Applicant also characterized the pending claims as requiring a thin epitaxial silicon layer to provide a non-resistive path to the metal silicide for both the source and drain of the same field effect transistor and the emitter of a bipolar transistor. (Ex. 1004, 96).

Apparently agreeing with Applicant's arguments and claim amendments, the Examiner allowed the claims on May 20, 1999, and the '372 Patent issued on October 26, 1999. (Ex. 1004, 99-101).

## C. The Petition Relies on Previously Unapplied Prior Art

None of the references supporting the proposed Grounds in this Petition were previously considered by the Patent Office during examination of the '372 Patent. Additionally, this Petition relies on a declaration of R. Jacob Baker, Ph.D., P.E., an expert in the field of the '372 Patent and the prior art, which was also not considered during examination. (*See* Ex. 1002). The Board should institute IPR in light of 35 U.S.C. § 325(d).

### IV. GROUNDS FOR STANDING (37 C.F.R. § 42.104(a))

Petitioner certifies that (1) the '372 Patent is available for IPR; (2) Petitioner is not barred or estopped from requesting an IPR on the Grounds identified herein; and (3) Petitioner has not filed a complaint relating to the '372 Patent.

### V. PAYMENT OF FEES (37 C.F.R. §§ 42.15 AND 42.103)

Petitioner authorizes the USPTO to charge any required fees to Deposit Account 02–1818.

#### VI. PERSON OF ORDINARY SKILL IN THE ART

A person of ordinary skill in the art (referred to herein as a "POSA") is a hypothetical person who is presumed to know the relevant prior art. (*See Gnosis S.P.A et al. v. S. Ala. Med. Sci. Foundation*, Case IPR2013-00116, Paper 68 at 9, 37 (PTAB June 20, 2014)). A POSA has ordinary creativity, is not an automaton, and is capable of combining teachings of the prior art. (*Id.* (citing *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 420-421 (2007))).

With respect to the '372 Patent, a POSA as of December 6, 1997, would have had a bachelor's or master's degree in electrical engineering, materials science, or a closely related field and two to three years of academic or industry experience in the field of semiconductor processing. (Ex. 1002,  $\P\P17-18$ ). A person with less education, but more relevant industry experience, or a person with more education, but less relevant industry experience, may also meet this standard. (Ex. 1002,  $\P\P17-18$ ).

#### VII. CLAIM CONSTRUCTION

In accordance with 37 C.F.R. § 42.100(b), the challenged claims of the '372 Patent must be given their "broadest reasonable construction in light of the specification" of the '372 Patent. (37 C.F.R. § 42.100(b); *Cuozzo Speed Techs.*, *LLC v. Lee*, No. 15-446, slip op. at 20 (U.S. June 20, 2016)).

Under this standard, claim terms are generally given their ordinary and customary meaning, as would be understood by a POSA in the context of the entire disclosure. (*In re Translogic Tech., Inc.,* 504 F.3d 1249, 1257 (Fed. Cir. 2007)). If a special definition for a claim term is proffered, it must be described in the specification "with reasonable clarity, deliberateness, and precision." (*In re Paulsen,* 30 F.3d 1475, 1480 (Fed. Cir. 1994)).

In the event PO files a motion, as it is permitted to do, certifying that the '372 Patent will expire prior to the conclusion of this proceeding, the district court claim construction standard, such as articulated in *Phillips v. AWS Corp.*, applies. 415 F.3d 1303 (Fed. Cir. 2005). Indeed, Petitioner believes that the '372 Patent *will* expire during this proceeding, as Petitioner believes the '372 Patent will expire

on December 6, 2017. Thus, Petitioner believes that the *Phillips* district-court-type claim construction standard should apply here.

Regardless of the claim construction standard applied, Petitioner believes that the constructions described below should be adopted.<sup>2</sup> In particular, the proposed constructions constitute the *only* reasonable way a person of skill in the art would read the claims of the '372 Patent and these constructions are thus mandated by the intrinsic record.

<sup>2</sup> Lone Star served its Preliminary Claim Constructions in a consolidated case involving the '372 Patent, on June 7, 2017. (Ex. 1014, 3-4). Petitioner asserts that for purposes of this Petition, no terms, other than those proposed herein, need construction. Further, although Lone Star proposes that the term "adjacent" requires no construction, Petitioner submits that, for the reasons articulated herein, the term adjacent does require construction. Petitioner also submits that Lone Star may still present the construction of "adjacent" described herein as a potential PO construction in this proceeding despite not proposing that construction in the district court litigation. Nonetheless, under the constructions proposed by Lone Star, the prior art presented in this petition still applies to the claim terms as construe by Lone Star, and renders obvious the claims of the '372 Patent. Other than the terms specifically addressed below, Petitioner submits that a POSA would have understood each term of each of the challenged claims of the '372 Patent to have its ordinary and customary meaning.

# A. "metal silicide layer ... disposed adjacent the shallow junction" and "epitaxial silicon layer ... disposed between said upper silicon surface and said lower surface of metal silicide and adjacent the shallow junction ..."

Challenged claim 1 of the '372 Patent requires "a metal silicide layer having a lower surface *disposed adjacent* the shallow junction of each of the source and drain in the silicon substrate and above the upper surface of the silicon substrate" and "an epitaxial silicon layer *disposed* between the upper silicon surface and said lower surface of metal silicide and *adjacent* the shallow junction of the source and drain ... ." (Ex. 1001, 7:51-8:6; emphasis added). In the context of claim 1, the upper surface of the silicon substrate and the upper surface of the shallow junction are the same surface. (Ex. 1002, ¶40).

Because the claim requires two layers to be both "disposed adjacent" the same surface (i.e., the upper surface of the silicon substrate/shallow junction), Petitioner submits that the claim language requires interpretation to resolve the apparent ambiguity and to ascertain the actual scope of the claims. Indeed, the plain language—requiring two layers to be both adjacent the same layer—is nonsensical. Since the claim is written as an apparatus claim, two layers cannot both be adjacent to the shallow junction layer as the claims appear to suggest.<sup>3</sup> Further, the term "adjacent" is unclear. Unless the term "adjacent" is meant to mean "directly adjacent" or "in physical contact with" during the formation of each layer, the term would have an unascertainable scope to a POSA. (Ex. 1002, ¶41).

Claim 1 as originally presented in the application that issued as the '372 Patent did not require any adjacency. (Ex. 1004, 42). While it did recite a shallow junction, a metal silicide layer, and an epitaxial silicon layer, the claims as originally filed explained the relationship as follows:

[A]n epitaxial silicon layer between said upper silicon surface and said lower surface of metal silicide whereby the metal silicide extends only slightly below the upper silicon surface and does not encroach upon the shallow junction.

(Ex. 1004, 42). This is fully consistent with the description in the '372 Patent specification regarding FIG. 2(c), wherein titanium is first layered on top of a shallow junction. (Ex. 1001, 4:33-35). Thereafter, a layer of "silicon containing material 26, such as amorphous...silicon," is formed. (Ex. 1001, 4:35-38). During

<sup>&</sup>lt;sup>3</sup> Petitioner reserves the right to argue in the co-pending district court case, that the claims are invalid under 35 U.S.C. § 112 as indefinite in the event the Board (or the district court) finds that the requirement for two different layers to be adjacent to the shallow junction is not amenable to construction.

the subsequent formation of silicide, the '372 Patent discloses that some of the underlying silicon substrate is consumed, albeit at a slower rate than the amorphous silicon is consumed. (Ex. 1001, 4:38-41). This is consistent with the understanding of a POSA. (Ex. 1002, ¶35). This process mirrors the originally filed claims (Ex. 1004, 42) in the sense that the metal silicide extends "slightly below" the upper silicon surface.

During prosecution, the Examiner objected to the drawings as not showing this "slightly below" limitation and rejected the claims under 35 U.S.C. § 112 for indefiniteness. (Ex. 1004, 70-71). In response, PO (then Applicant) amended the claims to specify that the metal silicide layer is disposed adjacent the silicon substrate, but did not initially amend the claims to require the epitaxial silicon layer to also be adjacent the shallow junction. (Ex. 1004, 78). Applicant then argued that FIG. 2(c) (which is described in the specification as noted above) shows the structure recited in the claims. (Ex. 1004, 79). It argued that:

[O]ne skilled in the art is taught the ratio of silicon and metal, such as titanium to form metal silicide, such as titanium silicide ... it is the silicon that is the moving element and ... if the amorphous silicon is thick enough based on the ratio of silicon to metal, the silicon from the amorphous silicon will be in sufficient supply to not only consume essentially all of the metal in forming the metal silicide but will

migrate to the single crystal silicon and form a solid epitaxy layer *below the metal silicide*.

(Ex. 1004, 80-81; emphasis added). Applicant reiterated that "the metal silicide only can extent [sic - extend] slightly below the original single crystal silicon surface ....," (Ex. 1004, 81). Finally, the PO (then Applicant) argued that the prior art used to reject the claims was insufficient because "no amorphous silicon remains to form an epitaxial layer with the single crystal silicon substrate." (Ex. 1004, 82). In other words, the Applicant argued that the claims were patentable because the process used to manufacture the claimed apparatus was not disclosed in the prior art of record.

Later in prosecution, the Applicant further amended the claims to specify the dual-adjacency now required. (Ex. 1004, 93-94). It clarified in the remarks that the amendments were made to clarify that "the metal silicide and epitaxial layer structure were adjacent the shallow junctions of *both a source and drain*...." (Ex. 1004, 95; emphasis added). Applicant's remarks never addressed the nonsensical nature of the claims.

The claims were thereafter allowed. (Ex. 1004, 98-99).

In both drafting the application and in prosecuting the claims that led to the '372 Patent, PO consistently argued that the claimed structure (and process to make the claimed structure) was the structure described and illustrated in FIG. 2(c). Nonetheless, Petitioner submits that the claim language that was actually created by amendment (Ex. 1004, 93-94) is nonsensical by virtue of two different structures layered on top of each other both being adjacent to an underlying structure. (Ex. 1002, ¶41). Thus, for purposes of this proceeding, Petitioner submits that the only reasonable construction of this term must reflect the structure formed by the process described in connection with FIG. 2(c). (Ex. 1002, ¶44).

Petitioner proposes that the term "disposed" should be construed as "formed," such that the environmental structure existing at the time of the "formation" would be positionally relevant to the construction. This means that when the metal silicide layer is created it is disposed, or formed, adjacent to the shallow junction. Subsequent processing steps demonstrate that the metal silicide layer is not required to remain in its as-formed position indefinitely. In particular, future formation of the epitaxial layer can occur "between said upper silicon surface and said lower surface of metal silicide" and, at the time of formation, be adjacent "the shallow junction..." (Ex. 1001, Claim 1, 4:61-5:6). Therefore, the only logical interpretation of this claim is depicted in FIG. 2(c); the final structure formed after the completion of processing. (*See* Ex. 1002, ¶44).

Petitioner therefore submits that the only reasonable construction of the "disposed adjacent" terms of claim 1 is "formed adjacent" such that something is

formed at one point in the process that does not need to remain in the same relative position throughout the fabrication process. (Ex. 1002,  $\P$ 42-45). This construction properly reflects the claimed embodiment of FIG. 2(c).

(Ex. 1001, FIG. 2(c); Ex. 1002, ¶¶34-36, 42-45). Therefore, the claims of the '372 Patent *require* the formation of the silicide layer *before* the formation of an epitaxial layer; otherwise, the "disposed adjacent" relationship required in the claims is never met. (Ex. 1002, ¶¶42-45). Grounds 1, 2, and 6 below explain why the challenged claims of the '372 Patent are obvious under this construction.

It appears that PO may argue for a different construction unsupported by the '372 Patent specification in which the metal silicide layer can be adjacent to a layer of epitaxial silicon *previously formed* on the upper surface of the shallow junction. Though this construction is not supported by the '372 Patent specification and does not meet the adjacency required by the claims of the '372 Patent, it is the only construction under which the silicide does not consume a portion of the shallow junction during formation (i.e., because the metal is layered on the epitaxial silicon and the silicide is thereafter formed). While Petitioner does not believe this construction is supported by the '372 Patent specification, Grounds 1, 3, 4, and 5 below address this proposed construction.

## VIII. STATEMENT OF THE PRECISE RELIEF REQUESTED AND THE REASONS THEREFOR (37 C.F.R. §§ 42.22(a) AND 42.104(b))

Petitioner requests the institution of IPR and cancellation of claims 1 and 4-6 of the '372 Patent based on the Grounds listed below.

| Ground | Statutory Basis | <b>Relied-On References</b>                                   | Claims    |

|--------|-----------------|---------------------------------------------------------------|-----------|

| 1      | 35 U.S.C. § 103 | Saito (Ex. 1005)                                              | 1 and 4-6 |

| 2      | 35 U.S.C. § 103 | <i>Yu</i> (Ex. 1007)                                          | 1 and 4-5 |

| 3      | 35 U.S.C. § 103 | <i>Chau</i> (Ex. 1006) in view of<br><i>Rodder</i> Ex. (1008) | 1 and 4-6 |

| 4      | 35 U.S.C. § 103 | <i>Rodder</i> (Ex. 1008)                                      | 1 and 4-6 |

| 5      | 35 U.S.C. § 103 | Ogasawara (Ex. 1009)                                          | 1 and 4-6 |

| 6      | 35 U.S.C. § 103 | <i>Yu</i> (Ex. 1007) in view of <i>Ogasawara</i> (Ex. 1009)   | 6         |

Grounds 1, 2, and 6 address claims 1 and 4-6 under Petitioner's proposed constructions. Should the Board be inclined to institute either Ground 1 or Ground 2 (and Ground 6, which addresses claim 6 based on the same primary reference as Ground 2), Petitioner submits that Ground 1 should be instituted, as it also addresses the claims under the construction Patent Owner may advocate.

Grounds 3, 4, and 5 address a construction Petitioner submits should not be adopted, but may be advocated by Patent Owner.

Per 37 C.F.R. § 42.6(c), copies of the references are filed herewith. Additionally, Petitioner provides the declaration of R. Jacob Baker, Ph.D., P.E. in support of these Grounds.<sup>4</sup>

## A. Ground 1: Claims 1 and 4-6 Are Unpatentable Under 35 U.S.C. § 103(a) as Obvious over *Saito*

As supported by Dr. Baker's declaration, claims 1 and 4-6 of the '372 Patent are obvious in view of *Saito*.

#### **1.** Overview of the Prior Art of Ground 1

Japanese Patent Application No. JP08-204187 ("*Saito*") was published on August 9, 1996. (Ex. 1005 (foreign-language version and English-language translation, followed by declaration from translator)). *Saito* is prior art under 35 U.S.C. § 102(b). *Saito* describes a prior art technique (with regard to FIG. 6)

<sup>4</sup> Dr. Baker has a BS degree, an MS degree, and a Ph.D. in Electrical Engineering, and is a licensed Professional Engineer in the state of Idaho. He has more than 30 years of experience in circuit design and manufacture and has authored several books and other publications related to solid-state circuit design and packaging. Accordingly, Dr. Baker is an expert in the field of the '372 Patent and the prior art. (Ex. 1003).

and an allegedly inventive technique (with regard to FIG. 1) that each renders claims 1 and 4-6 obvious, depending on the construction applied.

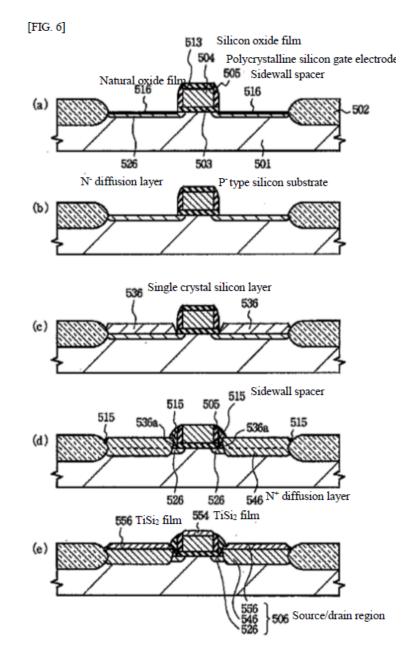

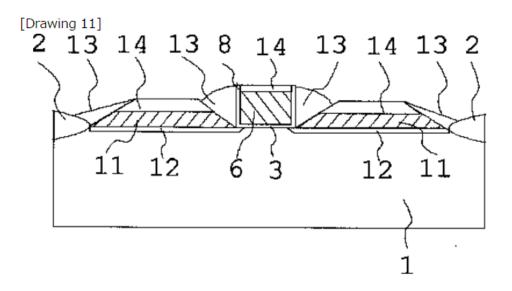

# a. Saito's FIG. 6 Technique

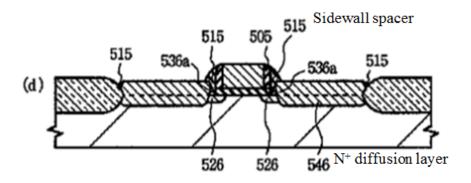

*Saito* is generally directed to methods of fabricating a semiconductor device. (Ex. 1005, [0017]; Ex. 1002, ¶48). *Saito* describes a prior art process in connection with its FIG. 6, which is reproduced below:

# IPR2017-01513 U.S. Patent No. 5,973,372

(Ex. 1005, FIG. 6, [0008]-[0013]; Ex. 1002, ¶49).

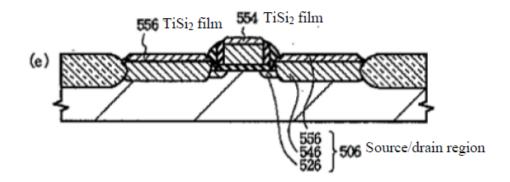

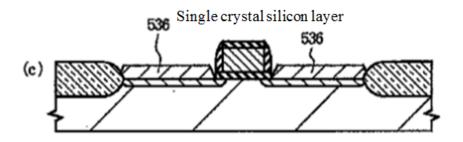

In FIG. 6, after the formation of the N- diffusion layer 526, *Saito* describes "a single crystal silicon layer 536 having a thickness of 100 to 200nm is selectively and epitaxially grown on the surface of the N- type diffusion layer 526."

(Ex. 1005, [0010]; Ex. 1002, ¶50). After the N+ diffusion layer is created, a "titanium film is formed over the entire surface, and a TiSi<sub>2</sub> film 554 and 556 are selectively formed ... on the surface of the N+ type diffusion layer 546 ... ." (Ex. 1005, [0011]-[0012]). This is a shallow junction. (Ex. 1005, [0013]; Ex. 1002, ¶51).

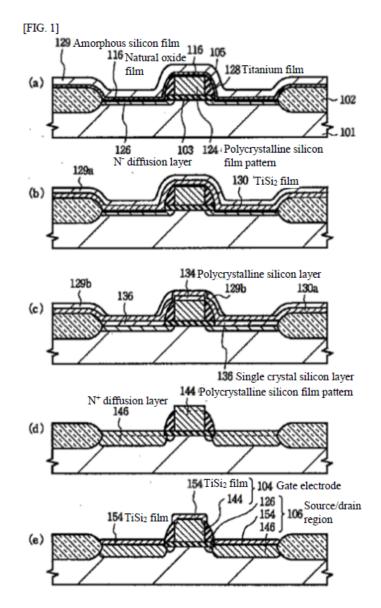

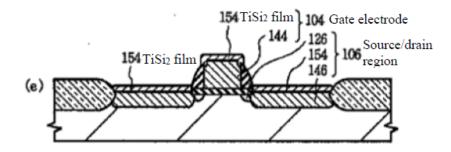

## b. Saito's FIG. 1 Technique

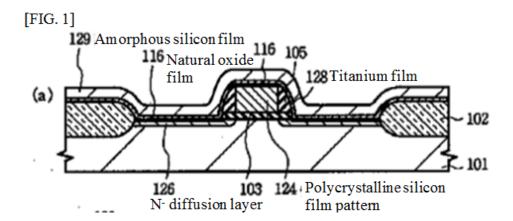

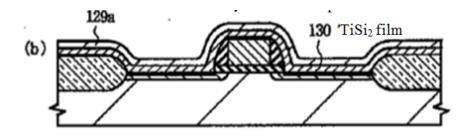

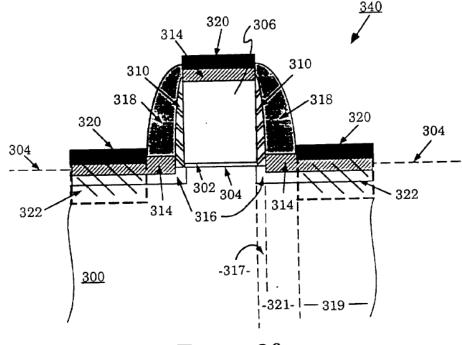

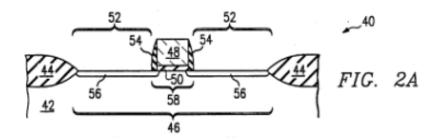

One of the allegedly inventive embodiments of *Saito* discloses the deposition of titanium 128 on a silicon substrate 101 having a thin natural oxide film 116. This embodiment is described in connection with FIG. 1, which is reproduced below:

(Ex. 1005, FIG. 1, [0025]). In this embodiment, a layer of amorphous silicon 129 is deposited on top of the titanium layer 128. (Ex. 1005, FIG. 1, [0025]; Ex. 1002, ¶53). The substrate is then annealed twice: the first annealing occurring between 400-500C, and the second annealing occurring between 500-600C. (Ex. 1005, [0026]-[0028]; Ex. 1002, ¶¶53-54).

During the first annealing, the process of forming a titanium silicide film 130 begins. (Ex. 1005, [0026]; Ex. 1002, ¶¶53-54). During the second annealing, the titanium silicide's formation is completed and the thin natural oxide film 116 previously present on the silicon substrate is removed. (Ex. 1005, [0027]). *Saito* also describes that the second annealing causes the remaining amorphous silicon film 129a to pass through the titanium silicide 130 and reach the substrate's surface

126. (Id.). In particular, Saito describes that:

When the second thermal annealing is carried out for a long time, the total energy of the system is decreased so that silicon from a portion of the amorphous silicon film 129a on the upper surface of the polycrystalline silicon film pattern 124 and on the surface of the Ndiffusion layer 126 via the TiSi<sub>2</sub> film 130, respectively passes through the  $TiSi_2$  film 130 and moves so as to reach the upper surface of the polycrystalline silicon film pattern 124 and the surface of the N- type diffusion layer 126. As a result, the polycrystalline silicon layer 134 having a thickness of about 70 is selectively grown in a solid phase on the surface of the polycrystalline silicon film pattern 124, the single crystal silicon layer 136 having a thickness of about 70 is selectively and epitaxially grown in a solid phase on the surface of the N- type diffusion layer 126; the TiSi<sub>2</sub> film 130 becomes the TiSi<sub>2</sub> film 130a, and the amorphous silicon film 129b is left only above the surface of the sidewall spacer 105 and above the surface of the field oxide film 102 via the TiSi<sub>2</sub> film 130a (FIG. 1 (c), FIG. 2 (c)).

(Ex. 1005, [0027]; Ex. 1002, ¶¶53-54).

The second thermal annealing is carried out at a temperature range so that the amorphous silicon film 129a is not changed into polysilicon film and the result of this anneal step is the formation of an epitaxial silicon layer 136 between the titanium silicide layer 130a and the source/drain junction. (Ex. 1005, [0027]-[0028]; Ex. 1002, ¶55). During the thermal anneal, the single crystal silicon layer at the source/drain junction also grows epitaxially, which contributes to the epitaxial silicon layer formed between the titanium silicide layer and the source/drain junction 126. (*Id.*). As explained below, this FIG. 1 embodiment of *Saito* mirrors the process and resultant structure described and claimed in the '372 Patent. (Ex. 1002, ¶72).

# 2. Specific Identification of Challenge

Under the construction Petitioner asserts should apply here, the challenged claims are obvious in view of *Saito* as depicted in FIGS. 1(a)-1(e). Alternatively, under a broader construction Petitioner expects PO may advocate notwithstanding its district court positions (where the epitaxial layer can be formed before silicide formation and where silicide formation can consume some of the epitaxial layer) the challenged claims are obvious in view of *Saito* as depicted in FIGS. 6(a)-6(e).

## a. Claim 1

## i. *Saito* FIGS. 1(a)-1(e)

The preamble of claim 1 states: "[i]n an integrated circuit in and on a silicon substrate having an active region including a field effect transistor with a source and a drain and a gate, all of which a conductive contact is made."

This is disclosed in *Saito*. (Ex. 1002,  $\P72$ ). The abstract of *Saito* states a purpose for the invention as "[a] method for fabricating a MOS transistor having a salicide structure having a source/drain diffusion layer in which there is a shallow junction depth and a source/drain region with reduced resistance value." (Ex. 1005, Abstract, [0024]). A POSA would understand that a MOS transistor such as the one disclosed in *Saito* contains an active region including a field effect transistor. (Ex. 1002,  $\P72$ ). Further, FIG. 1(e) discloses a gate and a conductive contact.

(Ex. 1005, FIG. 1(e)). *Saito* confirms this disclosure by describing the formation of a gate electrode. (Ex. 1005, [0024]).

Claim 1 of the '372 Patent requires "a single crystalline silicon substrate with a [sic] upper surface region." The silicon substrate 101 of Saito, depicted in FIG. 1(a), meets this limitation. Petitioner asserts that a POSA would understand that the teachings of Saito demonstrate the substrate 101 is a single crystalline semiconductor substrate based on a failure to indicate that it is not single crystalline. (Ex. 1002, ¶72). Nonetheless, to the extent a POSA would not have taken Saito's silence as a teaching of single crystalline silicon, a POSA would have found it obvious to use single crystalline silicon as the substrate 101 of Saito. (Ex. 1002, ¶72). In particular, Saito discloses "selectively and epitaxially growing a thin film of a single crystal silicon layer on the surface of a silicon substrate ....." (Ex. 1005, [0007]). A POSA would understand that in order to grow a single crystalline silicon thin film epitaxially, the substrate that acts as the seed layer must also be formed of single crystalline silicon. (Ex. 1002, ¶72). The textbook Silicon Processing for the VLSI Era by Wolf et al. ("Wolf") is a seminal, mid-1980's work in the semiconductor fabrication field that confirms that the "epitaxial growth process is a means of depositing a thin layer ... of single crystal material upon the surface of a single crystal substrate." (Ex. 1013, 76 (textbook page 124); Ex. 1002, ¶72). Thus, since the epitaxial growth of Saito is single crystalline, so too is the underlying substrate. (Id.). Accordingly, Saito renders this limitation obvious.

Claim 1 further requires "a shallow junction for each of the source and drain of the transistor underlying said upper surface of the silicon substrate." The shallow source and drain is depicted in *Saito* as an N- doped diffusion layer 126 in FIG. 1(a) or, alternatively, as an N+ doped diffusion layer 146 in FIG. 1(e). (*See also* Ex. 1005, [0016]). As the titanium film 128 is formed directly on the substrate 101 (and, in the process, the natural oxide film 116 is eliminated), the subsequently formed shallow junction never rises above the upper surface of the silicon substrate.

(Ex. 1005, FIG. 1(a), [0025]). Thus, *Saito's* disclosure of either region 126 or region 146 meets this limitation. (Ex. 1002, ¶72).

Claim 1 of the '372 Patent further requires "a metal silicide layer having a lower surface disposed adjacent the shallow junction of each of the source and drain in the silicon substrate and above said upper surface of the silicon substrate." This feature can be found in FIG. 1(b) of the *Saito* reference as titanium silicide layer 130.

(Ex. 1005, FIG. 1(b), [0026]-[0027]; Ex. 1002,  $\P72$ ). The formation of this TiSi<sub>2</sub> film 130 is not complete until the second annealing. This second annealing causes the natural oxide film to react with the TiSi<sub>2</sub>, causing the natural oxide to be removed, such that the formation of the titanium silicide film is adjacent to the substrate's surface. (Ex. 1005, [0027]; Ex. 1002,  $\P72$ ). To the extent PO argues that the natural oxide would *not* be removed, a POSA would have known that a natural oxide layer is not material to the fabrication process and could readily have been removed before the deposition of titanium. (Ex. 1002,  $\P72$ ). The titanium silicide layer described as layer 130 is contained within the TiSi<sub>2</sub> layers 154 and 156 at the point in fabrication illustrated in FIG. 1(e). (Ex. 1005, [0029]-[0030]). Thus, *Saito* meets this limitation.

Claim 1 of the '372 Patent further requires "an epitaxial silicon layer disposed between said upper silicon surface and said lower surface of metal silicide and adjacent the shallow junction of each of the source and drain whereby the metal silicide does not extend below the upper silicon surface and encroach upon the shallow junction of each of the source and the drain." The '372 Patent

33

describes this epitaxial silicon layer as a "solid phase epitaxy layer." (Ex. 1001, 4:62-5:3). *Saito* discloses the formation of an epitaxial layer as claimed from the remaining amorphous silicon disposed as part of the silicide formation process described above. (Ex. 1005, [0027]). In particular, *Saito* describes:

When the second thermal annealing is carried out for a long time, the total energy of the system is decreased so that silicon from a portion of the amorphous silicon film 129a on the upper surface of the polycrystalline silicon film pattern 124 and on the surface of the N<sup>-</sup> diffusion layer 126 via the TiSi<sub>2</sub> film 130, respectively passes through the TiSi<sub>2</sub> film 130 and moves so as to reach the upper surface of the polycrystalline silicon film pattern 124 and the surface of the N<sup>-</sup> type diffusion layer 126. As a result, the polycrystalline silicon layer 134 having a thickness of about 70 is selectively grown in a solid phase on the surface of the polycrystalline silicon film pattern 124, *the single* crystal silicon layer 136 having a thickness of about 70 is selectively and epitaxially grown in a solid phase on the surface of the N type diffusion layer 126; the TiSi<sub>2</sub> film 130 becomes the TiSi<sub>2</sub> film 130a, and the amorphous silicon film 129b is left only above the surface of the sidewall spacer 105 and above the surface of the field oxide film 102 via the  $TiSi_2$  film 130a.

(Ex. 1005, [0027], FIG. 1(c); emphasis added). Though this epitaxial layer on the surface of the N- diffusion layer is not illustrated in FIGS. 1(d) and 1(e), it is described as being positioned between layer 130 and the structure that forms the shallow junction (i.e., the N- diffusion layer 126 illustrated in FIG. 1(b)), satisfying

the claimed "epitaxial layer" having the required geometry. (See Ex. 1002, ¶30).

Moreover, *Saito's* discussion of FIG. 1(d) demonstrates that the epitaxial layer is still present even if not illustrated. (Ex. 1005, [0029]; Ex. 1002, ¶72). Specifically, when a second deposition of amorphous silicon is discussed, the thickness of said amorphous silicon "is determined by the required thickness of the single crystal silicon layer 136," which is the epitaxial layer formed as described above in paragraph 27 of *Saito*. (*Id*.). This demonstrates the epitaxial layer is still present, although not depicted, in FIGS. 1(d) and 1(e). (*Id*.).

For these reasons, the disclosed steps in *Saito* are identical to those described and claimed in the '372 Patent and the resulting structure is likewise identical. (Ex. 1002, ¶¶70-72). Claim 1 is obvious over this embodiment of *Saito* and its associated description under Petitioner's proposed construction of the claims.<sup>5</sup>

## ii. *Saito* FIGS. 6(a)-6(e)

Under an alternative interpretation, in which the epitaxial layer can be formed before the silicide layer (with the silicide formation consuming part of the epitaxial layer), other figures (and associated description) of *Saito* render claim 1

<sup>&</sup>lt;sup>5</sup> A POSA would have known that a functioning transistor was created as of FIG. 1(c) and processing could stop after this step. (Ex. 1002, ¶81).

obvious. Specifically, the prior art *Saito* describes in connection with FIG. 6 renders claim 1 of the '372 Patent obvious under this alternative construction.

Saito's FIG. 6 discloses the preamble of claim 1. For example, the abstract of Saito states a purpose for the invention as "[a] method for fabricating a MOS transistor having a salicide structure having a source/drain diffusion layer in which there is a shallow junction depth and a source/drain region with reduced resistance value." (Ex. 1005, Abstract, [0024]). With regard to FIG. 6, Saito teaches "a cross sectional view of the fabricating steps for a semiconductor device." (Ex. 1005, Further, while introducing then conventional art, Saito describes the [0008]). decreasing sizes of MOS transistor source and drain regions, and the FIG. 6 embodiment to achieve that goal. (Ex. 1005, [0002]). Further, it explains that the result of FIG. 6 is the formation of "an N-channel MOS transistor." (Ex. 1005, [0012]). A POSA looking at FIG. 6 would have understood that this device, which Saito states is relevant to the alleged invention disclosed therein, is an active region that contains or could contain a field effect transistor. (Ex. 1002, ¶73).

FIG. 6 illustrates a source, drain, gate, and conductive contact, as are further required. (Ex. 1005, FIG. 6). In particular, *Saito* describes that the N-channel MOS transistor formed by the FIG. 6 process includes "gate electrode 504" and "source/drain region 506." (Ex. 1005, [0012]). Claim 1 of the '372 Patent requires an integrated circuit that includes a single crystalline silicon substrate and a

shallow junction for both the source and drain. The silicon substrate 501 is depicted in FIG. 6(a). (*See also* Ex. 1005, [0009]; Ex. 1002, ¶73). A person of skill in the art would understand that this substrate is single crystalline based on the disclosure that the grown layer 536 is single crystalline. (*Id.*; *see also* Ex. 1005, [0010]). The shallow source and drain are depicted as an N+ doped diffusion layer 546 in FIG. 6(e).

(Ex. 1005, FIG. 6(e), [0013]; Ex. 1002, ¶73).

Claim 1 of the '372 Patent further requires a metal silicide layer having a lower surface disposed adjacent to the junctions. This feature can be found in FIG. 6(e) of the Saito reference as titanium silicide layer 556 formed by consuming part of the epitaxially grown silicon. (*See also* Ex. 1005, [0011]; Ex. 1002, ¶73).

Claim 1 of the '372 Patent further requires an epitaxial silicon layer disposed between said upper silicon surface and said lower surface of metal silicide and adjacent to the shallow junction of each the source and drain whereby the metal silicide does not extend below the upper silicon surface and encroach upon the shallow junction of each the source and drain. The '372 Patent describes this epitaxial silicon layer as a "solid phase epitaxy layer." (Ex. 1001, 4:62-5:3). *Saito* discloses the formation of this epitaxial layer as a "single crystal silicon layer 536 having a thickness of 100 to 200nm...selectively and epitaxially grown on the surface of the N- type diffusion layer 526." (Ex. 1005, [0010], FIG. 6(c)).

As the prior art process continues, the epitaxially grown crystal silicon layer can be found in FIG. 6(d) in its modified form 536a.

Although the epitaxially grown crystal silicon layer 536a is not depicted in

FIG. 6(e) under the TiSi<sub>2</sub> film 556, the N- type diffusion layer 526 is present and included as part of the source/drain. In FIG. 6(d), epitaxially grown crystal silicon layer 536a is located above the N- type diffusion layer 526. Therefore, the epitaxially grown crystal silicon layer 536a can also be considered adjacent to the shallow junction of each the source and drain in FIG. 6(d). (Ex. 1002, ¶73).

For these reasons, the disclosed steps in *Saito's* discussion of FIG. 6 render claim 1 obvious under the alternative construction PO may offer as described herein. (Ex. 1002, ¶¶52, 73).

## b. Claim 4

#### i. *Saito* FIGS. 1(a)-1(e)

Claim 4 is obvious in view of *Saito's* FIG. 1 embodiment. Claim 4 requires that "the shallow junction is P+/N." *Saito* discloses that "[f]urthermore, although the first example is applied to the N-channel MOS transistor, the present example is not limited to that, and can be applied to the fabrication method of a P-channel MOS transistor or a CMOS transistor." (Ex. 1005, [0034]-[0035]; Ex. 1002, ¶74).

## ii. *Saito* FIGS. 6(a)-6(e)

Claim 4 is obvious in view of FIG. 6 of *Saito*. Claim 4 requires that the shallow junctions must be a P+/N junction. *Saito* discloses that "[f]urthermore, although the first example is applied to the N-channel MOS transistor, the present

example is not limited to that, and can be applied to the fabrication method of a Pchannel MOS transistor or a CMOS transistor." (Ex. 1005, [0034]-[0035]). A POSA would have understood this passage to be a generally applicable passage that could apply either to the alleged invention of *Saito* or to the prior art embodiments described therein (including in connection with FIG. 6). (Ex. 1002, ¶75). Thus, claim 4 is obvious over *Saito*.

#### c. Claim 5

#### i. *Saito* FIGS. 1(a)-1(e)

Claim 5 is obvious in view of *Saito's* FIG. 1 embodiment. Claim 5 requires that the "gate includes and [sic - an] upper surface and a silicide layer is disposed on said upper layer." FIG. 1(b) of *Saito* shows that the silicide layer 130 is formed over the gate portion as required by this claim. *Saito* confirms this disclosure when it states that "a first thermal annealing is carried out in a nitrogen atmosphere at 400 to 500°C ... ." (Ex. 1005, [0026]). In the temperature range of the first thermal annealing, the reaction between silicon and the titanium film, 128, constituting the N<sup>-</sup> diffusion layer 126 and the polycrystalline silicon film pattern 124 "does not contribute to the silicidation reaction progress, and once finished, a uniform TiSi<sub>2</sub> film 130 can be obtained." (Ex. 1005, [0026]). The polysilicon film pattern 124 is "in the region in which a gate electrode is to be formed." (Ex. 1005, [0025]). Thus, claim 5 is obvious over *Saito*. (Ex. 1002, ¶76).

## ii. *Saito* FIGS. 6(a)-6(e)

Alternatively, FIG. 6(e) of *Saito* shows that the silicide layer 554 is formed over the gate portion as required by this claim. *Saito* confirms this disclosure when it states that "[t]hen, a titanium film is formed over the entire surface, and a TiSi<sub>2</sub> film 554 and 556 are selectively formed on the upper surface of the polycrystalline silicon gate electrode 504 and on the surface of the N<sup>+</sup> type diffusion layer 546 using RTA in a nitrogen atmosphere." (Ex. 1005, [0012]). Thus, claim 5 is obvious over *Saito*. (Ex. 1002, ¶77).

# d. Claim 6

#### i. *Saito* FIGS. 1(a)-1(e)

Claim 6 is obvious in view of *Saito's* FIG. 1 embodiment. Claim 6 requires "the depth of the shallow junction is less than about 2500Å." When converted, this requires the junction to have a depth of less than about 250nm. (Ex. 1002, ¶78). In *Saito*, N- junction has a depth of 40nm. (Ex. 1005, [0025]). The later formed N+ junction has a depth of 130nm. (Ex. 1005, [0029]). Thus, claim 6 is obvious over *Saito*. (Ex. 1002, ¶78).

## ii. *Saito* FIGS. 6(a)-6(e)

Claim 6 is obvious in view of the discussion of FIG. 6 of *Saito*. Claim 6 requires that the depth of the shallow junction is less than about 2500Å. When converted, this requires the junction to have a depth of less than about 250nm.

(Ex. 1002, ¶79). With regard to FIG. 6, *Saito* states "[a]lthough the N<sup>+</sup> type diffusion layer 546 has an equivalently deep junction depth, the effective junction depth becomes shallow if viewed from the surface of the initial P type silicon substrate 501. From this and the presence of the TiSi<sub>2</sub> film 556, the junction depth of the source/drain diffusion layer is shallow, and the resistance value of the source/drain region itself can be reduced." (Ex. 1005, [0013]).

Given the dimensions of the relatively larger epitaxial layer (described as 100 to 200nm) to the relatively smaller shallow junction depth, as well as the fact that *Saito* discloses the junction as a "shallow junction," a POSA would have understood that, at least at the thinner range disclosed in *Saito*, the shallow junction has a depth that meets the requirements of this claim limitation. (Ex. 1002, ¶79). Thus, claim 6 is obvious over *Saito*. (*Id*.).

# B. Ground 2: Claims 1 and 4-5 Are Unpatentable Under 35 U.S.C. § 103(a) as Obvious over *Yu*

As supported by Dr. Baker's declaration, claims 1 and 4-5 of the '372 Patent are obvious in view of *Yu* under the Petitioner's proposed construction.

## 1. Overview of the Prior Art of Ground 2

#### a. Yu

United States Patent No. 5,409,853 ("Yu") was filed on May 20, 1994, and issued on April 25, 1995. (Ex. 1007). Yu is prior art under 35 U.S.C. § 102(b).

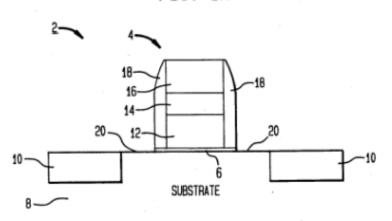

*Yu* is directed to a process of fabricating a semiconductor device. (Ex. 1007, 3:10-12; Ex. 1002, ¶56). *Yu* discloses the formation of a silicide gate on a substrate. (Ex. 1007, 3:10-28; Ex. 1002, ¶57). Palladium is then deposited on the substrate. (Ex. 1007, 3:40-57; Ex. 1002, ¶57). Next, the palladium is caused to react with the silicon surface via a low temperature anneal, forming metal-rich junction silicide, specifically, palladium silicide on the surface. (Ex. 1007, 3:58-4:9; Ex. 1002, ¶57). The palladium silicide extends below the substrate surface. (*Id.*).

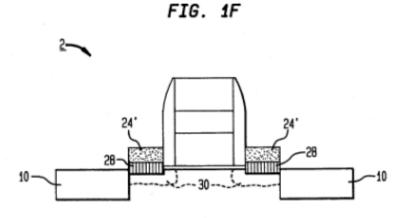

Next, a film or layer of amorphous silicon or fine grain silicon is deposited on the device. (Ex. 1007, 4:18-29; Ex. 1002, ¶58). As appropriate, the deposited silicon layer is then implanted with the proper dopant species; the proper dopant species depends on the polarity of the device. (Ex. 1007, 4:28-31; Ex. 1002, ¶58). The device is then annealed at a temperature of about 600C. (Ex. 1007, 4:37-46; Ex. 1002, ¶58). At this temperature, the palladium silicide acts as a transport media for the solid phase epitaxy. (*Id.*). The amorphous silicon layer is transported through the palladium silicide and epitaxially recrystallizes on the active silicon junction surface to form a doped epitaxial silicon region. (Ex. 1007, 4:37-46, FIG. 1F; Ex. 1002, ¶58). According to *Yu*, the palladium silicide that was formerly located below the substrate surface has been lifted and is now located on top of the doped epitaxial silicon region. (Ex. 1007, 4:53-58; Ex. 1002, ¶58).

## 2. Specific Identification of Challenge

#### a. Claim 1

The preamble of claim 1 states "[i]n an integrated circuit in and on a silicon substrate having an active region including a field effect transistor with a source and a drain and a gate, all of which a conductive contact is made." *Yu* teaches "[r]eferring initially to FIG. 1A, a semiconductor device or, more specifically, a metal-oxide-semiconductor field-effect-transistor (MOSFET), 2 is shown. The semiconductor device 2 includes a silicided gate 4 comprising a gate oxide or insulating film 6...." (Ex. 1007, 3:10-14). Further, claim 1 of *Yu* provides that the disclosure is directed to a "semiconductor device having raised source and drain regions." (Ex. 1007, 6:10-40; Ex. 1002, ¶83).

Claim 1 of the '372 Patent requires an integrated circuit that includes a single crystalline silicon substrate and a shallow junction for both the source and drain of the transistor underlying the upper surface of the silicon substrate.

The single crystalline silicon substrate is disclosed in Yu as semiconductor substrate 8 in FIG. 1A.

FIG. 1A

(Ex. 1007, FIG. 1A; Ex. 1002,  $\P$ 83). The fact that Yu refers to layer 12 as "polysilicon" indicates that the substrate, which is not specified to be polysilicon, is single crystalline silicon. (Ex. 1007, 3:15). Even if not expressly disclosed in Yu, it would have been obvious to a POSA that Yu taught or suggested the use of a single crystalline silicon substrate—the most common crystalline form of silicon substrate at the time of the filing of the '372 Patent. (Ex. 1002, ¶83). Specifically, Yu discloses "[a]t such a temperature, the palladium silicide 24 acts as a transport media for the solid phase epitaxy of the sputter deposited silicon 26. The amorphous, unseeded silicon layer 26 is transported through the palladium silicide 24 and epitaxially recrystallizes on the active silicon junction surfaces 20 to form doped epitaxial silicon regions 28, as shown in FIG. 1F." (Ex. 1007, 4:38-45). A POSA would understand that in order to grow a single crystalline silicon thin film epitaxially, the substrate that acts as the seed layer must also be formed of single

crystalline silicon. (Ex. 1002, ¶83). The "epitaxial growth process is a means of depositing a thin layer ... of single crystal material upon the surface of a single crystal substrate." (Ex. 1013, 76 (textbook page 124); *see also* Ex. 1002, ¶83).

The shallow junctions for both the source and drain are depicted in Yu as shallow outdiffused junctions 30 in FIG. 1F. (Ex. 1007, 5:48-54; Ex.1002, ¶83).

Claim 1 of the '372 Patent further requires a metal silicide layer having a lower surface disposed adjacent to the junctions. This feature can be found in FIG. 1F of *Yu* as the palladium silicide contacts 24'. (Ex. 1007, FIG. 1F, 3:39-4:10; Ex. 1002, ¶83). The palladium is deposited directly onto the substrate. (Ex. 1007, FIG. 1B, 3:39-4:10).

Claim 1 of the '372 Patent further requires an epitaxial silicon layer disposed between said upper silicon surface and said lower surface of metal silicide and adjacent to the shallow junction of each the source and drain whereby the metal silicide does not extend below the upper silicon surface and encroach upon the shallow junction of each of the source and drain. The '372 Patent describes this epitaxial silicon layer as a "solid phase epitaxy layer." (Ex. 1001, 4:62-5:3).

*Yu* discloses the formation of an epitaxial layer from amorphous silicon as described above. (Ex. 1007, 4:37-46; Ex. 1002, ¶83). In particular, the palladium silicide acts as a transport media for the solid phase epitaxy. The amorphous silicon layer is transported through the palladium silicide and epitaxially recrystallizes on the active silicon junction surface to form a doped epitaxial silicon region 28. (*Id.*; *see* FIG. 1F). This doped epitaxial silicon region is located below the palladium silicide 24' and at the surface of the shallow outdiffused junctions 30. (*Id.*; Ex. 1002, ¶83). Therefore, the doped epitaxial silicon region is located between the upper silicon surface and the lower surface of the metal silicide. (*Id.*). Further, the palladium silicide 24' is raised; therefore, there is no longer metal silicide that extends below the surface of the substrate 8. (Ex. 1007, 4:53-58; Ex. 1002, ¶82-83).

For these reasons, Yu meets the Petitioner's proposed construction, where the epitaxial layer is formed between the silicide and the substrate after formation of the silicide; therefore, claim 1 is obvious over Yu.

#### b. Claim 4

Claim 4 is obvious in view of *Yu*. Claim 4 requires that the shallow junctions must be a P+/N junctions. *Yu* discloses that the amorphous silicon layer

26 "is then implanted with the proper dopant species. The proper dopant species depends on the polarity of the device 2." (Ex. 1007, 4:28-31). This means that the dopant species can be either P+ or N+ depending on the polarity already applied to the silicon substrate. (Ex. 1002, ¶84). Thus, claim 4 is obvious over *Yu*.

## c. Claim 5