# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

SanDisk LLC Petitioner v.

Memory Technologies, LLC Patent Owner

Patent No. RE45,542

PETITION FOR INTER PARTES REVIEW UNDER 35 U.S.C. § 311, 37 C.F.R.

<u>§§ 42.100 ET SEQ.</u>

# **TABLE OF CONTENTS**

| I.   | MANDATORY NOTICES, STANDING, AND FEES                            | 1  |  |  |  |

|------|------------------------------------------------------------------|----|--|--|--|

|      | A. Mandatory Notices                                             |    |  |  |  |

|      | 1. Real Party in Interest - 37 C.F.R. § 42.8(b)(1)               | 1  |  |  |  |

|      | 2. Related Matters - 37 C.F.R. § 42.8(b)(2)                      | 1  |  |  |  |

|      | 3. Lead and Back-up Counsel - 37 C.F.R. § 42.8(b)(3)             | 2  |  |  |  |

|      | 4. Service Information - 37 C.F.R. § 42.8(b)(4)                  | 2  |  |  |  |

|      | B. Certification of Grounds for Standing - 37 C.F.R. § 42.104(a) | 3  |  |  |  |

|      | C. Fees - 37 C.F.R. § 42.103(a)                                  | 3  |  |  |  |

| III. | Identification of Challenge                                      |    |  |  |  |

|      | A. Challenged Claims                                             |    |  |  |  |

|      | B. Publications Relied Upon                                      | 3  |  |  |  |

|      | C. Grounds for Challenge                                         | 4  |  |  |  |

| IV.  | Background of the Technology                                     | 4  |  |  |  |

|      | A. Technical Background                                          | 4  |  |  |  |

|      | B. Level of Skill in the Art                                     | 6  |  |  |  |

| V.   | THE '542 PATENT                                                  |    |  |  |  |

|      | A. Overview of the '542 Patent                                   |    |  |  |  |

|      | B. The '542 Patent Prosecution History                           | 11 |  |  |  |

| VI.  | Prior Art                                                        | 13 |  |  |  |

|      | A. Overview of Garner (U.S. Patent No. 5,724,592)                | 14 |  |  |  |

|                                                                                 | B. | Overview   | v of Toombs (U.S. Patent No. 6,279,114)                                                                         | 16 |

|---------------------------------------------------------------------------------|----|------------|-----------------------------------------------------------------------------------------------------------------|----|

| VII.                                                                            | С  | laim Cons  | truction                                                                                                        | 17 |

|                                                                                 | A. | "peripher  | al device"                                                                                                      | 18 |

|                                                                                 | B. | "default v | value"                                                                                                          | 19 |

|                                                                                 | C. | "limiting  | value"                                                                                                          | 20 |

|                                                                                 | D. |            | ctor configured to connect the peripheral device to an electroni<br>r supplying power to the peripheral device" |    |

|                                                                                 | E. | "maximu    | m power consumption of the peripheral device"                                                                   | 23 |

|                                                                                 | F. |            | or setting the maximum power consumption of the peripheral a value"                                             | 28 |

| VIII. REASONABLE LIKELIHOOD EXISTS THAT THE CHALLED<br>CLAIMS ARE UNPATENTABLE. |    |            |                                                                                                                 | 29 |

|                                                                                 | A. | Ground 1   | : Garner anticipates Claims 28-33, 37, 38 and 40 under § 102.                                                   | 29 |

|                                                                                 |    | 1.         | Independent Claim 28                                                                                            | 29 |

|                                                                                 |    | 2.         | Dependent Claim 29                                                                                              | 39 |

|                                                                                 |    | 3.         | Dependent Claim 30                                                                                              | 39 |

|                                                                                 |    | 4.         | Dependent Claim 31                                                                                              | 41 |

|                                                                                 |    | 5.         | Dependent Claim 32                                                                                              | 42 |

|                                                                                 |    | 6.         | Dependent Claim 33                                                                                              | 42 |

|                                                                                 |    | 7.         | Dependent Claim 37                                                                                              | 43 |

|                                                                                 |    | 8.         | Dependent Claim 38                                                                                              | 43 |

|                                                                                 |    | 9.         | Dependent Claim 40                                                                                              | 44 |

|                                                                                 | B. |            | 2: Combination of Garner and Toombs renders Claims 28-33, vious under § 103                                     | 45 |

|                                                                                 |    | 1.         | Independent Claim 28                                                                                            | 57 |

|     |      | 2.  | Dependent Claim 29 | .67 |

|-----|------|-----|--------------------|-----|

|     |      | 3.  | Dependent Claim 30 | .67 |

|     |      | 4.  | Dependent Claim 31 | .68 |

|     |      | 5.  | Dependent Claim 32 | .68 |

|     |      | 6.  | Dependent Claim 33 | .68 |

|     |      | 7.  | Dependent Claim 37 | .69 |

|     |      | 8.  | Dependent Claim 38 | .69 |

|     |      | 9.  | Dependent Claim 39 | .69 |

|     |      | 10. | Dependent Claim 40 | .70 |

| IX. | CONC | LUS | ION                | .71 |

# PETITIONER'S LIST OF EXHIBITS

| EXHIBIT                                | DESCRIPTION                                                      |  |

|----------------------------------------|------------------------------------------------------------------|--|

| 1001                                   | U.S. Patent No. RE45,542                                         |  |

| 1002 Declaration of Dr. R. Jacob Baker |                                                                  |  |

| 1003                                   | U.S. Patent No. 4,019,068 (Bormann)                              |  |

| 1004                                   | File History for U.S. Patent No. 7,278,033 (App. No. 10/401,338) |  |

| 1005                                   | U.S. Patent No. 7,278,033 (Mylly)                                |  |

| 1006                                   | File History for U.S. Patent No. RE45,542 (App. No. 13/902,227)  |  |

| 1007                                   | U.S. Patent No. 5,724,592 (Garner)                               |  |

| 1008                                   | U.S. Patent No. 6,279,114 (Toombs)                               |  |

| 1009                                   | PCMCIA PC Card Standard, Release 2.1                             |  |

| 1010                                   | Declaration of Scott Bennett                                     |  |

SanDisk LLC ("Petitioner" or "SanDisk"), hereby petitions for *inter partes* review of Claims 28-33 and 37-40 of U.S. Patent No. RE45,542 ("the '542 Patent"), assigned to Memory Technologies, LLC ("Patent Owner" or "Memory Technologies").

#### I. MANDATORY NOTICES, STANDING, AND FEES

- A. Mandatory Notices

- 1. Real Party in Interest 37 C.F.R. § 42.8(b)(1)

The real parties in interest are: SanDisk LLC, Western Digital Corporation, Western Digital Technologies, Inc., SanDisk, Limited, SanDisk Storage Malaysia Sdn. Bhd., SanDisk Semiconductor (Shanghai) Co., Ltd., and SanDisk Israel (Tefen) Ltd. The following are direct or indirect parents or subsidiaries of the preceding companies: HGST, Inc., Virident Systems International Holdings Ltd., Western Digital International Ltd., SD International Holdings Ltd., SanDisk Technologies LLC, SanDisk International Holdco B.V., SanDisk IL Ltd., SanDisk Bermuda Limited, SanDisk Manufacturing Unlimited Company, SanDisk Bermuda Unlimited and SanDisk China Limited.

2. Related Matters - 37 C.F.R. § 42.8(b)(2)

The '542 Patent is subject to a pending lawsuit entitled *Memory Technologies, LLC v. SanDisk LLC et. al.*, No. 8:16-cv-02163 (C.D. Cal. filed Dec. 6, 2016). Petitioner is a defendant in this lawsuit. The '542 Patent is also subject to a pending investigation before the International Trade Commission, Inv. No. 337TA-3186, entitled In the Matter of Certain Flash Memory Devices and Components Thereof. Petitioner is a respondent in this investigation.

Further, the Petitioner has filed or will file other petitions for IPR against other patents held by Patent Owner, including Patent Nos. RE45,486; 8,307,180; 9,063,850; 7,275,186; 7,565,469; 7,739,487; and 7,827,370.

3. Lead and Back-up Counsel - 37 C.F.R. § 42.8(b)(3)

Petitioner designates the following counsels: Lead Counsel is Eliot D. Williams (Reg. No. 50,822) of Baker Botts L.L.P.; Back-up Counsels are Brian Oaks (Reg. No. 44,981) and David Wu (Reg. No. 66,351) of Baker Botts L.L.P.

4. Service Information - 37 C.F.R. § 42.8(b)(4)

Address: Baker Botts L.L.P., 1001 Page Mill Road, Building One, Suite 200, Palo Alto, California 94304-1007.

Telephone: 650-739-7500.

Facsimile: 650-736-7699.

Petitioner consents to service by electronic mail at:

- <u>eliot.williams@bakerbotts.com</u>,

- <u>brian.oaks@bakerbotts.com</u>, and

- <u>davd.wu@bakerbotts.com</u>.

A Power of Attorney is filed concurrently herewith under 37 C.F.R. § 42.10(b).

B. Certification of Grounds for Standing - 37 C.F.R. § 42.104(a)

Petitioner certifies that the '542 Patent is available for IPR and the Petitioner is not barred or estopped from requesting IPR of any claim therein on the grounds set forth herein.

C. Fees - 37 C.F.R. § 42.103(a)

The Office is authorized to charge any fee set forth in 37 C.F.R. § 42.15(a) or due in connection with this Petition to Deposit Account No. 02-0384.

III. IDENTIFICATION OF CHALLENGE

A. Challenged Claims

IPR is requested for Claims 28-33 and 37-40 of the '542 Patent.

- B. Publications Relied Upon

- Exhibit 1007 U.S. Patent No. 5,724,592 ("Garner"), entitled "Method and Apparatus for Managing Active Power Consumption in a Microprocessor Controlled Storage Device," filed December 5, 1996 and issued March 3, 1998. Garner is prior art under at least 35 U.S.C. §§ 102(a), 102(b) and 102(e). Garner was not previously presented to the PTO in the context of the '542 Patent.

- Exhibit 1008 U.S. Patent No. 6,279,114 ("Toombs"), entitled "Voltage Negotiation in a Single Host Multiple Cards System," filed November 4, 1998 and issued August 21, 2001. Toombs is prior art

under at least 35 U.S.C. §§ 102(a) and 102(e).

# C. Grounds for Challenge

The statutory grounds on which the challenges are based and the references relied upon are as follows:

- Ground 1: Garner anticipates Claims 28-33, 37, 38, and 40 under § 102.

- Ground 2: The combination of Garner and Toombs renders Claims 28-33, 37-40 obvious under § 103.

## IV. BACKGROUND OF THE TECHNOLOGY

A. Technical Background

Generally, the '542 Patent relates to power management of peripheral devices, such as memory cards. (EX1002 ¶¶68, 69.) A memory card is a device for storing electronic data. (EX1002 ¶70.) By 2002, several types of memory cards that use flash or EEPROM memory were in existence, including MultiMediaCard, CompactFlash, and PCMCIA memory cards. (EX1002 ¶71.)

A memory card typically relies on a host electronic device (*e.g.*, laptop) to which it is connected for power. (EX1002 ¶72.) Different hosts may have different power-supply restrictions or preferences, and different memory cards may have different power needs. (*Id.*) Since memory cards were intended to work with a variety of hosts, the issue of compatibility between hosts and memory cards was

well recognized by 2002. (*See, e.g.*, EX1007 1:48-62; EX1008 1:36-56.) A wellknown solution to the problem was to allow hosts and memory cards to negotiate the desired operating configuration. (EX1002 ¶73.) For example, a host may read the configuration options supported by a memory card and cause the card to operate in a selected option. (*See, e.g.*, EX1007 2:12-20, EX1008 15:42-49.)

Power management circuits have been used by memory devices since at least the 1970s. (EX1002 ¶74.) A well-known power-management technique was for hosts to specify a mode of operation for memory cards, which in turn affects the operational configuration of the memory cards. (EX1002 ¶75.) Memory cards capable of operating in different modes typically start at a default mode and change to a different mode upon request or meeting triggering conditions. (EX1002 ¶76-77.) The supported modes of operation are often stored on the memory device itself in order to inform a host of the available options. (EX1002 ¶78.)

The mode in which a memory card operates may affect one or more operational configurations that affect power consumption. (EX1002 ¶75.) Power consumption, which is often measured in Watt-Hours, refers to the amount of energy that is consumed or used over a period of time. (EX1002 ¶80.) Limiting the rate at which power is used (measured in Watts) would in effect limit power consumption. (*Id.*) For example, power consumption of a 60 Watt lightbulb is limited to 60 Watt-Hours in an hour. (*Id.*)

Power consumption of a memory card may be limited by adjusting operational configurations of the card. Well-known operational configurations that affect power consumption include, *e.g.*, clock frequency, bus width, and operating voltage/current. (EX1002 ¶¶81-84.) For example, a low clock frequency limits power consumption to a lower level relative to that of a higher frequency. (*Id.*)

#### B. Level of Skill in the Art

The '542 Patent relates to the field of power management systems for managing power consumption of peripheral devices, such as memory cards. (*See, e.g.*, EX1002 ¶66.) A person of ordinary skill in the art (hereinafter "POSITA") "would be a person with a bachelor's or master's degree in electrical engineering or a closely related field and two to three years of academic or industry experience in the field of memory system design." (*Id.*) Someone with less technical education but more practical experience or vice versa may also meet this standard. (*Id.*) The prior art also evidences the level of skill in the art.

#### V. THE '542 PATENT

#### A. Overview of the '542 Patent

The '542 Patent claims foreign priority to Finnish Patent Application No. 20020594, filed March 27, 2002. The '542 Patent is directed to methods and systems for determining and managing power consumption of a peripheral device (*e.g.*, MultiMediaCards). (EX1002 ¶86.) According to the Patent, the described solution is needed to address power-consumption compatibility issues between

-6-

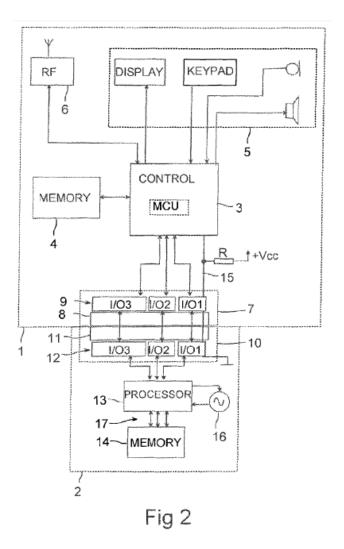

peripheral devices and the variety of host electronic devices to which they can connect. (*See* EX1001 1:61-2:4.) An illustrative embodiment of the '542 Patent is shown in Figure 2.

Figure 2 shows a peripheral device 2 connected to an electronic device 1 that supplies power to the peripheral device. (EX1001 4:41-48.) The peripheral device comprises a connector 10 for connecting the peripheral device to the electronic device. (EX1001 4:41-43.) The peripheral device also comprises "a processor 13 or the like for controlling the functions of the peripheral device 2," and a clock

generator 16 for generating clock signals for the processor. (EX1001 4:57-59, 5:1-4.) Further, the peripheral device comprises a memory 14 for storing program code and data, including "a first maximum value and a second maximum value for power consumption," with the first maximum value being lower than the second. (EX1001 4:65-5:1, 5:31-32.) In one embodiment, the two values define a range from which to select from. (EX1001 7:31-34.)

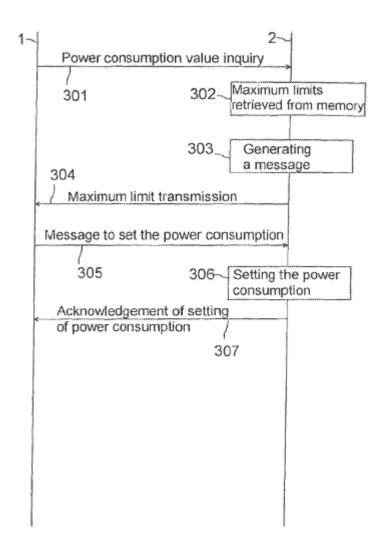

The '542 Patent describes an embodiment where "the suitable power consumption value can be negotiated by the electronic device and the peripheral device." (EX1001 9:27-31.) The operations performed by the devices are discussed with reference to Figure 3, copied below.

Fig 3

During startup, the power consumption of the peripheral device is set to a default value, and the processor also sets the clock generator to a frequency that corresponds to this power consumption value. (EX1001 5:26-34, 7:23-25.) Thereafter, the host electronic device queries the peripheral device for its first and second maximum power consumption values. (EX1001 5:48-54, Fig. 3, label 301) In response, the peripheral device reads the requested values from memory (Fig. 3,

label 302), generates a reply message containing the values (label 303), and sends the message to the host (label 304). (EX1001 5:56-6:5.) The host then selects from the received values and sends a "power control message indicat[ing] the power consumption value which is to be set as the maximum value for the peripheral device" (label 305). (EX1001 6:6-17.) Upon determining that the message is a power control message, the processor of the peripheral device "reads the maximum value for power consumption indicated in the message (block 306)." (EX1001 6:17-21.) Thereafter, the processor sets the clock frequency and/or bus width to a value corresponding to the maximum value for power consumption. (EX1001 6:21-27.) Other possible configuration adjustments include setting the operating voltage, current consumption, bus frequency, and operating mode (*e.g.*, "active mode" or "power-saving mode") of memory banks. (EX1001 8:1-39.)

The '542 Patent recognizes that several operational configurations that effectively limit a peripheral device's power consumption were well known in the art. For example, in its background section, the '542 Patent described power consumption being affected by clock frequency and bus width. (EX1001 2:49-59.) Additionally, the '542 Patent stated that "it should be evident that other methods for adjusting power consumption are also known," such as by controlling operating voltage and current consumption. (EX1001 7:64-8:10.)

However, as explained below, the techniques disclosed in the '542 Patent were well known in the prior art. (EX1002 Sections IX, X, and XI.)

B. The '542 Patent Prosecution History

The '542 Patent claims priority to a Finnish patent application, No. 20020594, filed on March 27, 2002. On March 26, 2003, the Applicant filed U.S. Patent Application No. 10/401,338 ("'338 Application") (EX1004). The '338 Application issued as U.S. Patent No. 7,278,033 ("'033 Patent") on November 2, 2007 (EX1005). On May 24, 2013, the Applicant sought reissue of the '033 Patent and filed Application No. 13/902,227 ("'227 Application") (EX1006). The resulting RE 45,542 Patent (EX1001) issued on June 2, 2015.

The prosecution history of the '338 Application clarifies the origin of the claim limitation, "a default value and a limiting value," as recited in Claim 28 of the '542 Patent. On June 26, 2006, the Applicant amended the claims to replace "first maximum value" and "second maximum value" with "first maximum limiting value" and "second maximum limiting value," respectively. (EX1004 p. 291-297.) The amendment was advanced with an argument that the cited prior art did not teach a "maximum power consumption" set between two limiting values. (EX1004 p. 298.) The Examiner rejected the claims because the words "maximum" and "limit" were superfluous or confusing, since "by the applicant's own admission, these values are merely limiting values for the maximum value,

and not the maximum value themselves." (EX1004 p. 312.) Accordingly, the Examiner recommended that the terms be amended to recite a first and second "limiting value for the power consumption." (*Id.*) In response to this rejection, the Applicant replaced "first maximum limiting value" and "second maximum limiting value" with "default value" and "limiting value," respectively. (EX1004 p. 321-327.)

The prosecution history of the reissuance of the '542 Patent is particularly relevant to the means-plus-function element and the "maximum power consumption" element. The reissue application added the dependent claims at issue in this IPR and sought to add the following limitation to independent Claim 28: "wherein the means for setting the maximum power consumption includes a processor configured to read an indication of the value from the received information and to set the maximum power consumption to the value based on the indication." (EX1006 p. 38-40.) The Applicant cited to "6:12-25" as the alleged support for this limitation. (EX1006 p. 41.)

With respect to the means-plus-function term, the Examiner rejected the added limitation because "processor" specified a structure for the recited function and therefore did not comply with Section 112 ¶6. (EX1006 p. 231-32.) In response, the Applicant replaced the added limitation with the language that ultimately issued, which removed "processor," and added Claim 38, which

-12-

specified a processor as the means-plus-function element in Claim 28. (EX1006 p. 259, 261.) Thereafter, the Examiner filed an Applicant Initiated Interview Summary, which stated that the Applicant expressed intent to invoke Section 112, ¶6 for Claim 28 but not Claim 38. (EX1006 p. 297.)

With respect to the term "maximum power consumption," The Examiner found it indefinite because the usage of "maximum" conflicts with its ordinary meaning. (EX1006 p. 231.) The Examiner reasoned that since "maximum power consumption" is set to a value between the default and limiting values, it is not actually a "maximum." (*Id.*) In response, the Applicant submitted a declaration from the inventor, Kimmo Mylly, to explain that "maximum" is a limit on power consumption. Citing to the declaration, the Applicant explained:

A POSA ("person having ordinary skill in the art at the time of filing the application") would understand that "maximum" as recited, at least "relates to a maximum limit on the fluctuating power consumption of a peripheral device." (Mylly Decl. ¶8.) "[A POSA] recognized that the power consumption of a peripheral device fluctuated over the course of its operation. As a result, the 'maximum power consumption' recited in the claims related to a limit on the fluctuating power consumption of the peripheral device." (*Id.* at ¶12.).

(EX1006 p. 266-267.)

VI. PRIOR ART

A. Overview of Garner (U.S. Patent No. 5,724,592)

Garner discloses a flash memory system capable of being placed in different power-expending modes by a host device. (EX1007 2:12-19.) To address compatibility issues between hosts and storage devices, Garner aims to "allow storage devices to function with all of these possible systems in the power ranges available to each of these systems." (EX1007 1:48-59, 4:40-45.)

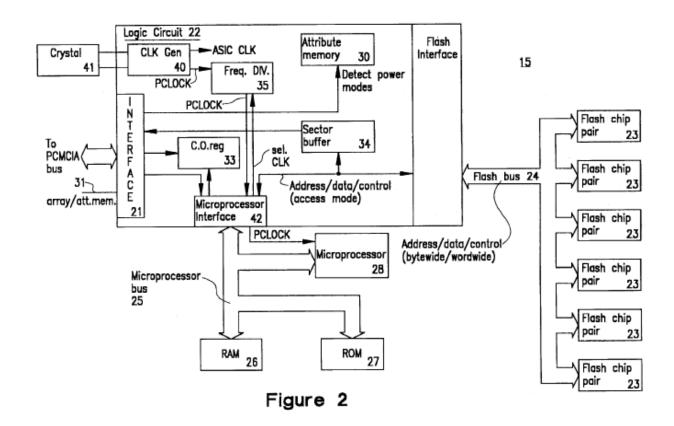

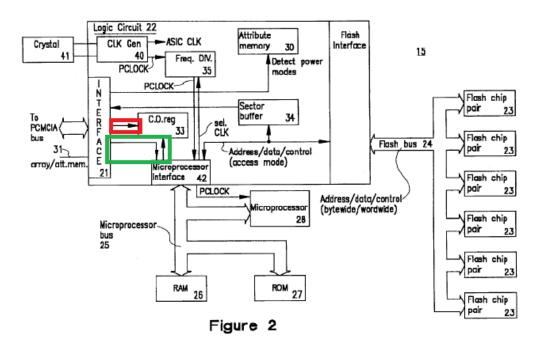

In one embodiment, Garner describes a microprocessor-controlled flash memory storage device 15, shown in Figure 2.

The storage device is configured to connect to and obtain power from a host digital device (*e.g.*, computer). (EX1007 4:36-45, Fig. 1.) The storage device connects to

the host through interface 21, PCMCIA bus, and PCMCIA bridge circuit 16 (shown in Fig. 1). (EX1007 3:26-33, 3:57-58.) Incoming signals are decoded by the interface and processed by logic circuit 22, which is "assisted in its operation by a microprocessor 28." (EX1007 3:59-4:16.)

In one embodiment, the storage device can operate in four different power modes "which use progressively less power," including a "lowest power mode" and a "highest power mode." (EX1007 5:3-31.) The available power modes are stored in attribute memory 30 and may be represented by two-bit "power tuples." (EX1007 5:12-15.)

In operation, the host can selectively place the storage device in a power mode supported by the device. The storage device starts up in a default mode, and in one embodiment it "always powers up in the lowest power mode." (EX1007 5:26-31, 6:48-51.) The storage device is configured such that the host can read its attribute memory and select any of the four available power modes. (EX1007 5:15-21.) The host then writes its power-mode selection into, *e.g.*, configuration options register 33. (EX1007 5:19-26.) Based on the host's selection, the storage device then configures, *e.g.*, its clock frequency and/or data-access bandwidth. (EX1007 5:41-6:15.) For example, the four power modes correspond to 16MHz, 8MHz, 4MHz, and 1MHz, respectively. (EX1007 5:50-60.) Garner further explains that clock frequency and data-access bandwidth affects how much power is expended.

(EX1007 5:46-50, 5:66-6:3.)

B. Overview of Toombs (U.S. Patent No. 6,279,114)

Toombs discloses a MultiMediaCard flash memory device capable of operating in a voltage range selected by a host. (EX1008 1:51-56, 16:21-25.) The invention addresses the problem of voltage compatibility between one or more memory cards and the host to which they are connected. (EX1008 1:51-56.)

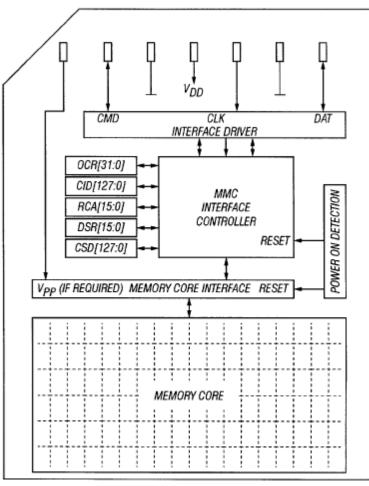

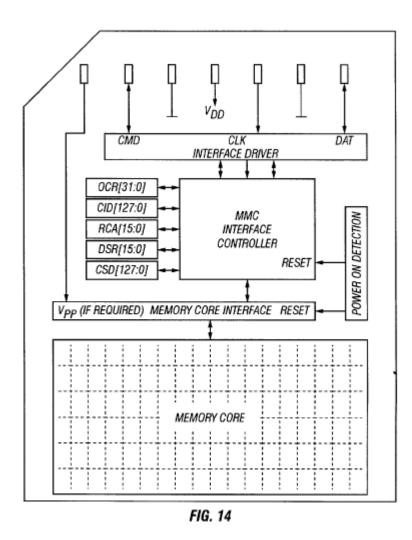

An embodiment of a MultiMediaCard is shown in Figure 14:

FIG. 14

The MultiMediaCard is designed to connect a host device through its connector pins. (EX1008 Fig. 1; EX1002 ¶182.) Figure 14 shows several connector pins on the top edge of the MultiMediaCard, including a power supply pins (*e.g.*,  $V_{DD}$  and  $V_{PP}$ ) and communication pins (*e.g.*, CMD and DAT). (*See* EX1008 7:32-44; *see also* EX1002 ¶182.) Figure 14 further shows that CMD and DAT signals are passed from the Interface Driver to the MMC Interface Controller for processing. (*Id.*) As shown, the Controller has exclusive access to the registers, which means the host cannot read/write to the registers directly. (*Id.*)

Toombs discloses a MultiMediaCard capable of negotiating an operating voltage with a host. (EX1008 15:22-24, 16:21-25.) The MultiMediaCard stores its operating voltage range (including "minimum and maximum operating values") in its OCR register. (EX1008 15:27-38, 15:66-16:9, Fig. 15.) During voltage negotiation with the host, the host queries the MultiMediaCard for its operating voltage range by sending a command. (EX1008 15:42-16:20, Fig. 38A.) "After a common operating voltage is determined by the host, the host sends the determined VDD voltage window as an operand of the command SEND\_OP\_COND (CMD1). In response to this command, each of the active cards will define its OCR register value according to this voltage." (EX1008 16:21-25.)

## VII. CLAIM CONSTRUCTION

Pursuant to § 42.100(b), a claim in an unexpired patent shall be given its

-17-

broadest reasonable interpretation ("BRI") in light of the specification in which it appears. Because the '542 Patent will not expire during the pendency of these proceedings, the Board should apply the BRI standard in its review. For terms not specifically listed and construed below, Petitioner interprets them for purposes of this review in accordance with their plain and ordinary meaning. Petitioner reserves the right to seek a different claim construction in litigation.

# A. "peripheral device"

The term "peripheral device" appears in Claims 28-33 and 37-40. The specification of the '542 Patent discloses that a peripheral device can be connected to an electronic device (e.g., laptops) and "expand the properties of the electronic device and to produce auxiliary functions." (EX1001 1:44-53; see also EX1002 ¶136.) The disclosed examples of peripheral devices include internal devices (e.g., memory cards and PCMCIA cards) and external devices (e.g., cameras). (EX1001 1:47-60, 4:20-28, 9:55-61; see also EX1002 ¶137-8.) Further, the recited "peripheral device" should at least be broad enough to cover memory cards, as recited in dependent Claims 32 ("the peripheral device is a memory card") and 39 ("the memory card is a MultiMediaCard"). (See also EX1002 ¶135.) Accordingly, a POSITA would understand the term "peripheral device" to mean "an internal or external device capable of expanding the properties of or produce auxiliary functions for a connected electronic device." (EX1002 ¶139.)

# B. "default value"

The term "default value" appears in Claims 28, 29, 37 and 40. Claim 28 recites in relevant part: (1) "a memory storing a default value ... for power consumption of the peripheral device" and (2) "a maximum power consumption of the peripheral device is set at a startup stage to said default value." Accordingly, the "default value" is at least a power consumption value to which the "maximum power consumption" is set. (*See* EX1002 ¶141.)

In addition, the ordinary meaning of "default" is "an adopted preselected option when no alternative has been specified," which is consistent with the term's usage in the specification. (EX1002 ¶142.) The specification states that during initialization of the peripheral device, "the power consumption of the peripheral device 2 is set to a default value which ... is a power consumption value according to the first maximum limit." (EX1001 5:25–31.) This initialization corresponds to the claimed "startup stage." (EX1002 ¶142.) Further, the specification states that unless the host subsequently selects a different value, the corresponding power consumption configurations need not be adjusted "because this value is the default value." (*See* EX1001 6:59-62.) This implies that the default value is preselected to be set as the peripheral device's "maximum power consumption." (EX1002 ¶142.)

The specification and claims do not specify or restrict the "default value" and "limiting value" to any particular type of measurement. Both values are "for

power consumption of the peripheral device." (EX1001 cl. 28; *see also* cls. 33, 37.) However, there is no requirement that the power consumption value be, *e.g.*, a specific clock frequency or any measure of power consumption (*e.g.*, Watt-Hours). (EX1002 ¶80.) The specification and claims only state that the clock can be adjusted to a frequency that <u>corresponds</u> to the power consumption value, maximum limit, or other similar terms. (*See, e.g.*, EX1001 5:32-34, 6:21-25, 14:18-22, cl. 31.) The exact nature of the "power consumption value" is not specified. Thus, under a broadest reasonable construction, the "default value" should not be limited to any particular type of measurement.

Accordingly, a POSITA would have understood "default value" to mean "a preselected power consumption value to which the 'maximum power consumption' of the peripheral device is set when no alternative has been specified." (EX1002 ¶143.)

C. "limiting value"

The term "limiting value" appears in Claims 28, 29, 33, and 40. Claim 28 recites in relevant part: (1) "a memory storing a ... limiting value for power consumption of the peripheral device"; (2) "said limiting value ... is defined for the power consumption of the peripheral device"; and (3) "setting the maximum power consumption of the peripheral device to a value which is in a range from said default value to said limiting value, said range including said default value and said

-20-

limiting value." Accordingly, the "limiting value" is at least a power consumption value to which the "maximum power consumption" can be set. (*See* EX1002 ¶145.)

The term "limiting value" does not appear in the specification, but the prosecution history of the '542 shows that it evolved from "second maximum value." (See EX1004 pp. 25-29, 291-97, 321.) In response to a rejection stating that the word "maximum" in "second maximum value" "lack[s] any significant meaning," the Applicant replaced the element with "second maximum limiting value" and argued that the "first value and the second value are limiting values for the maximum, the maximum being not yet set." (Id. pp. 280, 291-98). After the Examiner maintained his position that then-recited elements are not actually "maximum" values, the Applicant deleted the word "maximum" and replaced "second maximum limiting value" with "limiting value." (Id. pp. 312, 321.) In the specification, the "second maximum limit" (or similar terms) is "the power consumption value which is to be set as the maximum value for the peripheral device...." (EX1001 6:14-17.)

As discussed *supra* in Section VII.B, the specification and claims do not specify or restrict the "limiting value" or power consumption values in general to any particular type (*e.g.*, there is no requirement that it be a clock frequency or power consumption measurement). Thus, under a broadest reasonable

-21-

interpretation, the "limiting value," similar to the "default value," should not be limited to any particular type of measurement.

While Claim 28 restricts the "limiting value" to be "higher than said default value," there is no requirement in Claim 28 for it to be the highest, which is a limitation added by dependent Claim 33. (*See* EX1002 ¶148-49.) The specification states that there may be "more than two different maximum limits" (EX1001 7:31-33), which implies the possibility of having intermediate values between the lowest and highest values. (EX1002 ¶149.) Thus, the "limiting value" need not be the highest; it only needs to be higher than the "default value" as recited in Claim 28.

Accordingly, a POSITA would have understood "limiting value" to mean "a power consumption value (1) to which the 'maximum power consumption' of the peripheral device can be set and (2) is higher than the 'default value." (EX1002 ¶150.)

# D. "a connector configured to connect the peripheral device to an electronic device for supplying power to the peripheral device"

This limitation appears in Claims 28. Based on a plain and ordinary reading of this limitation, the phrase "for supplying power to the peripheral device" modifies the term that immediately precedes it, which is "electronic device" and not the "connector." (EX1002 ¶ 152.) If the phrase was intended specify a functional characteristic of the connector instead, the limitation should have for example recited: "a connector configured to connect the peripheral device to an

electronic device <u>and</u> for supplying power to the peripheral device." The recited phrase, however, modifies "electronic device."

Accordingly, a POSITA would understand that this limitation means "a connector configured to connect the peripheral device to an electronic device, wherein the electronic device is for supplying power to the peripheral device." (EX1002 ¶153.)

E. "maximum power consumption of the peripheral device"

This element appears in Claims 28, 30, 31, and 37-38.

A POSITA would have recognized that the '542 Patent describes an approach for limiting power consumption of a peripheral device that involves: (1) setting the peripheral device's maximum power consumption to a desired value and (2) adjusting operational configurations, such as clock frequency and bus width. (*See* EX1002 ¶156.) For example, the specification states that in addition to setting the power consumption value, the clock frequency or bus width is "<u>also</u>" set (EX1001 5:25-34, 3:45-54) or "<u>[n]ext</u>" set (EX1001 6:17-25, Fig. 3.). These operations are reflected in the claims, which recite that the "maximum power consumption of the peripheral device" (1) is set to the "default value" and can be set to "a value," (*see* Claim 28), and (2) the clock generator can be set to a "first frequency <u>corresponding</u> to the maximum power consumption of the peripheral device" (Claim 31).

A POSITA would understand that the term "maximum power consumption of the peripheral device" refers to a setting (e.g., a configuration parameter) of the peripheral device because it is repeatedly described as being set to a desired value. (EX1002 ¶157.) For example, Claim 28 recite that the "maximum power consumption of the peripheral device is set at a startup stage to said default value" and that the "means for setting the maximum power consumption of the peripheral device to a value" is configured to "set the maximum power consumption of the peripheral device to the value." (See also Claim 38.) The specification similarly states: "Signaling between the electronic device and the peripheral device sets a maximum value for the power consumption of the peripheral device which is between said first and second maximum values." (EX1001 Abstract; see also, e.g., 2:67-3:39, 3:48-52, 5:25-32, 6:14-17, 6:31-38, 6:45-49, 7:21-25, 8:61-64, 9:10-18, Fig. 3.)

A POSITA would recognize that the '542 Patent does not limit how or where the "maximum power consumption" is set. (EX1002 ¶158.) For example, the specification states that after the processor determines that a received message is a power control message, it "reads the maximum value for the power consumption indicated in the message (block 306)." (EX1001 6:17-21.) The referenced "block 306" is labeled in Figure 3 as "Setting the power consumption." According to Dr. Baker, "in this particular description the power consumption of

-24-

the device is set when the processor processes and recognizes the received maximum value." (EX1002 ¶158.) In another example, the specification states that the processor sets the "power consumption of the peripheral device" to a "power consumption value," and "also sets the frequency of the clock generator 16 to correspond to this power consumption value." (EX1001 5:25-34.) A POSITA would reasonably interpret this to encompass a scenario where the power consumption value is stored in memory or a register. (EX1002 ¶158.) Thus, according to Dr. Baker, a POSITA would reasonably understand that "the maximum power consumption could be set in any conventional manner, such as writing the specified value into a particular register/memory or processing and recognizing a value specified in a control message." (Id.)

Further, a POSITA would recognize that the value of the maximum power consumption is not limited to any particular type (*e.g.*, Watt-Hours, frequency, and bus width). (EX1002 ¶159.) The specification has broadly characterized the power consumption of the peripheral device being set to a "level" and a "less power consuming <u>state</u>" in response to an electronic device operating "in a power saving <u>mode</u>." (EX1001 9:10-18, 7:14-20.) Further, the specification states that <u>both</u> clock frequency and bus width can be changed according to the same maximum power consumption limit. (*See* EX1001 6:21-27, 9:1-4.) This is further evidence that the "maximum power consumption" can be a generic value since it can affect two

different types of operational configurations (i.e., clock frequency and bus width).

The prosecution history further shows that "maximum power consumption" does not have to be the actual power-consumption limit (*e.g.*, specified in Watt-Hours), but can be any value that effectively (even indirectly) sets a limit on power consumption. (EX1002 ¶160.) During prosecution, the Applicant submitted a declaration from the inventor of the '542 Patent, who stated that "the 'maximum power consumption' recited in the claims <u>relates</u> to a maximum limit on the fluctuating power consumption of a peripheral device," which may be limited by, *e.g.*, clock frequency. (EX1006 270-71.) According to Dr. Baker, a POSITA would reasonably interpret this statement to mean that a maximum power consumption of the peripheral device to be within a limit." (EX1002 ¶160.)

The value of the "maximum power consumption" affects how the peripheral device subsequently adjusts its operational configurations (*e.g.*, clock frequency). (EX1002 ¶161.) For example, once the maximum power consumption is set to a value, the processor adjusts the clock frequency to <u>correspond</u> to that value. (EX1001 5:25-34, 6:14-27, 7:52-63, cl. 31.) Other operational configurations that may be configured according to the maximum power consumption value include bus width, operating voltage, among others. (EX1001 6:25-27, 7:44-8:49; *see also* EX1002 ¶162.)

Any of these operational configurations set according to the maximum power consumption in turn limits the power consumption of the peripheral device during operation. (EX1002 ¶¶80-84, 161.) The specification explains that clock frequency and bus width (EX1001 2:49-59, 7:35-51), among other operational configurations (*See* EX1001 7:64-8:43), affect power consumption. The inventor of the '542 Patent stated in a declaration that a POSITA would have recognized that "the 'maximum power consumption' recited in the claims relates to a maximum limit on the fluctuating power consumption of a peripheral device." (EX1006 p. 270.) The inventor explains:

The skilled artisan knew that a memory device approached maximum power consumption at a particular clock frequency when it performed the most powerdemanding operations (*e.g.*, writing multiple banks at the same time). Conversely, power consumption at that frequency setting would fluctuate below the maximum power consumption when the device performed less demanding operation (*e.g.*, accessing only one memory bank at a time).

(EX1006 p. 271.) As explained in Dr. Baker's declaration, because the clock frequency establishes a rate at which power can be consumed (similar to a lightbulb's wattage), the maximum power that can be consumed over the time period (*e.g.*, Watt-Hours) is limited. (*See* EX1002 ¶¶80-81.) A POSITA would

-27-

have known that by affecting the operational configurations, the "maximum power consumption" would effectively limit the actual power consumption of the peripheral device. (EX1002 ¶¶81-84, 161.)

Accordingly, a POSITA would understand that this limitation means "a setting of the peripheral device whose value causes the power consumption of the peripheral device to be limited." (EX1002 ¶164.)

F. "means for setting the maximum power consumption of the peripheral device to a value"

This limitation occurs in Claims 28, 30, 31, and 38.

This limitation, as recited in Claims 28, 30, and 31, includes the phrase "means for" modified by functional language and is not modified by sufficient structure for achieving the specified function. Claim 38, however, recites "processor" as the structure. Thus, Claims 28, 30, and 31 invoke 35 U.S.C. § 112 ¶6 (Pre-AIA), whereas Claim 38 does not. This was the express intent of the Applicant. (*See* EX1006 297.)

The corresponding structure of this limitation is "a processor 13 or the like" (EX1001 4:57-59.) A POSITA would understand that a "processor" in the context of the Patent is "a circuitry that processes electronic data or signals." (EX1002 ¶169.) Examples of a processor include a controller, a general purpose processor, and an ASIC. (*Id.*) The processor being the corresponding structure is consistent with the prosecution history, during which the Applicant originally recited "a

processor" as the structure for this limitation but removed it once the Examiner noted that reciting structure was improper when invoking § 112 ¶6. (*See* EX1006 pp. 39, 230-31, 259, 261.) This construction is also consistent with Claim 38.

In the specification, processor 13 is described as the structure for setting the maximum power consumption. In particular, upon determining that a power control message has been received, the processor "reads the maximum value for power consumption indicated in the message (block 306)," where "block 306" is labeled as "Setting the power consumption" in Figure 3. (EX1001 6:14-21.) This description is captured by the last limitation of Claim 28. (EX1002 ¶171.)

Thus, a POSITA would have understood this means-plus-function element to mean "a processor or the like that is configured to obtain the value, as indicated by the received information, and to set the maximum power consumption of the peripheral device to the value." (*Id.*)

# VIII. REASONABLE LIKELIHOOD EXISTS THAT THE CHALLENGED CLAIMS ARE UNPATENTABLE.

All of the challenged claims are unpatentable as explained below.

# A. <u>Ground 1: Garner anticipates Claims 28-33, 37, 38 and 40 under</u> § 102.

# 1. Independent Claim 28

# (i) "A peripheral device comprising:"

To the extent the preamble is limiting, Garner teaches it. (EX1002 ¶¶184-87.) "Peripheral device" should be construed as discussed in Section VII.A, *supra*. Garner discloses a memory or storage device 15 that provides "storage functions" to a host digital device. (*See, e.g.*, EX1007 1:34-37, 1:48-52, 3:54-57, 4:49-52.) Figures 1 and 2 of Garner show storage device 15 being connected through PCMCIA to the host's "peripheral component interface (PCI) bus." (EX1007 3:18-21, emphasis added.) This is similar to the '542 Patent's description of a peripheral device being a PCMCIA card for memory expansion. (EX1001 1:47-53; EX1002 ¶186.) Thus, Garner's storage device teaches this element.

# (ii) "a memory storing a default value and a limiting value for power consumption of the peripheral device;"

Garner teaches this limitation. (EX1002 ¶¶188-192.) A "default value" and a "limiting value" should be construed as discussed in Sections VII.B and C, *supra*.

The storage device 15 in Garner comprises an attribute memory 30 that stores four "power-expending modes" which "use progressively less power," including a "lowest power mode" and a "highest power mode." (EX1007 2:11-19, 5:12-19, 5:26-31; EX1002 ¶189.) The power modes may be stored in the attribute memory as two-bit "power tuples." (EX1007 5:12-25.) Alternatively, instead of power modes, it would have been obvious to a POSITA that power consumption values (*e.g.*, in power/energy units) corresponding to the power modes can be stored. (EX1002 ¶189.) It would have been an obvious design choice to store either power modes or power consumption values to achieve the same functional purpose

of informing a host of the different power configurations supported by the storage device. (*Id.*) Discussions hereinafter relating to Garner's power modes apply equally to corresponding power consumption values. The selected power mode (or power consumption value) for the storage device limits power consumption of the storage device by causing corresponding adjustments to, *e.g.*, the clock frequency. (EX1007 5:40-61; EX1002 ¶190.)

The power mode of the storage device can be set to any one of the supported power modes, including the highest and the lowest. (EX1007 5:19-29.) The "storage device always powers up in the lowest power mode," and can be subsequently changed by the host to a different mode, such as the highest power mode. (EX1007 6:40-57, 5:25-31.) The lowest and highest power modes teach the "default value" and "limiting value," respectively. (EX1002 ¶191.) Thus, Garner teaches this limitation.

# (iii) "a connector configured to connect the peripheral device to an electronic device for supplying power to the peripheral device,"

Garner discloses this limitation. (EX1002 ¶¶193-198.) This limitation should be construed as discussed in Section VII.D, *supra*.

The storage device 15 can connect to a host (*e.g.*, computer), which supplies power to the storage device. (EX1007 1:34-59, 2:7-19; EX1002 ¶196.) The storage device connects to the host through interface 21, PCMCIA bus 17, and

PCMCIA bridge circuit 16. (EX1007 1:48-59, Figs. 1, 2; *see* EX1002 ¶194.) Any one or more of the interface, PCMCIA bus, and PCMCIA bridge circuit disclose the claimed "connector." (EX1002 ¶195.)

To the extent this limitation is construed to require a "connector," rather than an "electronic device", "for supplying power to the peripheral device," this limitation is still at least implicitly disclosed by Garner. Since the host supplies power to the storage device and the two are connected through the interface, PCMCIA bus, and PCMCIA bridge circuit, a POSITA would have recognized that these components must be the conduit for supplying power to the storage device. (EX1002 ¶197.) Furthermore, a POSITA would have recognized that PCMCIA connectors are capable of supplying power to and commonly did supply power to PCMCIA memory cards. (*Id.*)

Therefore, Garner discloses this limitation.

# (iv) "wherein a maximum power consumption of the peripheral device is set at a startup stage to said default value;"

Garner teaches this limitation. (EX1002 ¶¶199-205.) This limitation should be construed as discussed in Section VII.E, *supra*.

Garner discloses that the power mode of the storage device 15 can be set to any of the four supported power modes to limit power consumption of the storage device. (EX1002 ¶200.) In particular, Garner discloses that power tuples stored in

-32-

a register (e.g., bits 4 and 5 of configuration options register 33) designate the device's power mode. (EX1007 5:22-26.) Alternatively, a POSITA would have recognized that an alternative design choice is to store a corresponding power consumption value instead of a power mode to achieve the same function of indicating a desired configuration (hereinafter, discussions relating to storing a desired power mode applies equally to storing a corresponding power consumption value). (EX1002 ¶200.) The power mode reduces "the power used by components of the flash EEPROM memory arrays to a level compatible with a particular host system." (EX1007 2:7-10.) This is accomplished by the microprocessor testing "the state of the bits 4 and 5 in the configurations register 33 and run[ning] the appropriate setup process," such as adjusting the clock frequency and/or dataaccess bandwidth. (EX1007 5:32-6:15; EX1002 ¶202.) This in turn limits power consumption, as explained by Dr. Baker (EX1002 ¶¶80-84, 202), Garner (EX1007 5:45-50, 5:62-6:3), the '542 Patent (EX1001 2:49-55), and its inventor (EX1006 p. 271).

Garner further discloses that the storage device has a default power mode, which can be designated by the bits "00." (EX1007 5:29-31, 7:14-19.) In certain embodiments, "the storage device always powers up in the lowest power mode" (or alternatively, the lowest power consumption value), which corresponds to the recited "default value," as discussed *supra* in Section VIII.A.1.ii. (EX1007 6:4851.)

Therefore, Garner discloses this limitation.

# (v) "wherein at least said limiting value, which is higher than said default value, is defined for the power consumption of the peripheral device,"

Garner teaches this limitation. (EX1002 ¶¶206-209.)

The recited "default value" and "limiting value" are both "for power consumption of the peripheral device." A POSITA would therefore recognize that the comparative term "higher" applies to values for power consumption. (EX1002 ¶207.) As discussed in Section VIII.A.1.ii, Garner's "highest power mode" and "lowest power mode" can read on the claimed "limiting value" and "default value," respectively. The storage device uses more power in the "highest power mode" than in the "lowest power mode," because the "highest power mode" corresponds to relatively higher clock frequency and/or data-access bandwidth. (EX5:12-15, 5:46-6:15; EX1002 ¶207.) The highest and lowest power modes are defined in the attribute memory 30. (EX1007 5:12-29.)

In the event the comparative term "higher" applies to the indicators (*e.g.*, two-bit power tuples) used for representing power consumption values, a POSITA would nevertheless find this limitation to be taught by Garner. (EX1002 ¶208.) Garner discloses that the default power mode is represented by 00. (EX1007 5:29-31, 7:14-19.) In an embodiment where the highest power mode is the default, 00

would represent the highest power mode. (EX1007 5:29-31.) Since Garner also discloses an embodiment where the lowest power mode is the default, a POSITA would have recognized that it would be represented by 00 in that embodiment. (EX1002 ¶208.) Further, Dr. Baker explains that a POSITA would have recognized that "the particular bits used for representing information, such as power consumption value or power mode, is arbitrary." (*Id.*) Thus, a POSITA would have recognized that the highest and lowest power modes can be represented by 11 and 00, respectively. (*Id.*) As such, 11 is "higher" than 00.

Therefore, Garner discloses this limitation.

(vi) "wherein the peripheral device comprises means for setting the maximum power consumption of the peripheral device to a value which is in a range from said default value to said limiting value, said range including said default value and said limiting value,"

Garner teaches this limitation. (EX1002 ¶¶210-215.) The means-plusfunction element should be construed as "a processor or the like that is configured to obtain the value, as indicated by the received information, and to set the maximum power consumption of the peripheral device to the value." (Section VII.F, *supra*.) This mirrors the last limitation of Claim 28.

Garner's storage device 15 comprises a microprocessor 28 that discloses "a processor or the like that is configured to obtain the value, as indicated by the received information." (EX1002 ¶211-13) As discussed in Section VIII.A.1.vii

below, the storage device receives from the host signals that cause a selected power mode (or power consumption value) to be written to a register (corresponding to the "received information"). (*See also* EX1002 ¶212.) The power tuples (corresponding to the "value") indicated by the host can be stored in bits 4 and 5 of the configurations option register 33. (EX1007 5:19-31; 6:63-7:3, 7:45-59 ("a configuration register which stores a power mode configuration value, provided by a host processor").) The "microprocessor, responsive to commands from the host processor, [] read[s] the configuration register and [] control[s] operations related to the flash EEPROM array in accordance with the power mode configuration value." (EX1007 7:55-59; *see also* 5:32-38, 7:3-9.)

The microprocessor 28 is also configured to "to set the maximum power consumption of the peripheral device to the value." (EX1002 ¶213.) Garner discloses that "the microprocessor 28 tests the state of the bits 4 and 5 in the configuration options register 33 and runs the appropriate setup process" in order to "place the storage device 15 in the proper power mode for operation." (EX1007 5:32-38, 7:3-9.) Examples of the setup process include controlling the frequency divider circuit to set the processor clock frequency (PCLOCK) to a value that corresponds to the selected power mode (*e.g.*, 16MHz for the highest power mode), and setting the data-access bandwidth (*e.g.*, wordwide for the highest power mode). (EX1007 5:40-6:15). To do this, a POSITA would have recognized

that "the microprocessor must process the bits' values and identify the power mode that corresponds to the 'appropriate setup process." (EX1002 [213.) This identification of the desired power mode to select and then "run[] the appropriate set up process" corresponds to the claimed step of setting the maximum power consumption of the device to the value. (*Id.*)

Garner further discloses that the "value" "is in a range from said default value to said limiting value, said range including said default value and said limiting value." (EX1002 ¶214.) As discussed immediately above, the power mode selected by the host corresponds to the "value," and as discussed in Section VIII.A.1.ii the lowest and highest power modes correspond to the "default value" and "limiting value," respectively. Garner discloses that the storage device supports "four distinct power modes of operation which use progressively less power," two of which being the lowest and highest power modes. (EX1007 5:12-29.) A POSITA would have recognized that the four power modes from the lowest to the highest define a range. (EX1002 ¶214.) Garner also discloses that the host can select any of the four power modes, including the lowest and highest. (EX1007 5:12-31.)

Therefore, Garner discloses this limitation.

(vii) "wherein the peripheral device is configured to receive information from the electronic device for setting the maximum power consumption of the

# peripheral device, and"

Garner teaches this limitation. (EX1002 ¶¶212, 216-219.)

Garner discloses that the host can "place the storage device in the proper power mode of operation" by sending the selected power tuples to the storage device. (EX1007 2:12-19, 5:15-25.) The storage device is configured to receive signals from the host through PCMCIA bus, PCMCIA bridge, and interface 21, which "decod[es] signals furnished on the PCMCIA bus to a logic circuit 22." (EX1007 3:25-33, 3:57-60, Figs. 1 and 2.) The storage device then stores the power tuples (or alternatively power consumption values) provided by the host in, *e.g.*, bits 4 and 5 of the configuration options register. (EX1007 5:19-25, 7:51-59.) As discussed in Section VIII.A.1.vi, *supra*, the stored power tuples are subsequently used "for setting the maximum power consumption of the peripheral device." Thus, the signals from the host that caused the selected power tuples to be stored correspond to the claimed "information."

Therefore, Garner discloses this limitation.

(viii) "wherein the means for setting the maximum power consumption of the peripheral device is configured to obtain the value, as indicated by the received information, and to set the maximum power consumption of the peripheral device to the value."

As discussed above in Section VIII.A.1.vi, Garner discloses this limitation. (EX1002 ¶220.)

Accordingly, Claim 28 is anticipated because each of its limitations is disclosed by Garner. (EX1002 ¶221.)

# 2. <u>Dependent Claim 29</u>

Claim 29 recites: "The peripheral device according to the Claim 28, wherein said default value and at least one limiting value are stored in the peripheral device." Garner discloses this limitation. (EX1002 ¶222-226.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Section VIII.A.1.ii explains that Garner's lowest and highest power modes, which correspond the claimed "default value" and "limiting value," respectively, are stored in the attribute memory of the storage device. (EX1007 5:3-31.)

Therefore, Garner discloses every additional limitation introduced by Claim 29.

# 3. Dependent Claim 30

Claim 30 recites: "The peripheral device of Claim 28 further comprising: a clock generator, wherein the means for setting the maximum power consumption of the peripheral device is configured to adjust a frequency of the clock generator in response to the received information from the electronic device." Garner discloses this limitation. (EX1002 ¶227-233.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Garner discloses the recited "clock generator." A POSITA would have recognized that the storage device's "CLK Gen 40," which generates a "processor clock frequency (PCLOCK)" for the microprocessor, discloses the recited "clock generator." (EX1007 5:50-57, Fig. 2; EX1002 ¶229.) Alternatively, the combined circuitry of "CLK Gen 40" and the frequency divider circuit, "Freq. DIV. 35," discloses an adjustable "clock generator." (EX1007 5:50-57, Fig. 2; EX1002 ¶229.)

As discussed above, microprocessor 28 of Garner discloses the means-plusfunction element, and signals received from the host for power-mode selection discloses the recited "received information." (*See* Sections VIII.A.1.vi-vii; EX1002 ¶230.) Garner discloses that "[o]nce a mode of operation has been set by a host system when power is applied to the system, the microprocessor 28 utilizes processes stored in ROM 27 to place the storage device 15 in the proper power mode for operation." (EX1007 5:32-32; *see also* 4:11-16, 7:55-59 ("a microprocessor, responsive to commands from the host processor"); EX1002 ¶231.) Based on the set power mode, the microprocessor then takes the appropriate action to configure the device, such as controlling the "frequency of operation" by using the frequency divider circuit to adjust the clock to a frequency of 16 MHz, 8 MHz, 4 MHz, or 1 MHz. (EX1007 5:40-57; EX1002 ¶232.)

Therefore, Garner discloses every additional limitation introduced by Claim

30.

# 4. <u>Dependent Claim 31</u>

Claim 31 recites: "The peripheral device of claim 30, wherein the means for setting the maximum power consumption of the peripheral device is configured to adjust the frequency of the clock generator to a first frequency corresponding to the maximum power consumption of the peripheral device." Garner discloses this limitation. (EX1002 ¶234-239.)

Claims 28 and 30 are disclosed by Garner, as explained in Sections VIII.A.1 and VIII.A.3.

The microprocessor of Garner is configured to adjust the frequency (PCLOCK) of the clock generator to one of four frequencies (any of which can correspond to the recited "a first frequency"), which correspond to the four power modes of the storage device. (EX1007 5:38-57.) The microprocessor selects the appropriate frequency "in accordance with the power mode configuration values." (EX1007 8:6-9; *see also* 5:53-55, 7:3-8.) For example, the "lowest frequency is used for the lowest power mode while each higher frequency is used for the next higher power mode with the highest frequency being used for the highest power mode." (EX1007 5:57-61.)

Therefore, Garner discloses every additional limitation introduced by Claim 31.

-41-

## 5. <u>Dependent Claim 32</u>

Claim 32 recites: "The peripheral device of Claim 28, wherein the peripheral device is a memory card." Garner discloses this limitation. (EX1002 ¶240-243.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Garner's storage device is a flash EEPROM memory that can be joined to a host via PCMCIA (Personal Computer *Memory Card* International Association). (EX1007 3:27-48, Figs. 1, 2) (emphasis added). Thus, a POSITA would have recognized that the storage device is a "memory card." (EX1002 ¶242.)

Therefore, Garner discloses every additional limitation introduced by Claim 32.

## 6. <u>Dependent Claim 33</u>

Claim 33 recites: "The peripheral device of Claim 28, wherein the limiting value is a highest possible power consumption of the peripheral device." Garner discloses this limitation. (EX1002 ¶244-247.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Section VIII.A.1.ii explains that Garner's highest power mode discloses the claimed "limiting value." The highest power mode is the highest of the "total of four possible power modes of operation." (EX1007 19-29.) Further, the highest power mode correspond to the highest clock frequency and/or data-access

-42-

bandwidth, which results in the highest power consumption for the storage device. (See EX1007 5:47-6:15; EX1002 ¶246.)

Therefore, Garner discloses every additional limitation introduced by Claim 33.

# 7. <u>Dependent Claim 37</u>

Claim 37 recites: "The peripheral device of Claim 28, wherein the default value is a lowest possible maximum power consumption for the peripheral device." Garner discloses this limitation. (EX1002 ¶248-250.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Section VIII.A.1.ii explains that Garner's lowest power mode discloses the claimed "default value." The lowest power mode is the lowest of the "total of four possible power modes of operation." (EX1007 19-29.) Further, the lowest power mode correspond to the lowest clock frequency and/or data-access bandwidth, which results in the lowest power consumption for the storage device. (*See* EX1007 5:47-6:15; EX1002 ¶250.)

Therefore, Garner discloses every additional limitation introduced by Claim 37.

## 8. <u>Dependent Claim 38</u>

Claim 38 recites: "The peripheral device of Claim 28, wherein the means for

-43-

setting the maximum power consumption of the peripheral device comprises a processor operable to set the maximum power consumption of the peripheral device to the value." Garner discloses this limitation. (EX1002 ¶251-252.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Section VIII.A.1.vi explained that the microprocessor disclosed in Garner disclosed the means-plus-function limitation. The microprocessor "function[s] essentially as a general purpose processor in a manner well known to those skilled in the art." (EX1007 4:7-10.)

Therefore, Garner discloses every additional limitation introduced by Claim 38.

## 9. Dependent Claim 40

Claim 40 recites: "The peripheral device of Claim 28, wherein the range includes values other than the default value and the limiting value." Garner discloses this limitation. (EX1002 ¶253-254.)

Claim 28 is disclosed by Garner, as explained in Section VIII.A.1.

Section VIII.A.1.vi explained that the claimed "range" is taught by the four power modes of Garner. (EX1007 5:12-31.) The four power modes include two intermediate power modes other than the highest and lowest power modes, which teach the claimed "default value and the limiting value." (EX1007 5:22-31, 5:50-

61, 6:13-15; EX1002 ¶254.)

Therefore, Garner discloses every additional limitation introduced by Claim 40.

## B. <u>Ground 2: Combination of Garner and Toombs renders Claims</u> 28-33, 37-40 obvious under § 103.

A POSITA would have found it obvious to combine (1) Garner's teaching of a power consumption management system and (2) Toombs' teaching of a MultiMediaCard to arrive at the alleged invention of the '542 Patent. (EX1002  $\P255-57$ .) A POSITA looking to improve either Garner or Toombs would have been motivated to look to techniques used in the other reference because both references relate to similar fields of endeavor (managing and configuring memory cards), address similar problems (power compatibility between memory cards and hosts), and disclose similar solutions (allowing negotiation between host and card to determine the operating configuration). (*Id.*) As discussed below, it would have been obvious to a POSITA to modify Garner in view of Toombs, as well as to modify Toombs in view of Garner.

## Garner in view of Toombs

It would have been obvious to a POSITA that the storage device in Garner can adopt the form factor of a MultiMediaCard as taught in Toombs. (EX1002 ¶258.) Since MultiMediaCard is also a type of flash memory, a POSITA would have recognized that substituting its small form factor for that of the storage device

in Garner would have been a simple substitution of known elements. (*Id.*) A POSITA would have been motivated to do so to decrease the size of the storage device. (*Id.*) The modified MultiMediaCard would be capable of negotiating with its host to determine mutually acceptable power consumption levels, a benefit that Garner teaches. (*Id.*) The modification would expand the market for Garner's power management solution to the numerous host devices that were configured to accept MultiMediaCard cards, and further enable the modified MultiMediaCards to operate with different types of hosts. (*Id.*) This achieves Garner's objective of allowing the storage device to "function with as many types of digital systems as possible." (EX1007 1:60-62.)

As part of the modification, it would have been obvious to a POSITA to combine the connector pins and form factor taught in Toombs, as shown in Figure 14, with the flash memory storage device of Garner because such combination would achieve the desirable and predictable result of provide the flash storage device with electrical contacts and standard form factor for electrically connecting to an external device or interface. (EX1002 ¶259.) A POSITA would have recognized that the connector pins, once combined with Garner's storage device, would continue to perform the same function as described in Toombs. (*Id.*) This result is predictable and within the level of skill in the art since connector pins have long been used by memory cards and other types of electrical peripheral devices

for receiving and outputting electronic signals, as confirmed by the teachings of Toombs. (*Id.*)

A POSITA would have recognized that the modification may also involve modifying Garner's storage device to accommodate the communication protocol of MultiMediaCards. (EX1002 ¶260.) For example, Garner's microprocessor may be modified to handle host commands and register access, since a MultiMediaCard's host may be unable to access the card's registers directly. (*Id.*)

In view of Garner and Toombs' teachings, it would have been obvious and within the level of skill of a POSITA to make the modification. (EX1002 ¶261.) Garner describes a microprocessor-controlled memory/storage device 15 configured to manage power consumption according to the power mode selected by a host and written into a register (e.g., configuration options register 33). (EX1007 Abstract, 1:10-13, 5:19-25.) The storage device comprises a microprocessor 28. (EX1007 Fig. 2.) In view of Toombs' teachings, a POSITA would have found it obvious to modify the microprocessor to handle host commands for writing a selected power mode into a register. (EX1002 ¶261.) Toombs teaches a MultiMediaCard with a MMC Interface Controller that is configured to process commands from the host and write to the MultiMediaCard's registers. (Id.) Toombs discloses that during voltage negotiation, the host determines an acceptable voltage range supported by the MultiMediaCard and

-47-

"sends the determined VDD voltage window as an operand of the command SEND\_OP\_COND (CMD1). In response to this command, each of the active cards will define its OCR register value according to this voltage." (EX1008 16:21-25.) Figure 14 shows that the MMC Interface Controller is configured to receive the CMD and DAT signals and has exclusive access to the registers. (EX1002 ¶261.) Thus, a POSITA would have recognized that the Controller is responsible for processing the host's command and operand and, in response, writing the specified voltage range into the OCR register. (*Id.*)

In view of Toombs, a POSITA would have found it obvious that the storage device in Garner can be modified to have a central microprocessor that handles register-access commands from the host and controls access to the registers. (EX1002 ¶262.) By applying Toombs' known technique for commanding a memory card to store data, a POSITA would have recognized that in Garner, signals from the host for writing the selected power mode to the register (EX1007 5:19-21) can be a command and an operand specifying a desired power mode. (EX1002 ¶262.) Further, a POSITA would have also found it obvious to modify the architecture of Garner's storage device in a manner taught by Toombs (*e.g.*, Figure 14) such that the microprocessor is configured to receive commands and operands from the host and control access to the registers. (EX1002 ¶263.)

For example, Dr. Baker explains that the storage device shown in Figure 2 of

Garner can be modified (modification shown below) by removing the data path, highlighted in red, from interface 21 to configuration operations register 33. (*Id.*) This represents the host not having direct access to write to the register 33. (*Id.*) The remaining data path, highlighted in green, shows that the microprocessor 28 (via microprocessor interface 42) handles incoming signals from the host and controls access to the configuration options register 33. (*Id.*)

In this modified system, the host in operation may send a command and operand specifying the desired power mode to the storage device. (EX1002  $\P$ 262.) In response, the microprocessor of the storage device may process the command and write the desired power mode into the configuration options register. (EX1002  $\P$ 263.)

A POSITA would have been motivated to combine Garner and Toombs as described above for a variety of reasons. A POSITA would have recognized that having the microprocessor handle register-access commands provides a layer of logical abstraction to the host. (EX1002 ¶264.) This benefits the host because the host would not need to know precisely where to store data (*e.g.*, bits 4 and 5 in the configuration options register 33, as disclosed in Garner). (*Id.*) Instead, as shown in Toombs, the host can simply sends a SEND\_OP\_COND command with a voltage-range operand. (*Id.*) This design is also beneficial to the memory storage device because it allows the device to unilaterally alter the storage location without needing to inform the host. (*Id.*)

Another benefit of having a microprocessor-controlled memory device is the flexibility afforded to device designers for changing how the device operates. (EX1002 ¶265.) Since the microprocessor operates according to the stored software or processes (EX1007 4:13-16), a POSITA would have recognized that the manner in which commands are handled and data are stored can be altered simply with a software update. (EX1002 ¶265.) Since both Garner and Toombs address compatibility issues of memory cards, a POSITA would have recognized the importance of enabling memory devices to have the flexibility to change its operation if the need arises. (*Id.*)

A POSITA would have also recognized that a microprocessor controlling

-50-

access to registers provides the benefit of simplifying the overall system design and providing extra protection to the memory card since a single unit has control over read/write operations. (EX1002  $\P$ 266.) Configuring the registers to be exclusively controlled by the microprocessor provides the storage device with stability and predictability with respect to what is written to its registers, and prevents the host from writing improper or incorrectly formatted data to the configuration register. (*Id.*)

### Toombs in view of Garner

For similar reasons, a POSITA would have found it obvious to modify a MultiMediaCard, such as the one disclosed in Toombs, to include the power consumption management capabilities of Garner. (EX1002 ¶267.) In particular, Garner teaches how to configure a memory card to operate in a power mode selected by a host and adjust operating configurations (*e.g.*, clock frequency) accordingly to limit power consumption. (EX1007 2:11-19, 5:12-61.) A POSITA would have been motivated to modify Toombs' MultiMediaCard to include Garner's power consumption management capabilities because doing so would improve compatibility with hosts, as explained in Garner. (EX1002 ¶267.) Garner states that it is "desirable to allow any [removable] storage device ... to function with as many different types of digital systems as possible." (EX1007 1:60-62) However, because powers supplied by hosts differ, Garner recognize a need to

improve compatibility between hosts and memory cards. (EX1007 1:48-59.) Toombs similarly recognizes compatibility issues faced by MultiMediaCards. (EX1008 1:37-41, 15:39-44, 16:14-20.) To address compatibility issues, both Toombs and Garner devised a solution where the host and the memory card negotiate an acceptable operational configuration. (EX1007 2:11-20; EX1008 1:50-55.) While Toombs addresses operating voltage compatibility (EX1008 10:5-13, 16:21-25), it does not address power consumption compatibility. A POSITA would have been motivated to modify Toombs in accordance with Garner to design a MultiMediaCard with power consumption management capabilities in order to further improve compatibility. (EX1002 ¶267.)

Further, it would have been obvious to a POSITA that Garner's teaching can be implemented by a MultiMediaCard. (EX1002 ¶268-69.) A POSITA would have recognized that the storage device 15 in Garner is a flash memory card (EX1007 2:3-20, 3:27-33) and a MultiMediaCard is a type of flash memory card (EX1008 1:27-32, 1:45-47, Figs. 1 and 14). (EX1002 ¶268.) Moreover, a POSITA would have recognized that a MultiMediaCard capable of negotiating operating voltages (Toombs) can similarly be configured to negotiate power-expenditure modes (Garner), since the negotiation solutions described in Garner and Toombs utilize similar underlying techniques of configuring a memory card to store supported operational configurations for selection by a host. (EX1002 ¶269.)