## IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| In re Patent of:  | Gerald J. Banks                                                 |

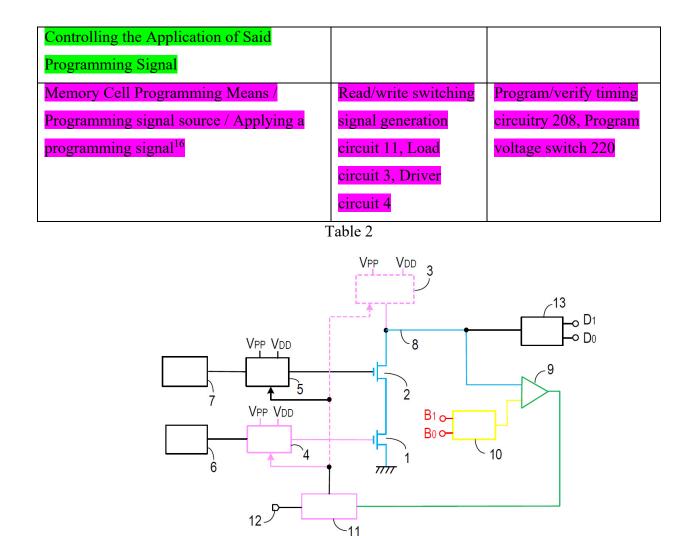

|-------------------|-----------------------------------------------------------------|

| U.S. Patent No .: | 5,764,571                                                       |

| Issue Date:       | June 9, 1998                                                    |

| Serial No.:       | 08/410,200                                                      |

| Filing Date:      | Feb. 27, 1995                                                   |

| Title:            | Electrically Alterable Non-Volatile Memory With N-Bits Per Cell |

Mail Stop Ex Parte Reexam Central Reexamination Unit Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

# REQUEST FOR EX PARTE REEXAMINATION UNDER 35 U.S.C. § 302 AND 37 C.F.R. § 1.510

Reexamination under 35 U.S.C. § 302 and 37 C.F.R. § 1.510 is requested for claims 1, 9, 12, 30, 42, and 45 of U.S. Patent No. 5,764,571 (the '571 patent), which issued on June 9, 1998 to assignee BTG USA Inc.

# Attorney Docket No. 36144-0018RX1

# TABLE OF CONTENTS

## Page

| I.    | INTRODUCTION                                                                                    |  |

|-------|-------------------------------------------------------------------------------------------------|--|

| А.    | . New Prior Art References Teach the Features that were the Basis for Allowance of the '571     |  |

|       | Patent7                                                                                         |  |

| B.    | New Prior Art References Teach the Features Cited as the Basis for Not Instituting Inter Partes |  |

|       | Review of the '571 Patent10                                                                     |  |

| C.    | New Reference U.S. Patent No. 7,911,851 Shows that the Claims of the '571 Patent Are Invalid    |  |

|       | for Obviousness-type Double Patenting11                                                         |  |

| D.    | New Evidence in Appendix A Supports Re-Examination                                              |  |

| II.   | CLAIMS FOR WHICH REEXAMINATION IS REQUESTED12                                                   |  |

| III.  | IDENTIFICATION OF PATENTS AND PRINTED PUBLICATIONS PRESENTED TO SHOW                            |  |

| SUBS  | TANTIAL NEW QUESTIONS OF PATENTABILITY                                                          |  |

| IV.   | CO-PENDING PROSECUTION AND LITIGATION14                                                         |  |

| V.    | THE ORIGINAL PROSECUTION HISTORY14                                                              |  |

| VI.   | PRIOR IPR PETITIONS                                                                             |  |

| VII.  | THE REFERENCES RELIED UPON HEREIN PROVIDE NEW, NON-CUMULATIVE                                   |  |

| TECH  | NICAL TEACHINGS                                                                                 |  |

| А.    | VLSI Design Provides New, Non-Cumulative Technical Teachings                                    |  |

| В.    | Connolly Provides New, Non-Cumulative Technical Teachings                                       |  |

| C.    | Oshita Provides New, Non-Cumulative Technical Teachings                                         |  |

| VIII. | ADDITIONAL PRIOR ART and newly submitted evidence                                               |  |

| IX.   | SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY NOT RAISED DURING                                    |  |

| PROS  | ECUTION OF THE '571 PATENT                                                                      |  |

| A.    | Overview of the '571 Patent Claims, Key Claim Constructions                                     |  |

| B.    | SNQ #1: Claims 1, 9, 12, 30, 42, and 45 are Obvious over Kitamura in view of VLSI Design 33     |  |

| C.    | SNQ #2: Claims 1, 9, 12, 30, 42, and 45 are Obvious over Kitamura in view of Connolly           |  |

| D.    | SNQ #3: Claims 1, 9, 12, 30, 42, and 45 are Obvious over Kitamura in view of Oshita73           |  |

| E.    | SNQ #4: Claims 1, 9, 12, 30, 42, and 45 are Invalid for Obviousness-Type Double Patenting in    |  |

|       | view of the '851 Patent                                                                         |  |

| X. CONC | LUSION1 | 49 |

|---------|---------|----|

|---------|---------|----|

# APPENDIX

# A Documents Filed Under Seal Pursuant to MPEP § 724.02 – Subject To Protective Order

# EXHIBITS

| А | U.S. Patent No. 5,764,571 to Banks ("the '571 patent")                                                                                                        |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| В | Excerpts from the Prosecution History of the '571 patent ("Prosecution History")                                                                              |  |

| С | Declaration of R. Jacob Baker ("Expert Declaration")                                                                                                          |  |

| D | Certified Translation of Japanese Patent Application Kokai No. S62-<br>34398 (A) ("Kitamura") (annotated with paragraph numbers)                              |  |

| E | Excerpts from "VLSI Design Techniques for Analog and Digital Circuits," by Geiger, Allen, and Strader, McGraw-Hill, 1989 ("VLSI Design")                      |  |

| F | U.S. Patent No. 4,198,622 to Connolly ("Connolly")                                                                                                            |  |

| G | U.S. Patent No. 5,014,054 to Oshita ("Oshita")                                                                                                                |  |

| Н | U.S. Patent No. 7,911,851 to Banks ("the '851 patent")                                                                                                        |  |

| Ι | Japanese Patent Application Kokai No. S62-34398 (A)                                                                                                           |  |

| J | Decision Denying Institution of <i>Inter Partes</i> Review, Case Nos. IPR2015-00504, IPR2015-00517, paper 8 (PTAB July 20, 2015) ("IPR Institution Decision") |  |

| K | Decision Denying Request for Rehearing, Case No. IPR2015-00504,<br>paper 10 (PTAB March 31, 2016) ("IPR Rehearing Decision")                                  |  |

| L | Patent Owner Preliminary Response, Case No. IPR2015-00504, paper 7                                                                                            |  |

|   | (April 21, 2015) ("IPR POPR")                                                                                                                                 |  |

| М | Excerpts from the Prosecution History of the '851 patent ("'851 Patent                                                                                        |  |

|   | File History")                                                                                                                                                |  |

| N | U.S. Patent No. 5,218,569 ("the '569 patent")                                                                                                                 |  |

| 0  | U.S. Patent No. 5,394,362 ("the '362 patent")                              |  |

|----|----------------------------------------------------------------------------|--|

| Р  | Excerpts from the Prosecution History of U.S. Patent No. 5,394,362         |  |

|    | ("'362 Patent File History")                                               |  |

| Q  | U.S. Patent No. 6,002,614                                                  |  |

| R  | U.S. Patent No. 6,246,613                                                  |  |

| S  | U.S. App. 09/493,139 ("the '139 application")                              |  |

| Т  | U.S. Patent No. 6,353,554                                                  |  |

| U  | U.S. Patent No. 6,434,050                                                  |  |

| V  | U.S. Patent No. 6,714,455                                                  |  |

| W  | U.S. Patent No. 7,006,384                                                  |  |

| Х  | U.S. Patent No. 7,068,542                                                  |  |

| Y  | U.S. Patent No. 7,286,414                                                  |  |

| Ζ  | U.S. Patent No. 8,570,814                                                  |  |

| AA | Images from Patent Application Information Retrieval (PAIR) website        |  |

|    | (showing the earliest application to which the '851 patent claims priority |  |

|    | is the application for the '571 patent)                                    |  |

| AB | Redline comparison between the '362 and '571 patent specifications         |  |

| AC | Images from Patent Application Information Retrieval (PAIR) website        |  |

|    | (showing that the '571 patent is a CIP of the '816 application)            |  |

| AD | U.S. Patent No. 5,095,344 to Harari ("Harari")                             |  |

| AE | June 17, 1997 Office Action response from the file history for U.S. Patent |  |

|    | No. 5,764,571                                                              |  |

| AF | MLC v. Micron, Case No. 3:14-cv-03657-SI, Dkt. No. 128 (April 26,          |  |

|    | 2017) - Order Denying Micron Motion for Summary Judgment                   |  |

| AG | MLC v. Micron, Case No. 3:14-cv-03657-SI, Dkt. No. 72 (August 15,          |  |

|    | 2016) - MLC Opening Claim Construction Brief                               |  |

| AH | MLC v. Micron, Case No. 3:14-cv-03657-SI, Court's Order re Additional      |  |

|    | Briefing, Dkt. No. 140 (July 18, 2017)                                     |  |

| AI | MLC v. Micron, Case No. 3:14-cv-03657-SI, Dkt. Nos. 142, 142-1 to 142-     |  |

|    | 5 (July 28, 2017) – Micron Letter Brief re: Order for Additional Claim     |  |

|    | Construction, with Exhibits                                                |  |

|    |                                                                            |  |

AJ *MLC v. Micron*, Case No. 3:14-cv-03657-SI, Dkt. No. 141 (July 28, 2017) – MLC Letter Brief re: Order for Additional Claim Construction

#### I. INTRODUCTION

The '571 patent is generally directed to an "electrically alterable, non-volatile multi-bit memory cell." The specification and prosecution history indicate that the alleged patentability of the claims challenged in this request lies in combining two well-known types of multi-level cell ("MLC") memory devices: read-only, non-volatile memory such as multi-bit ROM, and electrically programmable, volatile memory such as multi-bit DRAM) to create a non-volatile, electrically-alterable MLC device. *See* Ex. A at 2:31-46.

The prior art and evidence described in this request demonstrate that the challenged claims are unpatentable for three simple and independent reasons. First, a prior art Japanese patent application to Kitamura that was not considered during original prosecution had already made the purported combination that formed the basis for alleged patentability. Kitamura describes an electrically programmable, non-volatile, multi-level cell memory device and a programming technique as claimed in the '571 patent. MLC attempted to distinguish Kitamura in an *Inter Partes Review* ("IPR") proceeding by arguing that a D/A converter disclosed as part of the memory apparatus in Kitamura performs only a voltage "converting" function, rather than a voltage "selecting" function as claimed in the '571 patent. However, as demonstrated by three previously unconsidered prior art references submitted with this request, conventional D/A converters that were known long before the '571 patent. Kitamura has never been considered by the PTO in combination with any of these three prior art references. Kitamura combined separately with each such reference therefore raises three independent substantial new questions of patentability.

Second, evidence newly discovered by the Requester in a co-pending litigation including the inventor's notebook and prior sworn deposition testimony—flatly contradicts assertions made by the patent owner to preserve the alleged validity of the '571 patent in IPR. This evidence was never disclosed by the patent owner (an LLC of which the inventor is a current member) to the USPTO despite the fact that it debunks the patent owner's previous statements to the USPTO. The inventor's notebook and prior testimony show that the PTAB's decision denying institution of IPR in view of Kitamura was a direct result of false and misleading statements of the patent owner. This new evidence further supports that Kitamura in

view of the previously unconsidered secondary references present substantial new questions of patentability.

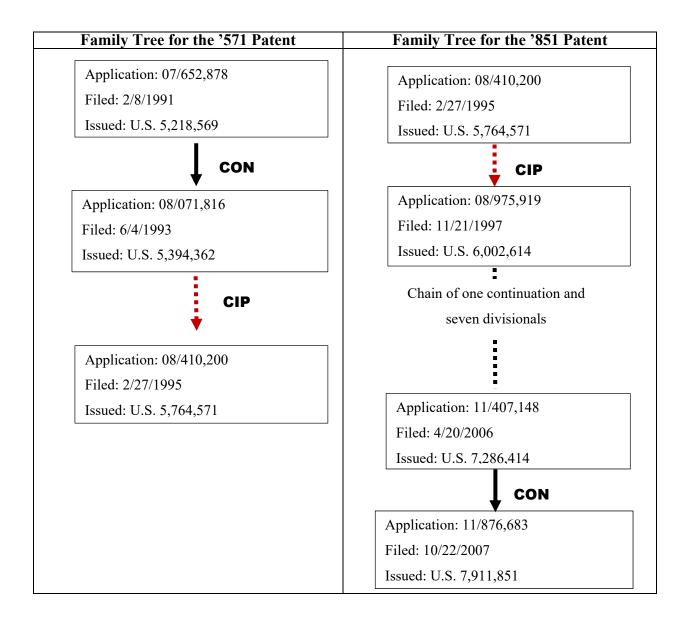

Third, the challenged claims are invalid for obviousness-type double patenting as a result of a related patent prosecuted after the '571 patent issued. Specifically, the challenged claims of the '571 patent are obvious variants of the claims of US Patent No. 7,911,851 ("the '851 patent") (Ex. H). Because the '851 patent expired before the '571 patent and the patentee did not disclaim the term of the '571 patent that extended beyond expiration of the '851 patent, the '571 patent is invalid. The '851 patent was filed after issuance of the '571 patent and was never considered, and could not have been considered, by the USPTO during prosecution of the '571 patent. Nor was it raised or considered in any IPR proceeding because obviousness-type double patenting is not a permissible ground for challenging claims in IPR. Accordingly, obviousness-type double patenting in view of the '851 patent is a substantial new question of patentability that justifies reexamination.

# A. New Prior Art References Teach the Features that were the Basis for Allowance of the '571 Patent

During the prosecution of the application from which the '571 patent issued, the Applicant attempted to distinguish over Examiner-cited prior art by arguing that the Examiner-cited prior art was (i) not electrically alterable, non-volatile memory, (ii) did not disclose the selection of a reference voltage, and (iii) did not disclose comparing the selected reference voltage with the cell voltage and generating a control signal indicating that the cell is correctly programmed. *See* Ex. B at 164-166. The Applicant further indicated that these alleged deficiencies in the prior art were reasons for allowance. *See* Ex. B at 166.

However, as described in more detail in Sections VII to IX, several prior art references clearly disclose the allegedly novel and non-obvious features. Each reason for allowance noted by the Applicant is rendered obvious based on noted combinations of the Kitamura, VLSI Design, Connolly, and Oshita references.

For example, Japanese Patent Application Kokai No. S62-34398 (A) ("Kitamura") (Ex. D) describes the same type of electrically alterable, non-volatile memory as the '571 patent. Ex. D at ¶¶ [02], [06], [14]. The Kitamura application's title is "Non-volatile memory," and the

device described therein uses MLC memory cells allowing a "plurality of bits of digital data to be written to the memory cell transistor of a single element." Ex. D at  $\P$  [14].

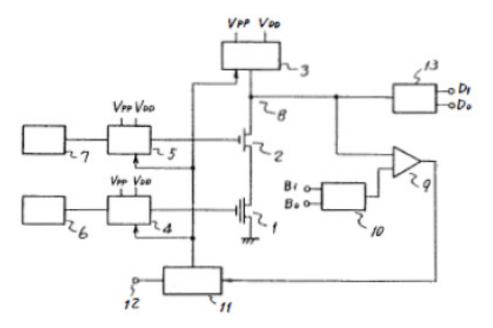

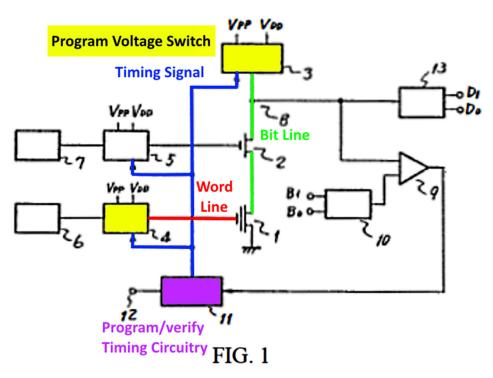

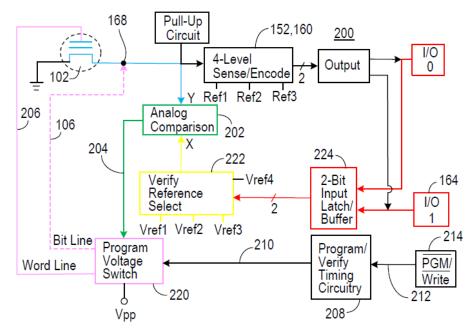

Kitamura's process of writing data also compares a reference voltage to a memory cell voltage to indicate if a memory cell is correctly programmed. Kitamura describes obtaining a reference voltage using "a D/A conversion circuit that converts a plurality of bits of digital signal into an analog signal." *Id.* at ¶ [06]. The resulting analog signal serves as a reference voltage representing the information in "input digital signals B<sub>0</sub> and B<sub>1</sub> to be written" in the memory cell. *Id.* at ¶ [09]. Kitamura determines whether the memory cell has been correctly programmed with a "circuit that compares a read level from a memory cell to the level of the analog signal." *Id.* at ¶¶ [06], [09]. Specifically, a "comparator 9" compares the analog signal from the D/A conversion circuit 10 with the "output voltage (V<sub>0</sub>) of the read point 8" for the memory cell. *Id.* The comparator 9 then triggers the programming process to stop once the correct memory state is reached:

... when the  $V_T$  of the floating gate MOS transistor 1 changes, the output voltage (Vo) of the read point 8 changes as shown in FIG. 3. Meanwhile, the two-bit input digital signals B0 and B1 to be written are converted by the D/A conversion circuit 10 into analog signals, and the [programming] operation is continued with write/read signals while lower than these analog signals, but when the comparator 9 determines that Vo [read from the memory cell] is higher than the analog signals from the D/A conversion circuit 10 [, which represent the information to be stored], the read/write switching signal generation circuit 11 halts the output of the write/read signals and ends the write operation. Therefore, the Vo at this point is a voltage that corresponds to the input digital signals ....

*Id.* at ¶ [09] (emphasis added). Thus, the output of Kitamura's comparator 9 when "V<sub>0</sub> is higher than the analog signals from the D/A conversion circuit 10" serves as a control signal that "ends the write operation" when the correct state of the memory is reached, e.g., when the memory cell reaches the state that "corresponds to the input digital signals" to be written. *Id.* at ¶ [09].

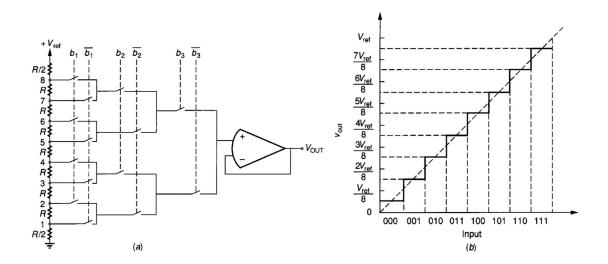

In addition, the VLSI Design, Connolly, and Oshita references each separately disclose selection of a reference signal from a predetermined set of reference voltages. VLSI Design, Connolly, and Oshita each disclose digital-to-analog conversion techniques that involve selecting a voltage from a predetermined set of voltages. Ex. C at ¶¶ 86-91, 109-111, 126-131. Because Kitamura's design includes a "D/A conversion circuit 10," it, would have been obvious to use well-known digital-to-analog conversion techniques, such as those taught by VLSI Design,

Connolly, and Oshita, to implement Kitamura's "D/A conversion circuit 10." *Id.* at ¶¶ 80-83, 90, 117-120, 130-131.

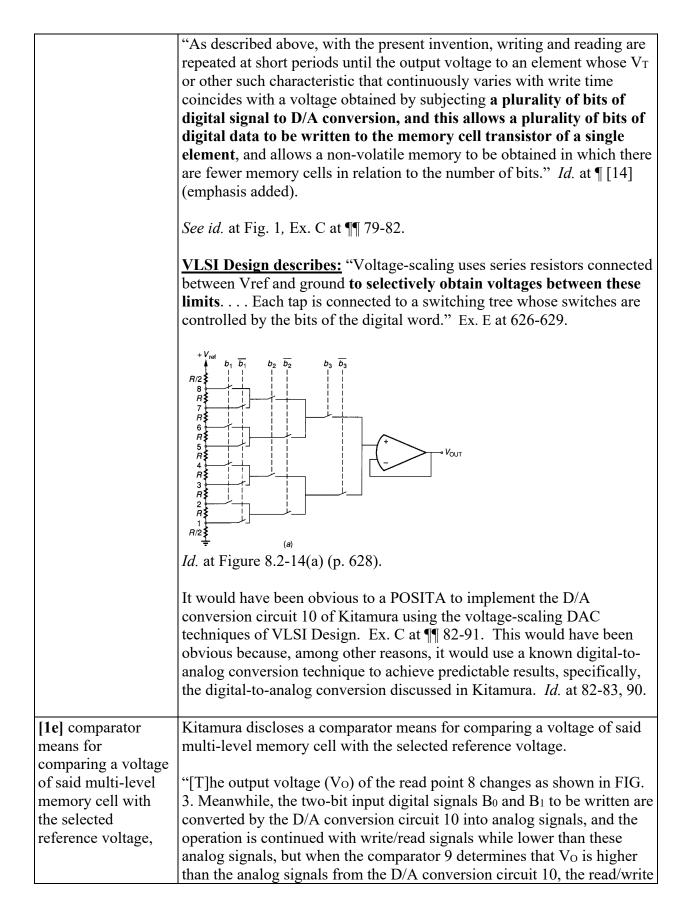

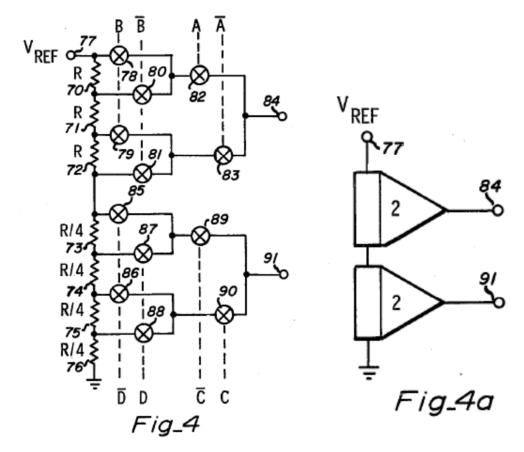

Regarding selecting a reference signal, VLSI Design describes voltage-scaling digital-toanalog converters that use "series resistors connected between Vref and ground to **selectively obtain voltages between these limits**." Ex. E at 626 (emphasis added). Taps between the series resistors have predetermined voltage levels, and "[e]ach tap is connected to a switching tree whose switches are controlled by the bits of the digital word" to be converted by the circuit. *Id.* at 627. Thus, the circuit selects one of the analog voltages at the taps to output based on the digital input to the circuit. *Id.* at 627-629; Ex. C at ¶¶ 83, 86-90.

Connolly also describes selecting a reference voltage from a predetermined set of reference voltages. Connolly describes circuits in which each digital-to-analog converter "includes a resistor ladder and switching tree that permits coupling the output to any single tap on the ladder." Ex. F at Abstract. The act of "coupling the output to any single tap" based on digital input shows that the switching tree selects a voltage (e.g., the voltage at the selected "single tap") from among the set of reference voltages available at the different taps of the resistor ladder. *Id.*; Ex. C at ¶¶ 108-112.

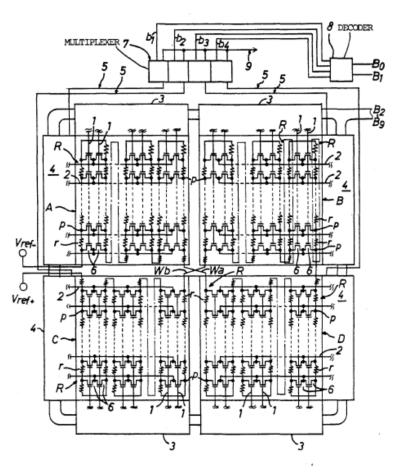

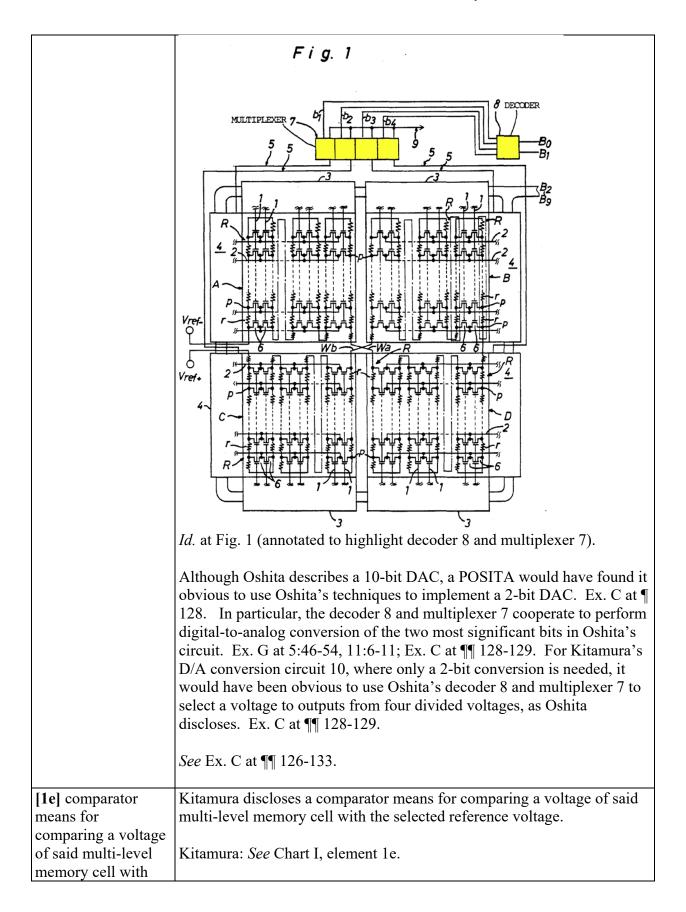

Oshita also describes selecting a reference voltage from a predetermined set of reference voltages. Oshita states that a "digital-to-analog converter of the resistor string type comprises a string of resistors for dividing a reference voltage into a series of divided voltages, and **a switch matrix circuit for selectively generating the divided voltages as an analog signal** when activated in response to a digital signal." Ex. G at Abstract (emphasis added). The "switch matrix circuit" includes a "selection means" or "selector" that responds to a digital signal by "selecting one of the respective [] divided voltages" at the input of the selector "to generate the selected one divided voltage as the analog signal" for output by the circuit. *Id.*; *see also id.* at 3:1-5, claim 1. Oshita uses a multiplexer 7 as the selector, and multiplexers are well-known to perform the function of selecting an output from among various inputs. *Id.* at 5:19-54, Fig. 1; Ex. C at ¶ 127. The multiplexer 7 receives four signals from different sections of the resistor string (e.g., arrays A, B, C, and D), and the multiplexer 7 selects one voltage to output on an external line 9:

the multiplexer 7 cooperates with the decoder 8 responsive to signals appearing on the input lines  $B_0$ ,  $B_1$  to permit electrical connection between the external line 9 and the output line 5 of line decoder 4 for one of the square arrays A, B, C and

# D. This means that the multiplexer 7 cooperates with decoder 8 to select one of the square arrays A to D on a basis of the signals appearing on the input lines $B_0$ , $B_1$ .

Ex. G at 5:46-54 (emphasis added).

Therefore, combinations of Kitamura, VLSI Design, Connolly, and Oshita, which were not considered by the Examiner during original prosecution, raise substantial new questions of patentability with respect to the claims of the '571 patent, because the combinations of these references render obvious all of the claim features which appear to have been responsible for allowance.

# **B.** New Prior Art References Teach the Features Cited as the Basis for Not Instituting *Inter Partes* Review of the '571 Patent

The '571 patent was subject to two petitions for *inter partes* review (IPR) that were substantively identical. The PTAB declined to institute trial on the basis that the references in the asserted IPR grounds allegedly did not teach or suggest a "reference voltage selecting means" to select from "reference voltages." Ex. J (Denying Institution of *Inter Partes* Review) at 9-10.'

The PTAB's denial of institution of IPR was based on a finding that is contradicted by evidence that was not submitted by the patent owner and was not considered by the PTAB, but has now been discovered by the requester and is described and submitted in Appendix A, which is subject to a protective order. Appendix A is being submitted concurrently with this request and under seal pursuant to MPEP § 724.02. This new evidence soundly refutes arguments made by the Patent Owner in the IPR and reasons that the PTAB gave for not instituting IPR in view of the Kitamura reference.

Moreover, the VLSI Design, Connolly, and Oshita references—which were not part of the asserted IPR grounds—describe the exact features that were allegedly not taught in the IPR grounds. As noted above, VLSI Design and Connolly each separately disclose resistor networks to generate reference voltages, and switching trees to select from among the voltages. Ex. E (VLSI Design) at 626-629; Ex. F (Connolly) at Abstract. Further, Oshita describes a "selection means" including a multiplexer 7, which has the purpose of selecting from among the "divided voltages" from a resistor string. Ex. G (Oshita) at Abstract, 3:1-5, 5:19-54.

Thus, VLSI Design, Connolly, and Oshita, in combination with Kitamura as discussed below, raise substantial new questions of patentability with respect to the claims of the '571

patent, because VLSI Design, Connolly, and Oshita each teaches the "reference voltage selecting means" feature that was the basis for not instituting IPR of the '571 patent.

# C. New Reference U.S. Patent No. 7,911,851 Shows that the Claims of the '571 Patent Are Invalid for Obviousness-type Double Patenting

The original prosecution of the '571 patent did not consider U.S. Patent No. 7,911,851 ("the '851 patent"), which renders the claims of the '571 patent invalid for obviousness-type double patenting. The '851 patent has the same inventor as the '571 patent, claims the same or patentably indistinct technology as the '571 patent, and expired before the '571 patent. Because the term of the '571 patent unlawfully extends beyond the full statutory term of the '851 patent for the same or patentably indistinct technology, the '571 patent is invalid for obviousness-type double patenting.

The '571 patent improperly prevents the public from using the technology claimed in the earlier-expiring '851 patent—technology that should have been freely available to the public after the '851 patent expired. This is precisely the scenario that the doctrine of obviousness-type double patenting is intended to prevent:

The doctrine of double patenting seeks to prevent the unjustified extension of patent exclusivity beyond the term of a patent. The public policy behind this doctrine is that:

The public should . . . be able to act on the assumption that upon the expiration of the patent it will be free to use not only the invention claimed in the patent but also modifications or variants which would have been obvious to those of ordinary skill in the art at the time the invention was made, taking into account the skill in the art and prior art other than the invention claimed in the issued patent.

*In re Zickendraht,* 319 F.2d 225, 232, 138 USPQ 22, 27 (CCPA 1963) (Rich, J., concurring). Double patenting results when the right to exclude granted by a first patent is unjustly extended by the grant of a later issued patent or patents. *In re Van Ornum,* 686 F.2d 937, 214 USPQ 761 (CCPA 1982). Note that in *Gilead Sciences, Inc. v. Natco Pharma Ltd.,* 753 F.3d 1208, 110 USPQ2d 1551 (Fed. Cir. 2014), the court found an earlier-expiring patent, which was issued after the later-expiring patent, may be used to invalidate the later-expiring patent.

MPEP § 804 (emphasis added).

As discussed in detail below, the claims of the '851 patent teach or render obvious each of the features of claims 1, 9, 12, 30, 42, and 45 of the '571 patent. Therefore, the expiration of

the '851 patent before the '571 patent, and the patent owner's failure to disclaim the improper term of the '571 patent, renders these claims of the '571 patent invalid under obviousness-type double patenting, as an unlawful extension of patent rights.

#### **D.** New Evidence in Appendix A Supports Re-Examination

Appendix A has been filed under seal pursuant to MPEP § 724.02. The documents in this appendix provide additional reasons that support re-examination. The documents contain information subject to protective order that was not previously considered by the USPTO.

The references discussed in this request combine as reflected in the following table to render claims of the '571 patent obvious and invalid for obviousness-type double patenting. Each basis for rejection includes at least one reference that was not considered by the Examiner and was not included any previously-asserted IPR grounds.

| Claims                   | <b>Basis for Rejection</b>                   |

|--------------------------|----------------------------------------------|

| 1, 9, 12, 30, 42, and 45 | Obviousness in view of Kitamura in view of   |

|                          | VLSI Design                                  |

| 1, 9, 12, 30, 42, and 45 | Obviousness in view of Kitamura in view of   |

|                          | Connolly                                     |

| 1, 9, 12, 30, 42, and 45 | Obviousness in view of Kitamura in view of   |

|                          | Oshita                                       |

| 1, 9, 12, 30, 42, and 45 | Obviousness-type double patenting in view of |

|                          | claims 3, 7, and 14 of the '851 patent       |

#### II. CLAIMS FOR WHICH REEXAMINATION IS REQUESTED

Reexamination is requested for each of claims 1, 9, 12, 30, 42, and 45 of the '571 patent. As explained in greater detail below, prior art that was not considered by the USPTO during prosecution of the '571 patent renders obvious all features of claims 1, 9, 12, 30, 42, and 45 of the '571 patent. Claims 1, 9, 12, 30, 42, and 45 are also invalid for non-statutory obviousness-type double patenting in view of U.S. Patent No. 7,911,851 (Ex. H), which was not considered by the USPTO during prosecution of the '571 patent.

Consequently, reexamination is hereby requested for claims 1, 9, 12, 30, 42, and 45 of the '571 patent in view of the patents and publications discussed below. A copy of the '571 patent is attached as Ex. A of this document.

# III. IDENTIFICATION OF PATENTS AND PRINTED PUBLICATIONS PRESENTED TO SHOW SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY

- Certified Translation of Japanese Patent Application Kokai No. S62-34398 (A) ("Kitamura") (Ex. D); the Japanese-language version of Kitamura is attached as Ex. I;

- Excerpts from "VLSI Design Techniques for Analog and Digital Circuits," by Geiger, Allen, and Strader, McGraw-Hill, 1989 ("VLSI Design") (Ex. E)

- 3. U.S. Patent No. 4,198,622 to Connolly ("Connolly") (Ex. F)

- 4. U.S. Patent No. 5,014,054 to Oshita ("Oshita") (Ex. G)

- 5. U.S. Patent No. 7,911,851 to Banks ("the '851 patent") (Ex. H)

The references at Exhibits D-H were not named on the face of the '571 patent and were not documented as being considered by the Examiner during ex parte prosecution of the '571 patent.

Prior IPR proceedings considered an invalidity ground of obviousness in view of Kitamura alone. Ex. J (IPR Institution Decision) at 7-10. VLSI Design was included as an exhibit in the IPR petition, and was discussed in a declaration by Dr. R. Jacob Baker in support of the IPR petition. However, the PTAB specifically noted that VLSI Design and other textbooks cited in the declaration were not part of the asserted invalidity grounds:

Dr. Baker goes on to further interpret Kitamura . . . , citing additional references [including VLSI Design], but those additional references do not form part of the obviousness ground, and are not cited in the Petition."

Ex. K (IPR Rehearing Decision) at 6. Moreover, Appendix A provides important evidence that contradicts the patent owner's arguments to the PTAB in IPR regarding the teachings of Kitamura and certain elements of the challenged patent claims, and contradicts the PTAB's findings about Kitamura in response to those arguments. This evidence was not submitted by the patent owner and therefore has not yet been considered by the USPTO. Thus, the combination of Kitamura and VLSI design represents a substantial new question of patentability that was not considered in the IPR proceedings.

## IV. CO-PENDING PROSECUTION AND LITIGATION

Requester is aware of the following civil actions involving the '571 patent: *MLC Intellectual Property, LLC v. Micron Technology, Inc.*, No. 3:14-cv-03657 (N.D. Cal. August 12, 2014); *BTG International Inc. v. Apple Inc. et al*, No. 2:09-cv-00223 (E.D. Tex. July 20, 2009); *BTG International Inc. v. Samsung Electronics Co. LTD et al*, No. 2:08-cv-00482 (E.D. Tex. December 29, 2008); and *MLC Flash Memory Devices and Products Containing Same*, Inv. No. 337-TA-683, (January 19, 2011) (Completed).

As noted above, the '571 patent was the subject of two petitions for IPR, IPR2015-00504, filed December 24, 2014, and IPR2015-00517, filed on December 30, 2014. The PTAB did not institute trial for either of the IPR petitions.

Requester is not aware of any previous disclaimers or reexamination certificates for the '571 patent. Requester is not aware of any pending prosecution concerning the '571 patent.

#### V. THE ORIGINAL PROSECUTION HISTORY

U.S. Patent No. 5,764,571 was filed on February 27, 1995, as U.S. Patent Appl. Ser. No. 08/410,200 ("the '200 application"), and issued on June 9, 1998. *See* Ex. A. The '571 patent claims to be a divisional of U.S. Patent No. 5,394,362 filed on June 4, 1993, which, in turn, claims to be continuation of U.S. Patent No. 5,218,569 filed on February 8, 1991. *See id*.

The USPTO issued an office action on December 17, 1996, rejecting or objecting to all of the original twenty-three claims of the '200 application over Suzuki (U.S. Patent No. 4,809,224) as being "drawn to a basic multi-level memory with comparator as shown by Suzuki et al." *See* Ex. B (Prosecution History) at 107-08.

In response, the Applicant amended certain claims to add limitations directed to selecting a reference voltage for use in comparing to a signal representing the current state of the memory cell. *See* Ex. B at pages 144-167. The Applicant then argued that it "is apparent that Suzuki neither teaches nor suggests a multi-level memory device having the aforementioned features of Claim 1. Note, for example, that Suzuki discloses a conventional ROM which is not electrically alterable . . . . Further, Suzuki lacks any suggestion whatsoever of the reference voltage selecting means and comparator means, both as now defined." Ex. B at 165.

The USPTO subsequently allowed all pending claims in a Notice of Allowance, which did not include any reasons for allowance or an examiner's amendment. *See* Ex. B at 169. Thus, the above-described amendments to the independent claims appear to have led directly to and been the basis for the Examiner's allowance. As described above, and as shown in more detail in the claim charts below, the Kitamura, VLSI Design, Connolly, and Oshita references render obvious the claim elements that the patent owner relied upon to distinguish the claims in the '571 patent over the prior art.

#### VI. PRIOR IPR PETITIONS

A petition for *inter partes* review (IPR) of the '571 patent was filed on December 24, 2014. A second petition for IPR, which was essentially a copy of the first petition, was filed on December 30, 2017. These petitions asserted invalidity on two separate grounds: (1) obviousness over Kitamura alone, and (2) obviousness over U.S. Patent No. 5,172,338 ("Mehrotra") alone.

In a Patent Owner Preliminary Response (POPR), the patent owner argued that the prior art failed to describe "reference voltage selection means." Ex. L at 4-15. The patent owner further argued that the petition did not demonstrate that Kitamura's "digital-to-analog conversion circuit makes a selection of any type, let alone a selection of a plurality of reference voltages." *Id.* at 6. The patent owner also alleged that there was "no evidence or reason to believe that the conversion of digital input signals to an analog signal involves a 'selection' of 'one of a plurality of reference voltages." *Id.* at 7.

In a Decision dated July 20, 2015, the PTAB declined to institute IPR of the '571 patent. Ex. J at 10-11. The PTAB stated that "[w]e are not persuaded that Kitamura teaches or suggests the selection of one of a plurality of reference voltages in accordance with the input information,

per the challenged claims." Ex. J at 10. In a Decision denying a request for rehearing, the PTAB further noted that additional references relied upon to further interpret Kitamura "do not form part of the obviousness ground, and are not cited in the Petition." Ex. K at 4-5. In denying rehearing, the PTAB offered the following clarification:

The cited comment in the Decision ("[i]n addition, the Petitions fail to provide any rationale for why Kitamura's disclosure of D/A conversion renders the selection of a reference voltage or signal obvious," Dec. 10; Reh'g Req. 15) was made to note that Petitioner was relying on the same or equivalent structures in both, and was not relying on the obviousness of one over the other. *One example of this would have been if Petitioner had cited a structure in Kitamura, acknowledged that it was not the same, but argued that the equivalent structure disclosed in the '571 Patent would have been obvious in view of the structure in Kitamura; i.e., pointing out that one would have been an obvious variation of the other. Petitioner had not done this, as we merely noted.*

Ex. K at 8 (emphasis added). In other words, the PTAB declined to find that the D/A conversion circuit of Kitamura "must" perform a selection or must contain the same selection circuit as claimed in the '571 patent, but declined to address whether the D/A conversion circuit of Kitamura rendered obvious the selection function and circuit of the '571 patent, finding that this issue was not properly raised by the petition.

As shown in this request, the newly-presented prior art addresses the limitations alleged to be lacking in references previously presented, including the alleged deficiency of the petitions for IPR. While acknowledging that Kitamura does not specifically describe the details of the internal operation of Kitamura's D/A conversion circuit 10, this request demonstrates that Kitamura's teaching to use a D/A conversion circuit, in combination with references that describe in greater detail conventional digital-to-analog conversion techniques and circuits that include selecting one of a plurality of reference voltages, renders obvious the claims of the '571 patent. VLSI Design, Connolly, and Oshita each describe the feature of a "reference voltage selection means." In particular, each of these references describes digital-to-analog conversion techniques that unambiguously involve selecting one of a plurality of reference voltages, the very feature that was found to be lacking in the references used in the grounds of the prior IPR petitions. *See* Ex. E at 626-628 (DAC circuit "to selectively obtain voltages" from taps representing different voltages); Ex. F at Abstract (DAC including "a resistor ladder and switching tree that permits coupling the output to any single tap on the ladder"); Ex. G at claim 1 (DAC including "selection means responsive to the digital signal for selecting one of the respective divided voltages . . . as the analog [output] signal"); Ex. C at ¶¶ 86-91, 109-111, 126-131.

And as set forth in Appendix A, inventor Gerald Banks' prior testimony and engineering notebook further support institution of this ex parte reexamination request and show that the references present a substantial new question of patentability. Mr. Banks' testimony and notebook were not submitted to the PTAB by the patent owner during IPR and only recently became available to Requester through discovery in co-pending litigation. This evidence therefore has not previously been considered by the Patent Office.

Finally, as an additional difference from the Petitions for IPR, this request raises the issue of obviousness-type double patenting over the '851 patent as a substantial new question of patentability. Obviousness-type double patenting was not raised in the petitions for IPR, nor could the issue have been raised there because, in IPR, claims may be challenged "only on a ground that could be raised *under section 102 or 103*..." 35 U.S.C. § 311 (emphasis added). Thus, the issue of obviousness-type double-patenting in view of the '851 patent, which was not considered by the examiner during prosecution of the '571 patent, is a substantial new question of patentability that justifies reexamination.

# VII. THE REFERENCES RELIED UPON HEREIN PROVIDE NEW, NON-CUMULATIVE TECHNICAL TEACHINGS

VLSI Design (Ex. E), Connolly (Ex. F), and Oshita (Ex. G) provide new technical teachings and present substantial new questions of patentability. Specifically, each reference teaches features that the patent owner relied on to distinguish prior art and which the PTAB relied on to decline institution of prior-filed petitions for IPR.

#### A. VLSI Design Provides New, Non-Cumulative Technical Teachings

VLSI Design qualifies as prior art under 35 U.S.C. § 102(b) because it was published and publicly available on or before December 8, 1989, which is more than one year before the earliest possible effective filing date of the '571 patent (i.e., February 8, 1991). VLSI Design describes techniques and circuits for digital-to-analog conversion, including voltage-scaling D/A

converter circuits. Ex. E at 615, 626-629. The voltage-scaling circuits use "series resistors connected between Vref and ground to selectively obtain voltages between these limits." *Id.* at 626. Taps between resistors are "connected to a switching tree whose switches are controlled by the bits of the digital word," and the switching tree selects one of the taps to provide an output voltage. *Id.* at 627.

VLSI Design was not before the Examiner during prosecution of the '571 patent. VLSI Design was included as an exhibit in the prior IPR petitions, but was not part of the asserted invalidity grounds in the IPR petitions. VLSI Design presents new, non-cumulative teachings that were not previously considered by the Patent Office and therefore presents a substantial new question of patentability with respect to the claims of the '571 patent. Specifically, VLSI Design clearly describes features of the independent claims that led to allowance of the application and the decision not to institute IPR. For example, VLSI Design teaches the feature of a "reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with ... input information" as recited in claim 1 the '571 patent as well as similar "selecting" features of claims 9, 12, 30, 42, and 45, which the patent owner relied upon to distinguish the prior art in original prosecution and during the IPR proceedings. *See* Ex. C at ¶ 86-91; Ex. L at 4-10.

#### **B.** Connolly Provides New, Non-Cumulative Technical Teachings

United States Patent No. 4,198,622 to Connolly qualifies as prior art under 35 U.S.C. § 102(b) because it issued on April 15, 1980, which is more than one year before the earliest possible effective filing date of the '571 patent (i.e., February 8, 1991). The Connolly reference describes digital-to-analog conversion circuits and techniques in which a "converter includes a resistor ladder and switching tree that permits coupling the output to any single tap on the ladder." Ex. F at Abstract. A different, predetermined voltage is present at each tap on the resistor ladder. Ex. 2:49-57, 3:57-4:23; Ex. C at ¶¶ 109-111. By "coupling the output to any single tap," the switching tree performs a selection of a voltage—that is, the switching tree selects a voltage to output from among the predetermined set of voltages present at the taps of the resistance ladder. *Id*.

Connolly was not before the Examiner during prosecution of the '571 patent and was not considered by the PTAB in the prior IPR proceedings. Connolly thus presents new, non-

cumulative teachings that were not previously considered by the Patent Office and therefore presents a substantial new question of patentability with respect to claims of the '571 patent. Specifically, Connolly clearly describes features of the independent claims that led to allowance of the application and the decision not to institute IPR. For example, Connolly teaches the feature of a "reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with . . . input information" as recited in claim 1 the '571 patent as well as similar "selecting" features of claims 9, 12, 30, 42, and 45, which the patent owner relied upon to distinguish the prior art in original prosecution and IPR proceedings. *See* Ex. C at ¶¶ 126-131; Ex. L at 4-10.

#### C. Oshita Provides New, Non-Cumulative Technical Teachings

United States Patent No. 5,014,054 to Oshita qualifies as prior art under 35 U.S.C. § 102(e) because it was filed on July 22, 1988, which is before the earliest possible effective filing date of the '571 patent (i.e., February 8, 1991). The Oshita reference describes a "digital-to-analog converter of the resistor string type" that includes "a string of resistors for dividing a reference voltage into a series of divided voltages, and a switch matrix circuit for selectively generating the divided voltages as an analog signal when activated in response to a digital signal." Ex. G at Abstract (emphasis added). The "switch matrix circuit" includes a "selection means" that responds to a digital signal by "selecting one of the respective [] divided voltages" at the input of the selector "to generate the selected one divided voltage as the analog signal" for output by the circuit. *Id.* at 3:1-5, claim 1.

Oshita was not before the Examiner during prosecution of the '571 patent and was not considered by the PTAB in the prior IPR proceedings. Oshita thus presents new, non-cumulative teachings that were not previously considered and therefore presents a substantial new question of patentability with respect to claims of the '571 patent. Specifically, Oshita clearly describes features of the independent claims that led to allowance of the application and the decision not to institute IPR. For example, Oshita teaches the feature of a "reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with . . . input information" as recited in claim 1 the '571 patent as well as similar "selecting" features of claims 9, 12, 30, 42, and 45, which the patent owner relied upon to distinguish the prior art in original prosecution and IPR proceedings. *See* Ex. C at ¶¶ 126-131; Ex. L at 4-10.

#### VIII. ADDITIONAL PRIOR ART AND NEWLY SUBMITTED EVIDENCE

Requester submits that substantial new questions of patentability are raised by the combination of (i) Kitamura (which was discussed in prior IPR proceedings but not original prosecution of the '571 patent) with (ii) the new references in Exhibits E-G (which were not before the examiner during prosecution and were not part of the invalidity grounds of the prior IPR proceedings). Requester further notes that inventor testimony and the inventor's notebook, which contradict the patent owner's arguments to the PTAB regarding Kitamura and elements of the challenged claims, was not disclosed by the patent owner and has never been considered by the USPTO. Kitamura, in combination with the new references and in view of this newly submitted evidence, presents a substantial new question of patentability. In addition, according to MPEP 2242(II)(A), "reliance on old art does not necessarily preclude the existence of a substantial new question of patentability."

Kitamura qualifies as prior art under 35 U.S.C. § 102(b) because it published on February 14, 1987, which is more than one year before the earliest priority date of the '571 patent (February 8, 1991). Kitamura describes a storage device with non-volatile memory cells allowing a "plurality of bits of digital data to be written to the memory cell transistor of a single element." Ex. D at ¶ [14]. Kitamura determines whether a memory cell has been correctly programmed with a "circuit that compares a read level from a memory cell to the level of the analog signal" representing the desired memory state. *Id.* at ¶¶ [06], [09]. Specifically, a "comparator 9" compares the analog signal from a D/A conversion circuit 10 with the "output voltage (Vo) of the read point 8" for the memory cell, and the comparator 9. *Id.*

Kitamura was not before the Examiner during prosecution of the '571 patent. The prior IPR proceedings asserted invalidity of the '571 patent on the basis of obviousness over Kitamura alone.

Kitamura clearly describes various features of the independent claims that led to the allowance of the application. For example, Kitamura teaches features of 1, 9, 12, 30, 42, and 45 including an electrically alterable, non-volatile memory having more than two memory states, as well as comparing a selected reference voltage with a memory cell voltage and generating a control signal indicating that the cell is correctly programmed, which the patent owner relied upon to distinguish the prior art during original prosecution. *See* Ex. B at 164-166.

Although the prior IPR petitions asserted a ground based on obviousness over Kitamura alone, they did not include grounds based on combinations of Kitamura with any other reference. *See* Ex. J (IPR Institution Decision) at 7-10. When combined with other references that were not before the examiner and were not before the PTAB, the teachings of Kitamura in combination with these references present a substantial new question of patentability with respect to claims 1, 9, 12, 30, 42, and 45 of the '571 patent.

Additionally, Kitamura provides a substantial new question of patentability when understood in light of the new evidence in Appendix A. While Appendix A does not recite new prior art references, the new evidence contained within nevertheless compels a different and more expansive interpretation of the '571 patent and the similarity with the Kitamura reference. In particular, Appendix A directly contradicts statements by the Patent Owner and reasons that the PTAB gave for denying institution of IPR in view of Kitamura. The new evidence in Appendix A shows that the PTAB's interpretations of the '571 patent and the Kitamura reference were incorrect and incomplete, and the Challenged Claim are invalid over Kitamura and other references as discussed below.

# IX. SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY NOT RAISED DURING PROSECUTION OF THE '571 PATENT

Four substantial new questions of patentability (SNQs) are described in detail below: three based on obviousness under 35 U.S.C. § 103 and one based on obviousness-type double patenting. Each SNQ demonstrates that each of claims 1, 9, 12, 30, 42, and 45 is invalid and should not have been allowed by the USPTO.

With respect to SNQ's 1-3, a person of ordinary skill in the art (POSITA) would have had numerous reasons to combine Kitamura with VLSI Design, Connolly, or Oshita. As discussed further below, Kitamura's memory system uses a D/A conversion circuit 10. *See* Ex. D at ¶¶ [07]-[09]. However, since digital-to-analog converters were well-known, ubiquitous, devices, Kitamura does not fully describe the internal structure and operation of this element. *See id.* at ¶¶ [09]-[11]; Ex. C at ¶ 82. As a result, a POSITA implementing Kitamura's design would have been motivated to implement the D/A conversion circuit 10 using well-known techniques for digital-to-analog conversion as taught in other documents. Ex. C at ¶ 82. VLSI Design, Connolly, and Oshita each independently disclose digital-to-analog conversion techniques that a POSITA would have found obvious to use to implement Kitamura's D/A conversion circuit 10. *Id.* at ¶¶ 83-85, 117-122, 130-132. The reason for the combination is simple: Kitamura's circuit requires a DAC (e.g., D/A conversion circuit 10) and VLSI Design, Connolly, and Oshita each teach a DAC that can perform the D/A conversion function needed in Kitamura's circuit. *Id.*

First, combining any of VLSI Design, Connolly, and Oshita with Kitamura would have been obvious as a combination of prior art elements according to known methods to yield predictable results. See MPEP 2143(I)(A); KSR Intl. Co. v. Teleflex Inc, 550 U.S. 398, 417 ("when a patent simply arranges old elements with each performing the same function it had been known to perform and yields no more than one would expect from such an arrangement, the combination is obvious") (quotation omitted); id. at 416 ("The combination of familiar elements according to known methods is likely to be obvious when it does no more than yield predictable results."). As discussed below and shown in the claim charts, Kitamura discloses all elements of the Challenged Claims except the "reference voltage selecting means" or "selecting device," but VLSI Design, Connolly, and Oshita each supply this final element in the form of a DAC. Ex. C at ¶¶ 68-86, 106-107, 124-125. A POSITA would have used the DAC techniques of VLSI Design, Connolly, or Oshita in Kitamura's D/A conversion circuit 10, with the D/A conversion circuit 10 performing the same function that VLSI Design, Connolly, and Oshita disclose. Ex. C at ¶¶ 90-91, 117-122, 130-132. The DAC from VLSI Design, Connolly, or Oshita would have produced the same predictable results that a DAC is known to produce: output of an analog voltage selected from a predetermined set of voltages in accordance with the digital input to the DAC. Id. at ¶¶ 76, 83, 118-119, 130.

Second, combining any of VLSI Design, Connolly, and Oshita with Kitamura would have been obvious as a simple substitution of one known element for another to obtain predictable results. *See* MPEP 2143(I)(B); *KSR*, 550 U.S. at 417 (discussing obviousness of "the simple substitution of one known element for another" and the importance of asking "whether the improvement is more than the predictable use of prior art elements according to their established functions"). VLSI Design, Connolly, and Oshita each describe a DAC that is equivalent to the "reference voltage selecting means" or "selecting device" of the Challenged Claims—each DAC selects one of a predetermined plurality of analog signals to output. Ex. C at ¶¶ 86-91, 109-111, 126-131. When substituted for Kitamura's D/A conversion circuity, the

DAC of any of VLSI Design, Connolly, and Oshita would perform in exactly the same manner, producing the same predictable result of outputting the selected voltage corresponding to the digital input to the DAC. *Id.* at ¶¶ 76, 83, 118-119, 130. The operation of Kitamura's overall circuit would not be changed due to the substitution, since this is the same function as Kitamura's D/A conversion circuit 10 performs. *Id.* at ¶¶ 86-91, 109-111, 126-131.

Third, combining any of VLSI Design, Connolly, and Oshita with Kitamura would have been obvious as a use of a known technique to improve a similar device in the same way. *See* MPEP 2143(I)(C); *KSR*, 550 U.S. at 417 ("if a technique has been used to improve one device, and a POSITA in the art would recognize that it would improve similar devices in the same way, using the technique is obvious unless its actual application is beyond his or her skill."). A POSITA would have recognized that VLSI Design, Connolly, and Oshita each teach DAC techniques that can improve Kitamura's D/A conversion circuit 10 in the same way those techniques improve other DACs. For example, a POSITA would have recognized that the techniques of VLSI Design, Connolly, and Oshita improve Kitamura's D/A conversion circuit 10 through simple circuit techniques that are easy to manufacture; use simple, well-known circuit elements; and provide versatility to meet many different circuit configurations. Ex. C at ¶¶ 84, 118-119, 130.

Fourth, combining any of VLSI Design, Connolly, and Oshita with Kitamura would have been obvious as an application of a known technique to a known device ready for improvement to yield predictable results. *See* MPEP 2143(I)(D); *KSR*, 550 U.S. at 417 (discussing obviousness of "application of a known technique to a piece of prior art ready for the improvement"). In particular, Kitamura's device presents a circuit that is ready for application of the DAC techniques of VLSI Design, Connolly, and Oshita. Ex. C at ¶¶ 68-86, 106-107, 124-125. A POSITA would have recognized that these DAC techniques would have improved Kitamura by providing a reliable and effective design that would perform the functions that the D/A conversion circuit 10 is designed to perform. Ex. C at ¶¶ 76, 83, 118-119, 130.

Fifth, design incentives and market forces would also have prompted a POSITA to combine any of VLSI Design, Connolly, and Oshita with Kitamura, since their techniques represent a variation that is predictable to one of ordinary skill in the art. *See* MPEP 2143(I)(F); *KSR*, 550 U.S. at 417 ("When a work is available in one field of endeavor, design incentives and other market forces can prompt variations of it, either in the same field or a different one. If a

POSITA can implement a predictable variation, § 103 likely bars its patentability.") A POSITA implementing Kitamura's circuit would have had an incentive to minimize cost and manufacturing complexity. As a result, a POSITA would have been motivated to use the DAC techniques of VLSI Design, Connolly, and Oshita to implement the D/A conversion circuit 10 of Kitamura, because these DAC techniques use very simple parts and a small number of parts. Ex. C at ¶¶ 84, 117-119, 130. This would have been desirable to facilitate manufacturing and minimize IC chip area, and thus minimize cost, while still providing the D/A conversion needed in Kitamura's circuit. *Id*.

The circuits taught by VLSI Design, Connolly, and Oshita are each consistent with the structure and function that Kitamura describes for the D/A conversion circuit 10. Kitamura mentions that the D/A conversion circuit 10 has "a voltage dividing element and a reference voltage supply." Ex. D at ¶ [11]. VLSI Design, Connolly, and Oshita each have a corresponding resistor string that serves as a "voltage dividing element" connected to a "reference voltage supply," demonstrating that each of these DAC designs generates voltages in the same way Kitamura contemplates. *See* Ex. E at 627 ("resistor string"); Ex. F at Abstract ("resistor ladder"); Ex. G at Abstract ("string of resistors for dividing a reference voltage").

In addition to the reasons for combination discussed above, a POSITA would have been motivated to combine the references as discussed in SNQs 1-3 because of the specific teachings and advantages disclosed in VLSI Design, Connolly, and Oshita. *See* MPEP 2143(I)(G). These additional reasons are discussed in more detail in the respective sections below.

The new evidence in Appendix A is relevant to each of SNQs 1-3 and further demonstrates that each combination of references presents a substantial new issue of patentability not previously before the USPTO.

#### A. Overview of the '571 Patent Claims, Key Claim Constructions

Claims 1, 9, 12, and 30 of the '571 patent vary slightly, but all essentially claim a device with four main components and functions: (1) an electrically alterable, non-volatile memory, (2) reference voltage selecting, (3) memory cell programming, and (4) comparing. Method claims 42 and 45 mirror these claim requirements, albeit using modified language. Claim 1 is exemplary:

1. A multi-level memory device comprising:

an electrically alterable non-volatile multi-level memory cell for storing input information in a corresponding one of  $K^n$  predetermined memory states of said multi-level memory cell, where K is a base of a predetermined number system, n is a number of bits stored per cell, and  $K^n > 2$ ;

memory cell programming means for programming said multi-level memory cell in accordance with said input information;

reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with said input information, each of said reference voltages corresponding to a different one of said predetermined memory states; and

comparator means for comparing a voltage of said multi-level memory cell with the selected reference voltage, said comparator means further generating a control signal indicating whether the state of said multi-level memory cell is the state corresponding to said input information.

When compared to claims 9, 12, and 30, it is clear that claim 1 contains similar

requirements, but claim 1 is written in means-plus-function form while claims 9, 12, and 30 are

not. Claim 9 is exemplary:

9. Multi-level memory apparatus, comprising:

an electrically alterable non-volatile memory cell having more than two predetermined memory states;

a selecting device which selects one of a plurality of predetermined reference signals in accordance with information indicating a memory state to which said memory cell is to be programmed, each reference signal corresponding to a different memory state of said memory cell;

a programming signal source which applies a programming signal to said memory cell; and

a comparator which compares a signal corresponding to the state of said memory cell with the selected reference signal to verify whether said memory cell is programmed to the state indicated by said information.

Means-plus-function claiming is controlled by 35 U.S.C. §  $112 \ \fill 6$ , which provides that "[a]n element in a claim for a combination may be expressed as a means or step for performing a specified function without the recital of structure, material, or acts in support thereof, and such claim shall be construed to cover the corresponding structure, material, or acts described in the

specification and equivalents thereof."  $35 \text{ U.S.C. } 112 \text{ 6. "If a claim limitation recites a term$ and associated functional language, the examiner should determine whether the claim limitationinvokes <math>35 U.S.C. 112(f) or pre-AIA 35 U.S.C. 112, sixth paragraph." MPEP 2181(I). "The claim limitation is presumed to invoke 35 U.S.C. 112(f) or pre-AIA 35 U.S.C. 112, sixth paragraph when it explicitly uses the term 'means' or 'step' and includes functional language." *Id.* When using the means-plus-function format, "[t]he applicant must describe in the patent specification some structure which performs the specified function." *Valmont Industries, Inc. v. Reinke Manufacturing Co., Inc.*, 983 F.2d 1039, 1042 (Fed. Cir. 1993). "The first step in construing such a limitation is a determination of the function of the means-plus-function limitation. The next step is to determine the corresponding structure described in the specification and equivalents thereof." *Medtronic, Inc. v. Advanced Cardiovascular Sys., Inc.*, 248 F.3d 1303, 1311 (Fed. Cir. 2001) (internal citations omitted). As is described in more detail below, the '571 patent's use of mean-plus-function language in claim 1 invokes specific corresponding structure that is obvious in view of the references relied upon herein.

Moreover, three groups of terms within these four main required components and functions require additional attention.

1. The "reference voltage selecting" terms. The "reference voltage selecting" term takes on three forms across claims 1, 9, 12, 30, 42, and 45: (1) "reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with said input information" in claim 1; (2) "a selecting device which selects one of a plurality of [predetermined] reference signals in accordance with information indicating a memory state to which said memory cell is to be programmed" in claims 9, 12, and 30<sup>1</sup>; and (3) "selecting one of a plurality of reference signals in accordance with information indicating a memory state to which said memory cell is to be programmed" in claims 42 and 45. While each of these three "reference voltage selecting" terms require the substantially similar analysis, each will be addressed in turn to address their slight differences.

<sup>&</sup>lt;sup>1</sup> This phrase appears in identical form in claim 9, 12, and 30, except claim 9 further specifies that the reference signals are "predetermined."

2. The "reference voltages/signals" terms. The "reference voltages/signals" terms, as can be seen in exemplary claims 1 and 9 above, occur throughout the claims across various components. A "reference signal" is broader than and includes a "reference voltage." *See* Ex. C at ¶ 53. The prior art reference Kitamura discloses the narrower element of "reference voltage," and so also discloses the broader "reference signal." *See id.* at ¶ 91. Similarly, for obviousness-type double patenting, the '851 patent discloses reference parameters that "are voltages," which meets the requirement for the "reference voltage" and the "reference signal." Ex. H at claim 3; Ex. C at ¶¶ 149-154. Thus, the invalidity analysis for "reference voltage" and "reference signal" is the same because the reference voltages in the references meet both limitations.

3. The remaining means-plus-function claim elements from claim 1. As can be seen above, these are the "memory cell programming means" and "comparator means" terms. Because of their means-plus-function claiming, they require identification of both appropriate structure and appropriate function.

### 1. <u>"Reference Voltage Selecting" Terms</u>

# (a) "Reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with said input information"

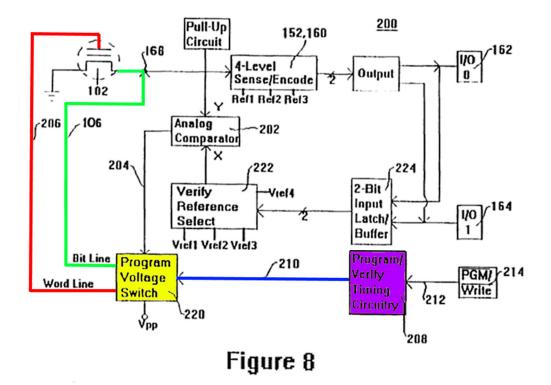

Claim 1 recites a "reference voltage selecting means for selecting one of a plurality of reference voltages in accordance with said input information, each of said reference voltages corresponding to a different one of said predetermined memory states." As is prescribed by MPEP 2181(I), using the word "means" in this claim (*i.e.*, "selecting means") and including functional language (*i.e.*, "selecting one of a plurality of reference voltages in accordance with said input information") invokes means-plus-function treatment. As the '571 patent discloses, the corresponding structure for the "reference voltage selecting means" includes at least the "verify reference select circuit 222." *See* Ex. C at ¶¶ 45-46.

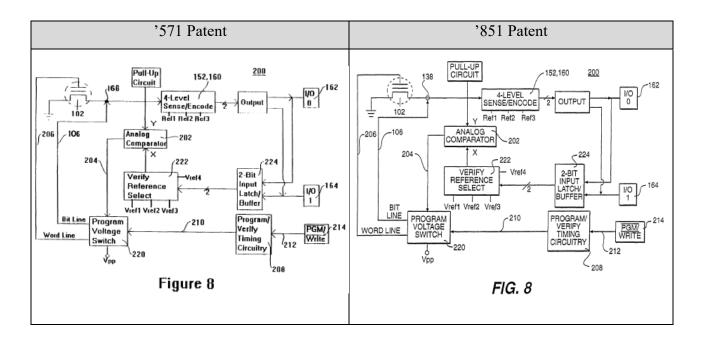

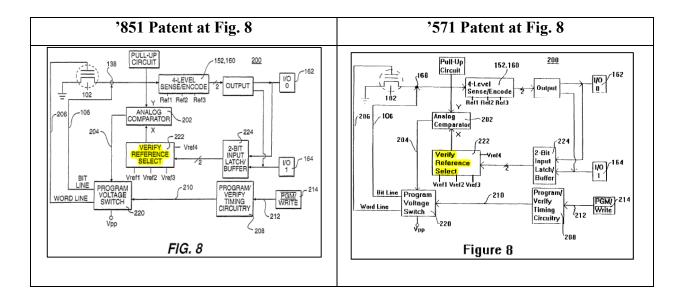

For example, the '571 patent describes that the "voltage threshold of memory cell 102 is then determined by using the comparator 202 to compare the bit line voltage at terminal 168 with *the selected verify reference voltage from the verify reference voltage select circuit 222.*" Ex. A ('571) at 8:66-9:3 (emphasis added). "The verify reference voltage select circuit 222 analog *output voltage X* is determined by decoding the output of the n-bit input latch/buffer 224 (n=2 in the illustrative form)." *Id.* at 9:11-14 (emphasis added). The "verify reference select circuit 222" also generates an analog voltage reference signal that is used by an analog comparator. *See id.* at 8:26-29 ("For the write mode of operation, a verify reference voltage select circuit 222 provides an analog voltage reference level signal X to one input terminal of an analog comparator 202."). Figure 8 echoes this by also showing the verify reference select circuit 222 providing the reference signal "X" to the comparator 202. *See id.* at Figure 8. Thus, the '571 patent discloses that the corresponding structure for the "reference voltage selecting means" includes at least the "verify reference select circuit 222."<sup>2</sup> *See* Ex. C at ¶ 46. The corresponding function is "selecting one of a plurality of reference voltages in accordance with the input information."<sup>3</sup> *See id.* at ¶ 46. Further information concerning the meaning of this term and its corresponding structure is included in the inventor notebook and testimony provided in Appendix A.

<sup>2</sup> This claim construction mirrors Judge Illston's claim construction order in the parties' copending litigation. *See MLC Intellectual Prop., LLC v. Micron Tech., Inc.*, No. 3:14-cv-03657, 2016 WL 6563343, at \*5 (N.D. Cal. Nov. 4, 2016) ("[T]he specification clearly links the verify reference select circuit to the function recited in the claim. . . . The Court does not limit the structure to the specific structures disclosed in Figure 8, and thus the *verify reference select circuit* may include, but is not limited to, the structure designated as '222' in Figure 8.") (emphasis added). While Judge Illston's identification of the corresponding structure is perhaps slightly broader than "verify reference select circuit 222" because it is not limited to the specific structure designated as "222" in the '571 patent, the distinction is immaterial for purposes of this ex parte reexamination. Thus, the prior art discloses the corresponding structure under either construction.

<sup>3</sup> This matches the function adopted by Judge Illston in the co-pending litigation. *See MLC*, 2016 WL 6563343, at \*5 ("For the foregoing reasons, the Court adopts the plain language function of 'selecting one of a plurality of reference voltages in accordance with the input information' with the corresponding structure of a verify reference select circuit.").

(b) "A selecting device which selects one of a plurality of [predetermined] reference signals in accordance with information indicating a memory state to which said memory cell is to be programmed"

This "selecting device" claim limitation from device claims 9, 12, and 30 is substantially similar to the "reference voltage selecting means" described directly above from claim 1. *See* Ex. C at ¶ 47. While this claim term is not explicitly written in means-plus-function form, it claims a generic device ("selecting device") with associated function ("which selects . . ."), thus requiring it to be construed in means-plus-function format. *See, e.g., Williamson v. Citrix Online, LLC,* 792 F.3d 1339, 1350 (Fed. Cir. 2015) (quoting *Mass. Inst. of Tech. & Elecs. For Imaging, Inc. v. Abacus Software*, 462 F.3d 1344, 1354 (Fed. Cir. 2006) ("Generic terms such as . . . 'device," are "nonce words that reflect nothing more than verbal constructs . . . used in a claim in a manner that is tantamount to using the word 'means' because they 'typically do not connote sufficiently definite structure' and therefore may invoke § 112, para. 6."). Based on the same disclosures from the '571 patent identified for the "reference voltage selecting means" above, the corresponding structure for the "selecting device" includes at least the "verify reference select circuit 222," and the function is "selecting one of a plurality of [predetermined] reference signals that corresponds to a memory state to which the memory cell is to be programmed."<sup>4</sup> *See* Ex. C at ¶ 47.

<sup>&</sup>lt;sup>4</sup> This claim construction mirrors Judge Illston's construction in the co-pending litigation. See MLC, 2016 WL 6563343, at \*9 ("[T]his Court will construe this term as a means-plus-function term subject to § 112, ¶ 6... The Court ... construes the claim as having the structure of the *verify reference select circuit*, pictured as example only in Fig. 8 as item 222, with the function of "selecting one of a plurality of [predetermined] reference signals that corresponds to a memory state to which the memory cell is to be programmed.") (emphases added). In

However, should the Office disagree that this "selecting device" term warrants meansplus-function treatment, a POSITA would have interpreted this "selecting device" component to be broad enough to include and be met by a device or process, that takes input information and selects, for a given memory cell's program/verify cycle, a reference signal from multiple reference signals such that the selected reference signal uniquely corresponds to the input information to be programmed in the memory cell. *See* Ex. C at ¶ 48. Further information concerning the meaning of this term and its corresponding structure is included in the inventor notebook and testimony provided in Appendix A.

# (c) "Selecting one of a plurality of reference signals in accordance with information indicating a memory state to which said memory cell is to be programmed"

This "selecting one of . . ." step from method claims 42 and 45 is substantially similar to the "reference voltage selecting means" described above from claim 1 but without requiring the means-plus-function treatment. Based on the same disclosures from the '571 patent identified for the "reference voltage selecting means" above, the proper construction for this term is

construing the claimed function, Judge Illston replaced the phrase "in accordance with information indicating" with the phrase "that corresponds to." *See id.* This is a non-substantive variation in the plain claim language that merely clarifies the term, as Judge Illston recognized when she said, "[t]he Court *adopts the same function* . . . for [the 'selecting device . . .' term] as it did for [the 'reference voltage selecting means . . .' term]," and then proceeded to modify the language of the function slightly from her construction of the function for the "reference voltage selecting means" term. *Id.* Because the difference between the express claim language and the construction adopted by Judge Illston does not affect the invalidity analysis, either one could be used.

"selecting one of a plurality of reference signals that corresponds to a memory state to which the memory cell is to be programmed."<sup>5</sup> As discussed above for the "selecting device" term, replacing the phrase "in accordance with information indicating" with the phrase "that corresponds to" helps to clarify this term but does not alter its scope or meaning. *See* Ex. C at ¶ 49. Further information concerning the meaning of this element and the nature of devices that perform the claimed function is included in the inventor notebook and testimony provided in Appendix A.

#### 2. <u>"Reference Voltages/Signals" Terms</u>

The three "reference voltage selecting" terms above interchangeably use "reference voltages" and "reference signals" to describe the same limitation. *Compare, e.g.*, Ex. A ('571) at Abstract ("Programming of the cell is verified by selecting a reference signal corresponding to the information to be stored and *comparing a signal* of the cell with the selected reference signal.") (emphasis added) with *id.* at 8:66-9:3 ("The voltage threshold of memory cell 102 is then determined by using the comparator 202 to *compare* the bit line *voltage* at terminal 168 with the selected verify reference *voltage* from the verify reference voltage select circuit 222.") (emphasis added); *see also* Ex. C at ¶ 53.

Further, the '571 patent indicates that a reference voltage/signal that can be either analog or digital. For example, in the analog context, the '571 patent describes that the "verify

<sup>&</sup>lt;sup>5</sup> This claim construction also mirrors Judge Illston's claim construction order in the co-pending litigation, in which she, once again, replaced "in accordance with information indicating" with "that corresponds to." *See MLC*, 2016 WL 6563343, at \*15 ("The main difference between the [parties'] proposals seems to be grammatical, not substantive. Because this difference does not change the scope of the claim, plaintiff's more concise word choice is adopted as less confusing to a jury. . . . Accordingly, the Court construes 'selecting one of a plurality of reference signals in accordance with information indicating a memory state to which said memory cell is to be programmed' as *'selecting one of a plurality of reference signals that corresponds to a memory state to which the memory cell is to be programmed.* ' (emphasis added)).

reference voltage select circuit 222 provides an *analog* voltage reference level *signal* X to one input terminal of an analog comparator 202." Ex. A ('571) at 8:26-29 (emphasis added). In the digital context, the '571 patent discloses that the reference voltage can be an encoded digital signal, as described in connection with the implementation of a digital comparator. *See id.* at 11:50-56 (the "verify reference voltage select [circuit] 222 would provide the voltage to be *encoded* with the input coming from the output of the n-bit input latch/buffer 224, representing the data to be programmed.") (emphasis added); *see also* Ex. C at ¶ 50. Further, the '571 patent also describes a "signal" as a digital signal. *See* Ex. A ('571) at 10:17-19 ("A low logic level state of the PGM/Write signal on signal line 212 enables the timing circuit 208."); *see also* Ex. C at ¶ 51-52.

Thus, a person of ordinary skill in the art would have interpreted this "reference voltage/signal" feature to be broad enough to include and be met by either a digital reference voltage/signal or an analog reference voltage/signal. *See* Ex. C at ¶ 54; *see also MLC*, 2016 WL 6263343, at \*16 ("Despite the analog embodiment, depicted in Figure 8, that includes reference voltages as opposed to signals, the specification makes clear that the technology can be implemented using analog or digital signals.").

#### 3. <u>Remaining Means-Plus-Function Terms</u>

#### (a) "Memory Cell Programming Means"

Claim 1 recites a "memory cell programming means for programming said multi-level memory cell in accordance with said input information." Much like the "reference voltage selecting means" discussed above and as is prescribed by MPEP 2181(I), this "memory cell programming means" term requires an appropriate structure and function for construction. Because the functional language of the claim as it stands is sufficiently clear, no modification is needed. As such, the appropriate function of the "memory cell programming means" is "programming the multi-level memory cell in accordance with the input information." For structure, the '571 patent discloses the programming of the memory cell through bit line and word line voltages, which are both provided by the program voltage switch. *See* Ex. A at 10:17-37 (The "program voltage switch 220" outputs "bit line and word line program voltage outputs" during a "programming process" to "add charge to the floating gate of the memory cell."). As such, the appropriate structure for the "memory cell programming means" is "program/verify

timing circuitry and a program voltage switch having its outputs (1) a bit line and (2) a word line." *See* Ex. C at ¶ 55. This also matches Judge Illston's claim construction ruling. *See* MLC, 2016 WL 6263343, at \*6.

#### (b) "Comparator Means"