## IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re patent of Braceras et al.:

U.S. Patent No. 6,967,861

Issued: November 22, 2005

Title: METHOD AND APPARATUS FOR IMPROVING CYCLE TIME IN A QUAD DATA RATE SRAM DEVICE Petition for Inter Partes Review

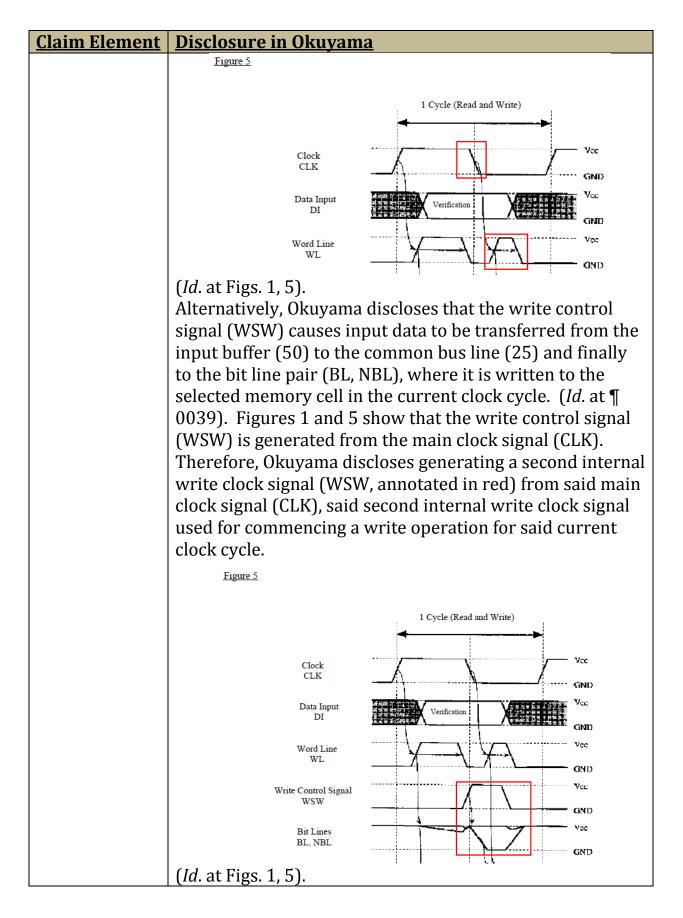

Attorney Docket No.: <u>351479-15.861</u>

Customer No.: 26379

Real Party-in-Interest: <u>GSI Technology, Inc.</u>

#### PETITION FOR INTER PARTES REVIEW

Mail Stop Patent Board Patent Trial and Appeal Board P.O. Box 1450 Alexandria, VA 22313-1450

Dear Sir:

Pursuant to the provisions of 35 U.S.C. § 311 and 37 C.F.R. § 42.100, GSI

Technology, Inc. ("Petitioner") hereby petitions the Patent Trial and Appeal Board

to institute an inter partes review of claims 1-3, 9-11, 17-20, 26-28 and 34 of

United States Patent No. 6,967,861 (the "861 patent").

# **TABLE OF CONTENTS**

| I.   | MAN | MANDATORY NOTICES                  |          |                                                                                  |

|------|-----|------------------------------------|----------|----------------------------------------------------------------------------------|

|      | A.  | Real                               | Party-i  | n-Interest1                                                                      |

|      | B.  | Relat                              | ed Ma    | tters1                                                                           |

|      | C.  | Lead                               | and Ba   | ack-up Counsel and Service Information1                                          |

|      | D.  | Servi                              | ce Info  | prmation2                                                                        |

| II.  | GRO | UNDS                               | S FOR    | STANDING2                                                                        |

| III. | REL | IEF REQUESTED2                     |          |                                                                                  |

| IV.  |     | C REASONS FOR THE REQUESTED RELIEF |          |                                                                                  |

|      | A.  | Sumr                               | nary o   | f Reasons3                                                                       |

|      | B.  | The '                              | 861 Pa   |                                                                                  |

|      |     | 1.                                 | Over     | view3                                                                            |

|      |     | 2.                                 | Prose    | cution History6                                                                  |

|      | C.  | Ident                              | ificatio | on of Challenges7                                                                |

|      |     | 1.                                 | Chall    | enged Claims7                                                                    |

|      |     | 2.                                 | Statu    | tory Grounds for Challenges8                                                     |

|      |     | 3.                                 | Clain    | n Construction8                                                                  |

|      |     | 4.                                 | Level    | of Ordinary Skill in the Art10                                                   |

|      |     | 5.                                 | Ident    | ification of How the Claims Are Unpatentable10                                   |

|      |     |                                    | i.       | Challenge #1: Takahashi Anticipates Claims 1, 9, 18 and 2610                     |

|      |     |                                    | ii.      | Challenge #2: Takahashi Renders Claims 2-3, 10-<br>11, 19-20 and 27-28 Obvious25 |

|      |     |                                    | iii.     | Challenge #3: Takahashi and Tsuchida Render<br>Claims 17 and 34 Obvious          |

# TABLE OF CONTENTS (continued)

Page

| V. | CONCLUSION |                                              | 60 |

|----|------------|----------------------------------------------|----|

|    |            | with Tsuchida                                | 35 |

|    |            | Combination with Takahashi or in Combination |    |

|    |            | 11, 17-20, 26-28 and 34 Obvious Alone, in    |    |

|    | iv.        | Challenge #4: Okuyama Renders Claims 1-3, 9- |    |

# EXHIBIT LIST

| <u>Exhibit Number</u> | <b>Description</b>                                 |

|-----------------------|----------------------------------------------------|

| GSI-1001              | U.S. Patent No. 6,967,861                          |

| GSI-1002              | File History for U.S. Patent No. 6,967,861         |

| GSI-1003              | U.S. Patent No. 7,162,657 to Takahashi             |

|                       | ("Takahashi")                                      |

| GSI-1004              | Japanese Patent Application Kokai No. 2000-173270  |

|                       | to Okuyama ("Okuyama")                             |

| GSI-1005              | U.S. Patent No. 6,647,478 to Tsuchida ("Tsuchida") |

| GSI-1006              | Declaration of R. Jacob Baker                      |

| GSI-1007              | Certified English Translation of Japanese Patent   |

|                       | Application Kokai No. 2000-173270 to Okuyama       |

|                       | ("Okuyama")                                        |

## I. MANDATORY NOTICES

#### A. Real Party-in-Interest

Pursuant to 37 C.F.R. § 42.8(b)(1), GSI Technology, Inc. ("Petitioner") is the real party-in-interest for this petition.

## **B.** Related Matters

Pursuant to 37 C.F.R. § 42.8(b)(2), the '861 patent is presently the subject of a patent infringement lawsuit brought by the assignee, Cypress Semiconductor Corporation, which may affect or be affected by a decision in this proceeding: *Cypress Semiconductor Corp. v. GSI Technology, Inc.*, N.D. Cal., Case Nos. 3:13cv-02013-JST (JCS) and 4:13-cv-03757-JST (JCS).

As of the filing of this petition, no other judicial or administrative matters are known to Petitioner that would affect, or be affected by, a decision in an *inter partes* review of the '861 patent.

# C. Lead and Back-up Counsel and Service Information

Pursuant to 37 C.F.R. §§ 42.8(b)(3) and 42.10(a), Petitioner provides the following designation of counsel.

| Lead Counsel           | Back-up Counsel          |

|------------------------|--------------------------|

| Timothy W. Lohse       | Kevin C. Hamilton        |

| DLA PIPER LLP (US)     | DLA PIPER LLP (US)       |

| 2000 University Avenue | 401 B Street, Suite 1700 |

| East Palo Alto, CA 94303   | San Diego, CA 92101         |

|----------------------------|-----------------------------|

| Phone: (650) 833-2055      | Phone: (619) 699-2634       |

| Fax: (650) 687-1183        | Fax: (619) 764-6633         |

| timothy.lohse@dlapiper.com | kevin.hamilton@dlapiper.com |

| USPTO Customer No. 26379   | USPTO Customer No. 26379    |

| USPTO Reg. No. 35,255      | USPTO Reg. No. 67,593       |

#### **D.** Service Information

Pursuant to 37 C.F.R. § 42.8(b)(4), papers concerning this matter should be served on either Timothy Lohse or Kevin Hamilton identified above and copying, as appropriate, the following email address: GSI-DLA-Team@dlapiper.com.

#### II. GROUNDS FOR STANDING

Pursuant to 37 C.F.R. § 42.104(a), Petitioner hereby certifies that the '861 patent is available for *inter partes* review and that Petitioner is not barred or estopped from requesting *inter partes* review challenging the claims of the '861 patent on the grounds identified herein.

#### III. RELIEF REQUESTED

Petitioner asks that the Board review the accompanying prior art and analysis, institute a trial for *inter partes* review of claims 1-3, 9-11, 17-20, 26-28 and 34 of the '861 patent, and cancel claims 1-3, 9-11, 17-20, 26-28 and 34 as invalid for the reasons set forth below.

#### IV. THE REASONS FOR THE REQUESTED RELIEF

#### A. Summary of Reasons

The '861 patent relates to a method and apparatus for improving cycle time in a Quad Data Rate SRAM device in which a self-timed, read to write operation in the SRAM is implemented. GSI-1001 at Title, Abstract. The '861 patent was issued on a first office action allowance without any prior art rejections. GSI-1002 at Notice of Allowance. In the specification, the patentee emphasizes the aspect that achieves the improvement in the cycle time as: "Briefly stated, an improvement in the cycle time is achieved by implementing a self-timed read to write protocol in which write addresses and data are captured and buffered during a given read to write cycle are actually written in the next read to write cycle. As such, the write operation (of data and address captured in the previous cycle) may be timed immediately after the read operation of the current cycle." GSI-1001 at 3:24-32 (emphasis added). However, as set forth below, this feature, as well as others claimed in the '861 patent, were well known in the art long before the '861 patent was filed.

#### B. The '861 Patent

#### 1. Overview

The '861 patent, entitled "METHOD AND APPARATUS FOR IMPROVING CYCLE TIME IN A QUAD DATA RATE SRAM DEVICE," issued on November 22, 2005, from an application filed on February 27, 2004, by

named inventors George Braceras and Harold Pilo. The '861 patent does not claim priority to any earlier filing.

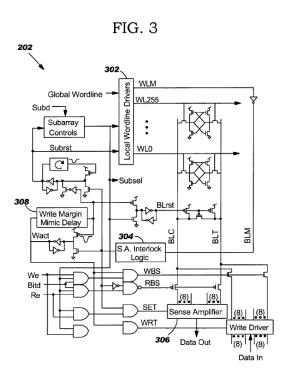

The '861 patent discloses read-to-write interlock circuitry 202 (shown in detail in Figure 3, which is reproduced below) that generates control signals to a sense amplifier 306 that senses read data on bit lines from the memory array and a write driver that drives write data into the memory array.

GSI-1001 at Fig. 3.

The read-to-write interlock circuitry 202 generates a control signal (RBS) for a pair of read bit switches to couple the sense amplifier to the bit lines (BLC, BLT) during a read operation and a control signal (WBS) for a pair of write bit switches to couple the write driver to the bit lines during a write operation. *Id.*

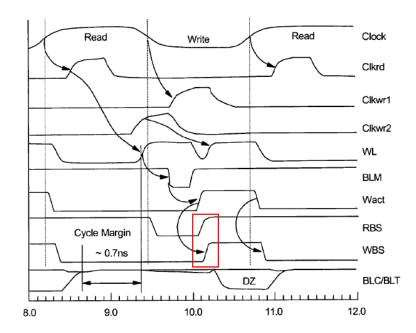

Figure 4 of the '861 patent (reproduced below in annotated form) shows the timing of the read bit switch control signal (RBS) and the write bit switch control signal (WBS) with respect to the timing between the read operation and the write operation. As shown in Figure 4, when the RBS signal goes high (which turns off the read bit switches because those switches are PMOS transistors as shown in Figure 3) the sense amplifier is isolated from the bit lines. Immediately after the sense amplifier is isolated from the bit lines, the write driver may be connected to the bit lines (shown by the WBS signal going high, which turns on the write bit switches because those switches are NMOS transistors as shown in Figure 3) which allows the write data to be written into the memory array using the bit lines. Id. at 2:55-65, 3:22-32, 4:50-62, Figs. 3-4. As shown in Figure 4 (annotated with the red box), the RBS signal transitions high (disconnecting the sense amplifier from the bit lines) as soon as the WBS signal transitions high (connecting the write driver to the bit lines) which allows the write operation (indicated by the transition of the WBS signal to high) to be timed immediately after the read operation (indicated by the transition of the RBS signal to high). Id.

#### 2. **Prosecution History**

The '861 patent matured from Patent Application No. 10/708,379, which was filed on February 27, 2004. The examiner issued the '861 patent on a Notice of Allowance mailed on July 20, 2005, without a prior art rejection. GSI-1002 at Notice of Allowance.

In the Notice of Allowance, the examiner indicated that the reasons for allowance were that the prior art identified by the examiner failed to teach the limitation of "wherein said write operation uses a previous write address captured during a preceding clock cycle; and capturing a current write address during a second half of said current clock cycle, said current write address to be used for a write operation implemented during a subsequent clock cycle; wherein said

commencing a write operation for said current clock cycle is timed independent of said current write address captured during said second half of said current clock cycle" (independent claims 1 and 9) or "wherein said write operation uses a previous write address captured during a preceding clock cycle; and capturing, in a write address buffer, a current write address during a second half of said current clock cycle, said current write address to be used for a write operation implemented during a subsequent clock cycle; wherein said commencing a write operation for said current clock cycle is timed independent of said current write address captured during said second half of said current write address captured during a subsequent clock cycle; wherein said commencing a write operation for said current clock cycle is timed independent of said current write address captured during said second half of said current clock cycle" (independent claims 18 and 25). GSI-1002 at Notice of Allowance at 2-3.

#### C. Identification of Challenges

Petitioner requests *inter partes* review of the '861 patent in view of the following references:

- GSI-1003 U.S. Patent No. 7,162,657 to Takahashi ("Takahashi")

- GSI-1004 Japanese Patent Application Kokai No. 2000-173270 to Okuyama ("Okuyama")

- GSI-1005 U.S. Patent No. 6,647,478 to Tsuchida ("Tsuchida")

#### 1. Challenged Claims

Petitioner requests that claims 1-3, 9-11, 17-20, 26-28 and 34 of the '861 patent be found unpatentable.

#### 2. Statutory Grounds for Challenges

### Challenge #1: Claims 1, 9, 18 and 26 are anticipated by Takahashi. The

'861 patent's earliest filing date is February 27, 2004. Takahashi was filed August 12, 2003, and published on February 19, 2004, and is prior art to the '861 patent under 35 U.S.C. §§ 102(a) and (e) (pre-AIA). GSI-1003 at cover page.

#### Challenge #2: Claims 2-3, 10-11, 19-20 and 27-28 are obvious over

Takahashi. Takahashi is prior art to the '861 patent as established above.

#### Challenge #3: Claims 17 and 34 are obvious over Takahashi and

**Tsuchida.** Takahashi is prior art to the '861 patent as established above. Tsuchida was filed June 20, 2002, published on October 31, 2002, and issued on November 11, 2003, and is prior art to the '861 patent under 35 U.S.C. § 102(b) (pre-AIA). GSI-1005 at cover page.

#### Challenge #4: Claims 1-3, 9-11, 17-20, 26-28 and 34 are obvious over

**Okuyama alone or in combination with Takahashi or Tsuchida.** Okuyama was filed December 4, 1998, and was published on June 23, 2000, and is prior art to the '861 patent under 35 U.S.C. § 102(b) (pre-AIA). GSI-1004 at cover page. Takahashi and Tsuchida are prior art to the '861 patent as established above.

#### **3.** Claim Construction

Pursuant to 42 C.F.R. §§ 42.100(b) and 42.204(b)(3), a claim subject to *inter partes* review receives the "broadest reasonable construction in light of the

specification of the patent in which it appears." 42 C.F.R. § 42.100(b). Claim terms are given their ordinary and accustomed meaning as they would be understood by one of ordinary skill in the art, unless the inventor, as a lexicographer, has set forth a special meaning for a term. *Multiform Desiccants, Inc. v. Medzam, Ltd.*, 133 F.3d 1473, 1477 (Fed. Cir. 1998); *York Prods., Inc. v. Central Tractor Farm & Family Ctr.*, 99 F.3d 1568, 1572 (Fed. Cir. 1996).

In the '861 patent, the inventors did not act as lexicographers and did not provide a special meaning for any of the claim terms. Accordingly, using the broadest reasonable interpretation standard, the terms should be given their ordinary and customary meaning as understood by a person of ordinary skill in the art and consistent with the disclosure. One key term is discussed below:

*as soon as*: "immediately, without delay." In the '861 patent, the specification discloses that the write operation is timed "immediately after the read operation" and "begin[s] the write operation immediately after the sense amplifier captures the read data." GSI-1001 at 2:55-60, 4:50-62. This is consistent with how one skilled in the art interprets this term. GSI-1006 at ¶ 18. Thus, this construction is consistent with and supported by the patent specification.

The proposed claim construction is presented using the broadest reasonable interpretation standard applied for purposes of *inter partes* review. Petitioner

reserves the right to advocate a different claim interpretation in any other forum in accordance with the claim construction standards applied in such forum.

#### 4. Level of Ordinary Skill in the Art

Petitioner proposes that one of ordinary skill in the art at the time the '861 patent was filed would have an undergraduate degree in electrical engineering, computer engineering, computer science or physics, and at least two years working in the field of digital semiconductor chip design. GSI-1006 at ¶ 10.

#### 5. Identification of How the Claims Are Unpatentable

## i. <u>Challenge #1: Takahashi Anticipates Claims 1, 9, 18</u> and 26

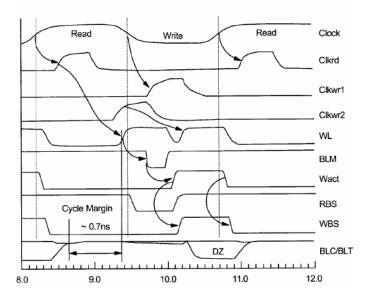

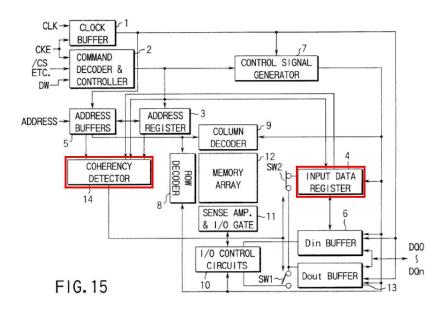

Takahashi anticipates claims 1, 9, 18 and 26 of the '861 patent under pre-AIA 35 U.S.C. §§ 102(a) and (e). Takahashi discloses the same technology that allegedly is the invention of the '861 patent. Specifically, Takahashi discloses a self-timed read to write operation in a memory storage device, including capturing a read address during a first half of a current clock cycle and commencing a read operation corresponding to the captured read address. Takahashi discloses commencing a write operation for the current clock cycle so as to cause write data to appear on the pair of bit lines as soon as the read data from the captured read address is amplified by the sense amplifier, wherein the write operation uses a previous write address captured during a preceding clock cycle. These elements are depicted in Figures 2 and 11 of Takahashi and discussed below in the chart.

GSI-1003 at Figs. 2, 11.

Takahashi discloses each limitation recited in claims 1, 9, 18 and 26. The

following claim chart demonstrates, on a limitation-by-limitation basis, how

Takahashi anticipates claims 1, 9, 18 and 26 of the '861 patent under pre-AIA 35

U.S.C. §§ 102 (a) and (e).

| <b><u>Claim Element</u></b>                                                                                                                        | Disclosure in Takahashi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1 preamble] A<br>method for<br>implementing a self-<br>timed, read to write<br>operation in a memory<br>storage device, the<br>method comprising: | Takahashi discloses a method for implementing<br>self-timed (GSI-1003 at 9:28-37), read to write<br>operation ( <i>id.</i> at 9:28-30) in a memory storage<br>device ( <i>id.</i> at 9:28). Self-timing is accomplished by<br>"a circuit for controlling the timing so that the<br>sense operation by the sense amplifier in the read<br>cycle and the address decoding operation by the<br>decoder in the write cycle in a cycle next following<br>the read cycle occur in parallel (105, 106, 107 in<br>Fig. 2). This configuration is effective to raise the<br>frequency of the driving clock signals." ( <i>Id.</i> at 9:28-<br>37). Figure 1 of Takahashi illustrates a read to<br>write operation implemented in a semiconductor<br>storage device. ( <i>Id.</i> at Fig. 1, 11:3-9). |

| [1 a] capturing a read<br>address during a first<br>half of a current clock<br>cycle;                                                              | Takahashi discloses this step. For example,Figure 15 (annotated in red below)illustrates that the read address A1 iscaptured on the rising edge of the CLK signal.The rising edge of the CLK signal marks thebeginning of the first half of the current clockcycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b><u>Claim Element</u></b>                                                 | Disclosure in Takahashi                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                             | FIG .15                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                             | CLK<br>Add A1 A2 A3                                                                                                                                                                                                                                                                                                                |  |  |

|                                                                             | R/W<br>COMMAND<br>Word                                                                                                                                                                                                                                                                                                             |  |  |

|                                                                             | SENSE AMPLIFIER                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                             | WA ACTIVATION                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                             | (GSI-1003 at Fig. 15). Furthermore, Takahashi states that the read address (A1) is sampled on the rising edge of the clock (CLK). ( <i>Id.</i> at 21:6-13).                                                                                                                                                                        |  |  |

| [1 b] commencing a<br>read operation so as to<br>read data                  | Takahashi discloses this step. For example,<br>Takahashi states:                                                                                                                                                                                                                                                                   |  |  |

| corresponding to said<br>captured read address<br>onto a pair of bit lines; | In the above mentioned circuit configuration, <u>during a</u><br>read cycle, the voltage appearing on a bit line responsive to<br>data stored in the selected memory cell is amplified by a<br><u>sense amplifier</u> which composes a read circuit for outputting<br>read data. During a write cycle, a bit line is driven with a |  |  |

|                                                                             | (GSI-1003 at 2:34-38, 11:35-41, 11:55-12:11).<br>Takahashi further explains that the captured read<br>address is used to generate X-address, Y-address                                                                                                                                                                             |  |  |

|                                                                             | and block selection address signals. ( <i>Id.</i> at 1:65-2:11, 12:36-51). The X-address, Y-address and                                                                                                                                                                                                                            |  |  |

|                                                                             | block selection address signals are used to select<br>the memory cell corresponding to the captured                                                                                                                                                                                                                                |  |  |

|                                                                             | read address. ( <i>Id.</i> at 1:65-2:11, 12:36-51). Figure 8 shows read data corresponding to the captured read address being read onto a pair of bit lines (B and /B). ( <i>Id.</i> at Fig. 8, 18:30-19:3).                                                                                                                       |  |  |

| [1 c] commencing a                                                          | Takahashi discloses this step. For example,                                                                                                                                                                                                                                                                                        |  |  |

| write operation for said current clock                                      | Takahashi discloses minimizing the total read-to-                                                                                                                                                                                                                                                                                  |  |  |

| cycle so as to cause                                                        | write cycle time by overlapping portions of the read and write cycles. (GSI-1003 at 11:35-41,                                                                                                                                                                                                                                      |  |  |

| write data to appear                                                        | 14:54-60). Overlapping the read and write cycles                                                                                                                                                                                                                                                                                   |  |  |

| <b><u>Claim Element</u></b> | Disclosure in Takahashi                                       |

|-----------------------------|---------------------------------------------------------------|

| on said pair of bit lines   | (shown in the red box annotation of Figure 1                  |

| as soon as said read        | below) enables writing data onto the bit lines as             |

| data from said              | soon as the read data is amplified by the sense               |

| captured read address       | amplifier, so the clock period can be reduced to its          |

| is amplified by a sense     | allowable limit. ( <i>Id</i> . at 12:19-32, 14:54-60).        |

| amplifier,                  | FIG.1                                                         |

|                             | Read                                                          |

|                             |                                                               |

|                             | DECODE Word LINE DECODE Word LINE DECODE                      |

|                             |                                                               |

|                             |                                                               |

|                             | Bit LINE PRE-CHARGE                                           |

|                             | (Id. at Fig. 1). Takahashi discloses that the read            |

|                             | and write operations occur alternately within the             |

|                             | current clock cycle. ( <i>Id.</i> at 9:28-37, 9:53-54, 11:56- |

|                             | 12:3). Figure 15 shows that the read to write                 |

|                             | operation illustrated in Figure 1 occurs in the               |

|                             | current clock cycle.                                          |

|                             | FIG .15                                                       |

|                             | CLK                                                           |

|                             | Add $(A1)$ $(A2)$ $(A3)$                                      |

|                             |                                                               |

|                             | Word                                                          |

|                             | SENSE AMPLIFIER                                               |

|                             | WA ACTIVATION                                                 |

|                             | (Id. at Fig. 15). Takahashi discloses that in a read-         |

|                             | to-write operation, there is no need to precharge             |

|                             | the bit line pair after the read data is captured by          |

|                             | the sense amplifier, and that write data can be               |

|                             |                                                               |

| <b><u>Claim Element</u></b> | Disclosure in Takahashi                                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------|

|                             | driven onto the bit lines as soon as the read data                                           |

|                             | sense operation is complete. ( <i>Id.</i> at 12:19-32).                                      |

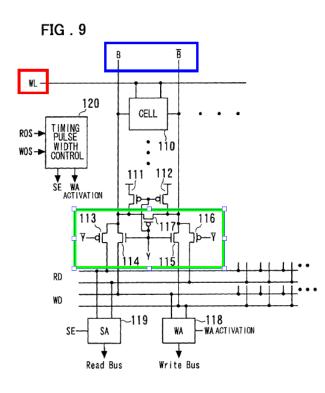

|                             | Figure 11 (annotated in red below) shows that                                                |

|                             | after sensing read data on a bit line pair using a                                           |

|                             | sense amplifier, instead of precharging the bit lines                                        |

|                             | after sensing the read data, the read word line is                                           |

|                             | reset, a Y-switch disconnects the sense amplifier                                            |

|                             | from the bit lines, and the write data is driven onto                                        |

|                             | the pair of bit lines. ( <i>Id</i> .).                                                       |

|                             | FIG . 11 read word line is reset                                                             |

|                             | WL SkewX CELL SkewX                                                                          |

|                             | B. /B                                                                                        |

|                             | Y SkewY SkewY                                                                                |

|                             | Y-switch                                                                                     |

|                             | WD disconnects sense<br>amp from bit lines                                                   |

|                             | Skew Block<br>SELECTION amplifier to bit                                                     |

|                             | lines, driving write                                                                         |

|                             | data onto the pair<br>of bit lines (see                                                      |

|                             | WA ACTIVATION GSI-1003, 19:47-52;                                                            |

|                             | Fig. 9)                                                                                      |

|                             | Write<br>Bus                                                                                 |

|                             | WL and Y low is consistent with a read preceding a write<br>(see GSI-1003, 18:12-64; Fig. 8) |

|                             | ( <i>Id</i> . at Fig. 11).                                                                   |

The '861 patent was filed more than 6 months after Takahashi was filed. Like Takahashi, the '861 patent specification explains that after sensing read data on a bit line pair using a sense amplifier, write data can be driven onto the bit lines as soon as the read data is amplified by the sense amplifier because there is no need to precharge the bit line pair before writing the data. GSI-1001 at 5:5-10. Instead of precharging the bit lines after sensing the read data, the read word line is reset, the read bit switch is disabled to disconnect the sense amplifier from the bit lines, and the write data is driven onto the pair of bit lines. *Id*. This is the same operation disclosed in Takahashi. *See* step [1 c] above. The similarities of Takahashi (left below) and '861 patent (right below) disclosures are shown below.

In the present embodiment, the signal amplitude on the bit 20 line is reduced (the differential voltage  $\Delta V$  of the bit line pair during read is usually 100 mV or less on the line Bit of FIG. 1), such that there is no necessity of providing a pre-charge period on the bit line after reading. It is because the amplitude of the signal to be written during the next write 25 cycle is large as compared to the differential voltage  $\Delta V$

appearing on the bit line pair and hence the write operation on the bit line is possible even if no pre-charging is performed. That is, memory cell selection and write amplifier activation may be effected so that the write data on the bit 30 line will be presented during the period when the bit line is to be pre-charged after the sense amplifier SA is activated to

read the data.

data (DZ) onto the bit line pair. There is no need to precharge 5 the bit line pair once the read data is captured by the sense amplifier BL restore after the read operation; as can be seen in FIG. 4, once the read word line signal is reset and the read bit switches are disabled (RBS goes high), the bit line pair is driven by write data. Finally, after the execution of the 10

#### Takahashi (GSI-1003 at 12:19-32)

'861 patent (GSI-1001 at 5:5-10)

Likewise, the figures of Takahashi and the '861 patent show similar circuits for writing data onto the bit lines as soon as the read data is amplified by a sense amplifier. Figure 9 of Takahashi (left below) shows the read word line signal (WL, one of many, in red box annotations), the Y-switches (transistors controlled by Y signal in green box annotations) and the bit line pair (B, /B) in blue box annotations. Figure 3 of the '861 patent (right below) shows the corresponding read word line signal (one of WL0 ... WL255) in red box annotations, read and write bit switches (transistors controlled by RBS and WBS) in green box annotations and the bit line pair (BLC and BLT) in blue box annotations. In each disclosure, these are the circuit elements that implement the read to write operation in which the write data is driven onto the bit lines as soon as the read data has been amplified by the sense amplifier.

Takahashi (GSI-1003) at Fig. 9

FIG. 3 202 302 WLM Drivers Global Wordlin WL255 Subd -7 Wordline Subarray Controls ocal WL0 Write Margin Mimic De BLM 304 S.A. Interlock Logic WBS We RBS Bitd (8) (8) SE Sense Amplifier WR' Write Driver 306 Data Out (8) (8) . ta In Da

'861 patent (GSI-1001) at Fig. 3

| <u>Claim</u>   | Disclosure in Takahashi                                        |

|----------------|----------------------------------------------------------------|

| <u>Element</u> |                                                                |

| [1 d] wherein  | Takahashi discloses this step. For example, Takahashi states   |

| said write     | that in the write operation for the current clock cycle, the   |

| operation      | write address is decoded and the write amplifier is activated  |

| uses a         | using only the rising edge of the clock signal. (GSI-1003 at   |

| previous       | 21:6-17). In Figure 15 below, the first and second pulses of   |

| write address  | the word line (read and write pulses of the Word signal,       |

| captured       | respectively) illustrate that the read and write addresses are |

| during a       | decoded using only the rising edge of the clock (CLK) signal.  |

| <u>Claim</u>         | Disclosure in Takahashi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Element<br>preceding | FIG .15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| clock cycle;<br>and  | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                      | Add (A1) (A2) (A3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | SENSE AMPLIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | WA ACTIVATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | ( <i>Id.</i> at Fig. 15). The components of the write operation ( <i>i.e.</i> , write address decoding, word line selection and write amplifier activation) do not depend upon waiting to capture write data and address information during the second half of the current clock cycle because such information was already captured in the prior clock cycle. ( <i>Id.</i> at 4:44-49, 9:28-37, 21:6-17). In other words, in Figure 15 above, the write operation for the current clock cycle uses a previous write address captured during a preceding clock cycle, while the write address A2 (captured on the falling edge of CLK in the current clock cycle) is used in the next clock cycle. ( <i>Id.</i> at 21:6-17). |

The '861 patent, filed more than six months after Takahashi was filed,

discloses the same write operation. Like Takahashi, the '861 patent specification explains that during the current clock cycle, the write address is decoded and the write amplifier is activated using only the rising edge of the clock signal (GSI-1001 at 3:47-50, 4:57-62). Like Takahashi, the first and second pulses of the word line (WL) signal (read and write pulses, respectively) shown in Figure 4 below illustrate that the read and write addresses are decoded using only the rising edge of the clock signal.

GSI-1001 at Fig. 4. Like Takahashi, the components of the write operation (*i.e.*, address decoding, word line selection and write amplifier activation) in the '861 patent do not depend upon waiting to capture write data and address information during the second half of the current clock cycle because such information was already captured in the prior cycle. *Id.* at 4:63-5:5. In other words, in Figure 4 above, the write operation for the current clock cycle uses a previous write address captured during a preceding clock cycle (*id.* at 4:67-5:5), while the write address (not shown, but captured on rise of Clkwr1, triggered by the falling edge of Clock in the current clock cycle) is used in the next clock cycle (*id.* at 2:62-65, 3:43-46, Fig. 4).

| <b><u>Claim Element</u></b>                                                                                                                                                                                                               | Disclosure in Takahashi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

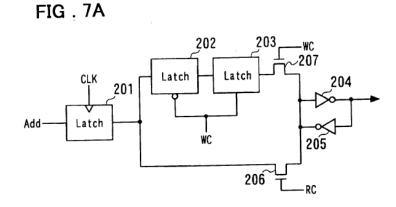

| [1 e] capturing a<br>current write<br>address during a<br>second half of<br>said current clock<br>cycle, said<br>current write<br>address to be<br>used for a write<br>operation<br>implemented<br>during a<br>subsequent clock<br>cycle; | Takahashi discloses this step. For example, Takahashi<br>discloses that: (1) an address clock generator 105<br>generates a read clock (RC) and a write clock (WC)<br>based on the first and second transitions of the clock,<br>respectively and (2) an address register 104 samples the<br>input address based on the CLK signal and then outputs<br>the address signals based on the read clock and write<br>clock, respectively. (GSI-1003 at 8:27-49). In other<br>words, in a given clock cycle, the address register 104<br>captures a current write address based on the clock<br>signal, and the address register 104 outputs a previous<br>write address captured during a previous clock cycle<br>when the WC signal is received. Figure 2 further shows<br>the address register 104. ( <i>Id.</i> at Fig. 2). |

|                                                                                                                                                                                                                                           | FIG . 7A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                           | Add Latch WC 205<br>202 203 WC<br>Latch Latch 204<br>WC 205<br>206 RC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                           | ( <i>Id.</i> at Fig. 7A). Figure 7A shows the structure of address register 104 shown in Figure 2. ( <i>Id.</i> at 17:9-14). Figure 7A shows that the current write address is captured in latch 201 during the current clock (CLK) cycle. Figure 7A shows latches 202 and 203 in the write address path between latch 201 and the output of address register 104. As configured, latches 202 and 203 act as a flip-flop clocked on the write clock WC. Consequently, in Figures 2 and 7A, the write address path has a one-clock-cycle delay relative to the read address path. Due to this delay, the captured write address will be used for a write operation implemented during a subsequent clock                                                                                                                  |

| <b><u>Claim Element</u></b>                                                    | Disclosure in Takahashi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                | cycle. ( <i>Id</i> . at 17:9-34).                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                | The example above describes an embodiment in which<br>the read and write addresses are sampled on rising<br>edges of the CLK signal. Takahashi discloses an<br>alternative embodiment in which the write address is<br>sampled on the falling edge of the clock (CLK) signal,<br>that is, during the second half of the current clock cycle.<br>( <i>Id.</i> at 21:6-13). Figure 15 below illustrates the<br>capturing of the current write address (A2) during the<br>second half of the current clock cycle: |  |  |

|                                                                                | FIG .15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                                                | ( <i>Id.</i> at Fig. 15). Therefore, Takahashi discloses capturing a current write address (A2) during a second half of said current clock cycle (at the falling edge of the clock signal CLK).                                                                                                                                                                                                                                                                                                                |  |  |

| [1 f] wherein said                                                             | Takahashi discloses this limitation. For example, as                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| commencing a<br>write operation<br>for said current<br>clock cycle is<br>timed | explained in claim [1 d] above, the write operation for<br>the current clock cycle uses a previous write address<br>captured in a preceding clock cycle. (GSI-1003 at 4:44-<br>49, 9:28-37, 21:6-17, Fig. 15).                                                                                                                                                                                                                                                                                                 |  |  |

| independent of<br>said current<br>write address<br>captured during             | As explained in claim [1 e] above, the write address<br>captured during the second half of the current clock<br>cycle is not used in the write operation for the current<br>clock cycle, but is used in a write operation of a                                                                                                                                                                                                                                                                                 |  |  |

| <b><u>Claim Element</u></b> | Disclosure in Takahashi                                            |  |

|-----------------------------|--------------------------------------------------------------------|--|

| said second half            | subsequent clock cycle. ( <i>Id.</i> at 8:27-49, 17:9-34, 21:6-13, |  |

| of said current             | Figs. 2, 15).                                                      |  |

| clock cycle.                |                                                                    |  |

In Takahashi, the write operation for the current clock cycle uses an address captured during a previous clock cycle. GSI-1003 at 4:44-49, 9:28-37, 21:6-17, Fig. 15. A write address (A2) is captured during the second half of the current clock cycle, but that address is not used for the write operation of the current clock cycle. GSI-1003 at 8:27-49, 17:9-34, 21:6-13, Figs. 2, 15. Instead, the write address captured during the second half of the current clock cycle is used in a subsequent clock cycle. Id. Therefore, the write operation of the current clock cycle does not depend upon when in the current clock cycle the write address (A2) is captured (e.g., early or late in the current clock cycle), or whether the write address (A2) is captured at all. GSI-1006 at ¶ 20. One of ordinary skill in the art at the time of the invention would have understood that this means the write operation for the current clock cycle is timed independent of the current write address captured during the second half of the current clock cycle. *Id.* The timing independence of the write address captured in the current clock cycle and the write operation in the current clock cycle is a necessary consequence of the limitations recited in claim elements [1 d] and [1 e] of the '861 patent because these limitations require that the write address captured in the current clock cycle is not

used in the write operation of the current clock cycle. *Id*. Therefore, Takahashi inherently discloses this limitation.

## <u>Claim 9</u>

The preamble of claim 9 recites "A method for implementing a self-timed,

read to write protocol for a Quad Data Rate (QDR) Static Random Access Memory

(SRAM) device," which is disclosed in Takahashi. Takahashi discloses a Quad

Data Rate SRAM and method for implementing data transfers. GSI-1003 at 1:13-

32, 22:32-35, Fig. 2; see also claim [1 preamble] above. Thus, Takahashi discloses

this element.

Takahashi also discloses the other elements of claim 9:

| Claim Element                                           | Disclosure in          |

|---------------------------------------------------------|------------------------|

|                                                         | <u>Takahashi</u>       |

| [9 a] capturing a read address during a first half of a | See claim [1 a] above. |

| current clock cycle;                                    |                        |

| [9 b] commencing a read operation so as to read         | See claim [1 b] above. |

| data corresponding to said captured read address        |                        |

| onto a pair of bit lines;                               |                        |

| [9 c] commencing a write operation for said current     | See claim [1 c] above. |

| clock cycle so as to cause write data to appear on      |                        |

| said pair of bit lines as soon as said read data from   |                        |

| said captured read address is amplified by a sense      |                        |

| amplifier,                                              |                        |

| [9 d] wherein said write operation uses a previous      | See claim [1 d] above. |

| write address captured during a preceding clock         |                        |

| cycle; and                                              |                        |

| [9 e] capturing, in a write address buffer, a current   | See claim [1 e] above. |

| write address during a second half of said current      |                        |

| clock cycle, said current write address to be used      |                        |

| for a write operation implemented during a              |                        |

| Claim Element                                                                                                                                              | <u>Disclosure in</u><br><u>Takahashi</u> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| subsequent clock cycle;                                                                                                                                    |                                          |

| [9 f] wherein said commencing a write operation<br>for said current clock cycle is timed independent of<br>said current write address captured during said | <i>See</i> claim [1 f] above.            |

| second half of said current clock cycle.                                                                                                                   |                                          |

# <u>Claim 18</u>

|                                  | D'ada anna 'n Talada d'                                |  |

|----------------------------------|--------------------------------------------------------|--|

| Claim Element                    | Disclosure in Takahashi                                |  |

| [18 preamble] A                  | <i>See</i> element [1 preamble] above. Takahashi       |  |

| semiconductor memory             | further discloses a semiconductor storage              |  |

| storage device, comprising:      | device. (GSI-1003 at Title, Abstract, 1:6-9).          |  |

| [18 a] circuitry configured to   | See claim [1 a] above. Takahashi further               |  |

| capture a read address during    | discloses an address register 104 that                 |  |

| a first half of a current clock  | samples the address signal. (GSI-1003 at               |  |

| cycle;                           | 1:65-67; see also id. at 12:36-48). Figure 2           |  |

|                                  | further illustrates that address register 104          |  |

|                                  | captures the address signal Add. ( <i>Id</i> . at Fig. |  |

|                                  | 2).                                                    |  |

| [18 b] circuitry configured to   | <i>See</i> claim [1 b] above. Takahashi further        |  |

| commence a read operation so     | discloses circuitry configured to commence             |  |

| as to read data corresponding    | a read operation so as to read data                    |  |

| to said captured read address    | corresponding to said captured read                    |  |

| onto a pair of bit lines;        | address onto a pair of bit lines. (GSI-1003            |  |

| onto a pari or bit intes,        | at 1:62-2:11, 8:27-49, 18:11-57, 20:16-44,             |  |

|                                  |                                                        |  |

| [10 a] aircuitres configured to  | 21:18-22:14, Figs. 2, 7A, 8, 9, 13, 16A, 17).          |  |

| [18 c] circuitry configured to   | <i>See</i> claim [1 c] above. Takahashi further        |  |

| commence a write operation       | discloses circuitry configured to commence             |  |

| for said current clock cycle so  | a write operation for said current clock               |  |

| as to cause write data to        | cycle so as to cause write data to appear on           |  |

| appear on said pair of bit lines | said pair of bit lines as soon as said read            |  |

| as soon as said read data from   | data from said captured read address is                |  |

| said captured read address is    | amplified by a sense amplifier. (GSI-1003              |  |

| amplified by a sense amplifier,  | at 9:28-37, 12:52-62, 19:4-17, 21:18-22:14,            |  |

|                                  | Figs. 2, 7A, 9, 13, 16A, 17).                          |  |

| [18 d] wherein said write        | See claim [1 d] above.                                 |  |

| operation uses a previous        |                                                        |  |

| Claim Element                  | Disclosure in Takahashi                     |  |

|--------------------------------|---------------------------------------------|--|

| write address captured during  |                                             |  |

| a preceding clock cycle; and   |                                             |  |

| [18 e] circuitry configured to | See claim [1 e] above. Takahashi further    |  |

| capture a current write        | discloses circuitry configured to capture a |  |

| address during a second half   | current write address during a second half  |  |

| of said current clock cycle,   | of said current clock cycle, said current   |  |

| said current write address to  | write address to be used for a write        |  |

| be used for a write operation  | operation implemented during a              |  |

| implemented during a           | subsequent clock cycle. (GSI-1003 at 8:27-  |  |

| subsequent clock cycle;        | 49, 17:9-58, 21:6-13, Figs. 2, 7A, 15).     |  |

| [18 f] wherein said write      | <i>See</i> claim [1 f] above.               |  |

| operation for said current     |                                             |  |

| clock cycle is timed           |                                             |  |

| independent of said current    |                                             |  |

| write address captured during  |                                             |  |

| said second half of said       |                                             |  |

| current clock cycle.           |                                             |  |

# <u>Claim 26</u>

Takahashi discloses each element of claim 26:

| Claim Element                                               | Disclosure in    |

|-------------------------------------------------------------|------------------|

|                                                             | <u>Takahashi</u> |

| [26 Preamble] A Quad Data Rate (QDR) Static Random          | See claim [18    |

| Access Memory (SRAM) device, comprising:                    | preamble]        |

|                                                             | above.           |

| [26 a] circuitry configured to capture a read address       | See claim [18 a] |

| during a first half of a current clock cycle;               | above.           |

| [26 b] circuitry configured to commence a read operation    | See claim [18 b] |

| so as to read data corresponding to said captured read      | above.           |

| address onto a pair of bit lines;                           |                  |

| [26 c] circuitry configured to commence a write             | See claim [18 c] |

| operation for said current clock cycle so as to cause write | above.           |

| data to appear on said pair of bit lines as soon as said    |                  |

| read data from said captured read address is amplified by   |                  |

| a sense amplifier,                                          |                  |

| [26 d] wherein said write operation uses a previous write   | See claim [18 d] |

| <u>Claim Element</u>                                                                                                                                                                                                                                              | <u>Disclosure in</u><br><u>Takahashi</u> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| address captured during a preceding clock cycle; and                                                                                                                                                                                                              | above.                                   |

| [26 e] circuitry configured to capture, in a write address<br>buffer, a current write address during a second half of<br>said current clock cycle, said current write address to be<br>used for a write operation implemented during a<br>subsequent clock cycle; | <i>See</i> claim [18 e]<br>above.        |

| [26 f] wherein said write operation for said current clock<br>cycle is timed independent of said current write address<br>captured during said second half of said current clock<br>cycle.                                                                        | <i>See</i> claim [18 f]<br>above.        |

#### ii. <u>Challenge #2: Takahashi Renders Claims 2-3, 10-11,</u> <u>19-20 and 27-28 Obvious</u>

Claims 2-3, 10-11, 19-20 and 27-28 depend from claims 1, 9, 18 and 26.

Takahashi discloses each element of claims 1, 9, 18 and 26 as set forth in the above charts.

#### Claims 2, 10, 19 and 27

Claims 2, 10, 19 and 27 further recite generating read and write clock signals (or circuitry for generating those read and write clock signals), which limitation is not inventive in view of Takahashi.

#### "Internal Read Clock Signal" Element

Takahashi discloses: (1) element [2 a] "generating an internal read clock signal from a main clock signal"; (2) element [10 a] "generating an internal read clock signal from a main clock signal"; (3) element [19 a] "circuitry configured to generate an internal read clock signal from a main clock signal"; and (4) element

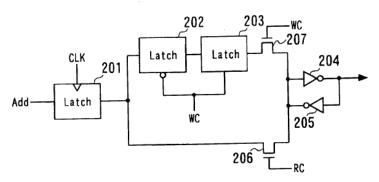

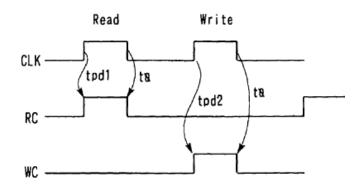

[27 a] "circuitry configured to generate an internal read clock signal from a main clock signal." Takahashi discloses generating an internal read clock signal (RC) from the main clock signal (CLK). GSI-1003 at 8:33-38, Fig. 7B. The internal read clock signal (RC) is used to capture a read address in a flip-flop formed by inverters 204 and 205, shown in Figure 7A below. *Id.* at 8:33-38, 17:13-19, 17:28-30, Figs. 7A, 7B.

Id. at Fig. 7A.

#### "First Internal Write Clock Signal" Element

Takahashi discloses: (1) element [2 b] "generating a first internal write clock signal write clock signal main clock signal, said first internal write clock signal used for said capturing a current write address"; (2) element [10 b] "generating a first internal write clock signal from said main clock signal, said first internal write clock signal used for said capturing a current write address"; (3) element [19 b] "circuitry configured to generate a first internal write clock signal from said main clock signal used for said capturing a current write clock signal from said main clock signal write clock signal from said main clock signal from said first internal write clock signal used for said capturing a current

write address"; and (4) element [27 b] "circuitry configured to generate a first internal write clock signal from said main clock signal, said first internal write clock signal used for said capturing a current write address." Takahashi discloses a write clock signal (CLK) used to capture a current write address in address register 104 on the falling edge of the clock signal (CLK). *Id.* at 21:6-13, Figs. 2, 7A, 15. Figure 7A (reproduced above) shows the structure of address register 104 and the clock signal (CLK). *Id.* at Fig. 7A, 7:9-14.

One of ordinary skill in the art would have understood that the main external clock signal shown in Figure 2 would be internally buffered to generate an internal CLK signal to drive the latch 201 shown in Figure 7A. GSI-1006 at ¶ 21. In a memory system such as that of Takahashi, the main clock signal is heavily loaded. *Id.* The main clock signal CLK must be internally buffered to guarantee signal integrity, ensure adequate noise immunity, and to minimize clock skew and insertion delay. *Id.* Therefore, Takahashi inherently discloses circuitry for generating a first internal write clock signal (CLK input of latch 201 in Figure 7A) from a main clock signal (CLK signal in Figure 2), said first internal write clock signal used for capturing a current write address. *Id.*

#### "Second Internal Write Clock Signal" Element

Takahashi also discloses: (1) element [2 c] "generating a second internal write clock signal from said main clock signal, said second internal write clock