| 1  | Frank E. Scherkenbach (SBN 142549 / scherkenbach@fr.com)<br>FISH & RICHARDSON P.C.                |                                      |  |  |

|----|---------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| 2  | 1 Marina Park Drive<br>Boston, MA 02210<br>Telephone: (617) 542-5070<br>Facsimile: (617) 542-8906 |                                      |  |  |

| 3  |                                                                                                   |                                      |  |  |

| 4  | Thomas L. Halkowski (admission pro hac vice to be                                                 | e filed /                            |  |  |

| 5  | <u>halkowski@fr.com</u> )<br>FISH & RICHARDSON P.C.                                               |                                      |  |  |

| 6  | 222 Delaware Avenue, 17th Floor<br>Post Office Box 1114                                           |                                      |  |  |

| 7  | Wilmington, DE 19899-1114<br>Telephone: (302) 652-5070                                            |                                      |  |  |

| 8  | Facsimile: (302) 652-0607                                                                         |                                      |  |  |

| 9  | Erin C. Jones (SBN 252947 / <u>erin.jones@fr.com</u> )<br>FISH & RICHARDSON P.C.                  |                                      |  |  |

| 10 | 500 Arguello Street, Suite 500<br>Redwood City, California 94070-1526                             |                                      |  |  |

| 11 | Telephone: (650) 839-5070                                                                         |                                      |  |  |

| 12 | Attorneys for Defendant                                                                           |                                      |  |  |

| 13 | CYPRESS SEMICONDUCTOR CORPORATION                                                                 |                                      |  |  |

| 14 | UNITED STATES DIS                                                                                 | STRICT COURT                         |  |  |

| 15 | NORTHERN DISTRICT OF CALIFORNIA                                                                   |                                      |  |  |

| 16 |                                                                                                   |                                      |  |  |

| 17 | CYPRESS SEMICONDUCTOR<br>CORPORATION,                                                             | Case No.                             |  |  |

| 18 | Plaintiff,                                                                                        | COMPLAINT FOR PATENT<br>INFRINGEMENT |  |  |

| 19 |                                                                                                   | JURY TRIAL DEMANDED                  |  |  |

| 20 | V.                                                                                                | JUKI I KIAL DEMANDED                 |  |  |

| 21 | GSI TECHNOLOGY, INC.,                                                                             |                                      |  |  |

| 22 | Defendant.                                                                                        |                                      |  |  |

| 23 |                                                                                                   |                                      |  |  |

| 24 |                                                                                                   |                                      |  |  |

| 25 |                                                                                                   |                                      |  |  |

| 26 |                                                                                                   |                                      |  |  |

| 27 |                                                                                                   |                                      |  |  |

| 28 |                                                                                                   |                                      |  |  |

|    |                                                                                                   |                                      |  |  |

. --

| Plaintiff Cypress Semiconductor Corporation ("Cypress" or "Plaintiff") alleges:                   |

|---------------------------------------------------------------------------------------------------|

| PARTIES                                                                                           |

| 1. Cypress is a corporation organized and existing under the laws of the State of                 |

| Delaware with its principal place of business located at 198 Champion Court, San Jose,            |

| California. Cypress is a supplier of high-performance, mixed-signal, programmable solutions that  |

| provide customers with rapid time-to-market and exceptional system value. In addition, and as     |

| described in further detail below, Cypress also is an industry-leading supplier of Static Random- |

| Access Memory (SRAM), including high-performance synchronous SRAMs, low-power                     |

| asynchronous SRAMs, fast asynchronous SRAMs, non-volatile SRAMs, and dual-port SRAMs.             |

| Cypress's innovations are used in a wide variety of consumer electronics, such as networking and  |

| telecommunication equipment, touchscreen devices, mobile handsets, video and imaging devices,     |

| as well as in military communication devices.                                                     |

| 2. On information and belief, Defendant GSI Technology, Inc. ("GSI") is a                         |

| corporation organized and existing under the laws of the State of Delaware and having its         |

| principal place of business at 1213 Elko Drive, Sunnyvale, California. As further described       |

| below, GSI manufactures SRAM products that infringe multiple Cypress patents.                     |

| JURISDICTION AND VENUE                                                                            |

| 3. This action arises under the patent laws of the United States, 35 U.S.C. § 101, et             |

| seq. This Court has subject matter jurisdiction over this action under 28 U.S.C. §§ 1331 and      |

| 1338(a).                                                                                          |

| 4. This Court has personal jurisdiction over GSI and venue is proper in the Northern              |

| District of California pursuant to 28 U.S.C. § 1391(b) and (c) and § 1400(b). GSI's principal     |

| place of business is in this District, GSI transacts business within this District and GSI offers |

| infringing products for sale in this District. On information and belief, GSI derives significant |

| revenue from the sale of infringing products distributed and used within this district, and/or    |

| expects or should reasonably expect its actions to have consequences within this district, and    |

| derives substantial revenue from interstate and international commerce. Moreover, GSI has         |

|                                                                                                   |

|                                                                                                   |

| 1  | already subjected itself to the personal jurisdiction of this Court by filing GSI Technology, Inc. v. |

|----|-------------------------------------------------------------------------------------------------------|

| 2  | Cypress Semiconductor Corp., Case No. 11-cv-03613-EJD (N.D. Cal.).                                    |

| 3  | INTRADISTRICT ASSIGNMENT                                                                              |

| 4  | 5. This is an Intellectual Property Action to be assigned on a district-wide basis                    |

| 5  | pursuant to Civil Local Rule 3-2(c).                                                                  |

| 6  | BACKGROUND                                                                                            |

| 7  | 6. For over thirty years, Cypress has been a pioneer and market innovator in the                      |

| 8  | SRAM field. SRAM "chips" are used to store instructions or data that can be read and modified.        |

| 9  | SRAM storage is generally volatile, meaning it must remain powered-up in order to preserve the        |

| 10 | instructions or data stored therein. Cypress's SRAM chips are used to store and retrieve data in      |

| 11 | networking, wireless infrastructure and handsets, computation, consumer, automotive, industrial       |

| 12 | and other electronic systems. Cypress's high-speed synchronous SRAM products include                  |

| 13 | standard synchronous pipelined, No Bus Latency ("NoBL"), Quad Data Rate™ ("QDR®"), and                |

| 14 | Double Data Rate ("DDR") SRAMs, which are all typically used in networking applications, as           |

| 15 | well as industrial, military, and medical electronics.                                                |

| 16 | 7. Cypress has a consistent track record of extensive investment in research and                      |

| 17 | development ("R&D"). Cypress's R&D efforts have been essential to its success as a supplier of        |

| 18 | semiconductor solutions. Cypress's R&D organization works closely with its manufacturing              |

| 19 | facilities, suppliers and customers to improve semiconductor designs and lower manufacturing          |

| 20 | costs.                                                                                                |

| 21 | 8. The SRAM field historically has been highly competitive, and Cypress's continued                   |

| 22 | success in the SRAM market depends on Cypress's continued dedication to R&D. To protect               |

| 23 | these critical R&D efforts, Cypress places a high value on its intellectual property. Cypress has     |

| 24 | applied for and received over 1800 patents in a variety of semiconductor-related technologies,        |

| 25 | and has over 900 pending patent applications. Of the issued patents, more than 200 are directed       |

| 26 | towards SRAM technology.                                                                              |

| 27 | 9. On information and belief, Defendant GSI was founded in San Jose, California in                    |

| 28 | March 1995. GSI designs, develops and markets SRAMs primarily for the networking and                  |

telecommunications markets. GSI is a longtime direct competitor of Cypress in the networkingSRAM market. GSI and Cypress compete for the same customers and design wins.

10. In contrast to Cypress, on information and belief, GSI has not made any significant

investment in the development and protection of intellectual property, holding less than

approximately 8 patents. Instead, in order to compete with Cypress, GSI decided to take

advantage of Cypress's hard work, including offering certain products that are "pin and function

compatible" with Cypress's corresponding QDR® SRAM chips. Through these deliberate

efforts, GSI has directly and indirectly infringed multiple Cypress patents.

9 11. Cypress has already taken steps to halt GSI's infringing acts by filing an action for 10 patent infringement on March 30, 2011, entitled Cypress Semiconductor Corp. v. GSI 11 Technology, Inc., Case No. 11-cv-00789-PJS (D. Minn.), and a complaint with the United States 12 International Trade Commission ("ITC"), In re Static Random Access Memories and Products Containing Same (Investigation No. 337-TA-792). As a reaction to Cypress's assertion of its 13 14 lawful intellectual property rights in the Minnesota and ITC actions, GSI filed an antitrust 15 complaint in this District, GSI Technology, Inc. v. Cypress Semiconductor Corp., Case No. 11-cv-16 03613-EJD (N.D. Cal.).

17 12. GSI's antitrust action is meritless and was filed only because Cypress chose to

18 protect its patent rights. Because GSI continues to take advantage of Cypress's hard work on

19 SRAM chips and willfully infringes Cypress's patents without authorization or license, Cypress is

20 filing the instant lawsuit to end GSI's infringement.

21

1

2

## GENERAL ALLEGATIONS

13. On May 30, 2000, the United States Patent and Trademark Office duly and legally

issued United States Patent No. 6,069,839 ("the '839 Patent"), entitled "Circuit and Method for

Implementing Single-Cycle Read/Write Operation(s), and Random Access Memory Including the

Circuit and/or Practicing the Method," to Cypress. Cypress owns the '839 Patent by assignment.

A true and correct copy of the '839 Patent is attached as Exhibit A to this Complaint.

27 14. On September 18, 2001, the United States Patent and Trademark Office duly and

28 legally issued United States Patent No. 6,292,403 ("the '403 Patent"), entitled "Circuit and

Method for Implementing Single-Cycle Read/Write Operation(s), and Random Access Memory

Including the Circuit and/or Practicing the Method," to Cypress. Cypress owns the '403 Patent

by assignment. A true and correct copy of the '403 Patent is attached as Exhibit B to this

Complaint.

5 15. On May 7, 2002, the United States Patent and Trademark Office duly and legally

6 issued United States Patent No. 6,385,128 ("the '128 Patent"), entitled "Random Access Memory

7 Having a Read/Write Address Bus and Process for Writing to and Reading From the Same," to

8 Cypress. Cypress owns the '128 Patent by assignment. A true and correct copy of the '128

9 Patent is attached as Exhibit C to this Complaint.

- 10 16. On September 3, 2002, the United States Patent and Trademark Office duly and

legally issued United States Patent No. 6,445,645 ("the '645 Patent"), entitled "Random Access

Memory Having Independent Read Port and Write Port and Process for Writing to and Reading

from the Same" to Cypress. Cypress owns the '645 Patent by assignment. A true and correct

copy of the '645 Patent is attached as Exhibit D to this Complaint.

- 15 17. On November 22, 2005, the United States Patent and Trademark Office duly and

legally issued United States Patent No. 6,967,861 ("the '861 Patent"), entitled "Method and

Apparatus for Improving Cycle Time in A Quad Data Rate SRAM Device," to International

Business Machines Corporation. Cypress owns the '861 Patent by assignment. A true and

correct copy of the '861 Patent is attached as Exhibit E to this Complaint.

20 18. The infringing SRAM parts manufactured by GSI include, but are not limited to, 21 (a) GSI's SigmaQuad product line, such as the SigmaQuad-II, SigmaQuad-II+, and SigmaQuad-22 III families of products, which include, but are not limited to, parts with the GS79, GS813xx, 23 GS834xx, GS818xx, GS866xx, and GS867xx part numbers, and (b) other products that 24 incorporate similar circuitry and/or have similar features, functionality, and/or architecture 25 (collectively, the "GSI Accused Products"). The identification of products and parts in this 26 Complaint is by way of example only, and on information and belief, the exemplary parts 27 identified in this Complaint are representative of all GS1 products and parts with reasonably 28 similar features, functionality and/or architecture, whether discontinued, current or future.

Making, selling, offering for sale, importing, or using any of the GSI Accused Products constitutes direct infringement of one or more claims of the '839, '403, '128, '645, and '861 patents.

4 19. The GSI Accused Products are designed for specific memory applications and

5 have no substantial non-infringing use.

20. According to GSI's 2012 Annual Report and other publicly available documents, 6 7 and on information and belief, the GSI Accused Products are sold to end customers in the United 8 States, and through distributors. These end customers and distributors are supplied with 9 datasheets that instruct downstream users how to operate the GSI Accused Products, and GSI 10 supplies such datasheets while knowing that the GSI Accused Products infringe multiple Cypress 11 patents. As detailed by the datasheets and other literature supplied by GSI, the GSI Accused 12 Products infringe multiple Cypress patents. Sale or use of the GSI Accused Products in accordance with the datasheets constitutes direct infringement of the '839, '403, '128, '645, and 13 14 '861 patents.

15 21. GSI is aware that the datasheets used by customers for the GSI Accused Products

16 demonstrate infringement of multiple Cypress patents, both through the filing of this Complaint

17 as well as the pleadings in the prior patent infringement lawsuits filed by Cypress against GSI.

18 GSI also advertises that certain of its SigmaQuad parts are "pin and function compatible" with

19 Cypress's corresponding QDR® chips, with the knowledge that Cypress's products incorporate

20 Cypress's proprietary technology, including the inventions disclosed in the '839, '403, '128, '645,

21 and '861 patents.

## FIRST CLAIM FOR RELIEF (Infringement of the '839 Patent)

22. Cypress incorporates and realleges the allegations of the preceding paragraphs as though set forth in full herein.

23. Cypress has not licensed or otherwise authorized GSI to make, use, offer for sale, sell, or import into the United States any products that embody the inventions of the '839 patent.

28

22

23

24

25

26

27

1

2

GSI has directly infringed and continues to directly infringe the '839 patent by

making, using, importing, offering for sale or selling the GSI Accused Products in the United

States.

4 25. GSI has had actual knowledge of the '839 patent since at least November 15,

5 2012.

6 26. GSI has indirectly infringed and continues to indirectly infringe the '839 patent by 7 inducing end-users to infringe the '839 patent by using the GSI Accused Products. GSI 8 intentionally took action that induced end-users to infringe the '839 patent by marketing, selling, 9 and supporting the infringing devices. For example, GSI supplies end customers and distributors 10 of the GSI Accused Products with datasheets that instruct downstream users how to operate the 11 GSI Accused Products, with knowledge that use in accordance with such instructions infringes 12 the '839 patent. As detailed by the datasheets and other literature supplied by GSI, the GSI 13 Accused Products infringe multiple Cypress patents. Sale or use of the GSI Accused Products in 14 accordance with the datasheets constitutes direct infringement of the '839 patent. GSI had 15 awareness of the '839 patent and knew, or was willfully blind to the fact, that its actions would 16 cause direct infringement by end-users.

17 27. GSI has indirectly infringed and continues to indirectly infringe the '839 patent by

18 contributing to direct infringement by end-users who use the GSI Accused Products. GSI

19 supplied a component whose use by downstream users is infringing; the component is not a

20 common component suitable for non-infringing use; and GSI supplied the component with the

21 knowledge of the '839 patent and knowledge that the component was especially made or adapted

22 for use in an infringing manner.

23

28. GSI's actions are in violation of one or more of the provisions of 35 U.S.C. § 271.

24 29. Cypress has been damaged and irreparably injured by GSI's infringing activities

25 and will continue to be so damaged and irreparably injured unless GSI's infringing activities are

26 enjoined by this Court.

- 27

- 28

| 1  | 30. On information and belief, GSI's infringement has been, and continues to be,                    |  |  |

|----|-----------------------------------------------------------------------------------------------------|--|--|

| 2  | willful, wanton, and deliberate, without license or excuse and with full knowledge of the '839      |  |  |

| 3  | patent.                                                                                             |  |  |

| 4  | SECOND CLAIM FOR RELIEF<br>(Infringement of the '403 Patent)                                        |  |  |

| 5  | 31. Cypress incorporates and realleges the allegations of the preceding paragraphs as               |  |  |

| 6  | though set forth in full herein.                                                                    |  |  |

| 7  | 32. Cypress has not licensed or otherwise authorized GSI to make, use, offer for sale,              |  |  |

| 8  | sell, or import into the United States any products that embody the inventions of the '403 patent.  |  |  |

| 9  | 33. GSI has directly infringed and continues to directly infringe the '403 patent by                |  |  |

| 10 | making, using, importing, offering for sale or selling the GSI Accused Products in the United       |  |  |

| 11 | States.                                                                                             |  |  |

| 12 | 34. GSI has had actual knowledge of the '403 patent since at least November 15,                     |  |  |

| 13 | 2012.                                                                                               |  |  |

| 14 | 35. GSI has indirectly infringed and continues to indirectly infringe the '403 patent by            |  |  |

| 15 | inducing end-users to infringe the '403 patent by using the GSI Accused Products. GSI               |  |  |

| 16 | intentionally took action that induced end-users to infringe the '403 patent by marketing, selling, |  |  |

| 17 | and supporting the infringing devices. For example, GSI supplies end customers and distributors     |  |  |

| 18 | of the GSI Accused Products with datasheets that instruct downstream users how to operate the       |  |  |

| 19 | GSI Accused Products, with knowledge that use in accordance with such instructions infringes        |  |  |

| 20 | the '403 patent. As detailed by the datasheets and other literature supplied by GSI, the GSI        |  |  |

| 21 | Accused Products infringe multiple Cypress patents. Sale or use of the GSI Accused Products in      |  |  |

| 22 | accordance with the datasheets constitutes direct infringement of the '403 patent. GSI had          |  |  |

| 23 | awareness of the '403 patent and knew, or was willfully blind to the fact, that its actions would   |  |  |

| 24 | cause direct infringement by end-users.                                                             |  |  |

| 25 | 36. GSI has indirectly infringed and continues to indirectly infringe the '403 patent by            |  |  |

| 26 | contributing to direct infringement by end-users who use the GSI Accused Products. GSI              |  |  |

| 27 | supplied a component whose use by downstream users is infringing; the component is not a            |  |  |

| 28 | common component suitable for non-infringing use; and GSI supplied the component with the           |  |  |

COMPLAINT FOR PATENT INFRINGEMENT

| 1  | knowledge of                                                                                        | f the '403 patent and knowledge that the component was especially made or adapted    |  |

|----|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| 2  | for use in an i                                                                                     | infringing manner.                                                                   |  |

| 3  | 37.                                                                                                 | GSI's actions are in violation of one or more of the provisions of 35 U.S.C. § 271.  |  |

| 4  | 38.                                                                                                 | Cypress has been damaged and irreparably injured by GSI's infringing activities      |  |

| 5  | and will cont                                                                                       | inue to be so damaged and irreparably injured unless GSI's infringing activities are |  |

| 6  | enjoined by the                                                                                     | his Court.                                                                           |  |

| 7  | 39.                                                                                                 | On information and belief, GSI's infringement has been, and continues to be,         |  |

| 8  | willful, wante                                                                                      | on, and deliberate, without license or excuse and with full knowledge of the '403    |  |

| 9  | patent.                                                                                             |                                                                                      |  |

| 10 |                                                                                                     | THIRD CLAIM FOR RELIEF<br>(Infringement of the '128 Patent)                          |  |

| 11 | 40.                                                                                                 | Cypress incorporates and realleges the allegations of the preceding paragraphs as    |  |

| 12 | though set for                                                                                      | rth in full herein.                                                                  |  |

| 13 | 41.                                                                                                 | Cypress has not licensed or otherwise authorized GSI to make, use, offer for sale,   |  |

| 14 | sell, or impor                                                                                      | t into the United States any products that embody the inventions of the '128 patent. |  |

| 15 | 42.                                                                                                 | GSI has directly infringed and continues to directly infringe the '128 patent by     |  |

| 16 | making, using                                                                                       | g, importing, offering for sale or selling the GSI Accused Products in the United    |  |

| 17 | States.                                                                                             |                                                                                      |  |

| 18 | 43.                                                                                                 | GSI has had actual knowledge of the '128 patent since at least November 15,          |  |

| 19 | 2012.                                                                                               |                                                                                      |  |

| 20 | 44.                                                                                                 | GSI has indirectly infringed and continues to indirectly infringe the '128 patent by |  |

| 21 | inducing end-                                                                                       | -users to infringe the '128 patent by using the GSI Accused Products. GSI            |  |

| 22 | intentionally took action that induced end-users to infringe the '128 patent by marketing, selling, |                                                                                      |  |

| 23 | and supportin                                                                                       | g the infringing devices. For example, GSI supplies end customers and distributors   |  |

| 24 | of the GSI Ac                                                                                       | ccused Products with datasheets that instruct downstream users how to operate the    |  |

| 25 | GSI Accused                                                                                         | Products, with knowledge that use in accordance with such instructions infringes     |  |

| 26 | the '128 pater                                                                                      | nt. As detailed by the datasheets and other literature supplied by GSI, the GSI      |  |

| 27 | Accused Prod                                                                                        | lucts infringe multiple Cypress patents. Sale or use of the GSI Accused Products in  |  |

| 28 | accordance w                                                                                        | ith the datasheets constitutes direct infringement of the '128 patent. GSI had       |  |

|    |                                                                                                     |                                                                                      |  |

1 awareness of the '128 patent and knew, or was willfully blind to the fact, that its actions would 2 cause direct infringement by end-users. 3 45. GSI has indirectly infringed and continues to indirectly infringe the '128 patent by 4 contributing to direct infringement by end-users who use the GSI Accused Products. GSI 5 supplied a component whose use by downstream users is infringing; the component is not a 6 common component suitable for non-infringing use; and GSI supplied the component with the 7 knowledge of the '128 patent and knowledge that the component was especially made or adapted 8 for use in an infringing manner. 9 46. GSI's actions are in violation of one or more of the provisions of 35 U.S.C. § 271. 10 47. Cypress has been damaged and irreparably injured by GSI's infringing activities 11 and will continue to be so damaged and irreparably injured unless GSI's infringing activities are 12 enjoined by this Court. 48. 13 On information and belief, GSI's infringement has been, and continues to be, 14 willful, wanton, and deliberate, without license or excuse and with full knowledge of the '128 15 patent. FOURTH CLAIM FOR RELIEF 16 (Infringement of the '645 Patent) 17 49. Cypress incorporates and realleges the allegations of the preceding paragraphs as 18 though set forth in full herein. 19 50. Cypress has not licensed or otherwise authorized GSI to make, use, offer for sale, 20 sell, or import into the United States any products that embody the inventions of the '645 patent. 21 51. GSI has directly infringed and continues to directly infringe the '645 patent by 22 making, using, importing, offering for sale or selling the GSI Accused Products in the United 23 States. 24 52. GSI has had actual knowledge of the '645 patent since at least November 15, 25 2012. 26 53. GSI has indirectly infringed and continues to indirectly infringe the '645 patent by 27 inducing end-users to infringe the '645 patent by using the GSI Accused Products. GSI 28 intentionally took action that induced end-users to infringe the '645 patent by marketing, selling,

and supporting the infringing devices. For example, GSI supplies end customers and distributors 1 of the GSI Accused Products with datasheets that instruct downstream users how to operate the 2 GSI Accused Products, with knowledge that use in accordance with such instructions infringes 3 4 the '645 patent. As detailed by the datasheets and other literature supplied by GSI, the GSI 5 Accused Products infringe multiple Cypress patents. Sale or use of the GSI Accused Products in 6 accordance with the datasheets constitutes direct infringement of the '645 patent. GSI had 7 awareness of the '645 patent and knew, or was willfully blind to the fact, that its actions would 8 cause direct infringement by end-users.

9 54. GSI has indirectly infringed and continues to indirectly infringe the '645 patent by

10 contributing to direct infringement by end-users who use the GSI Accused Products. GSI

11 supplied a component whose use by downstream users is infringing; the component is not a

12 common component suitable for non-infringing use; and GSI supplied the component with the

13 knowledge of the '645 patent and knowledge that the component was especially made or adapted

14 for use in an infringing manner.

15 55. GSI's actions are in violation of one or more of the provisions of 35 U.S.C. § 271.

16 56. Cypress has been damaged and irreparably injured by GSI's infringing activities

17 and will continue to be so damaged and irreparably injured unless GSI's infringing activities are

18 enjoined by this Court.

19 57. On information and belief, GSI's infringement has been, and continues to be,

20 willful, wanton, and deliberate, without license or excuse and with full knowledge of the '645

21 patent.

22

23

28

## FIFTH CLAIM FOR RELIEF (Infringement of the '861 Patent)

58. Cypress incorporates and realleges the allegations of the preceding paragraphs as

though set forth in full herein.

59. Cypress has not licensed or otherwise authorized GSI to make, use, offer for sale, sell, or import into the United States any products that embody the inventions of the '861 patent.

60. On information and belief, GSI has directly infringed and continues to directly

infringe the '861 patent by making, using, importing, offering for sale or selling the GSI Accused Products in the United States.

GSI has had actual knowledge of the '861 patent since at least the filing of this 61. 4 Complaint.

5 62. On information and belief, GSI has indirectly infringed and continues to indirectly 6 infringe the '861 patent by inducing end-users to infringe the '861 patent by using the GSI 7 Accused Products. On information and belief, GSI intentionally took action that induced end-8 users to infringe the '861 patent by marketing, selling, and supporting the infringing devices. For 9 example, on information and belief, GSI supplies end customers and distributors of the GSI 10 Accused Products with datasheets that instruct downstream users how to operate the GSI Accused 11 Products, with knowledge that use in accordance with such instructions infringes the '861 patent. 12 As detailed by the datasheets and other literature supplied by GSI, on information and belief, the 13 GSI Accused Products infringe multiple Cypress patents. On information and belief, sale or use 14 of the GSI Accused Products in accordance with the datasheets constitutes direct infringement of 15 the '861 patent. On information and belief, GSI had awareness of the '861 patent and knew, or 16 was willfully blind to the fact, that its actions would cause direct infringement by end-users.

17 63. On information and belief, GSI has indirectly infringed and continues to indirectly 18 infringe the '861 patent by contributing to direct infringement by end-users who use the GSI 19 Accused Products. On information and belief, GSI supplied a component whose use by 20 downstream users is infringing; the component is not a common component suitable for non-21 infringing use; and GSI supplied the component with the knowledge of the '861 patent and 22 knowledge that the component was especially made or adapted for use in an infringing manner.

23 64. On information and belief, GSI's actions are in violation of one or more of the 24 provisions of 35 U.S.C. § 271.

25 65. On information and belief, Cypress has been damaged and irreparably injured by 26 GSI's infringing activities and will continue to be so damaged and irreparably injured unless 27 GSI's infringing activities are enjoined by this Court.

28

1

2

3

| 1  | 66. On information and belief, GSI's infringement has been, and continues to be,                   |

|----|----------------------------------------------------------------------------------------------------|

| 2  | willful, wanton, and deliberate, without license or excuse and with full knowledge of the '861     |

| 3  | patent.                                                                                            |

| 4  | PRAYER FOR RELIEF                                                                                  |

| 5  | WHEREFORE, Cypress requests that this Court grant the following relief:                            |

| 6  | a. Enter judgment that the GSI Accused Products infringe the '839, '403, '128, '645,               |

| 7  | and '861 patents;                                                                                  |

| 8  | b. Enter an order permanently enjoining GSI and its officers, directors, agents,                   |

| 9  | servants, employees, attorneys, licensees, successors, assigns, and customers, and those in active |

| 10 | concert or participation with any of them, from making, using, offering to sell, or selling in the |

| 11 | United States or importing into the United States any devices that infringe any claim of the       |

| 12 | Cypress Patents;                                                                                   |

| 13 | c. Award Cypress its damages, including lost profits, resulting from GSI's                         |

| 14 | infringement in an amount to be determined at trial, pursuant to 35 U.S.C. § 284;                  |

| 15 | d. Find this to be an exceptional case pursuant to 35 U.S.C. § 285;                                |

| 16 | e. Award Cypress prejudgment interest and post-judgment interest on its damages                    |

| 17 | and award Cypress its costs;                                                                       |

| 18 | f. Perform an accounting of GSI's infringing sales not presented at trial and award                |

| 19 | Cypress additional damages from any such infringing sales; and                                     |

| 20 | g. Award Cypress its costs and attorneys' fees and such other and further relief as the            |

| 21 | Court deems just and appropriate.                                                                  |

| 22 |                                                                                                    |

| 23 |                                                                                                    |

| 24 |                                                                                                    |

| 25 |                                                                                                    |

| 26 |                                                                                                    |

| 27 |                                                                                                    |

| 28 |                                                                                                    |

|    | 12                                                                                                 |

| 1  | DEMAND FOR JURY TRIAL                                                                  |

|----|----------------------------------------------------------------------------------------|

| 2  | Pursuant to Rule 38(b) of the Federal Rules of Civil Procedure, Cypress hereby demands |

| 3  | trial by jury on all issues raised by the Complaint.                                   |

| 4  |                                                                                        |

| 5  | Dated: May 1, 2013 FISH & RICHARDSON P.C.                                              |

| 6  | Dated: May 1, 2013 FISH & RICHARDSON P.C.                                              |

| 7  | D. Hearth Sales Louis logal (90)                                                       |

| 8  | By: <u>Frank Scherkenbach &amp; Frank E. Scherkenbach</u>                              |

| 9  | Attorneys for Defendant                                                                |

| 10 | CYPRESS SEMICONDUCTOR<br>CORPORATION                                                   |

| 11 | CORPORATION                                                                            |

| 12 |                                                                                        |

| 13 |                                                                                        |

| 14 |                                                                                        |

| 15 |                                                                                        |

| 16 |                                                                                        |

| 17 |                                                                                        |

| 18 |                                                                                        |

| 19 |                                                                                        |

| 20 |                                                                                        |

| 21 |                                                                                        |

| 22 |                                                                                        |

| 23 |                                                                                        |

| 24 |                                                                                        |

| 25 |                                                                                        |

| 26 |                                                                                        |

| 20 |                                                                                        |

| 28 |                                                                                        |

| 20 |                                                                                        |

|    | 13<br>COMPLAINT FOR PATENT INFRINGEMENT                                                |

# **EXHIBIT A**

## United States Patent [19]

## Pancholy et al.

#### [54] CIRCUIT AND METHOD FOR IMPLEMENTING SINGLE-CYCLE READ/ WRITE OPERATION(S), AND RANDOM ACCESS MEMORY INCLUDING THE CIRCUIT AND/OR PRACTICING THE METHOD

- [75] Inventors: Ashish Pancholy, Milpitas; Cathal G. Phelan, Mountain View; Simon J. Lovett, Milpitas, all of Calif.

- [73] Assignee: Cypress Semiconductor Corp., San Jose, Calif.

- [21] Appl. No.: 09/238,270

[60]

[22] Filed: Jan. 27, 1999

### Related U.S. Application Data

- Provisional application No. 60/078,718, Mar. 20, 1998.

- [51] Int. Cl.<sup>7</sup> ...... G11C 8/00

- [58] Field of Search ...... 365/189.04, 233

#### [56] References Cited

#### **U.S. PATENT DOCUMENTS**

5,530,673 6/1996 Tobita et al. ..... 365/185.09

### US006069839A

## [11] **Patent Number:** 6,069,839

### [45] **Date of Patent:** May 30, 2000

| Primary.  | Examiner—Trong Phan                          |

|-----------|----------------------------------------------|

| Assistant | <i>Examiner</i> —M. Tran                     |

| Attorney, | Agent, or Firm-Christopher P. Maiorana, P.C. |

| [57]      | ABSTRACT                                     |

A circuit including an address bus providing random addresses for a random access memory array, and a register configured to receive, store or transfer (i) a first random address from the address bus in response to a first periodic signal transition and (ii) a second random address from the address bus in response to a second periodic signal transition, wherein the first and second periodic signal transitions occur within a single periodic signal cycle, and are preferably complementary to each other. In a further embodiment, the invention concerns a random access memory having an address bus providing random address information for a random access memory array, a predecoder configured to at least partially decode the random address information from the address bus, a register configured to receive, store or transfer (i) a first at least partially decoded random address from the address bus in response to a first periodic signal transition and (ii) a second at least partially decoded random address from the address bus in response to a second periodic signal transition, wherein the first and second periodic signal transitions occur within a single periodic signal cycle; and a postdecoder configured to activate the random addresses in the random access memory in response to receiving the random addresses from the register.

#### 22 Claims, 8 Drawing Sheets

6,069,839

**U.S.** Patent

May 30, 2000

Sheet 1 of 8

Fig. 2

6,069,839

**U.S.** Patent

May 30, 2000

Sheet 3 of 8

Fig. 3

6,069,839

**U.S.** Patent

May 30, 2000

Sheet 4 of 8

Fig. 4

**U.S.** Patent

May 30, 2000

Sheet 5 of 8

6,069,839

Fig. 5

Fig. 6B

Fig. 6C

This PDF of U.S. Utility Patent 6069839 provided by Patent Fetcher<sup>TM</sup>, a product of Stroke of Color, Inc. - Page

8 of 17

#### CIRCUIT AND METHOD FOR IMPLEMENTING SINGLE-CYCLE READ/ WRITE OPERATION(S), AND RANDOM ACCESS MEMORY INCLUDING THE CIRCUIT AND/OR PRACTICING THE METHOD

This application claims the benefit of U.S. Provisional application Ser. No. 60/078,718, filed Mar. 20, 1998.

The invention described and claimed in this application 10 may be related to subject matter described in one or more copending provisional applications entitled, "Random Access Memory And Process For Writing To And Reading From The Same," by Mathew R. Arcoleo, Cathal G. Phelan, Ashish Pancholy, and Simon J. Lovett, identified as Attorney 15 Docket No. CD98022, and/or "Random Access Memory Having Read/Write Address Bus and Process For Writing To And Reading From The Same," by Mathew R. Arcoleo, Cathal G. Phelan, Ashish Pancholy, and Simon J. Lovett, identified as Attorney Docket No. CD98023, both of which 20 were filed in the U.S. Patent and Trademark Office as a provisional patent application on Mar. 13, 1998, both of which are incorporated herein by reference in their entireties.

#### BACKGROUND OF THE INVENTION

This invention relates generally to the field of semiconductor and/or integrated circuit devices, particularly to a random access memory and process for writing to and reading from the same, and more particularly to a circuit and method for implementing single-cycle read/write operation (s) in a random access memory (RAM).

#### **OBJECTS OF THE INVENTION**

The primary object of the invention is to provide a circuit and method that enables reading from and writing to a random access memory in the same clock cycle.

Another object of the invention is to provide a circuit and method that enables reading from and writing to a random 40 access memory in the same clock cycle, using a single read/write address bus or separate read and write address busses.

A further object of the invention is to provide a circuit that latches a new address on each edge, transition or level of a periodic and/or control signal. memory (RAM) architecture employing a third embodiment of the present address scheme (FIG. 6A), a detailed schematic diagram of the address register shown in FIG. 6A

A further object of the invention is to provide a random access memory that increases data throughput.

Still yet another object of the invention is to provide such  $_{50}$  a circuit and/or random access memory that reduces the chip area dedicated to transmitting and/or storing address information.

An even further object of the invention is to provide a random access memory and method of operating the same in  $_{55}$  which read and write operations may be executed in the same clock cycle.

Yet further objects of the invention include providing such a random access memory and method of operating the same in which fully random addresses may be employed, in which successive and/or asserted addresses may be completely unrelated, and/or in which no restrictions are placed on successive and/or asserted addresses.

Another object of the invention is to provide such a random access memory and method of operating the same in 65 which the same address may be used to read from and write to the memory in the same clock cycle.

A further object of the invention is to provide such a random access memory and method of operating the same in which a periodic signal (e.g., a clock) is the only controltype signal essential to operability.

Other objects and advantages of the present invention will become apparent from the following description, taken in connection with the accompanying drawings, wherein, by way of illustration and example, embodiments of the present invention are disclosed.

#### SUMMARY OF THE INVENTION

The present invention concerns a circuit comprising an address bus providing random addresses for a random access memory array, and a register configured to store or receive (i) a first random address from the address bus to the random access memory array directly or indirectly in response to a first periodic signal transition and (ii) a second random address from the address bus to the random access memory array directly in response to a second periodic signal transition, wherein the second periodic signal transition occurs in the same periodic signal cycle as, and preferably is complementary to, the first periodic signal transition.

#### BRIEF DESCRIPTION OF THE DRAWINGS

<sup>25</sup> The drawings constitute a part of this specification and include exemplary embodiments to the invention, which may be embodied in various forms. The features and advantages of the present invention are illustrated by way of example in the drawings, in which:

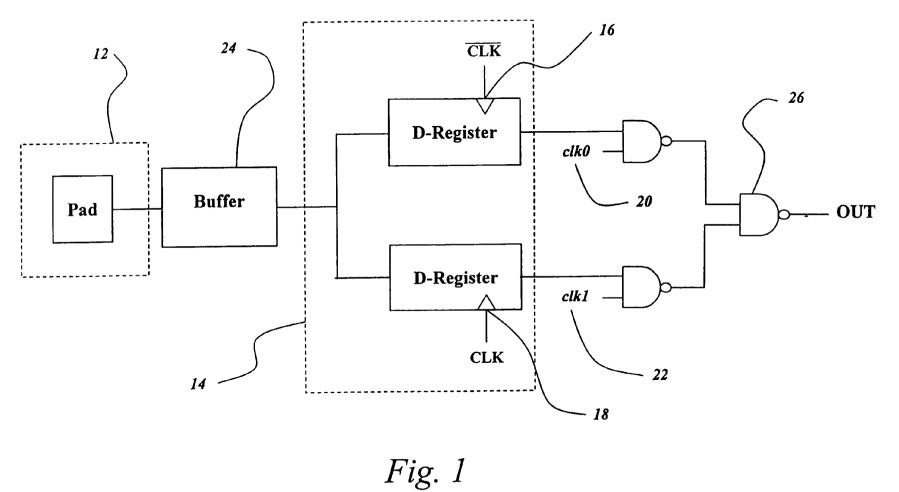

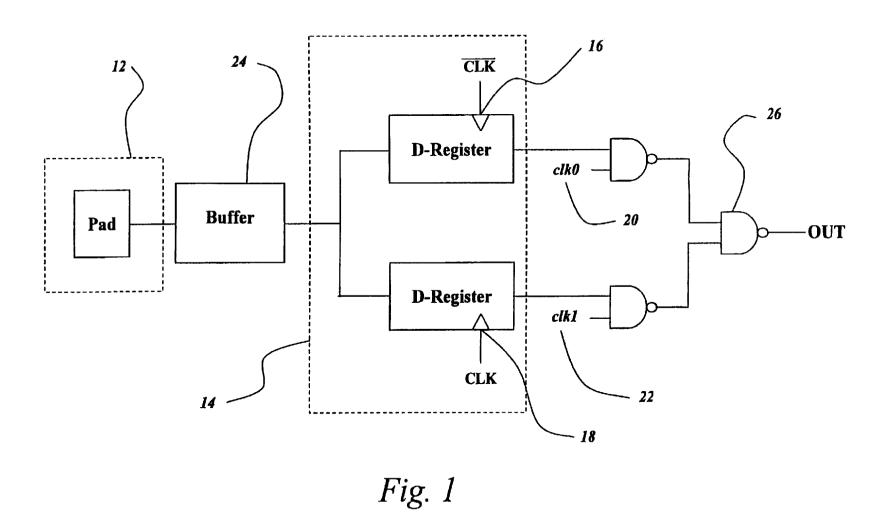

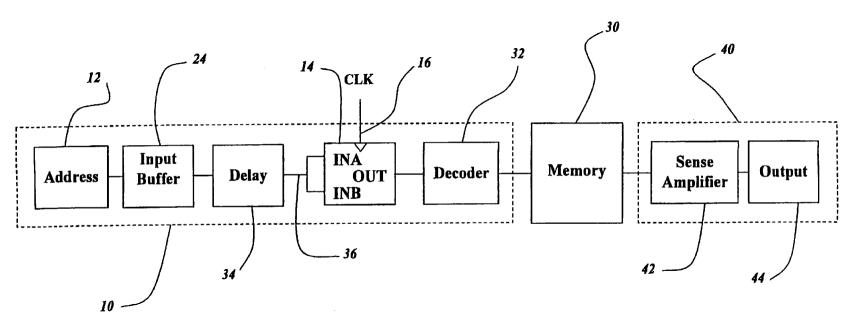

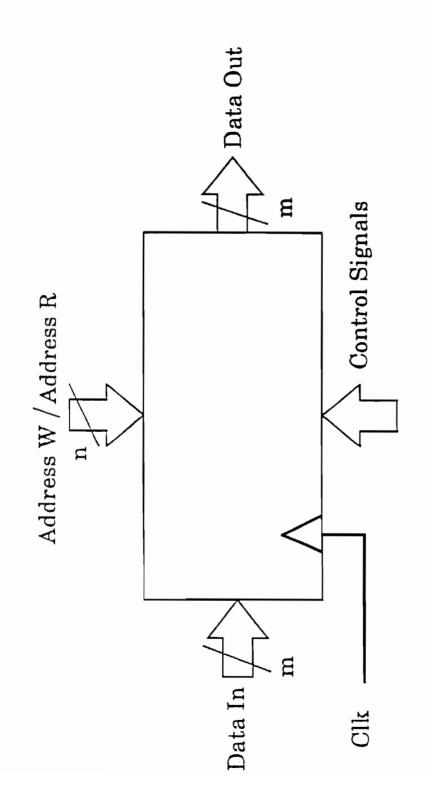

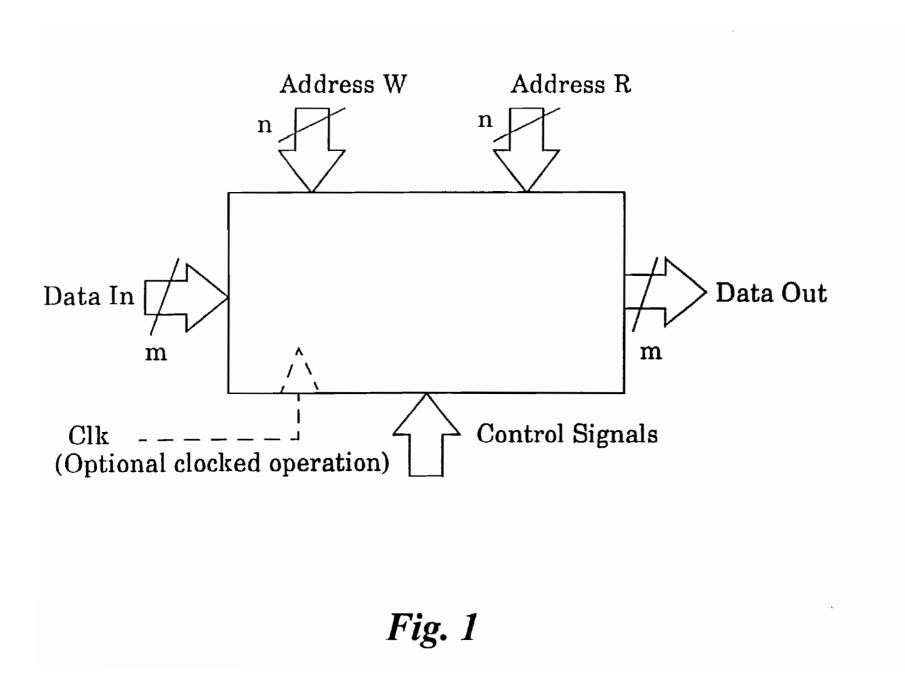

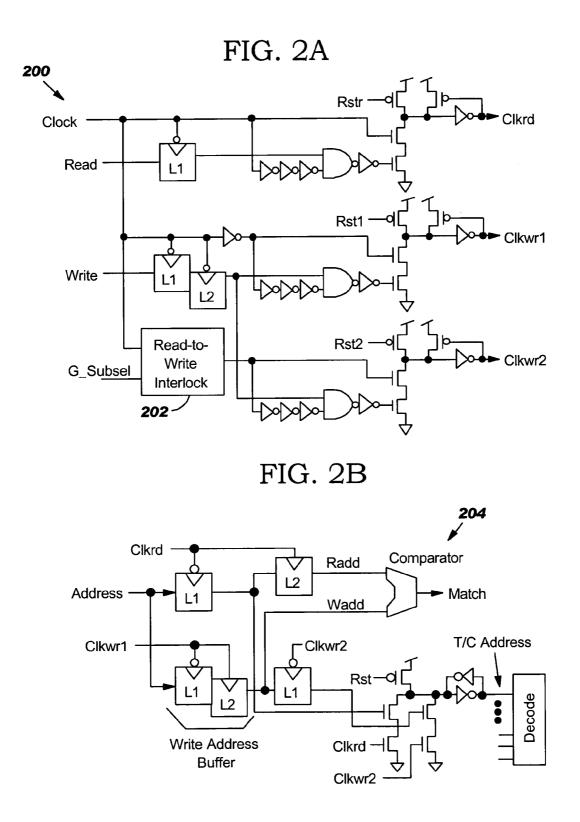

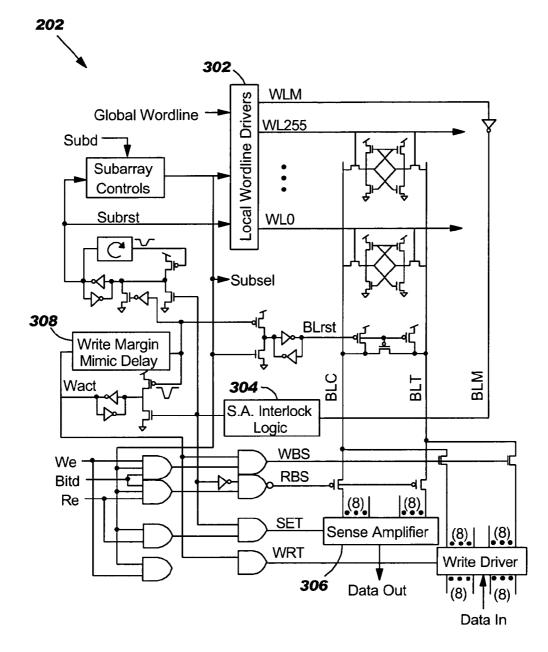

FIG. 1 shows an overview of an embodiment of the present address scheme;

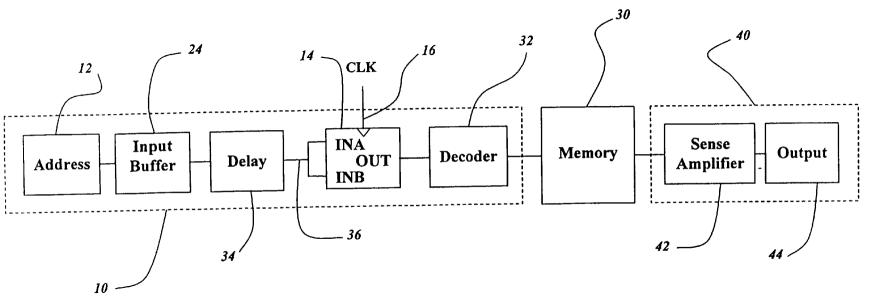

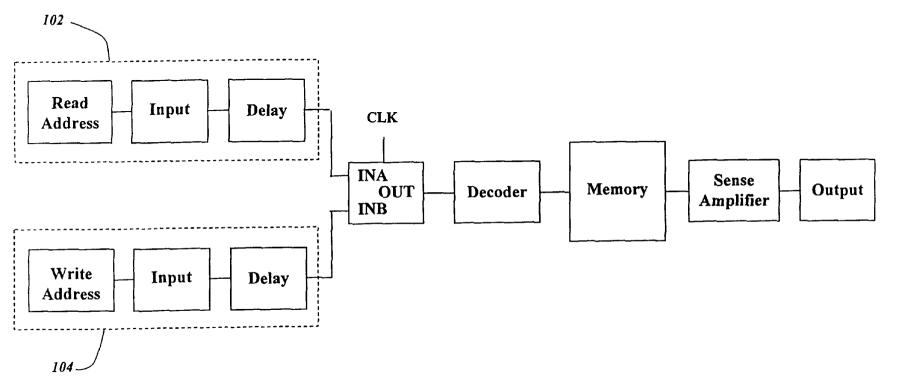

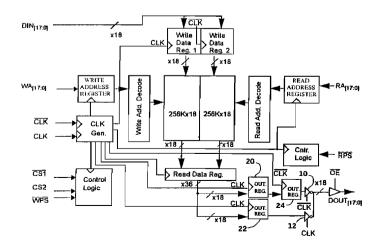

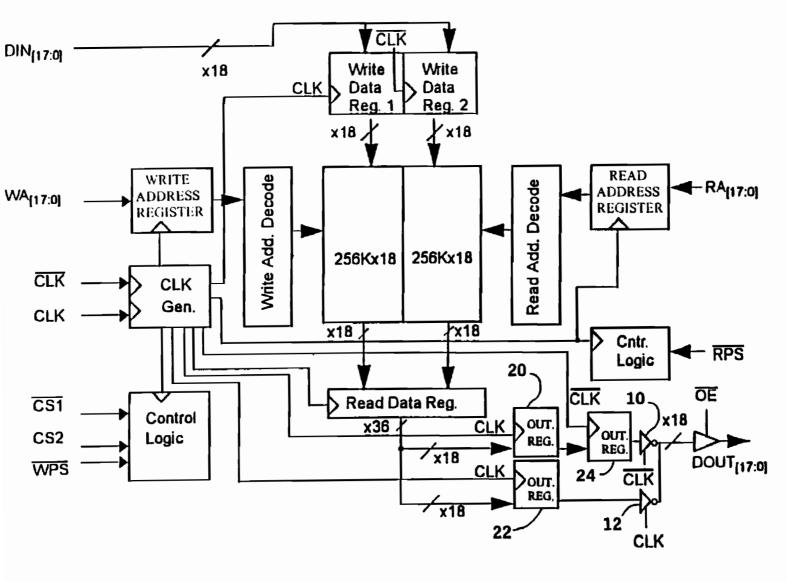

FIG. 2 shows an overview of a random access memory (RAM) architecture employing the address scheme shown in FIG. 1;

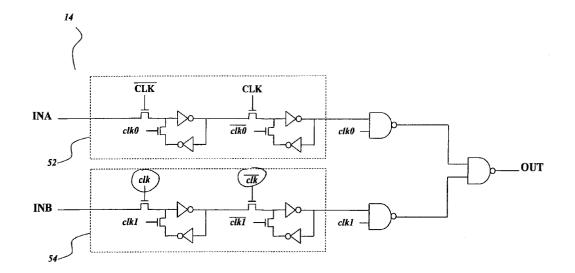

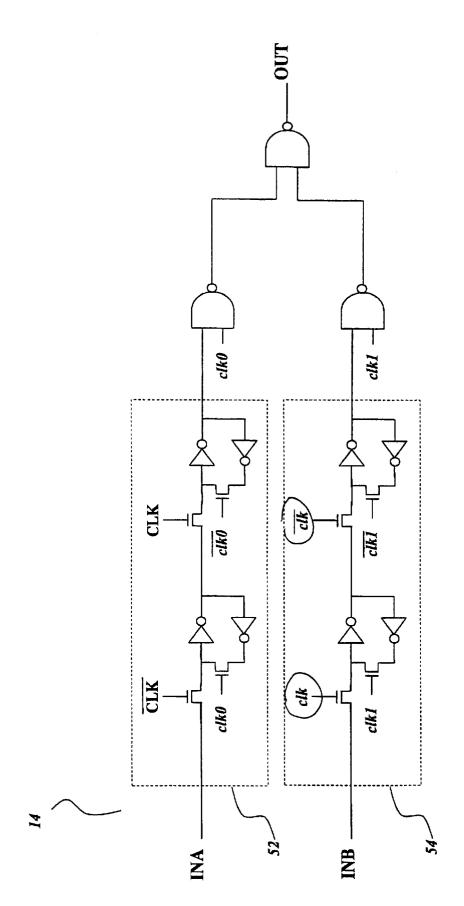

FIG. **3** shows a detailed schematic diagram of the address register shown in FIG. **1**;

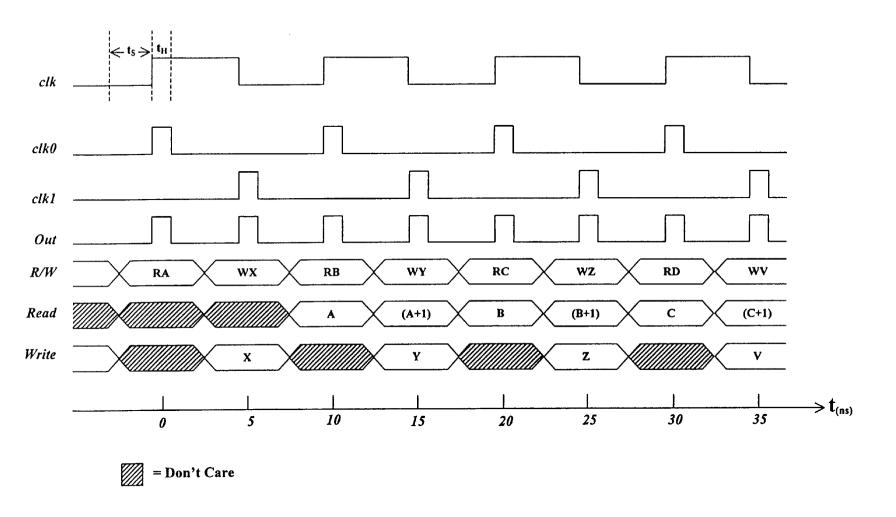

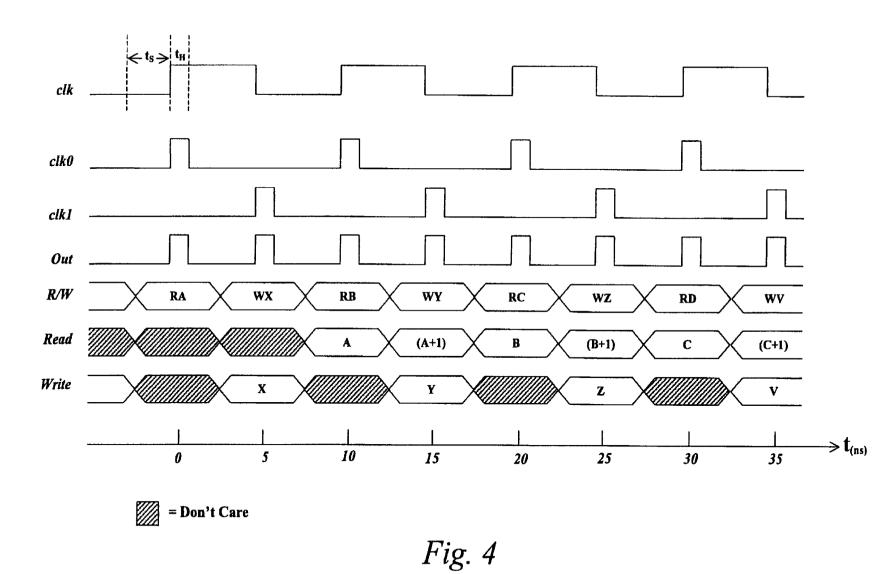

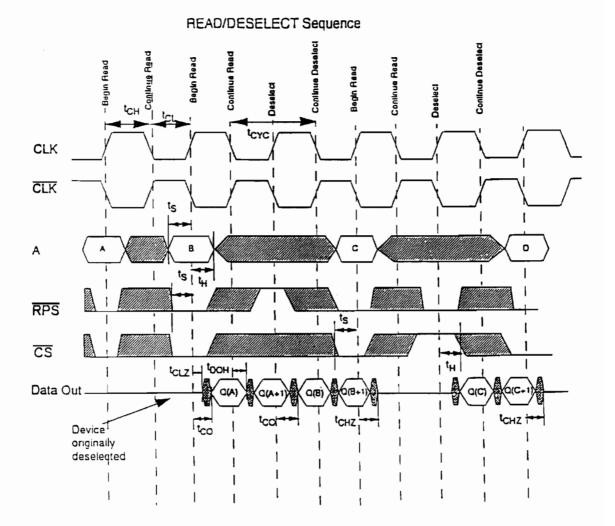

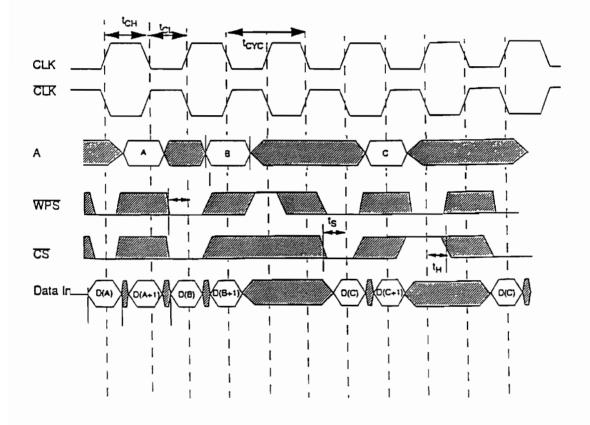

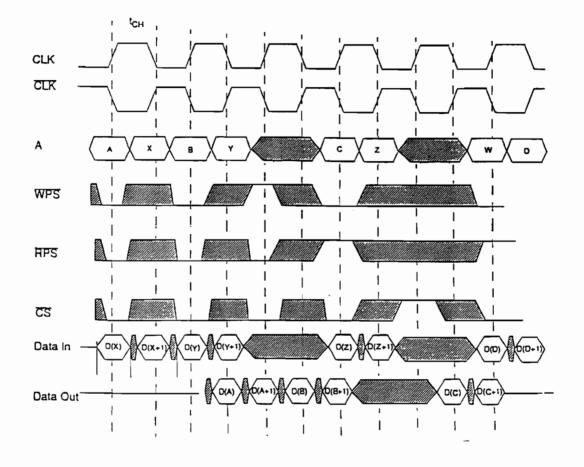

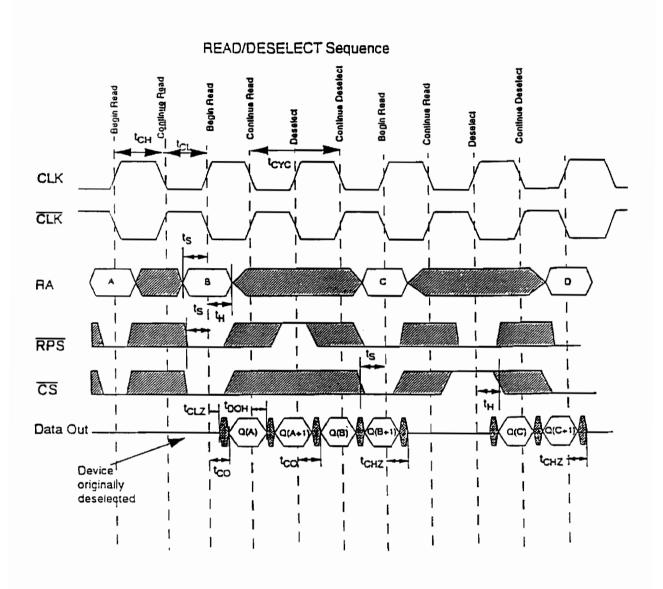

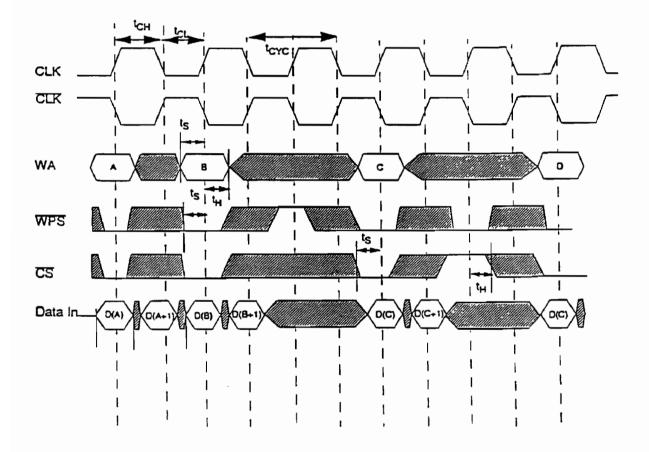

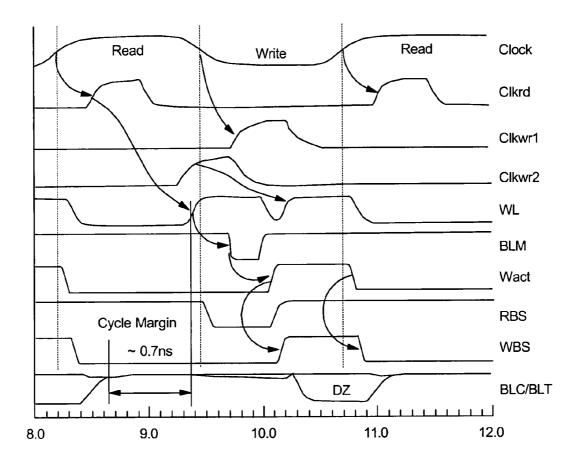

FIG. 4 shows various waveforms illustrating the relative timing of various signals in conjunction with exemplary read and/or write operations performed according to the invention;

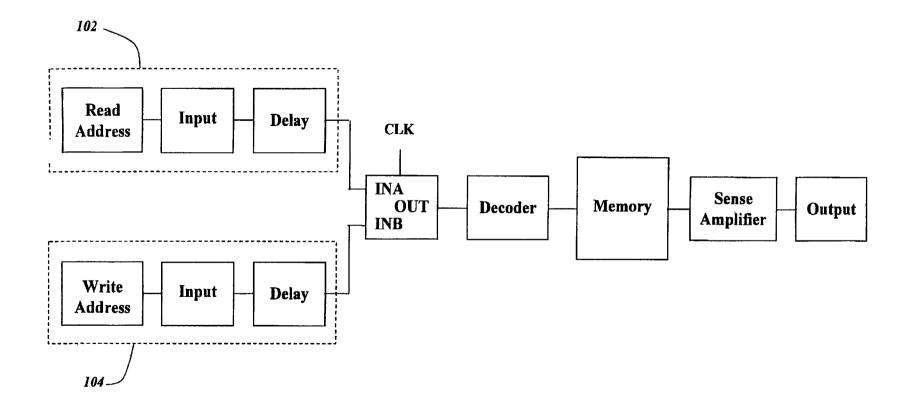

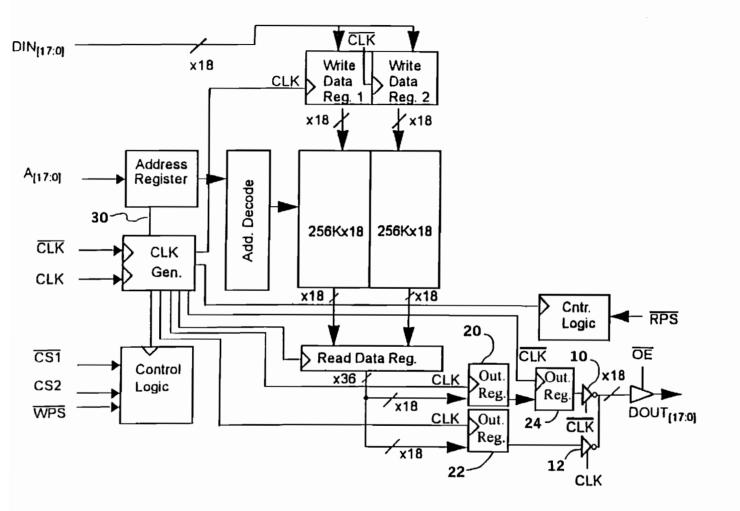

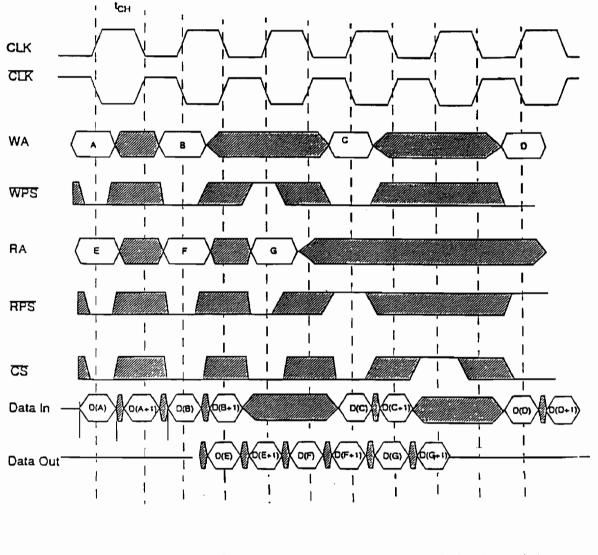

FIG. **5** shows an overview of a random access memory (RAM) architecture employing a second embodiment of the present address scheme;

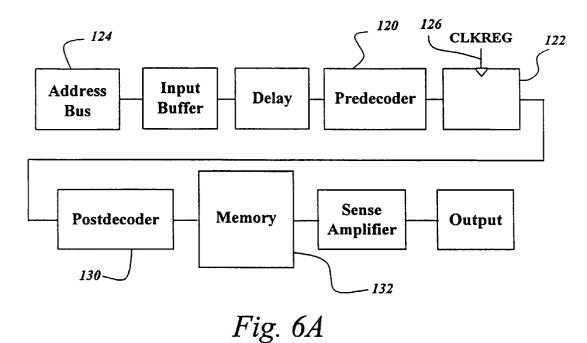

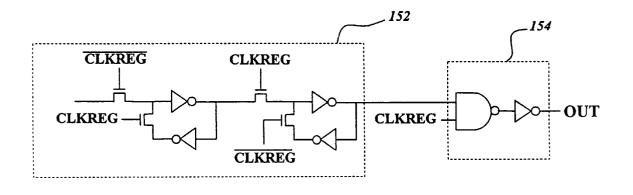

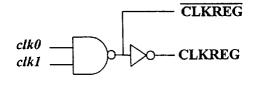

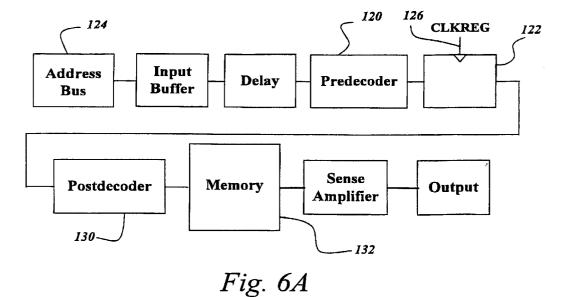

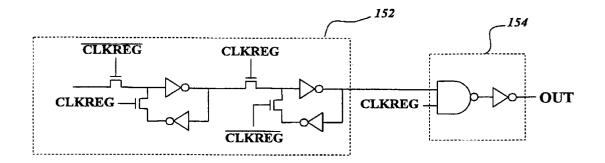

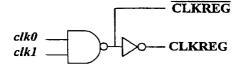

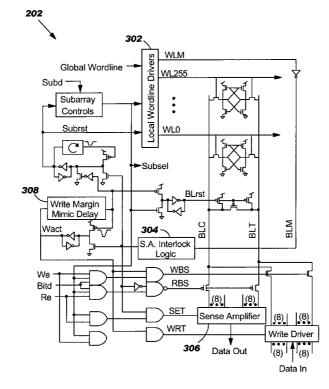

FIGS. **6A–6**C show an overview of a random access memory (RAM) architecture employing a third embodiment of the present address scheme (FIG. **6**A), a detailed schematic diagram of the address register shown in FIG. **6**A (FIG. **6**B), and an exemplary circuit configured to generate one or more pulses for latching address information in the address register shown in FIG. **6**B (FIG. **6**C); and

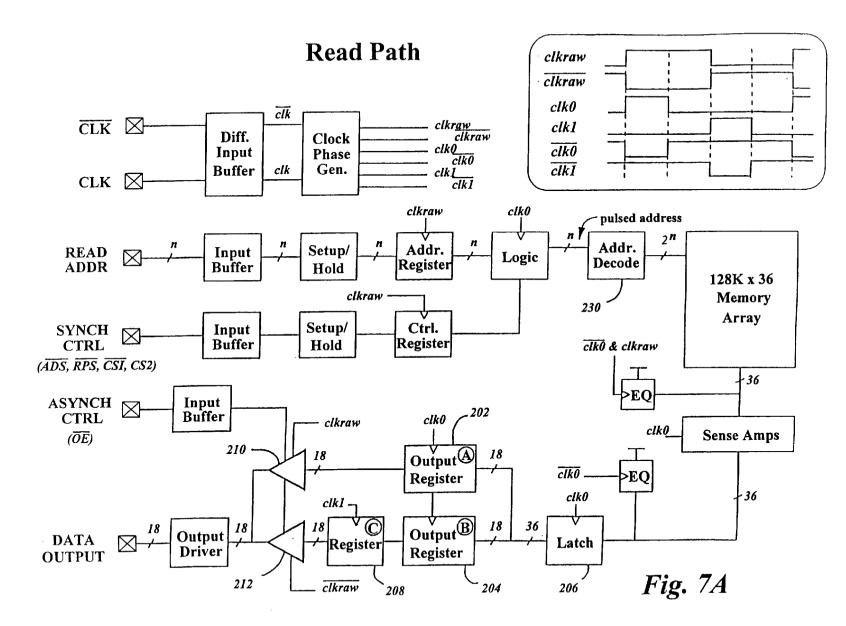

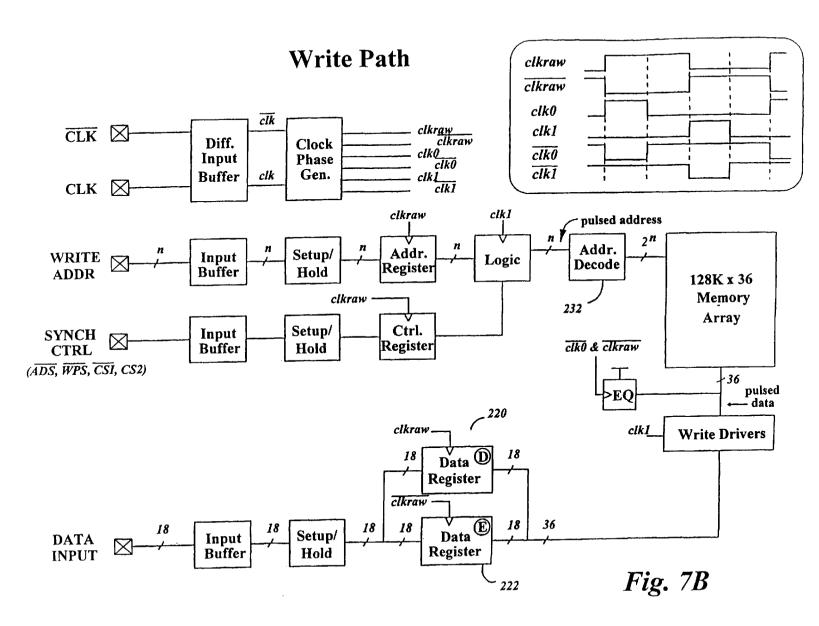

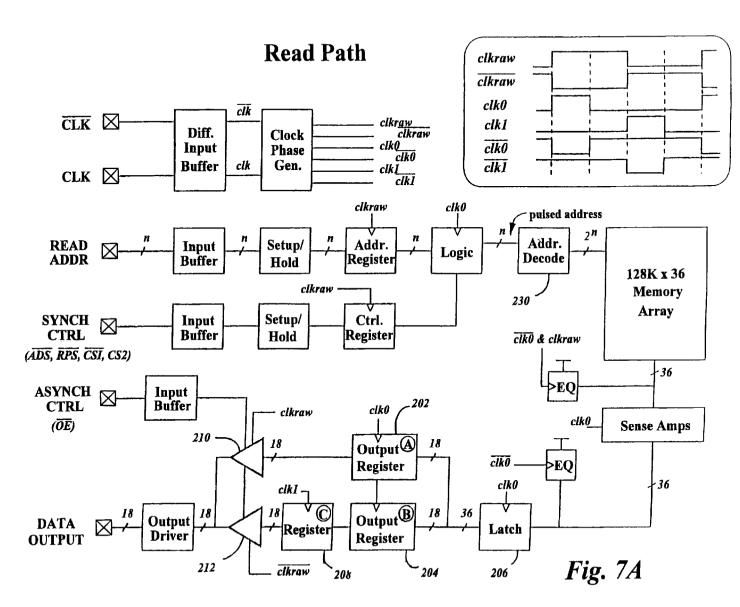

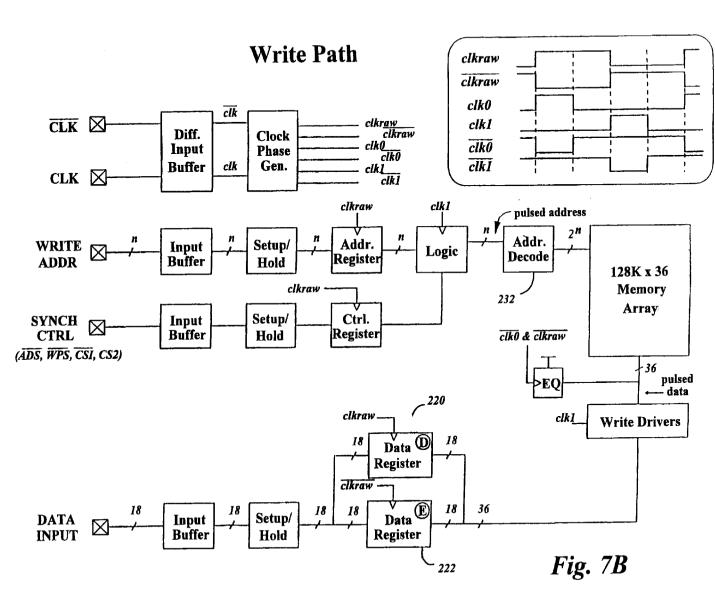

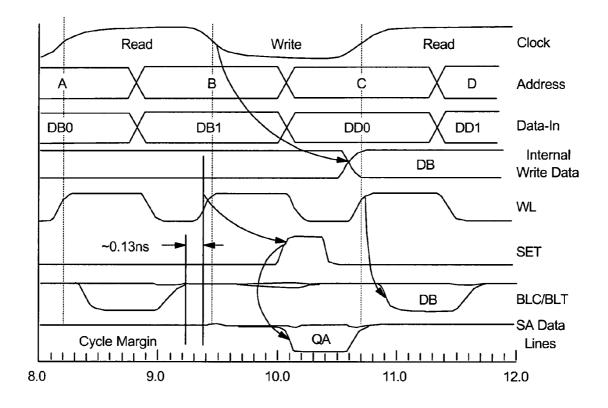

FIGS. 7A and 7B show an overview of a random access memory (RAM) architecture employing a fourth embodiment of the present address scheme, wherein FIG. 7A shows components useful for conducting one or more read operations, and FIG. 7B shows components useful for conducting one or more write operations.

It is to be understood that, in some instances, various aspects of the invention may be shown exaggerated or enlarged to facilitate an understanding of the invention, and in other instances, some aspects of the invention considered to be conventional may not be shown so as to avoid obfuscating more important aspects or features of the invention.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Detailed descriptions of the preferred embodiments are provided herein. It is to be understood, however, that the

present invention may be embodied in various forms. Therefore, specific details disclosed herein are not to be interpreted as limiting, but rather as a basis for the claims and as a representative basis for teaching one skilled in the art to employ the present invention in virtually any appro-5 priately detailed system, structure or manner.

In the present random access memory, each of the address bus, address register, data input bus, data output bus, and random access memory array may independently be n or m n bits wide, where n is an integer  $\geq 2$ , preferably  $\geq 4$ , and more 10 preferably  $\geq 8$ , and m is independently an integer  $\geq 2$ , preferably of 2-8, and more preferably of 2-4. In specific examples, n may be 8, 9, 16, 18, 32, 36, 64, 72, 128 or 144. The data input bus may receive data from an external source. In a preferred embodiment, each of the data input bus, data 15 output bus, and address bus is unidirectional (i.e., data flows in one direction only).

In the present invention, a "periodic signal" refers to any signal that has an oscillating waveform, the frequency of which may be predicted and/or controlled in accordance 20 with techniques known in the art, and that can be configured to control one or more circuit functions performed as part of a read operation or a write operation in a memory. The periodic signal may be configured to control one or more data transfer operations to or from a random access memory array in response to first and second transitions thereof, respectively, where the second transition occurs within the same periodic signal cycle as, and which may be complementary to, the first transition. Therefore, the memory may operate in a synchronous manner. For synchronous 30 operations, the periodic signal may be an internal or external clock signal, or a periodic control signal such as write enable or output enable. There may be more than one independent periodic signal controlling read, write, register and/or data pass gate functions (e.g., a clock signal and its complement). 35 Where appropriate and/or desirable, the periodic signals comprise a first clock signal and its complement. Alternatively, however, the periodic signal may comprise a pulse generated in response to a clock transition or, clock signal.

Accesses to and from the memory array, including transmission of address information along an address path to the array, may be controlled by a single input clock or a pair of differential input clocks (CLK/CLK\*, where a signal des- 45 random address in the random access memory in response to ignated "X\*" indicates the complement of the corresponding signal "X", similar to the signals in the Figures bearing an overstrike or "bar" designation). In the present application, a "complementary transition" may refer to either the same transition of complementary signals (e.g., the rising edges of 50both CLK and CLK\*), or opposite transitions of the same signal (i.e., the rising and falling edges of CLK). All synchronous timing may be referenced from the cross point of the differential input clock signals. Accesses can be initiated on any edge of any periodic signal (preferably on  $\ ^{55}$ the rising edge of a clock signal, assuming any other control signals are asserted at their active logic levels), but for ease and simplicity of logic circuitry, accesses to the array are initiated on the rising edge of the positive clock (CLK).

The present random access memory array may be configured to store and/or retrieve data at any random address therein. The address is defined by one or more signals on the address bus.

#### One (or More) Address Busses

As shown in FIG. 1, the present invention concerns a circuit comprising an address bus 12 providing random addresses for a random access memory (RAM), and a register 14 configured to store or receive (i) a first random address from the address bus in response to a first periodic signal transition 16 and (ii) a second random address from the address bus in response to a second periodic signal transition 18, wherein the second periodic signal transition occurs within the same periodic signal cycle as, and preferably is complementary to, the first periodic signal transition. The register may be further configured to transfer or output (i) the first random address to circuitry downstream from the register in the address path of the memory (e.g., a RAM array) in response to a first control signal 20 and (ii) the second random address in response to a second, independent control signal 22.

As shown in FIG. 1, the register may comprise two registers (each of which may independently comprise a D-type register, a T-type register, a master-slave register or a latch, but which preferably comprise a master-slave register or a D-type register) configured to store random address information from the address bus in response to the two complementary periodic signal transitions 16 and 18. Each register may independently further comprise a logic gate 26 configured to output or provide the random address information (or the complement thereof) from the register in response to a periodic signal or pulse 20 or 22. The periodic signals or pulses 20 and 22 may be independently the same as or different from (i) each other and/or (ii) the periodic signal(s) 16 and/or 18.

Where the circuit employs two registers, the circuit may further comprise a logic gate 26 configured to provide random address information or its complement (e.g., OUT) from the logic gates receiving the address information stored in the registers. Such logic gates are conventional and known to those skilled in the art, and may comprise and combination of transistors and/or logic elements providing a NAND or AND function (an "AND-type logic gate").

FIG. 2 shows an overview of a random access memory (RAM) architecture employing the circuit shown in FIG. 1. Thus, the present circuit may further comprise the random alternatively, a predetermined logic or voltage level of a 40 access memory 30 and circuitry operable to (i) read data into the random access memory array at the first random address and (ii) write data into the random access memory array at the second random address. The random access memory may further comprise a decoder 32 configured to activate the receiving the random address from the register. Address input path 10 may further comprise (i) an input buffer 24 configured to receive random address information from the address bus and provide the random address information to the register, and/or (ii) a delay element 34 interposed between the input buffer 24 and register 14. Delay element 34 may be configured in accordance with techniques and circuit elements known in the art to set up and hold the address information at node 36 for a length of time sufficient to enable register 14 to store or latch the address information.

> Where a decoder located downstream from the address register(s) fully decodes the address information, the length of time for which address information is set up and held (e.g., at node **36**) may be minimized. This allows for greater variations in the periodic signal duty cycle. One notorious limitation to maximizing data throughput in synchronous RAMs is the length of time one must allow for variability in the periodic signal duty cycle, a parameter that effectively 65 limits the maximum frequency of conventional clock circuits. In the present invention, practical limits to the data throughput rate may be determined by the set up and hold

30

35

40

window (e.g.,  $[t_S+t_H]$ ; see, for example, the CLK waveform in FIG. 4) and the pulse widths of the control pulses that latch address information and/or data into a register in the corresponding input or output path (e.g., clk0, clk1; see FIGS. 3, 4, 7A and 7B).

The width of a control pulse in the present invention may be, for example, from (1/p) to  $(1-\lceil 1/p \rceil)$  times the width of a half-cycle of the periodic signal (where p is, for example, from 1.1 to 10, preferably from 1.5 to 4). In the example shown in the waveforms inset into FIGS. 7A and 7B, p is 10 about 2. The set up and hold window in the present invention may be, for example, about [(1/q)+(1/r)] times the width of a half-cycle of the periodic signal, where q is, for example, from 0.5 to 10, preferably from 0.75 to 4, and r is independently from 1 to 20, preferably from 1.5 to 10). In the <sup>15</sup> example shown in FIG. 4, q is 1 and r is 4.

The circuitry operable to write data into the array at a random address may do so in response to at least one transition of the periodic signal. Similarly, the present random access memory may further comprise circuitry operable to read data from a random address in the array may do so in response to at least one transition of the periodic signal. The periodic signal transitions to which the read circuitry and write circuitry respond are preferably, but not 25 necessarily, complementary to each other. For example, when the memory comprises dedicated and/or independent data input and data output ports (see the copending provisional applications identified as Attorney Docket No. CD98022 and/or Attorney Docket No. CD98023), each transition of the periodic signal may be independently designated as a read operation or a write operation. In fact, when the memory comprises two or more independent address registers (and the data busses, data registers and memory array all have the same width), each transition of the periodic signal may be independently designated as a read operation, a write operation or both read and write operations.

The random access memory may further comprise an output path 40, which may comprise one or more sense amplifiers 42 and one or more data outputs 44. Each data output 44 may comprise a data bus and an output pad. The output data bus may be unidirectional.

Referring now to FIG. 3, an exemplary address register operable in the circuits of FIGS. 1 and 2 is shown. The  $_{45}$ register may comprise two or more subregisters 52 and 54, each of which may be a D-type or master-slave-type register. The address bus provides random address information one or more inputs to register 14 (e.g., INA and INB). Address information may be received by and/or pass into subregisters 50 52 and 54 in response to first and second periodic signal transitions, respectively (e.g., CLK\* and CLK). As shown in FIG. 3, the first and second periodic signal transitions may be complementary to each other.

Subregister 52 stores the random address information in 55 response to a first periodic signal transition or pulse (e.g., CLK0) and outputs the random address information in response to a second periodic signal transition or pulse (e.g., CLK0\*). As shown in FIG. 3, the periodic signal transitions or pulses that result in storing and outputting the random 60 address information may be complementary to each other. When pulse generated in response to a rising or falling edge of a periodic signal such as a clock (see, e.g., clk0 and/or clk1 in FIG. 4) controls receive, store, latch and/or output functions in a register, the receive, store, latch and/or output 65 function may be considered to be at least indirectly responsive to a periodic signal transition. Subregister 54 operates

in a manner similar to subregister 52, but in response to different periodic signal transitions or pulses (e.g., CLK1 and CLK1\*).

In one embodiment, the register stores two read addresses or two write addresses in a single cycle of the periodic signal (e.g., CLK). For example, register 14 stores the first random read address from the address bus in response to a first control pulse (e.g., CLK0) and the second random read address from the address bus in response to a second control pulse (e.g., CLK1). The control pulses may be generated in response to successive transitions of the periodic signal and/or its complement, such that the control pulses are in effect generated in response to complementary transitions of the periodic signal in a single cycle (see also waveforms CLK, clk0 and clk1 in FIG. 4).

Thus, the present circuit may further comprise a pulse generator configured to generate a first pulse in response to at least one of the first and second transitions of the periodic signal, the first pulse latching at least one of the random addresses into the register. The pulse generator may be further configured to generate a second pulse in response to at least one of the first and second transitions of the same or different periodic signal, the pulse latching at least a second one of the random addresses into the register.

#### Multiple Registers

In a further embodiment, the present circuit may comprise three or more registers. In such a case, the periodic signal and/or pulse generating logic may further comprise circuitry to provide multiple periodic signals and/or pulses, each offset from the other by a predetermined phase delay in accordance with known techniques and circuits. For example, in an embodiment comprising four registers, conventional phase delay circuitry can generate a second periodic signal phase-offset from the first clock by 90° or t/4 ns, where t is the length of the clock cycle in nanoseconds. Additional control pulses (e.g., clk2 and clk3) can be generated from the edges or transitions of this second, phaseoffset clock to control third and fourth address registers in the manner described above. Periodic signals complementary to the second, phase-offset clock and its corresponding control pulses can control other functions in the third and fourth registers, and elsewhere in the RAM for circuitry associated with the third and fourth registers, in a manner similar to that described both above for first and second registers and herein below for associated circuitry.

#### Transferring Data To and From the Array (Reading and Writing)

FIG. 4 shows the sequence of data transfer events occurring during read and write operations. In FIG. 4, the letters "A", "B", "C", etc., refer to addresses in the RAM array and the corresponding word or words to be written to or read from such addresses. The terms "RA", "RB", etc., refer to a read function at address A, B, etc. The terms "WX", "WY", etc., refer to a write function at address X, Y, etc. The terms "clk@" and "clk1" refer, for example, to the control pulses that latch address information in address register 14 as shown in FIG. 3. the signal "OUT" refers to the output signal from the address register(s) and associated logic circuitry (if present) shown, for example, in FIGS. 1-3. The term "R/W" refers to read or write address information that may be stored in the address register(s) shown, for example, in FIGS. 1-3. Although the clock pulse CLK shown in FIG. 4 is a 125 MHz clock with a cycle time of 4 ns, a clock of any frequency (e.g., from 10 kHz to 10 GHz, preferably from

200 kHz to 4 GHz, more preferably from 1 MHz to 1 GHz) may be used. Examples of suitable clock frequencies include 12.5 MHz, 20 MHz, 25 MHz, 33 MHz, 50 MHz, 66 MHz, 75 MHz, 83 MHz, 100 MHz, 125 MHz, 133 MHz, 150 MHz, 166 MHz, 183 MHz, 200 MHz, 250 MHz, 333 MHz, 5 etc.

Referring now to FIG. 4, at time t=0 ns, address A is latched or written into the address register from the address bus by pulse clk0. As described above, pulse clk0 may be generated from the positive clock CLK transition from LOW 10 to HIGH. Address A is present on the address bus at a time about t<sub>s</sub> ns before the rising CLK transition. This is commonly known in the art as the "setup time". Address A is maintained on the address bus for a period of time of about  $(t_s+t_H)$  ns (the "setup and hold time"; see, e.g., waveform 15 CLK in FIG. 4). For a read operation, a read port select signal (see, e.g., "RPS\*" in FIG. 7A) may be asserted briefly (and preferably while the periodic signal(s) CLK and/or CLK\* is/are transitioning at t=0 ns). The next rising transition of the periodic signal CLK, optionally in conjunction 20 with a control pulse (e.g., clkØ and/or clkØ\*), senses the data at address A and latches the corresponding data word(s) from address A in the array through one or more (optional) latches 206 into one or more output registers (e.g., 202 and 204 in FIG. 7A). 25

For either two n-bit-wide data words or one 2n-bit-wide data word stored in the array but output on an n-bit-wide data output bus, the HIGH logic level of CLK resulting from this initial transition at t=0 ns enables output buffer **210** and outputs a first n-bit-wide data word from address A to the 30 data output bus. For n-bit-wide circuitry, a complementary transition of the periodic signal (e.g., a falling CLK transition or a rising CLK\* transition) may then latch a second n-bit-wide data word from output register **204** into a shadow register (e.g., register **208** in FIG. 7A). The LOW logic level 35 of CLK resulting from this complementary CLK transition enables output buffer **212** and outputs the second n-bit-wide data word (e.g., "(A+1)", "(B+1)", "(C+1)", etc.) onto the data output bus and the data output pad(s).

In FIG. 4, at time t=2 ns, address X is latched or written 40 into the address register from the address bus by pulse clk1. As described above, pulse clk1 may be generated from either (i) the negative clock CLK\* transition from LOW to HIGH or (ii) the positive clock CLK transition from HIGH to LOW. Address X is also present on the address bus at a time 45 about  $t_s$  ns before the rising CLK transition. Address X is also maintained on the address bus for a period of time of about  $(t_s+t_H)$  ns (the "setup and hold time"; see, e.g., waveform CLK in FIG. 4). For a write operation, a write port select signal (see, e.g., "WPS\*" in FIG. 7B) may be asserted 50 briefly (and preferably while the periodic signal(s) CLK and/or CLK\* is/are transitioning at t=2 ns). This complementary transition of the periodic signal CLK/CLK\*, optionally in conjunction with a control pulse (e.g., clk1 and/or clk1\*), writes data stored in one or more data input 55 registers (see, e.g., 220 and 222 in FIG. 7B) into the array at address X.

More specifically, a rising periodic signal CLK transition latches an n-bit-wide data word D(X) on the Data In bus into the first write register **220**. Alternatively, for 2n-bit-wide 60 circuitry, the rising transition of the positive periodic signal CLK latches a single 2n-bit-wide data word in a single 2n-bit-wide data input register. Similar but complementary to the read operation described immediately above, address X is latched or written into the address register from the 65 address bus during the second, falling CLK transition from HIGH to LOW. The new address signal, or address transition

from A to X, occurs at least about  $t_s$  ns before the crossover of the differential external clocks CLK and CLK\* (see FIGS. 4 and 7B). The falling transition of the CLK pulse, which may be sent on a clock generator-to-address register bus, enables the address register to store the X address that is on the address bus after the address transition.

#### Advantages

The RAM may access two data words with each read operation on the same clock edge as that which latches the read address. For example, referring to FIG. 7A, the first or lower word of data may be driven onto the output data bus on the clock logic level resulting from the single clock edge that latches the data in the corresponding output register, provided any applied output control signal (e.g., an output enable signal OE) is asserted in an enabling state (e.g., LOW). On the subsequent clock transition, the second or higher order data word may be driven onto the output data bus on the clock logic level resulting from the clock transition that latches the second data word in the shadow register 208, provided any applied output control signal remains asserted in an enabling state. In this configuration, all data may be available, for example, as soon as 5.5 or 6 ns after a clock rise (assuming a 125 MHz clock signal), thus providing a read operation with as little as one cycle of latency.

On the same transitions of the subsequent clock cycle, the next data word(s) stored in the array is/are latched in the output register(s), then driven through one or more (threestate) output buffers onto the data output bus/pads on the same clock logic levels as before. Read accesses can be initiated, for example, on every rising edge of the positive clock. Doing so will "pipeline" the data flow such that data is transferred out of the device on every rising and falling edge of the clock.

When deselected (e.g., in a multiple-RAM system configuration), the present RAM may first complete the pending read transactions. Synchronous internal circuitry may automatically three-state the outputs following the next rising edge of the positive clock. This will allow for a seamless transition between a port in the present RAM and any external device (including without limitation a second RAM according to the invention) without the insertion of wait states.

The input and output ports in the present RAM architecture (e.g., DATA OUTPUT in FIG. 7A and DATA INPUT in FIG. 7B) may operate independently of one another. One can read or write to any location in the memory array, regardless of the transaction address on the other port. Should the input and output ports access the same location on the same cycle of the periodic signal, the information presented to the data inputs may be forwarded to the data outputs (by, e.g., conventional bypass logic circuitry responsive to a control signal generated in response to an ANDtype logic comparison of the read and write addresses), or alternatively, the data stored in the output register may first be output on the data output bus, then the same location written with the new data.

#### Two (or More) Address Busses

In a further embodiment, the present invention may comprise first and second address input paths **102** and **104**, as shown in FIG. **5**. More specifically, the circuit may further comprise a second address bus providing (i) a third random address in response to a first transition of the same or different periodic signal and (ii) a fourth random address in

response to a second transition of the same or different periodic signal; and a second register configured to store (i) the third random address from the second address bus in response to a third control pulse and (ii) a fourth random address from the second address bus in response to a fourth control pulse different from the third control pulse, the third and fourth control pulses being the same as or different from the first and second control pulses. Such a circuit may also further comprise a first and a second input buffer configured to receive first and second random address information from 10 the first and second address busses, respectively, and to provide the first and second random address information to the first and second

The present address bus and/or circuit may comprise a read address bus and an independent write address bus. In 15 such a case, the register may comprise (a) a read register configured to store (i) first random read address information from the read address bus in response to a first transition of a first periodic signal and (ii) second random read address 20 information from the read address bus in response to a second transition of the first periodic signal, and (b) a write register configured to store (i) first random write address information from the write address bus in response to a first transition of a second periodic signal and (ii) second random write address information from the write address bus in <sup>25</sup> response to a second transition of the second periodic signal, the first and second periodic signals being the same or different.

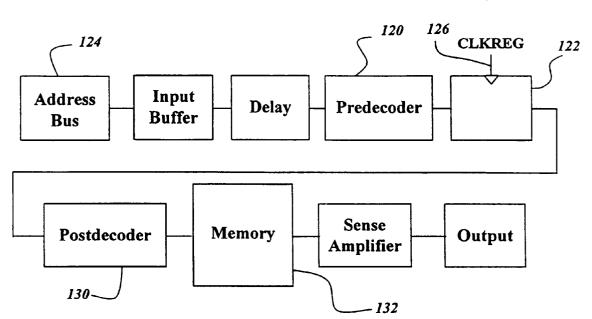

#### Predecoding

In a further embodiment, as shown in FIG. 6A, the present invention may further concern a predecoder 120 configured to at least partially decode the random address information from the address bus 124 prior to storing the at least partially 35 decoded random address information in the register 122. Consequently, the register may be configured to store (i) a first at least partially decoded random address from the address bus in response to a first periodic signal transition (e.g., at input 126) and (ii) a second at least partially decoded random address from the address bus in response to a second periodic signal transition, wherein the second transition is complementary to the first transition. The address input circuit and/or RAM may also further comprise a postdecoder 130 configured to activate the random addresses in the RAM array 132 in response to receiving the random addresses from the register.

Because some decoding is done prior to synchronously storing the address information, this embodiment may maximize the amount of time available to write data to and/or 50 read data from the array. Maximizing the array "cycle time" (i.e., the amount of time to write data to and read data from the array) provides opportunities to increase wordline and/or bitline recovery times, thus reducing power and/or current consumption. It may also permit one to employ a larger array 55 without requiring additional and/or more sophosticated logic circuitry, and/or to implement pulsed or self-resetting logic.

Suitable descriptions and examples of predecoder and postdecoder circuitry can be found in copending application Ser. No. 08/575,554 (entitled, "Method and Apparatus for Reducing Skew Among Input Signals Within an Integrated Circuit," filed Dec. 20, 1995) and in copending application Ser. No. 08/575,555 (entitled, "Method and Apparatus for Reducing Skew Among Input Signals and Clock Signals Within an Integrated Circuit," filed Dec. 20, 1995; aban-65 doned in favor of continuing prosecution application Attorney Docket No. 016820.P128C, filed on Oct. 30, 1997). For