EE421L Project: High Speed Digital Receiver

Report Due Date:

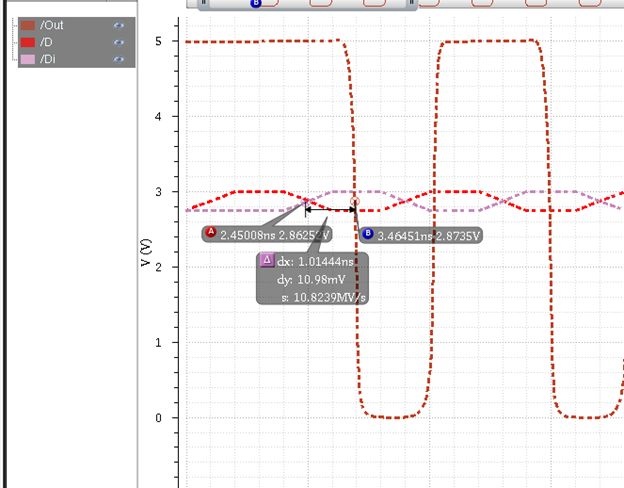

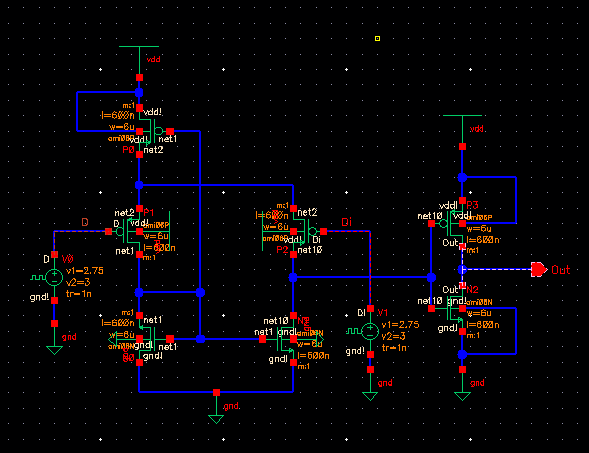

Note that when output approach to ground, there is an offset, to get rid of that offset, we could combine both the NMOS and PMOS version.

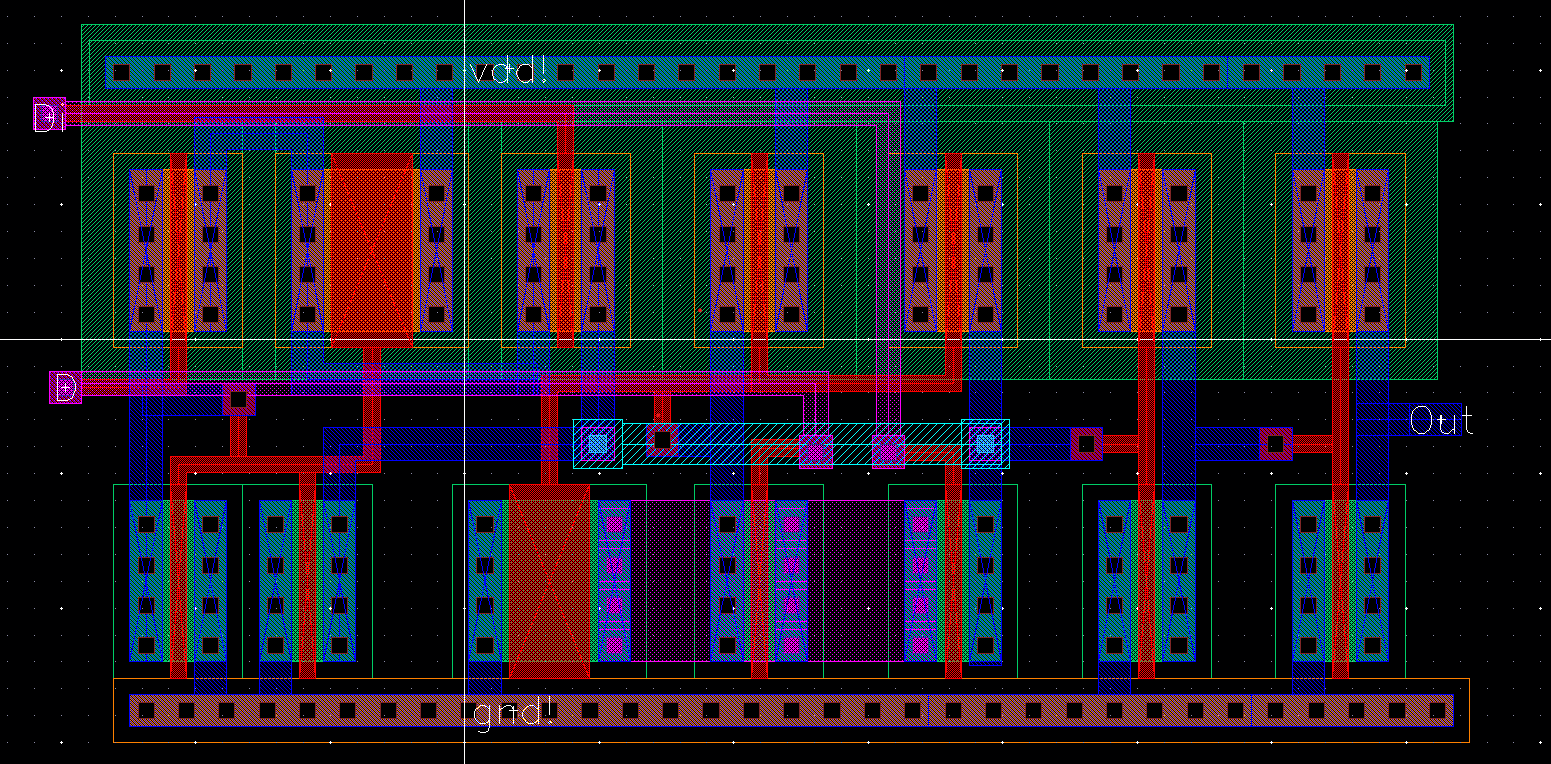

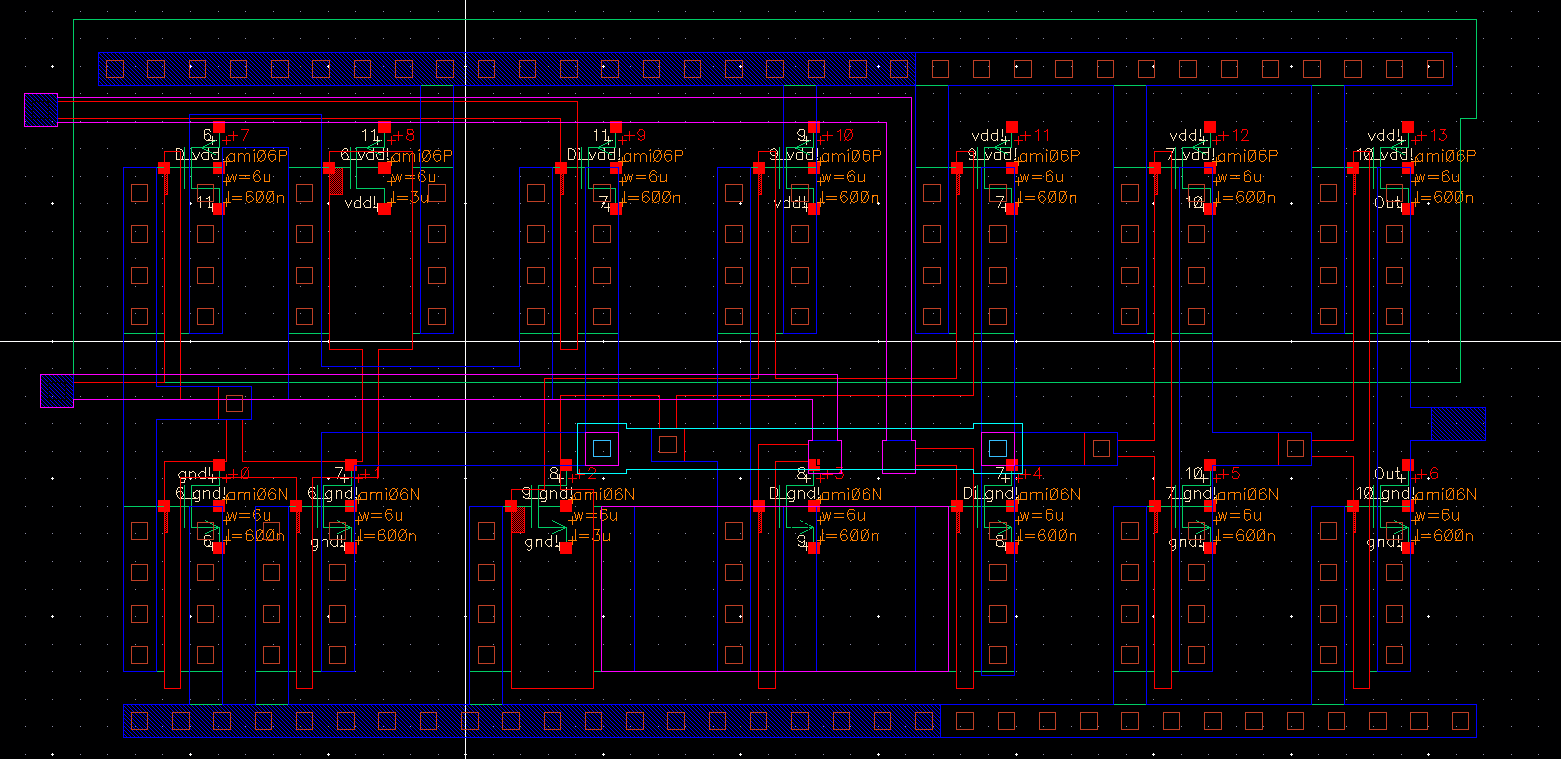

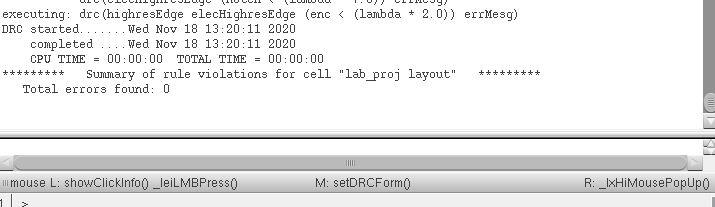

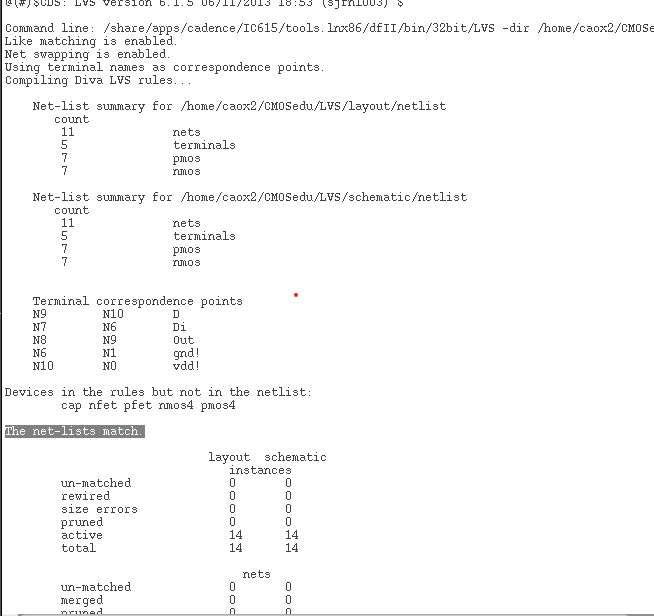

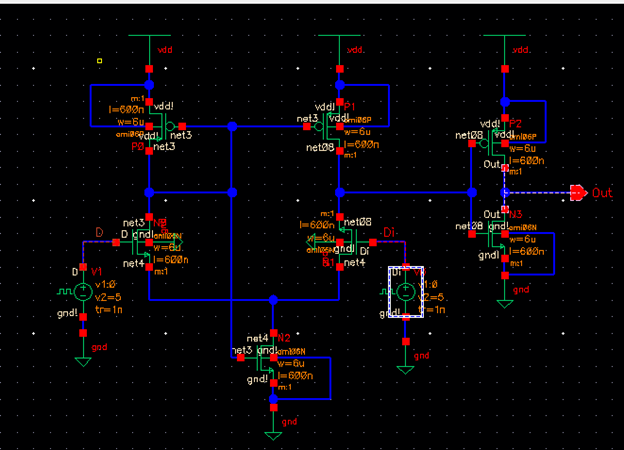

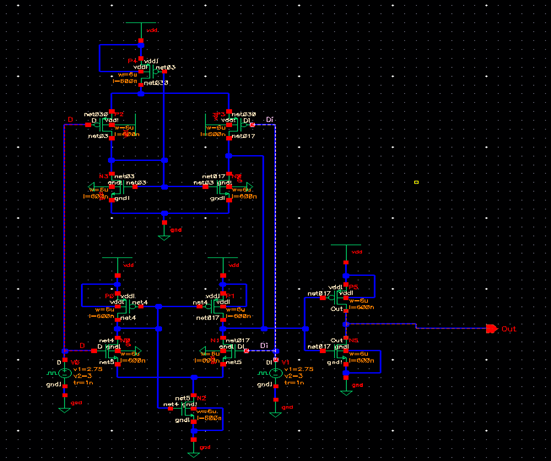

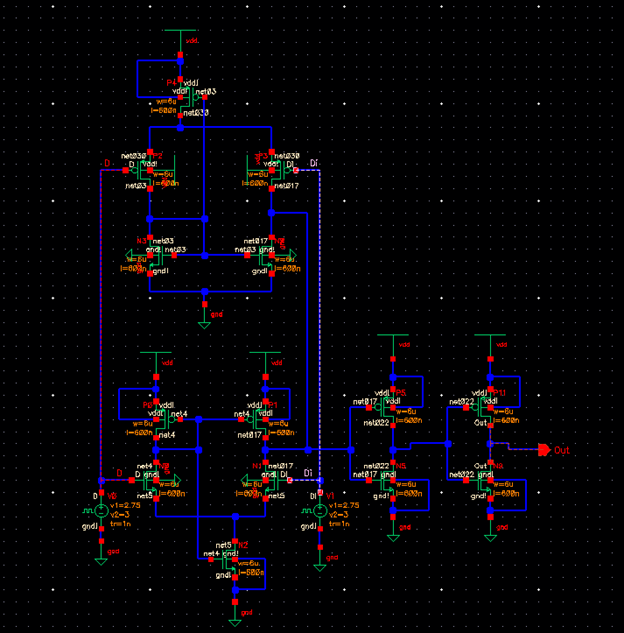

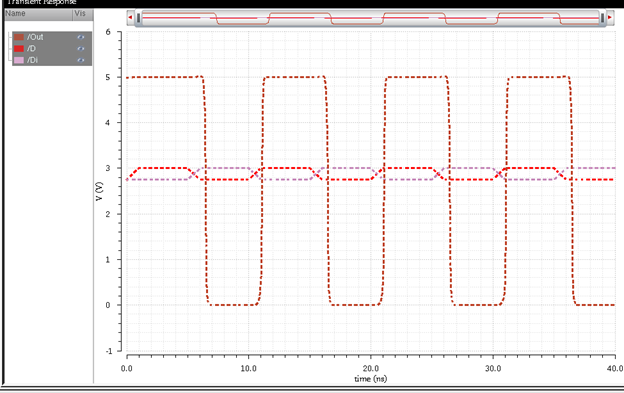

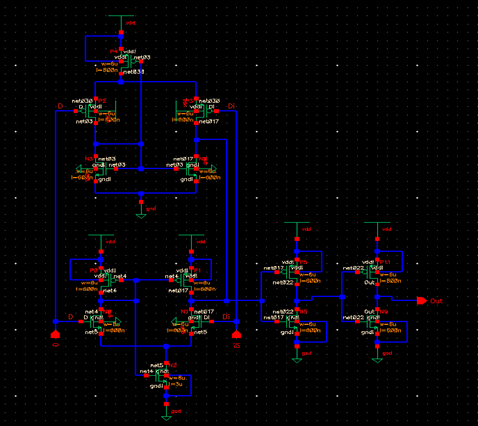

Here is the combined and the final version of the circuit.

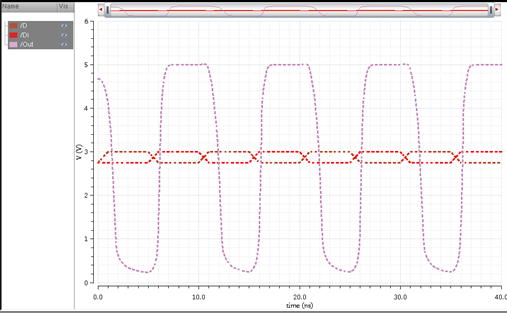

The output is not perfectly at Vdd or ground, so I added another inverter to the output, so it will square the output and to get the correct logic, that is, when D > Di, Out = 1, and 0 otherwise.

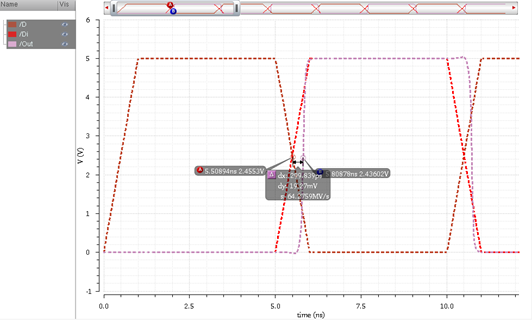

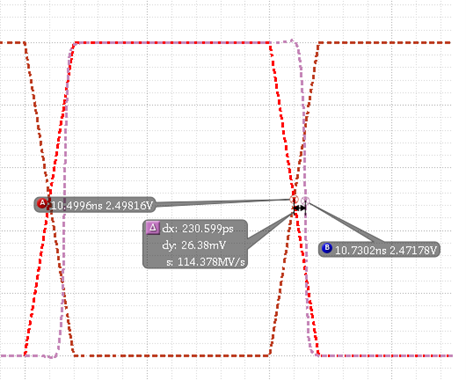

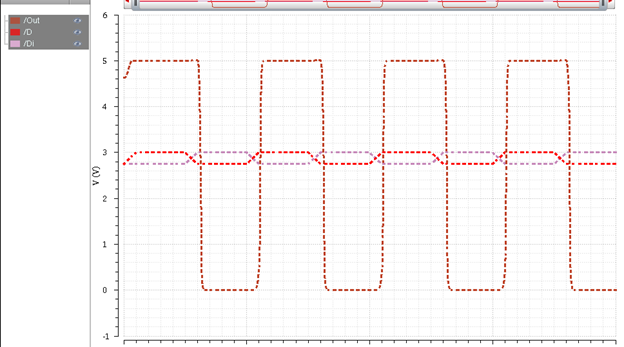

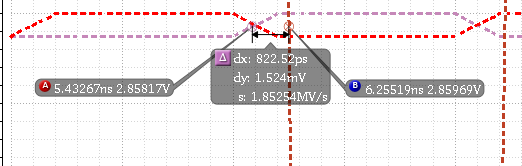

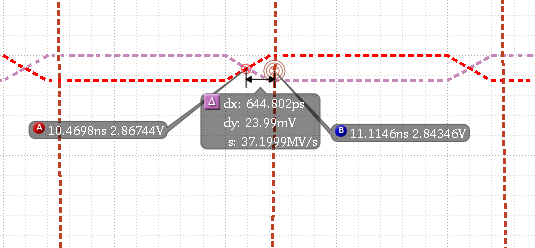

The propagation high to low delay is around 823 ps, and low to high is around 645 ps.

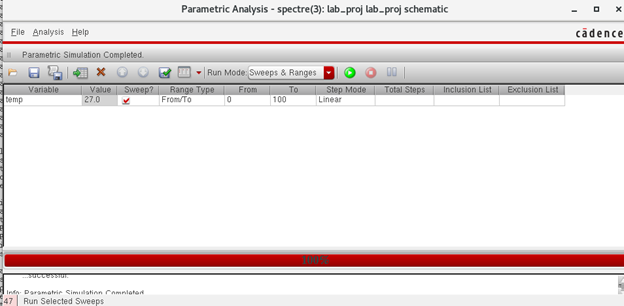

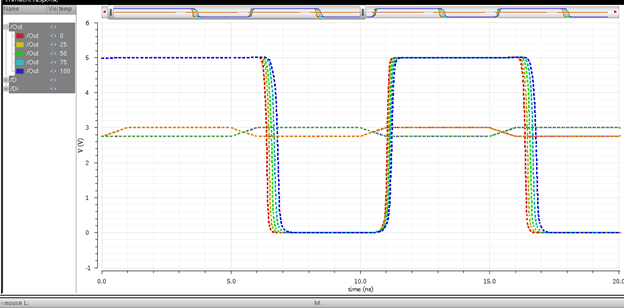

Since I was using the 6u/0.6 MOSFETs, whereas 0.6u is the minimal length for C5 process, which implies that this design would use more power. To reduce the power usage, in the meantime, for the circuit to still be fast, we can modify the size of the bottom NMOS and the top PMOS, in other words, we can use a longer L or shorter W to reduce the power, but in return, the circuit gets slower.

Power Dissipated can be calculated by:

P_avg = Vdd * I_avg = C_Tot * Vdd ^ 2 * f_clk. From this equation, we know that power is related to the input frequency and the total capacitance of the circuit, in other words, the size of the transistaors will also affect the power consumption.

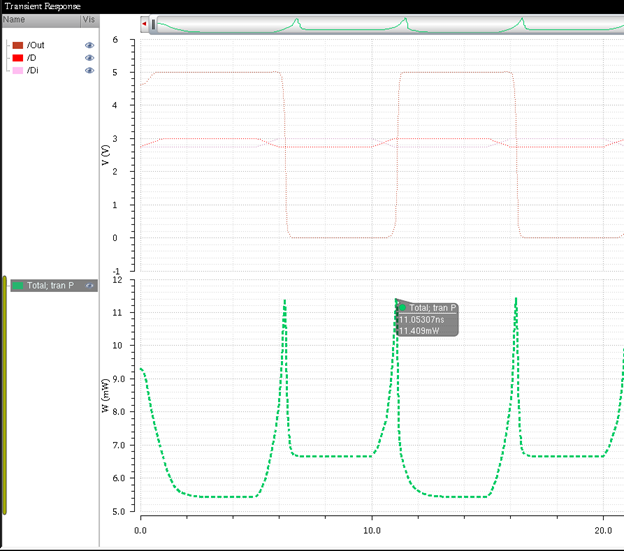

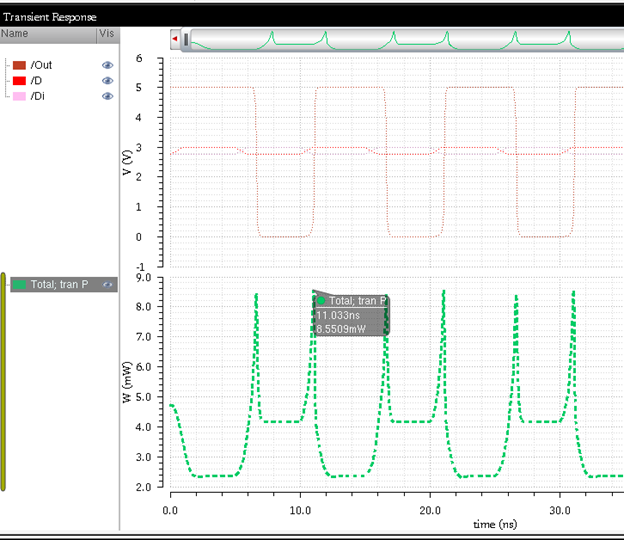

Here is the power for size of 6u/0.6u:

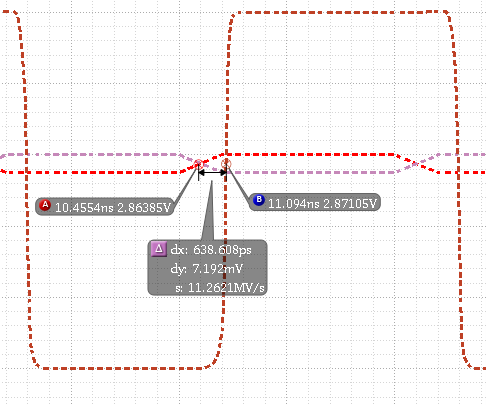

Size of 3u/3u:

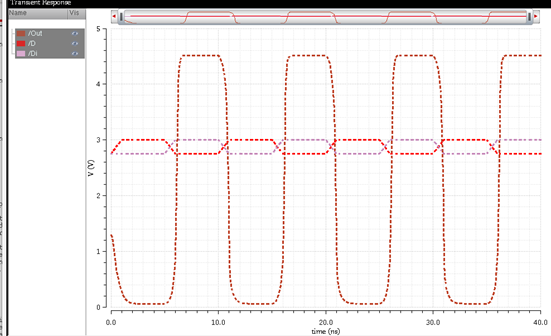

The propagation high to low delay is around 1.1 ns, and the low to high is around 661 ps.

For my design, I wish to have delay less than the rise time and the fall time of the input, in this case, 1 ns, so I want it to be litter bit faster.

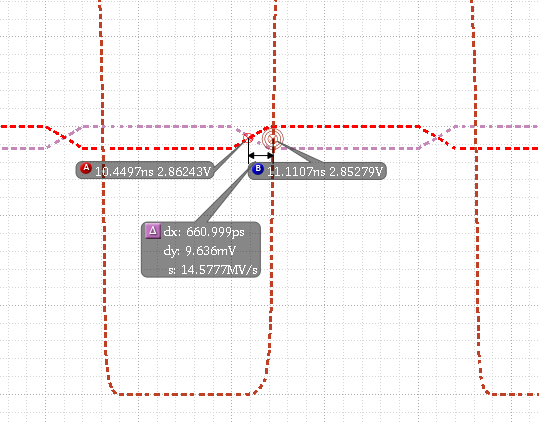

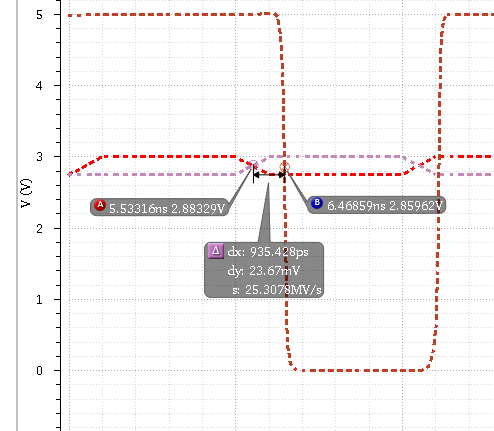

Size of 6u/3u:

Power for size of 6u/3u:

The propagation high to low delay is 935 ps, and thhe low to high is 639 ps. Both met my desired values, so this is going to be my final design.

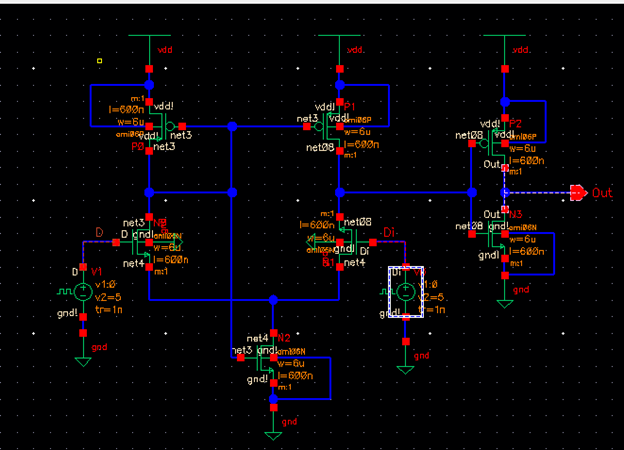

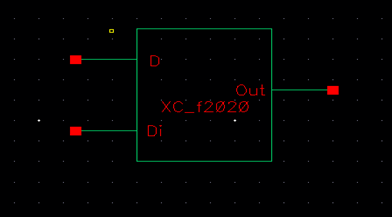

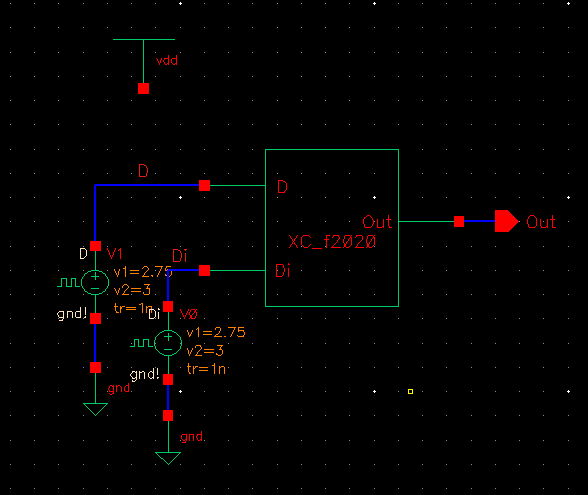

Next, I'm going to simulate my circuit to see what are the limatation of the circuit. Here is the symbol for the digital receiver and a circuit I'm going to use for simulation.

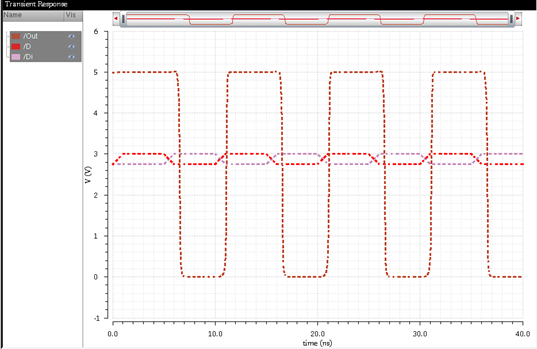

When D = 5V, Di = 0V, V_diff = 5V at 250Mbits/s:

From the above simulation result, I know that my design works with high V_diff.

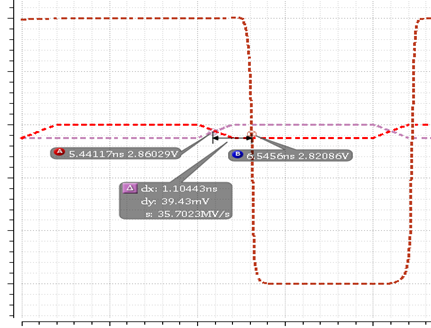

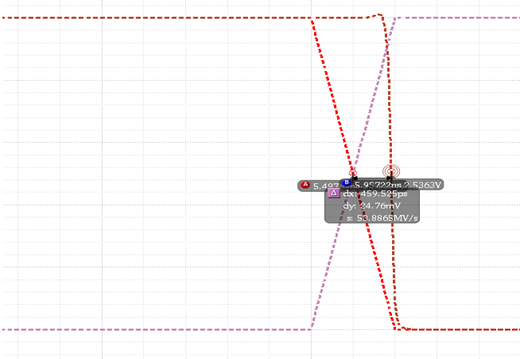

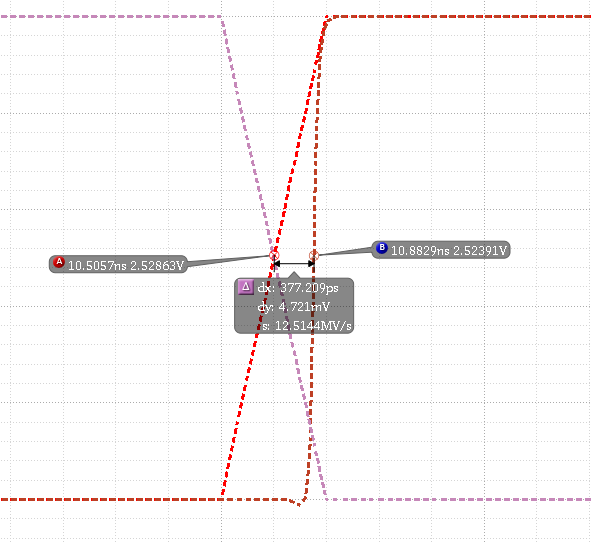

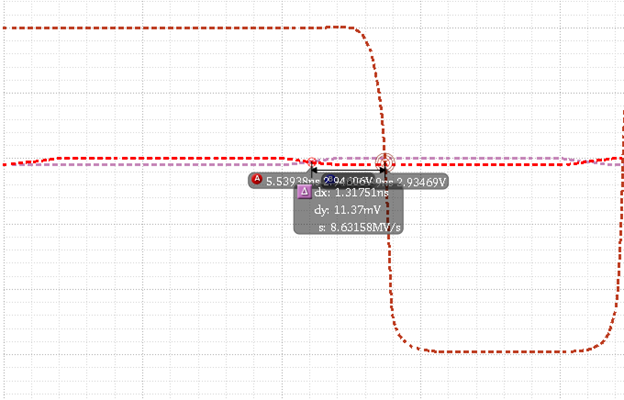

When D = 3V, Di = 2.9V, V_diff = 100mV at 250Mbits/s:

The propagation high to low delay is 1.31ns, and an offset is present too, so I might say that the performance of my design decline when V_diff < 100 mV.

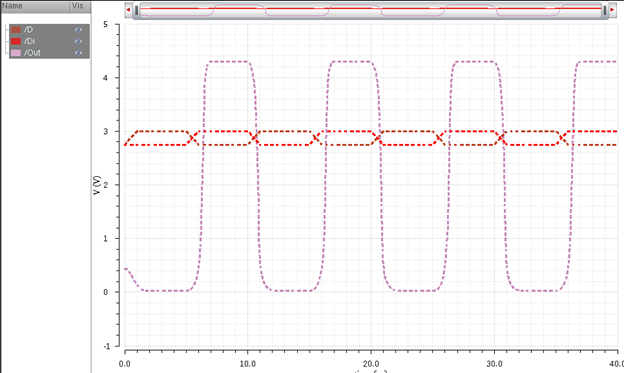

When Bit width is 2 ns or 500Mbit/s: