Lab 4 - EE 421L Fall 2020

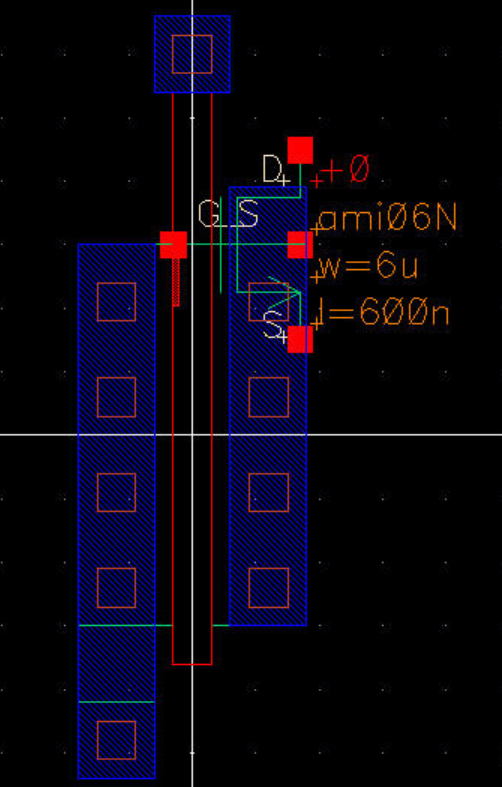

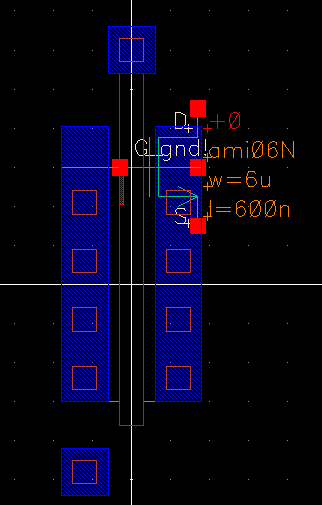

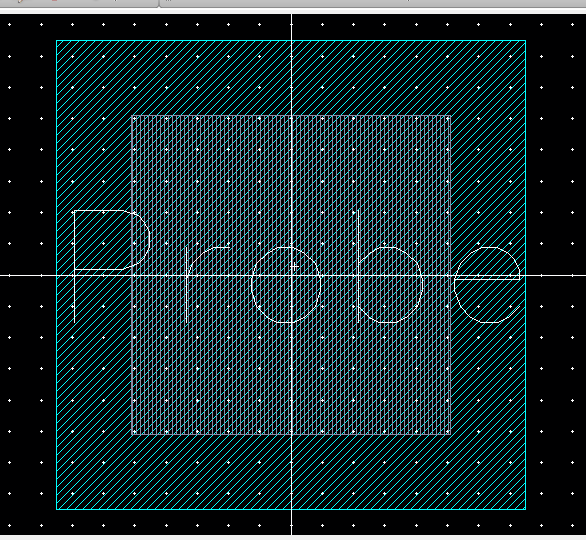

To fix that we'll ave to remove the metal1 rectangle and pin connecting the S to thhe bulk, as seen below:

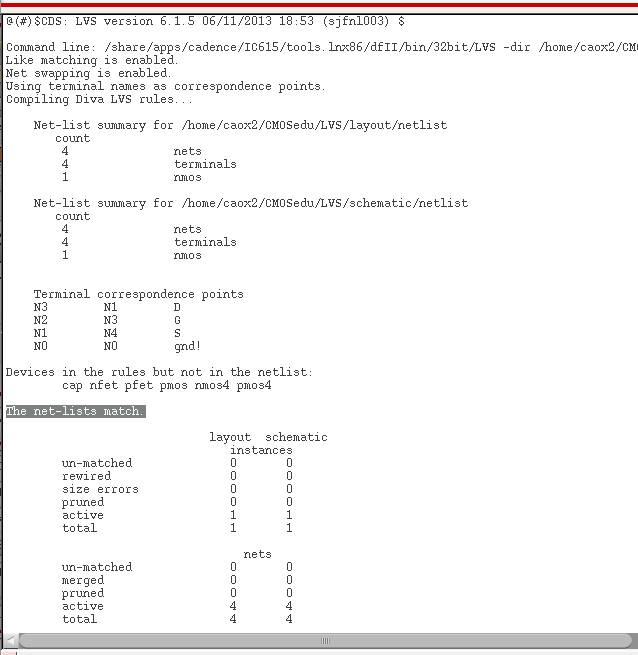

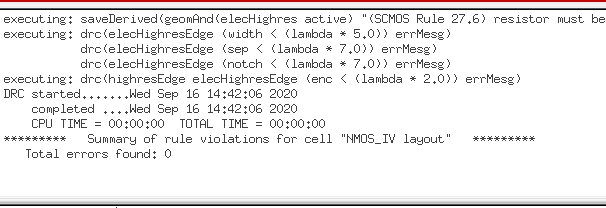

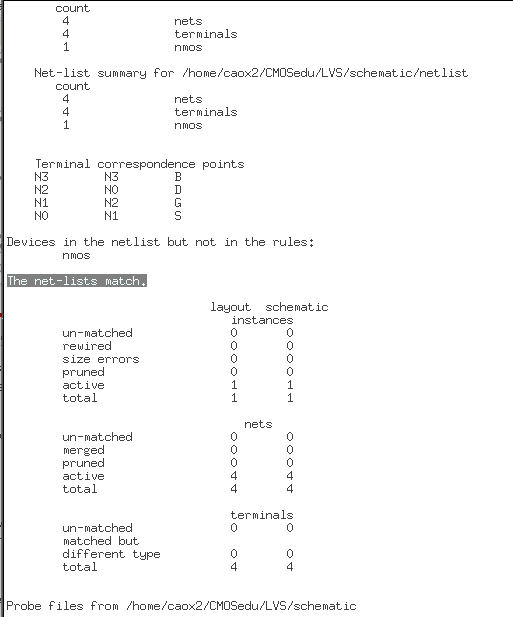

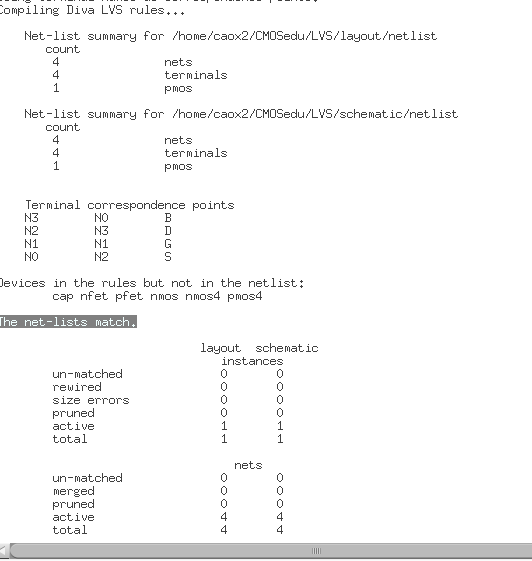

In order to run the LVS, there is one more step left, we need to change the cell name in the schematic from nmos to nmos4. After that, the LVS output is as following:

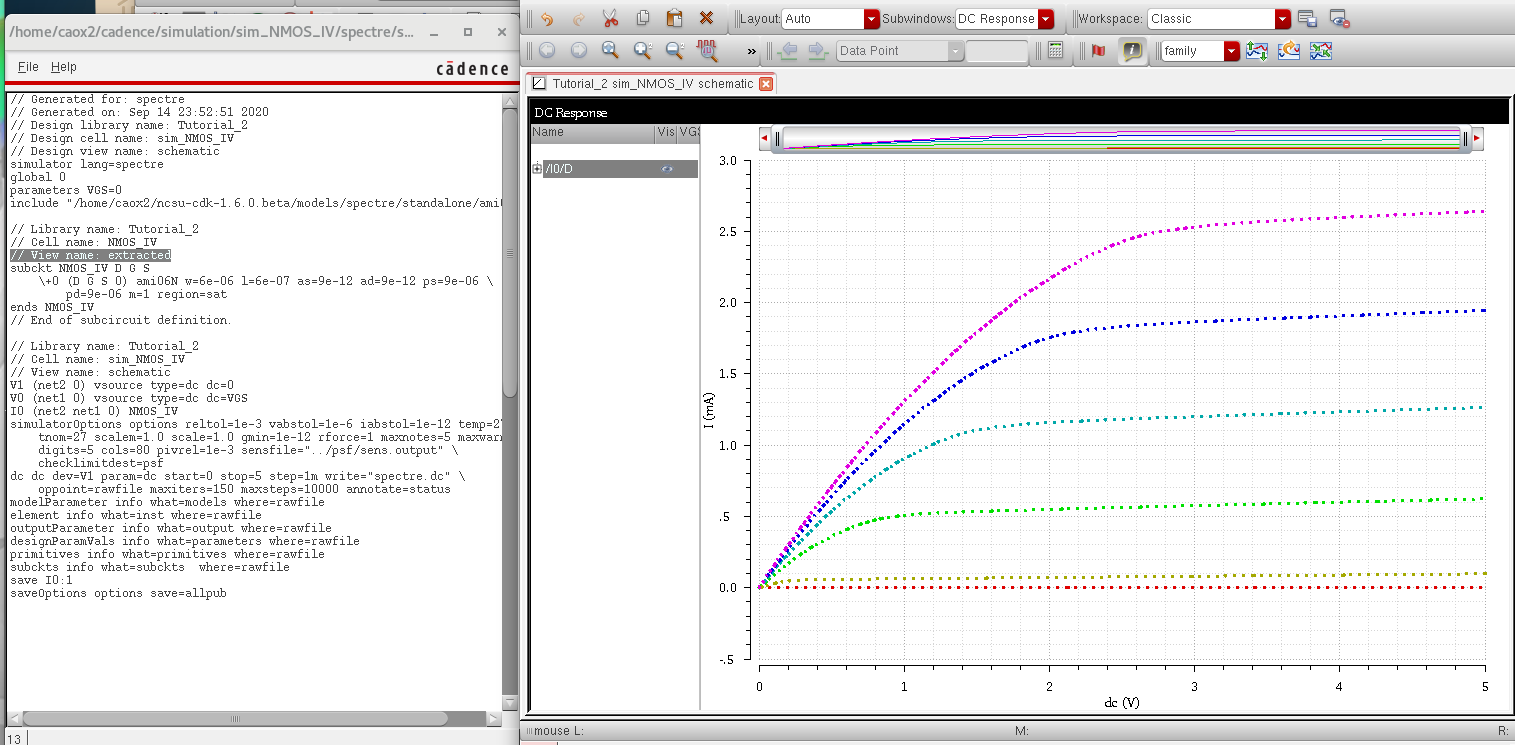

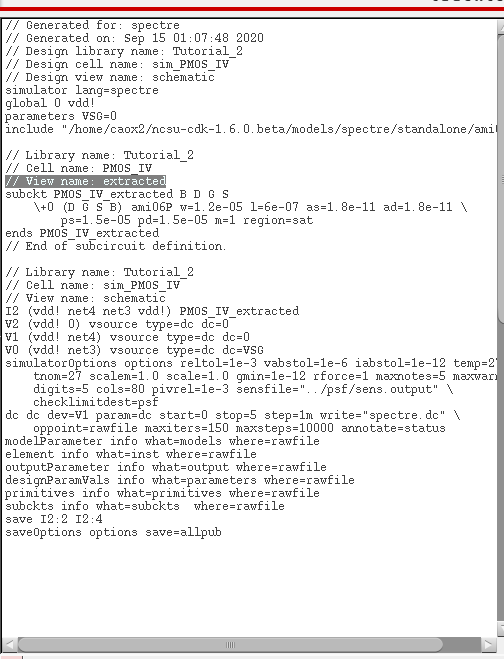

Then we simulate the extracted layout:

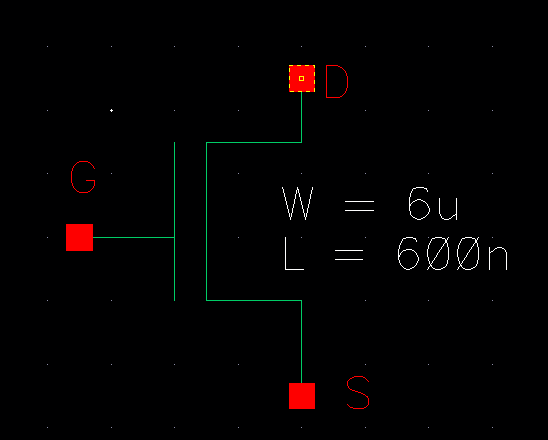

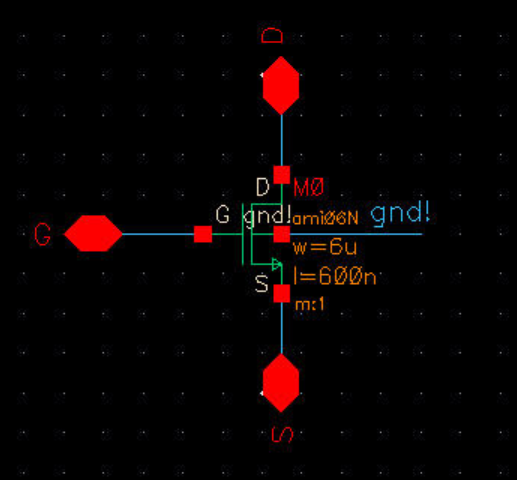

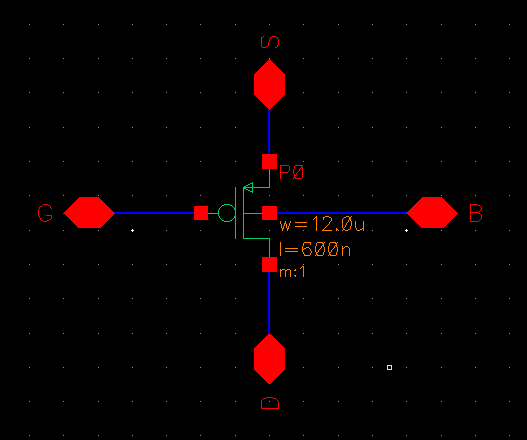

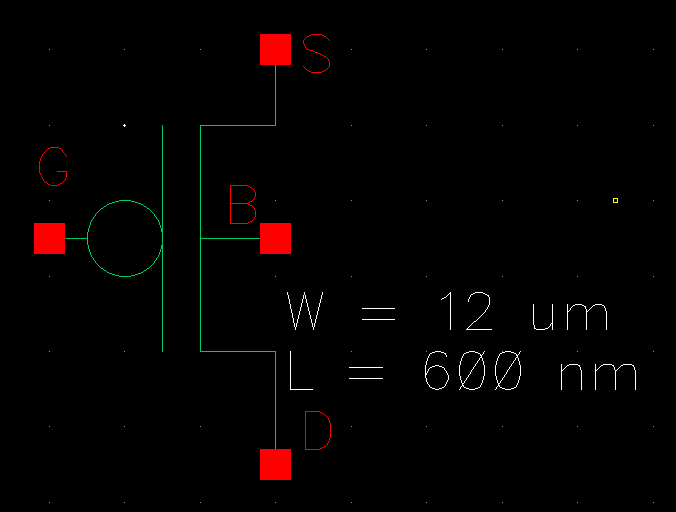

The shematic and the symbol view are seen below:

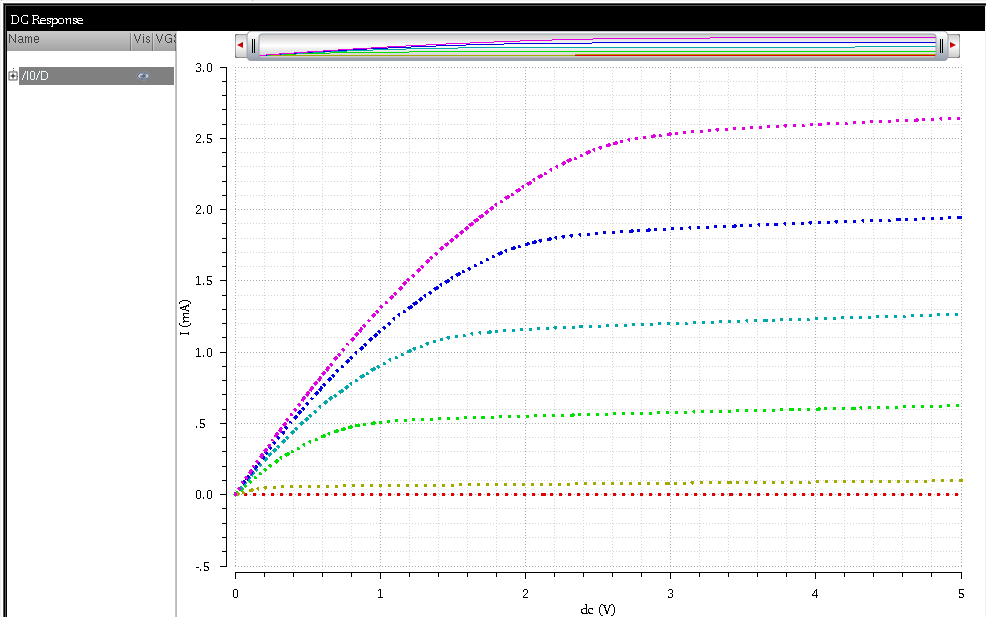

Extracted simulation:

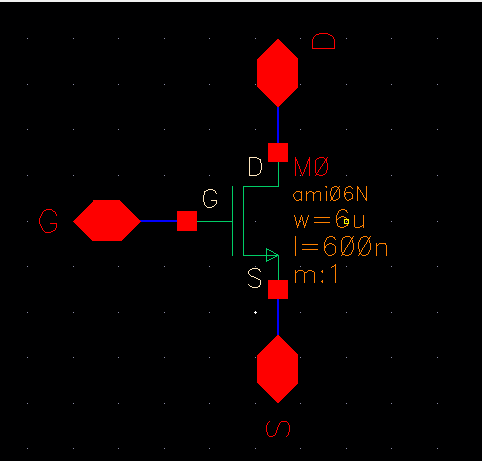

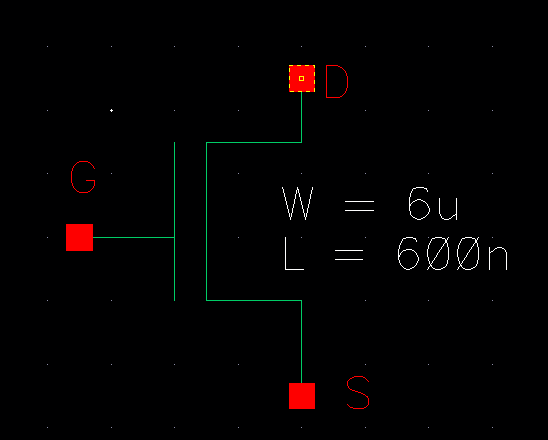

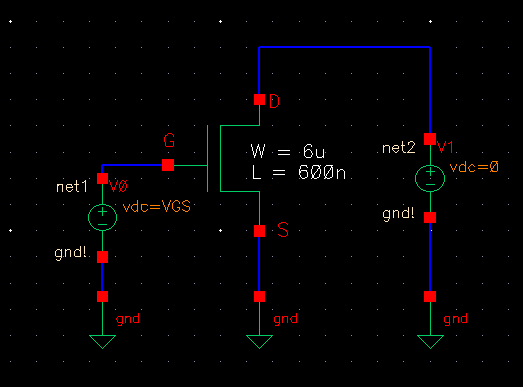

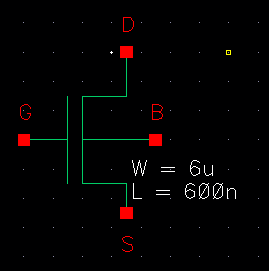

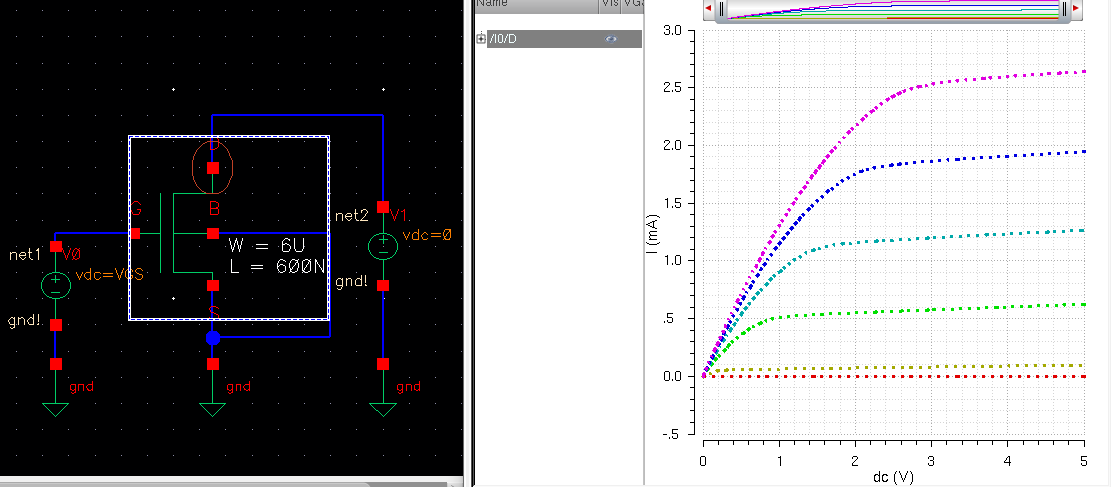

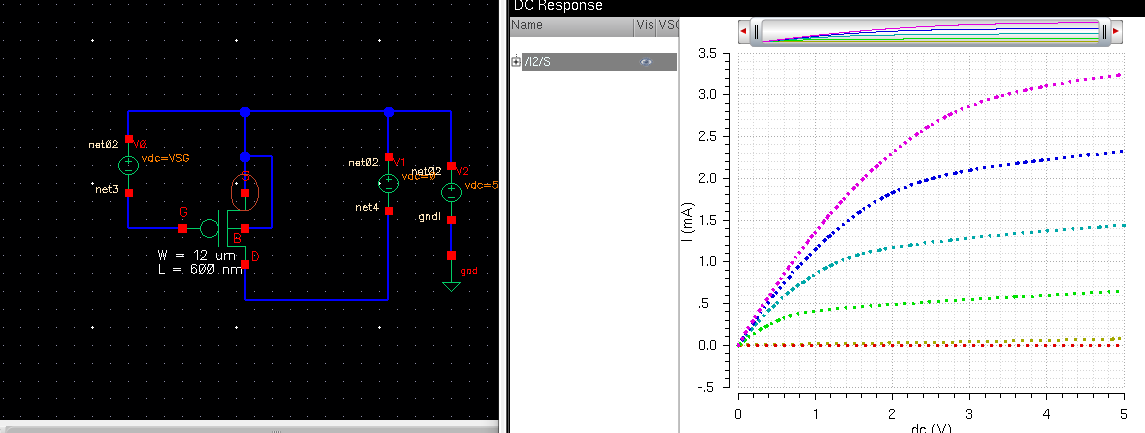

1. A schematic for simulating ID

v. VDS of an NMOS device for VGS varying from 0 to 5 V in 1 V steps

while VDS varies from 0 to 5 V in 1 mV steps. Use a 6u/600n

width-to-length ratio.

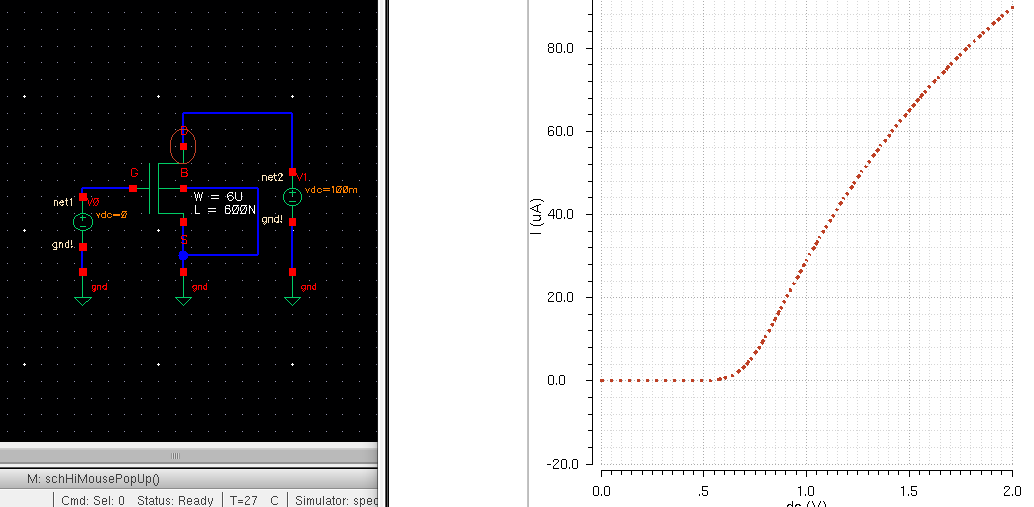

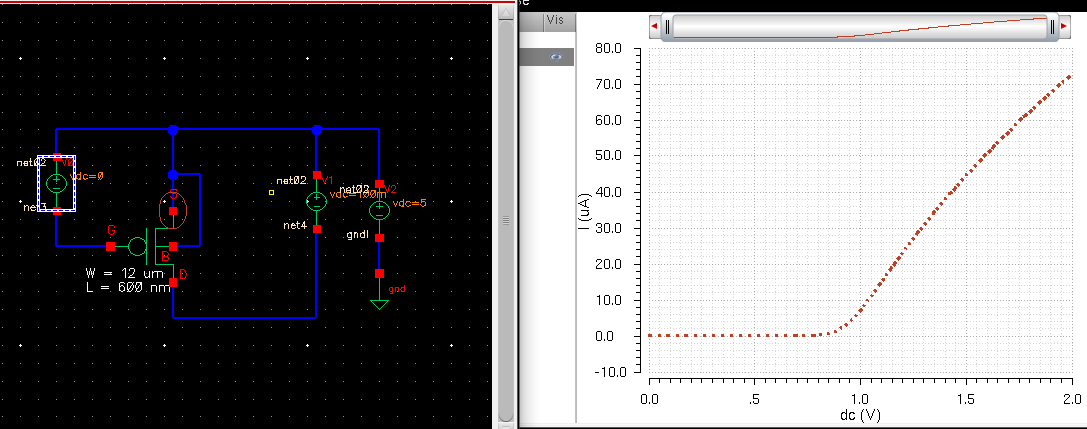

2. A schematic for simulating ID v. VGS of an NMOS

device for VDS = 100 mV where VGS varies from 0 to 2 V in 1 mV steps.

Again use a 6u/600n width-to-length ratio.

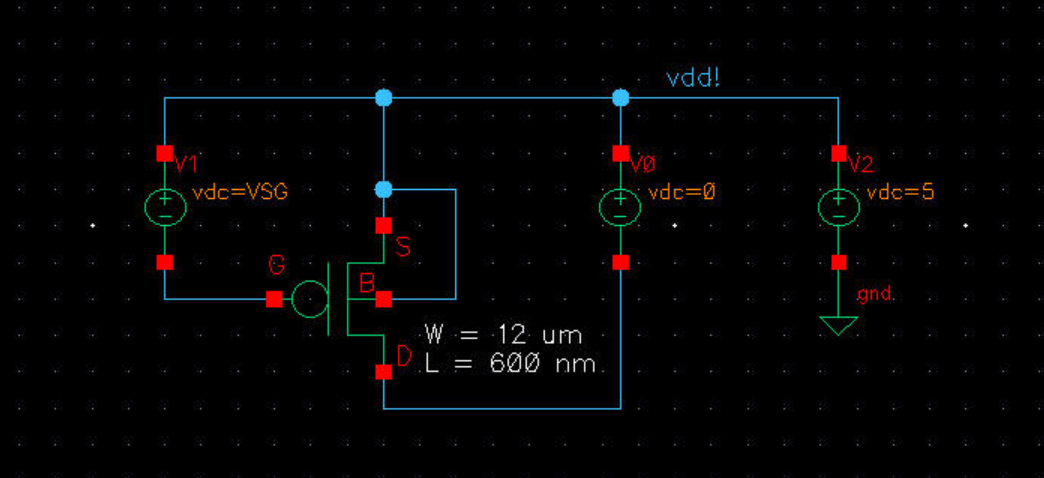

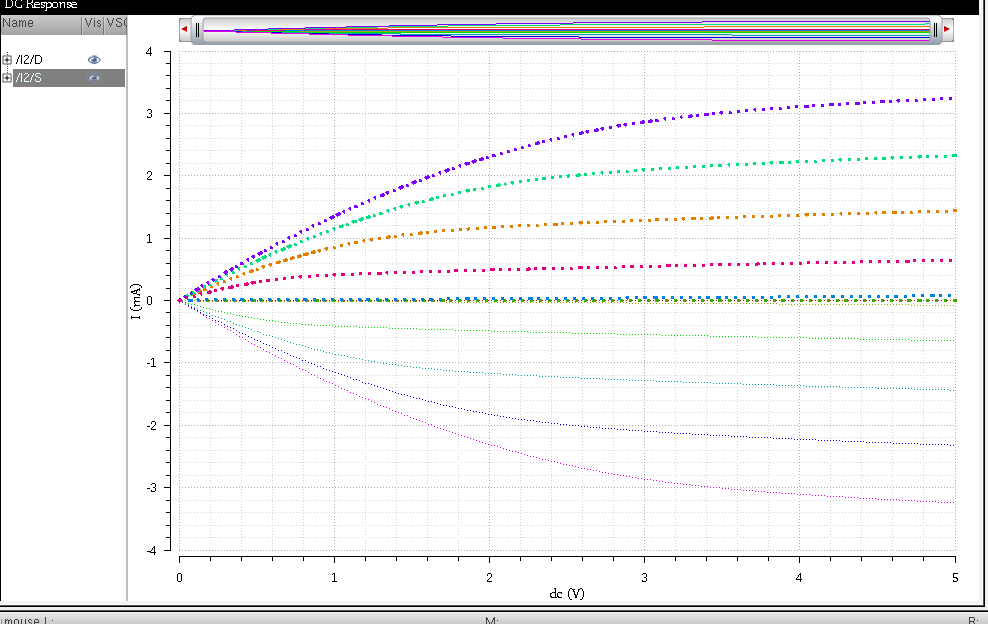

3. A schematic for simulating ID v. VSD (note VSD

not VDS) of a PMOS device for VSG (not VGS) varying from 0 to 5 V in 1

V steps while VSD varies from 0 to 5 V in 1 mV steps. Use a 12u/600n width-to-length ratio.

4. A schematic for simulating ID v. VSG of a PMOS device for VSD = 100 mV where VSG varies from 0 to 2 V in 1 mV steps. Again, use a 12u/600n width-to-length ratio.

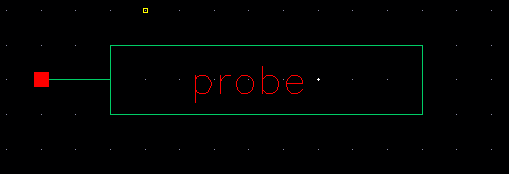

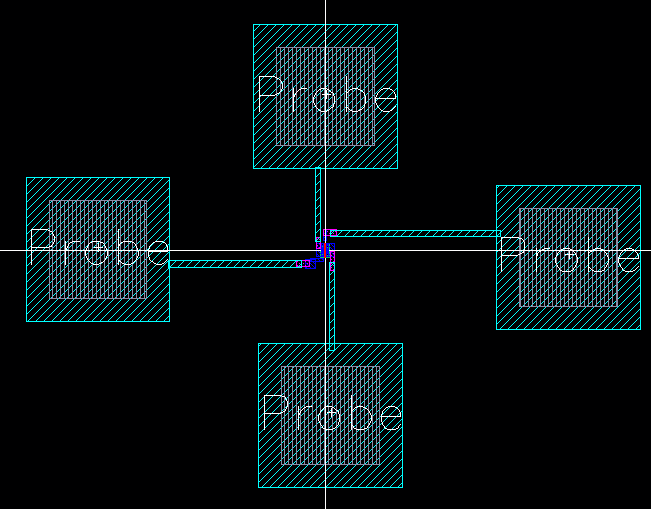

1) Lay out the Probe pad with metal3 and glass layer, then create a symbol for it.

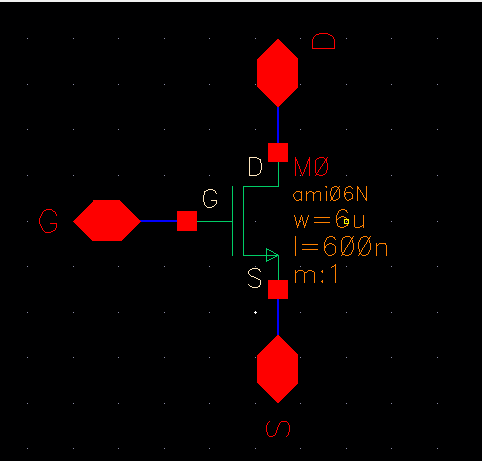

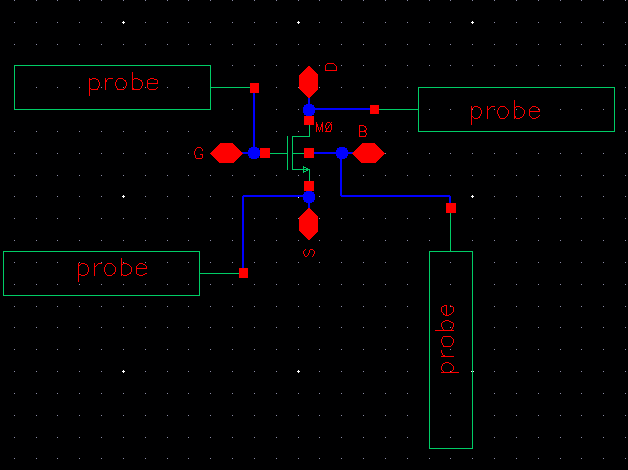

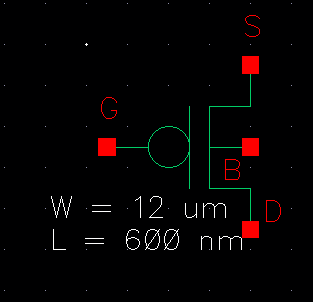

2) Draw the schematic for a 4 terminals NMOS device and then create a symbol from the cellview.

3) Schematic for a 4 terminals PMOS device and its symbol.

4) Simulation of ID vs VDS of an NMOS devices for VGS varying from 0 to 5V in 1V steps while VDS varies from 0 to 5V in 1mV steps.

5) Simulation of ID vs VGS of an NMOS device for VDS = 100mV and VGS varies from 0 to 2V in 1 mV steps.

6) Simulation of ID vs VSD of a PMOS device for VSG varying from 0 to 5 V in 1V steps and VSD varies from 0 to 5V in 1mV steps.

7) Simulation of ID vs VSG of a PMOS device for VSD = 100mV and VSG varies from 0 to 2V in 1mV steps.

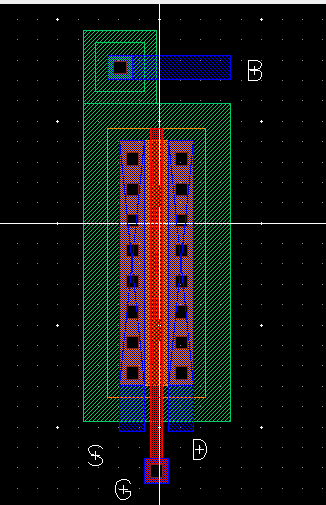

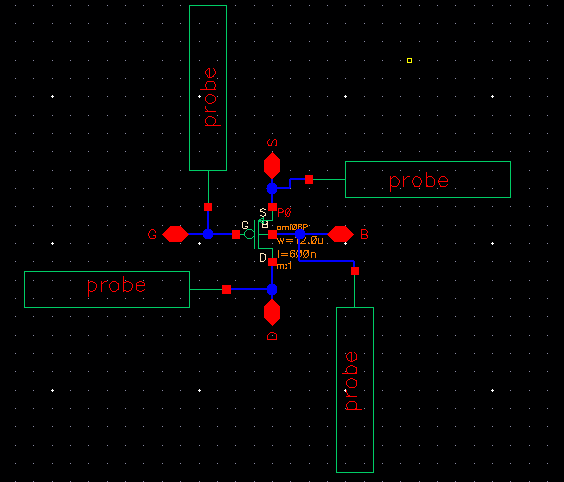

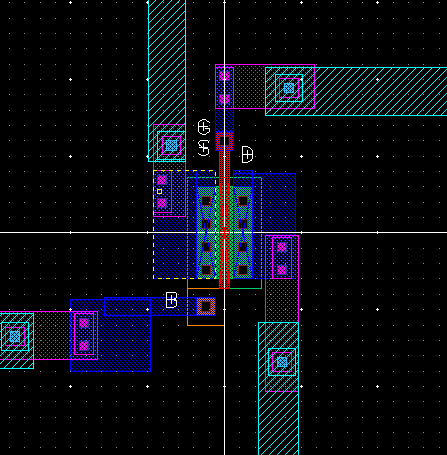

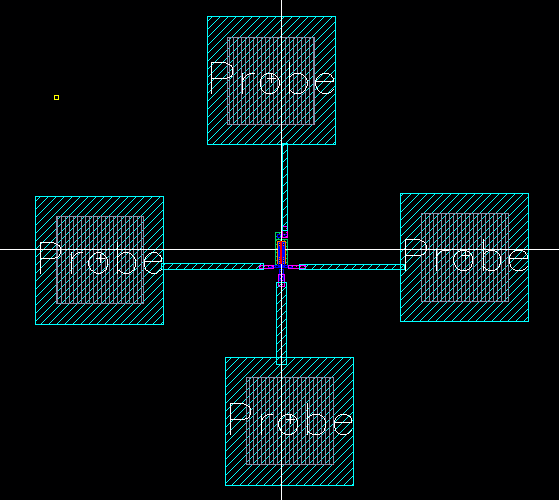

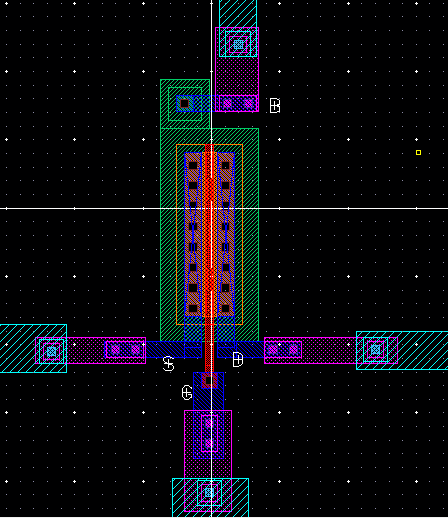

8) Layout of the NMOS device with all 4 terminals connecting to probe pads.

The closer view of the layer connections.

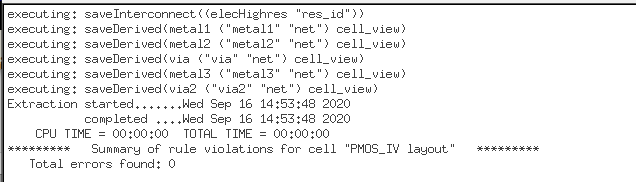

Passed both DRC and LVS check.

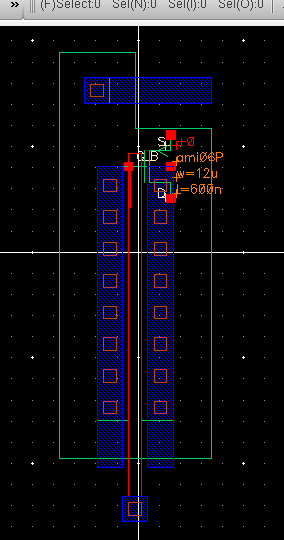

9) Layout of the PMOS device with all 4 terminals connecting to probe pads.

Closer view of the layer connections.

Passed both DRC and LVS.

Backups:

zipped the library folder and the folder that has all the collected images to the desktop, then upload them into my personal github repository for backups.