Lab 2 - EE 421L Fall 2020

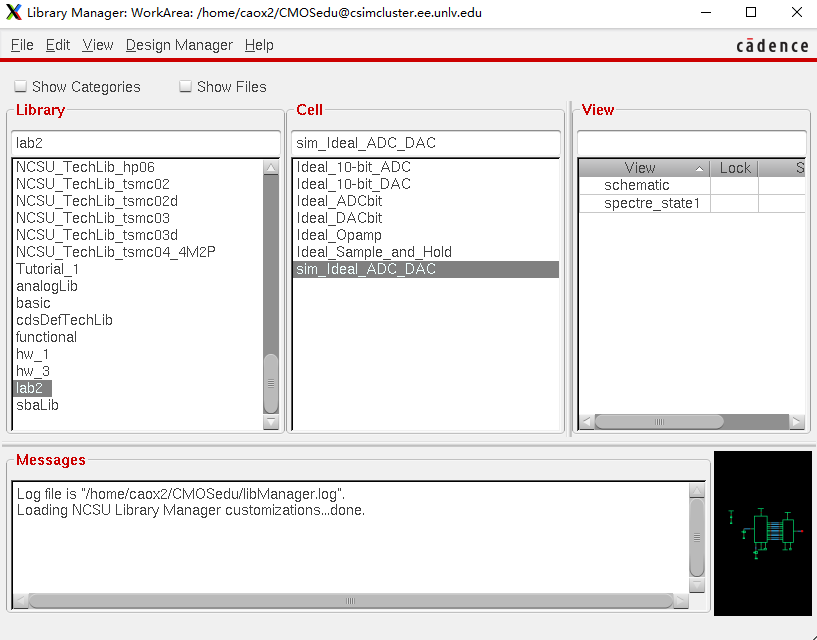

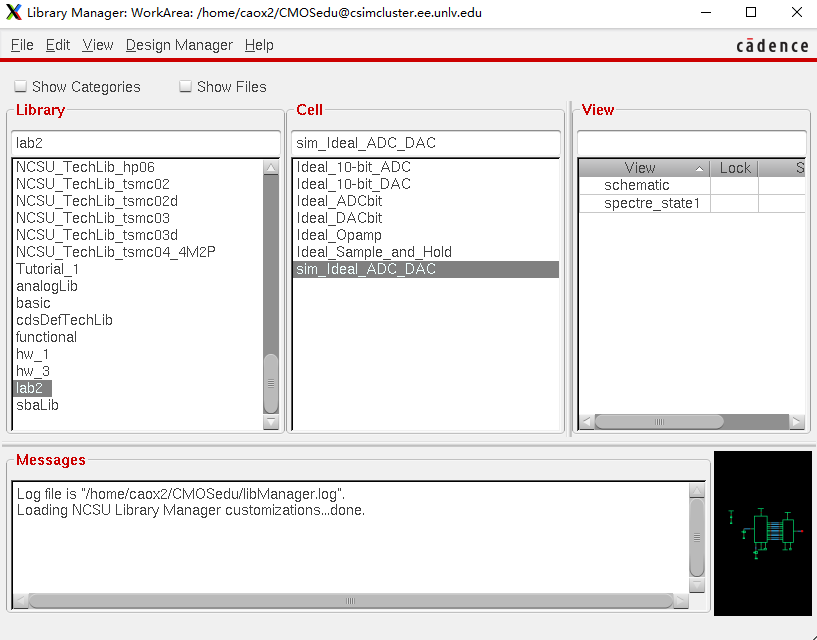

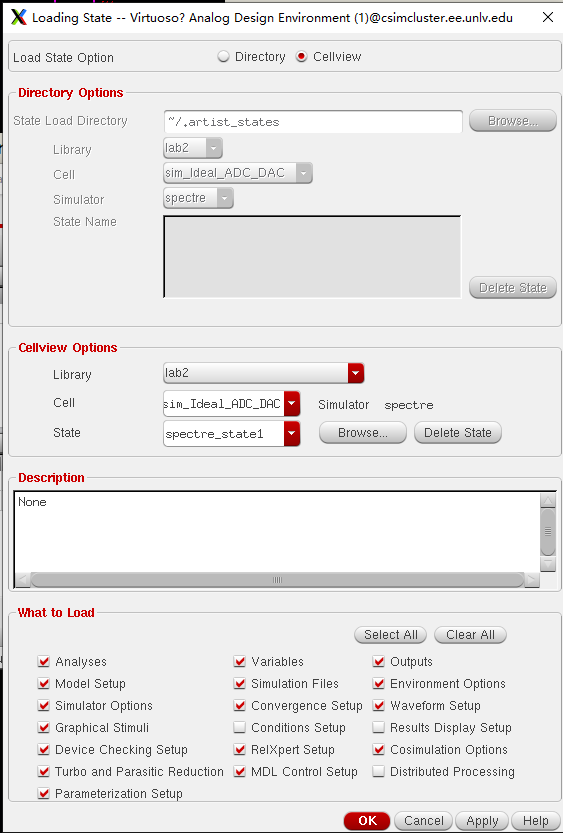

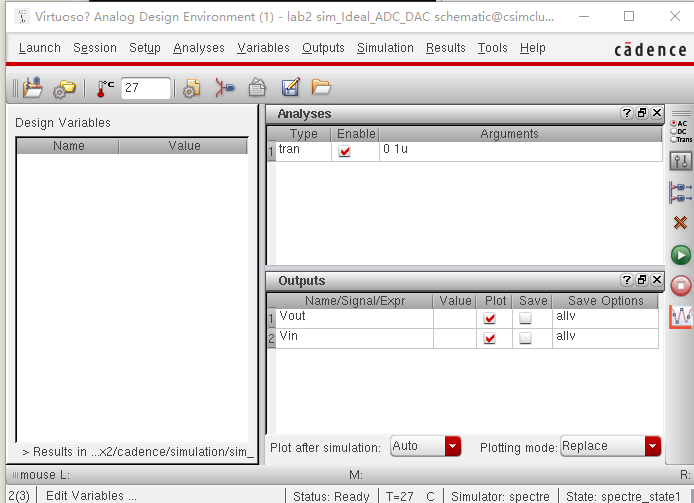

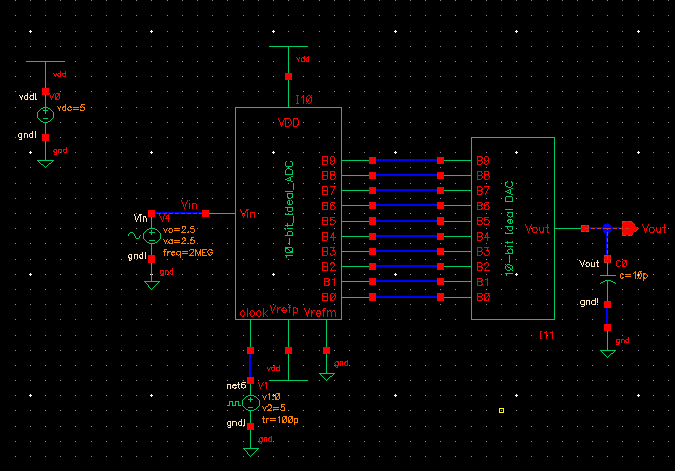

For the simulation purpose, we could just load the state from Cellview as it was given in the lab2.zip folder.

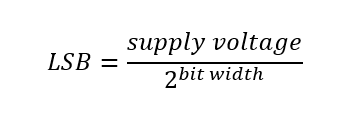

, in our case, bit width is 10, hence LSB = 5V/1024, which is approximately 4.88mV.

, in our case, bit width is 10, hence LSB = 5V/1024, which is approximately 4.88mV.

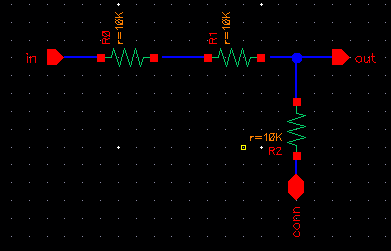

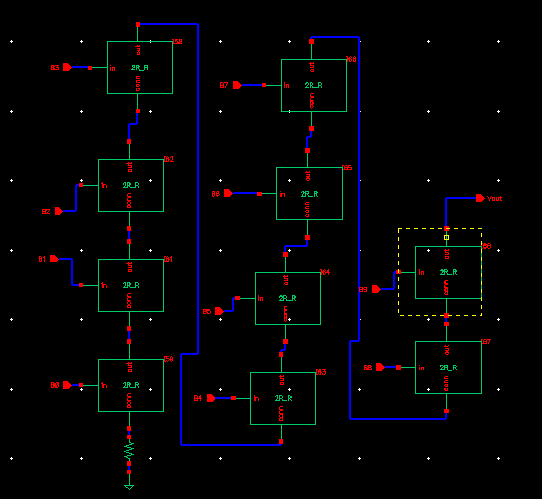

1) As we saw from the above image, the controlling input bits are connect to a voltage divider; therefore, make a symbol for the voltage divider would be helpful.

To determine the output resistance, we can combine the resistors, starting from very bottom, 2R || 2R which just R, then we add to the resistor in series, we now have 2R||2R again. By continue the same process, we will get the output resistance, in our case, just R (10K).

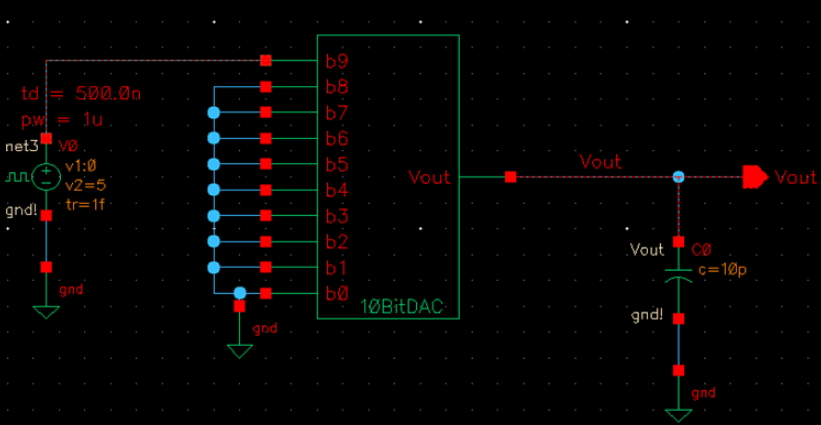

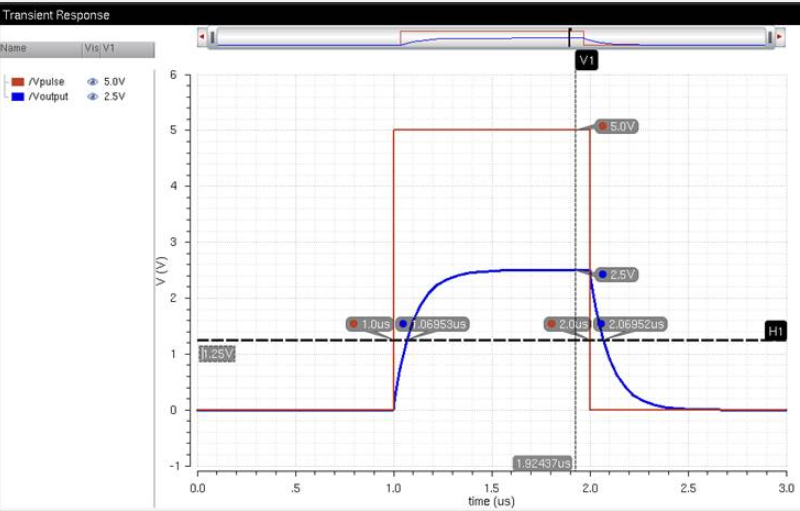

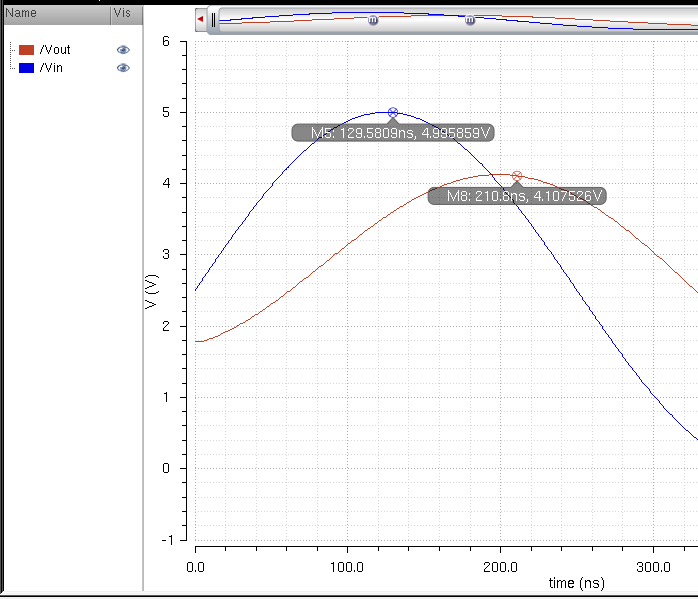

2) The Delay of thhe DAC when driving a 10 pF load can be calculated as 0.7RC, that is 0.7(10K)(10pF) = 70ns. To verify the correctness of the calculation, we can ground all DAC inputs, but with B9 connnnect to a pulse(0 to VDD). It should be as the following:

From the simulation, when Vout is at 1/2 of the maximum voltage, that is 1.25V, the delay is 1.069us - 1us = 69ns. Hence, delay verified.

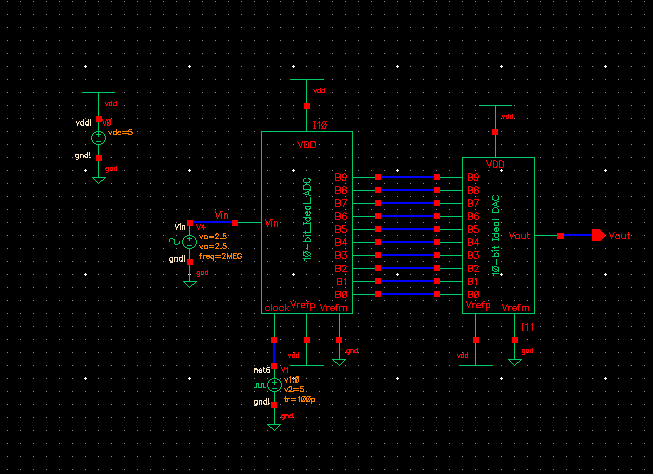

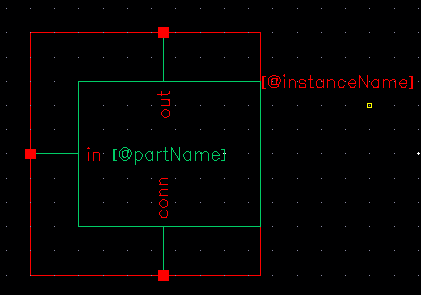

3) Creating our own symbol and schematic for the DAC.

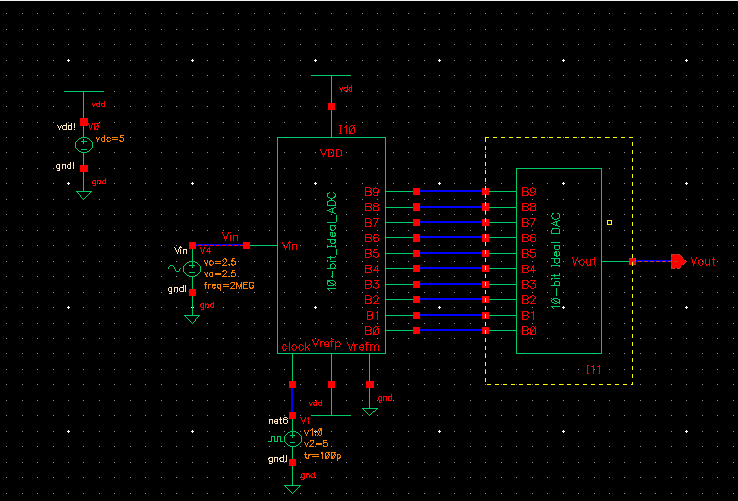

4) To verify DAC functions correctly, we should simulate the DAC with different load.

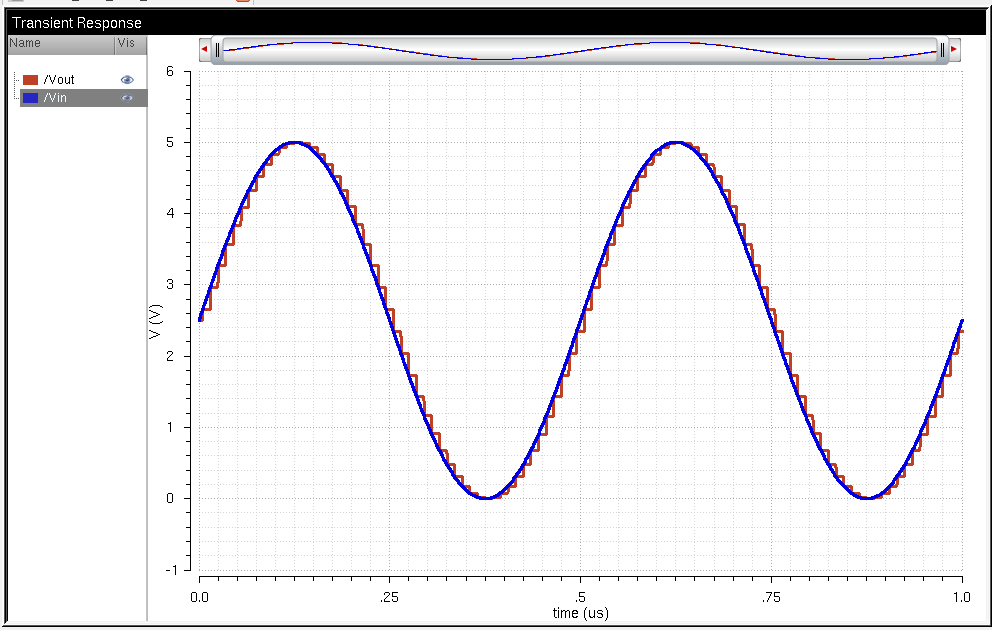

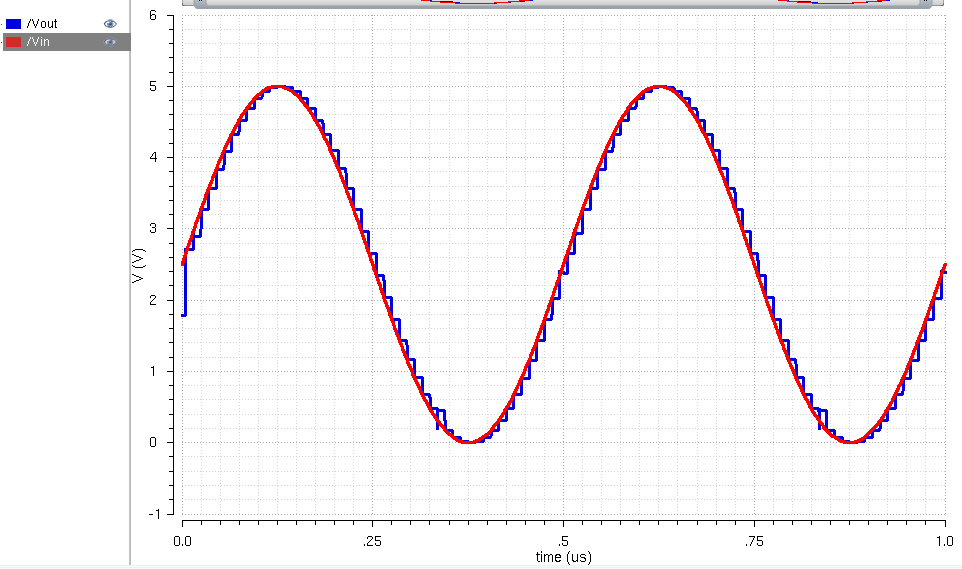

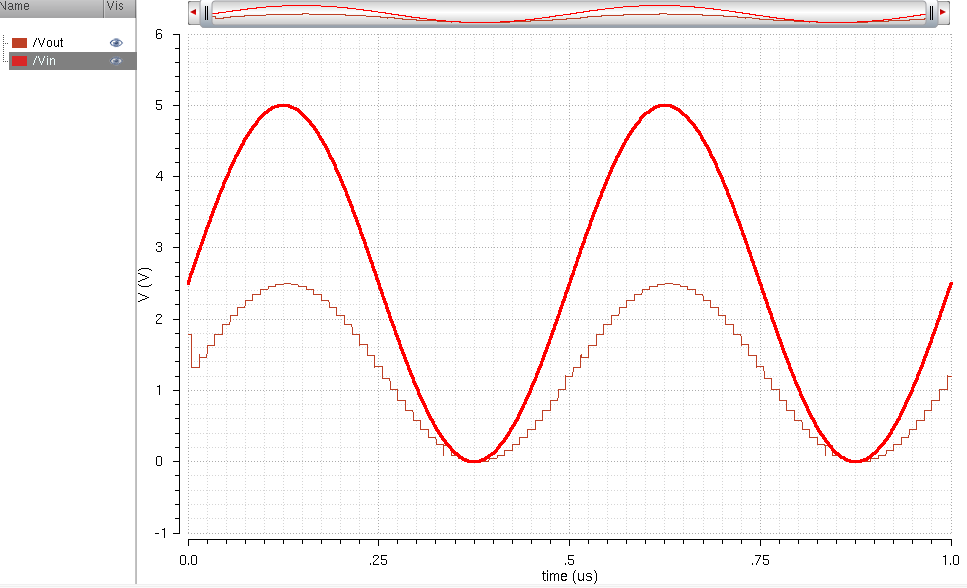

Simulation under no load:

With no load, the Vout has the same amplitudes of the Vin, in fact, this is to be expected.

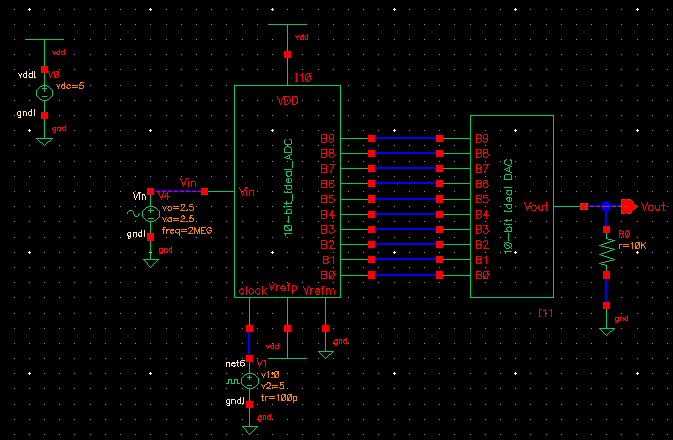

Simulation under 10K resistive load:

As we calculated at step 2, the output resistance is 10K when no load, hence, with the 10K resistive load, it forms a voltage divider, as result of this, Vout is going to be half of Vin.

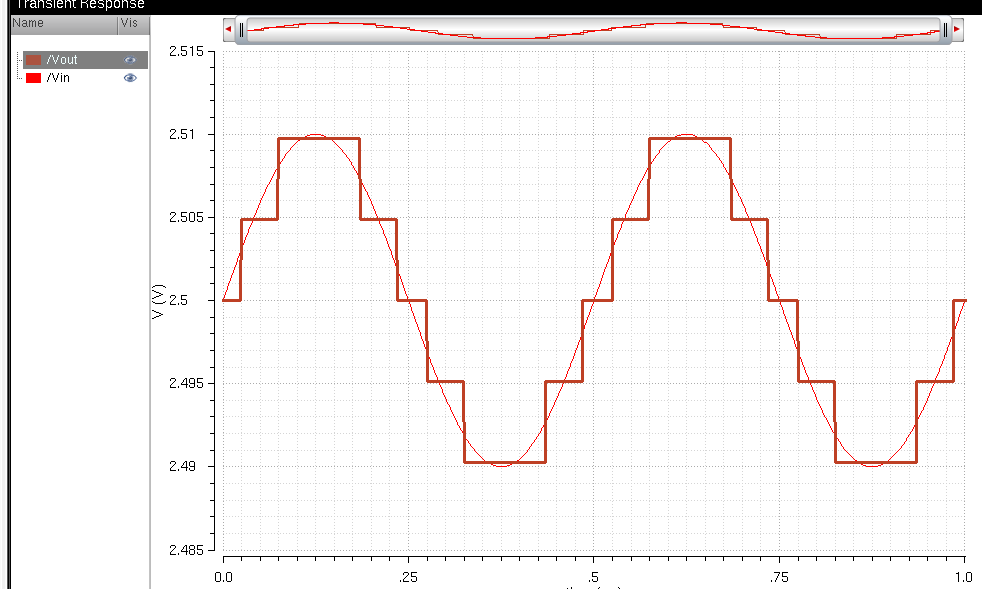

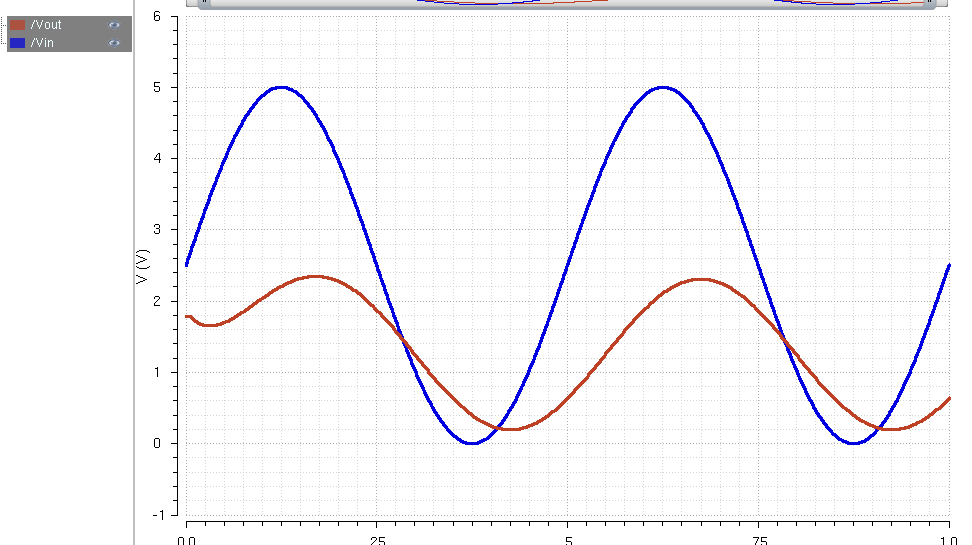

simulation under 10p capacitive load:

with the 10 pF caapacitor, it smooths the output waveform, but it also introduces the delay to the output.

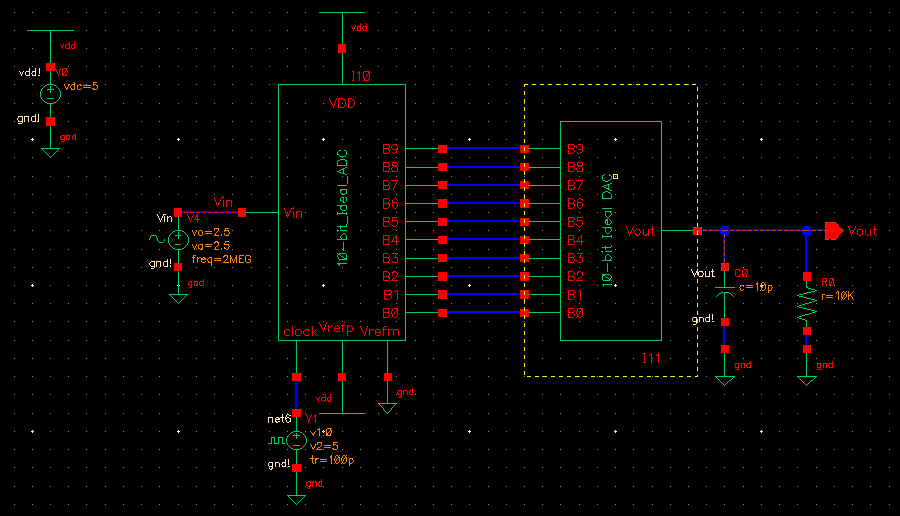

simulation under 10K and 10pF load:

http://cmosedu.com/jbaker/courses/ee421L/f20/students/caox2/Lab2/lab_snip_11.png

With both resistive and capacitive load, the output will still be lagging the input and half of the Vin amplitude.

Backups:

zipped the library folder and the folder that has all the collected images to the desktop, then upload them into my personal github repository for backups.