Lab 1 - EE 421L Fall 2020

Authored

by Xianjie Cao

25 August 2020

Prel-lab:

Our pre-lab work includes drafting the lab report using html and post

them on CMOSedu, to acquire a CMOSedu account that gives us access to

the CMOSedu.com, and knowing the tools that we'll need, such as Cadence and Kompozer.

Lab

description:

In this lab, we'll be laying out and simulating a voltage divider on Cadence.

Lab procedure:

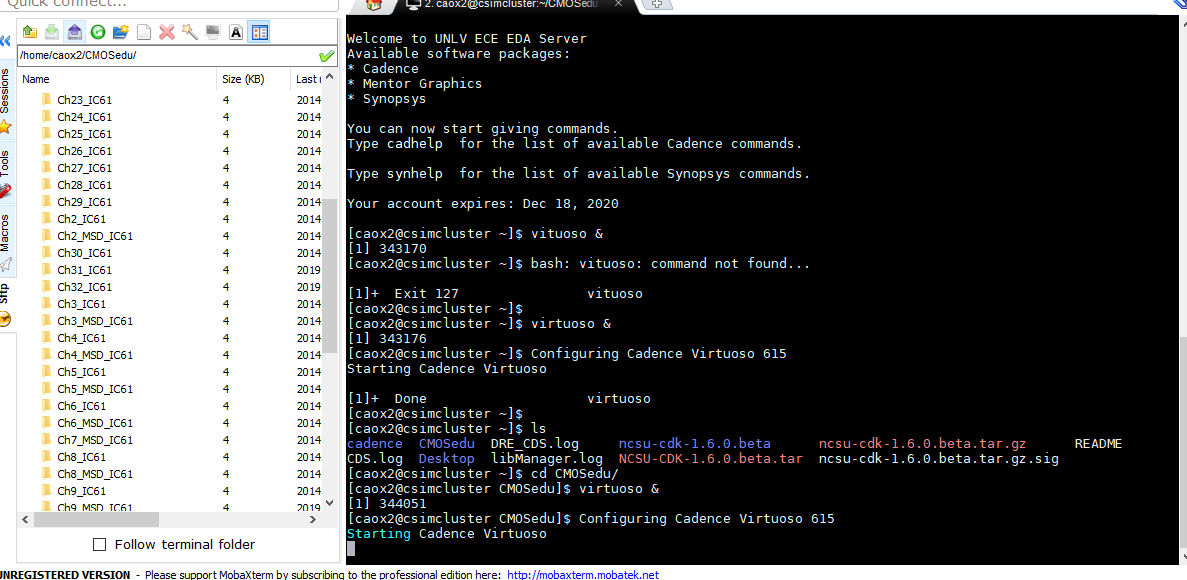

1) Starting by access Cadence remotely through MobaXterm, as our libraries were all zipped in CMOSedu directory, we'll be running our Cadence in CMOSedu directory.

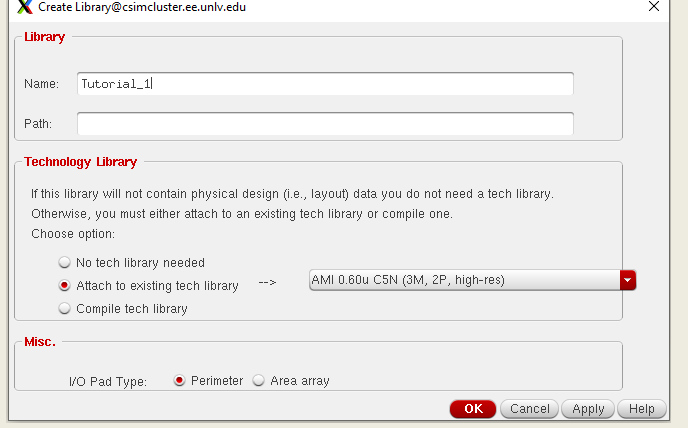

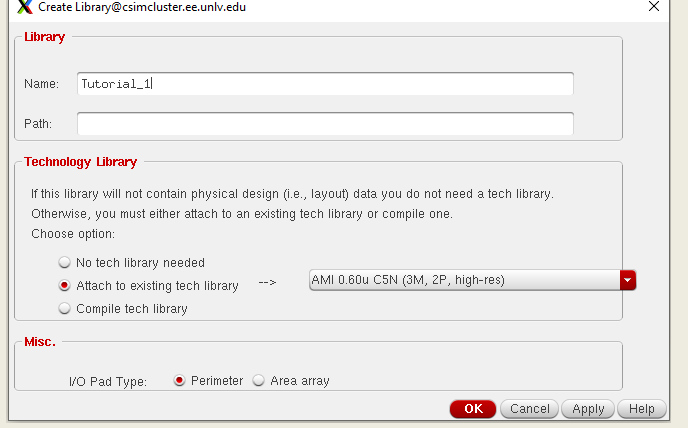

2) Create a library called "Tutorial_1", then select AMI 0.6u C5N as our tech library to attach to, then don't forget to add a DEFINE line to the cds.lib file in the CMOSedu director.

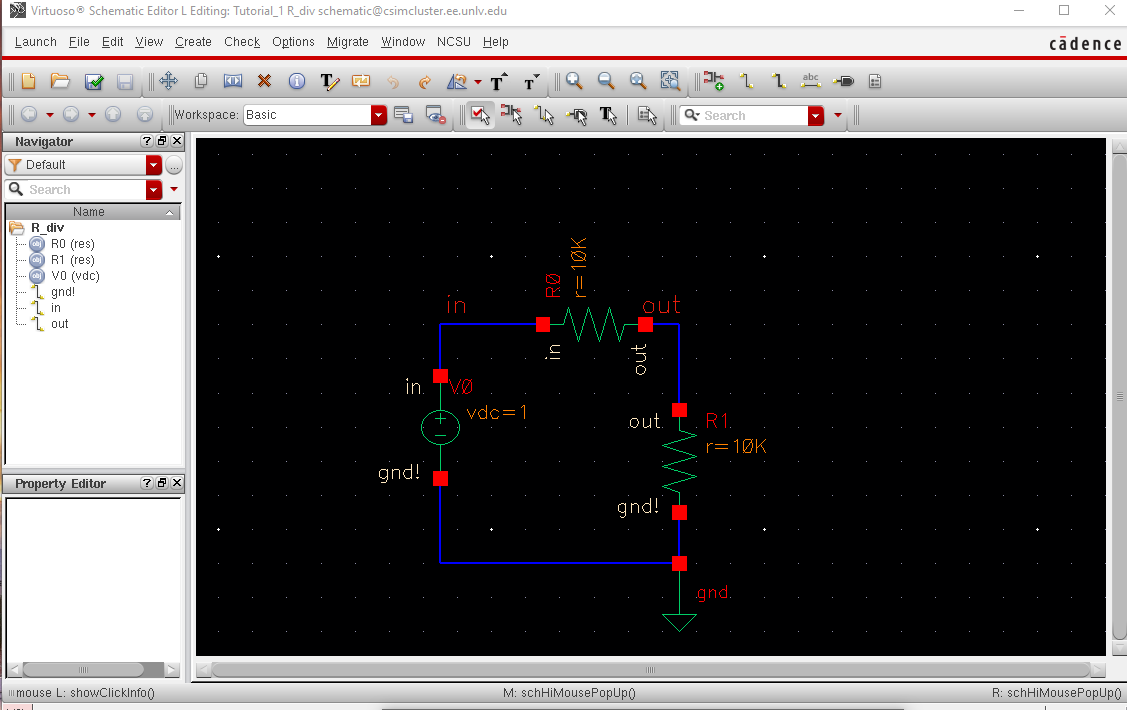

3) create a new cell and implementing the following voltage divider circuit on Cadence>

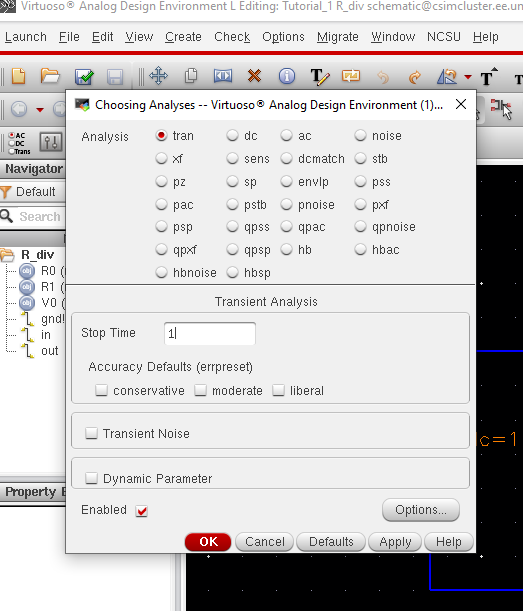

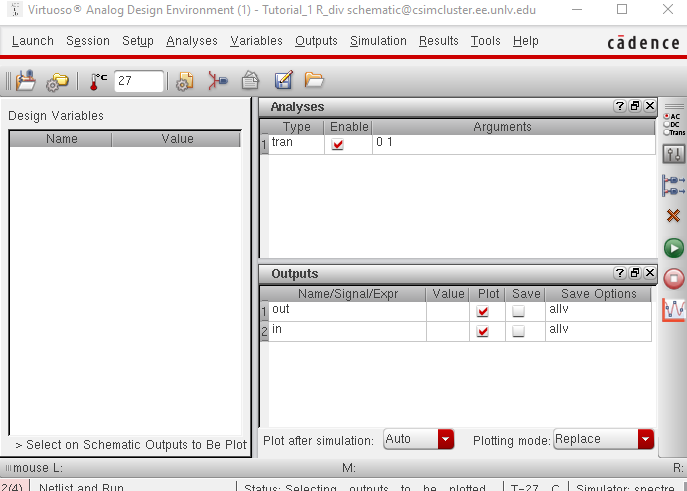

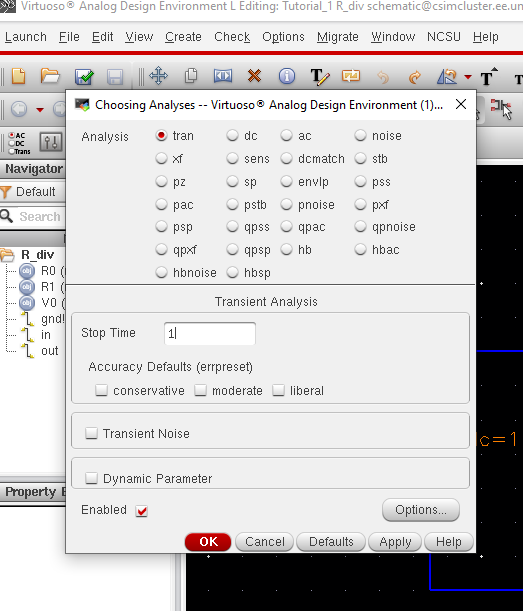

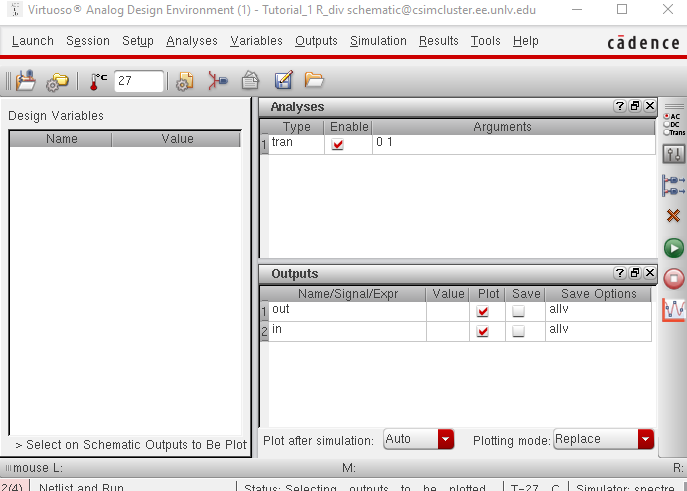

4) run a transient analysis of the circuit (for 1 second), and plot both in and out nodes as labeld in the previous image.

5)

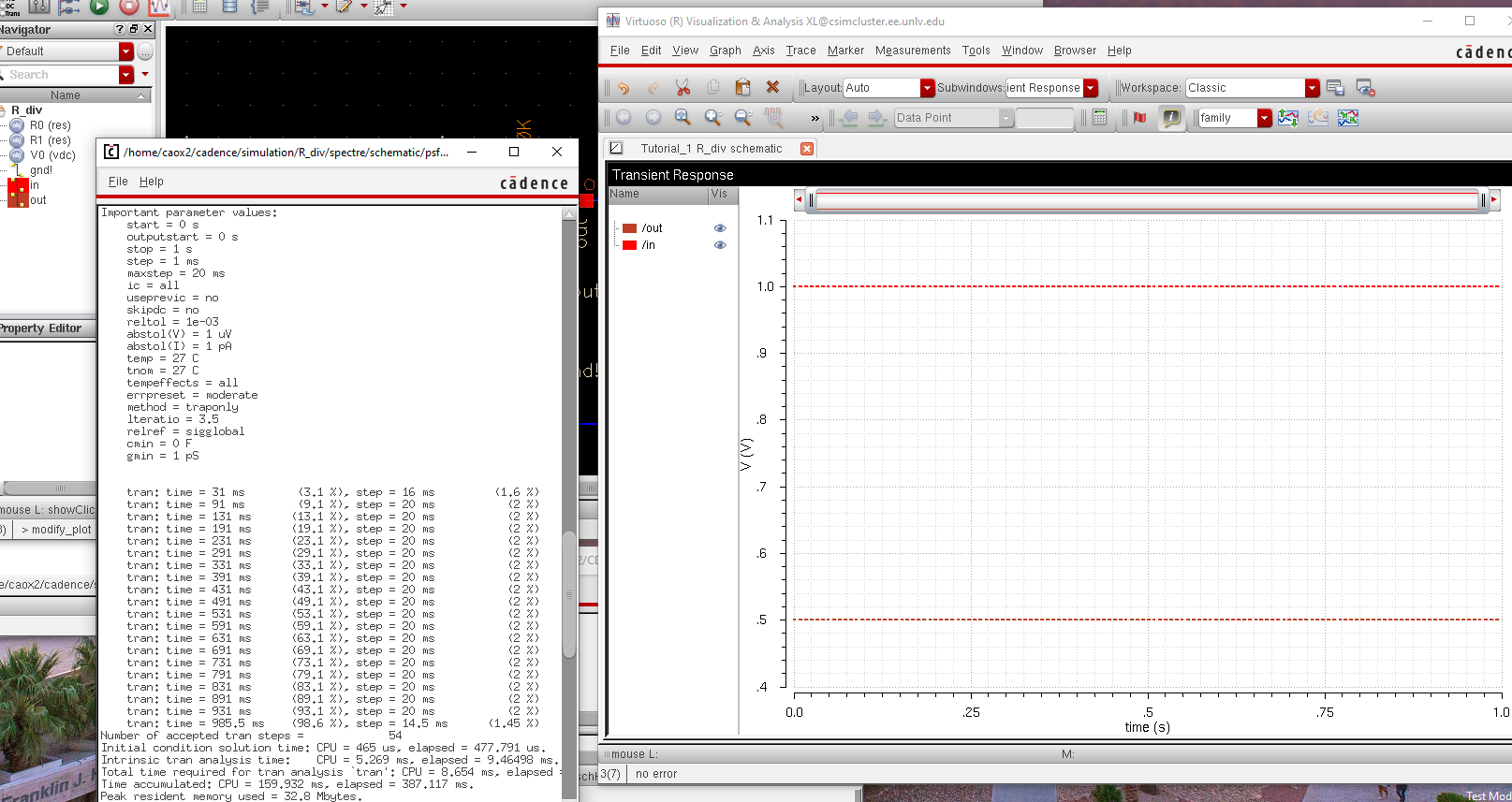

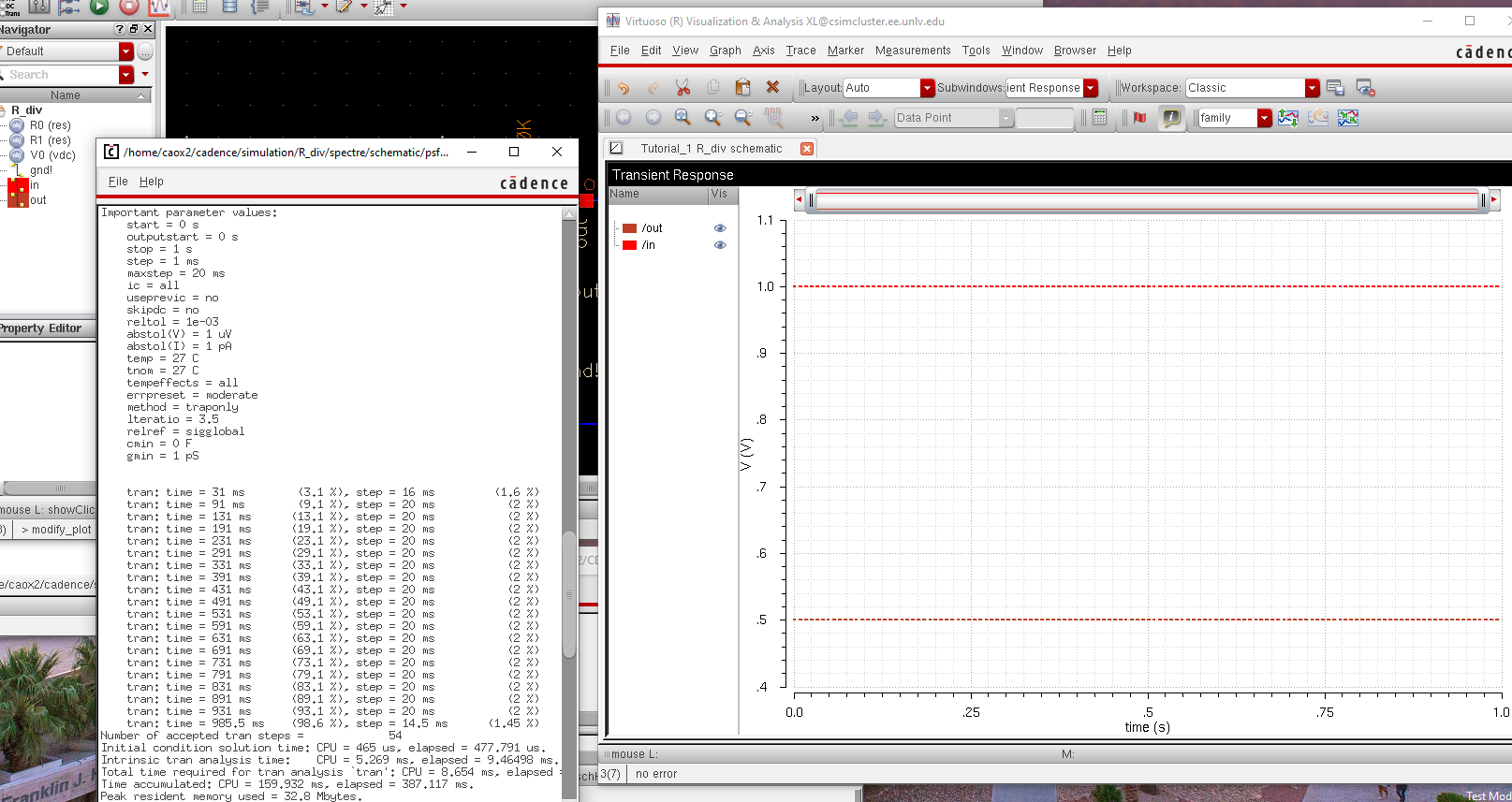

press the green play button in the previous image will start the

simulation. The plot is as below (a white background is great for

printing purpose).

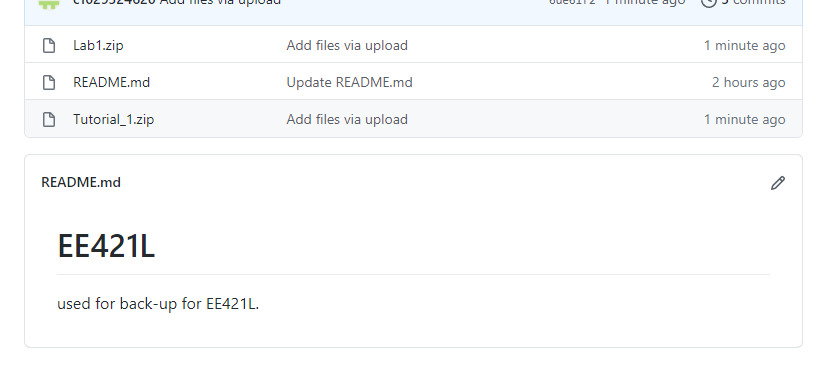

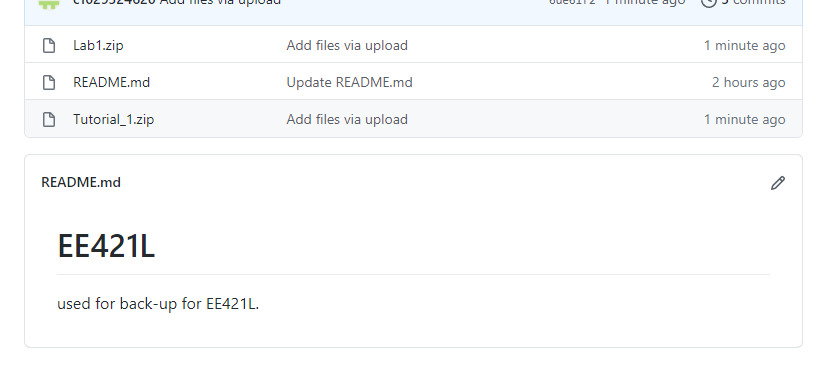

For backups:

I zipped the library folder and the folder that has all the collected

images to the desktop, then upload them into my personal github

repository to prevent if something goes wrong.

Return to EE421L Labs