Lab 08 - EE 421L

----------------------------------------------------------------------------------------------------

Guidelines:

Images can be clicked increase the size.

----------------------------------------------------------------------------------------------------

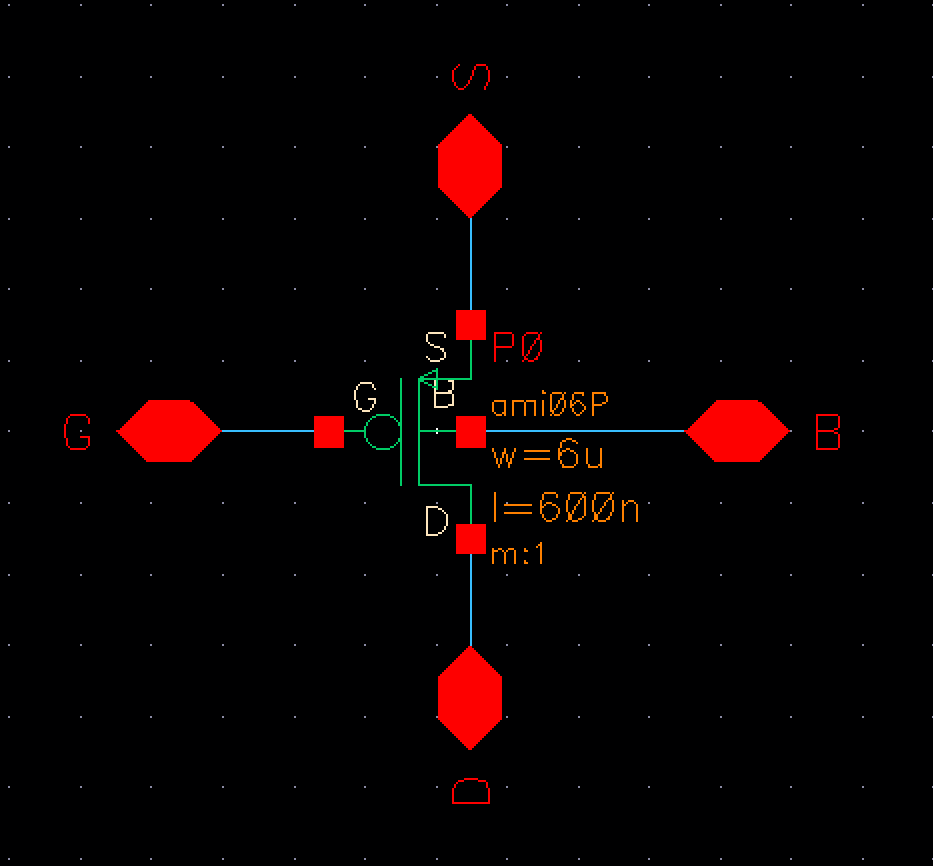

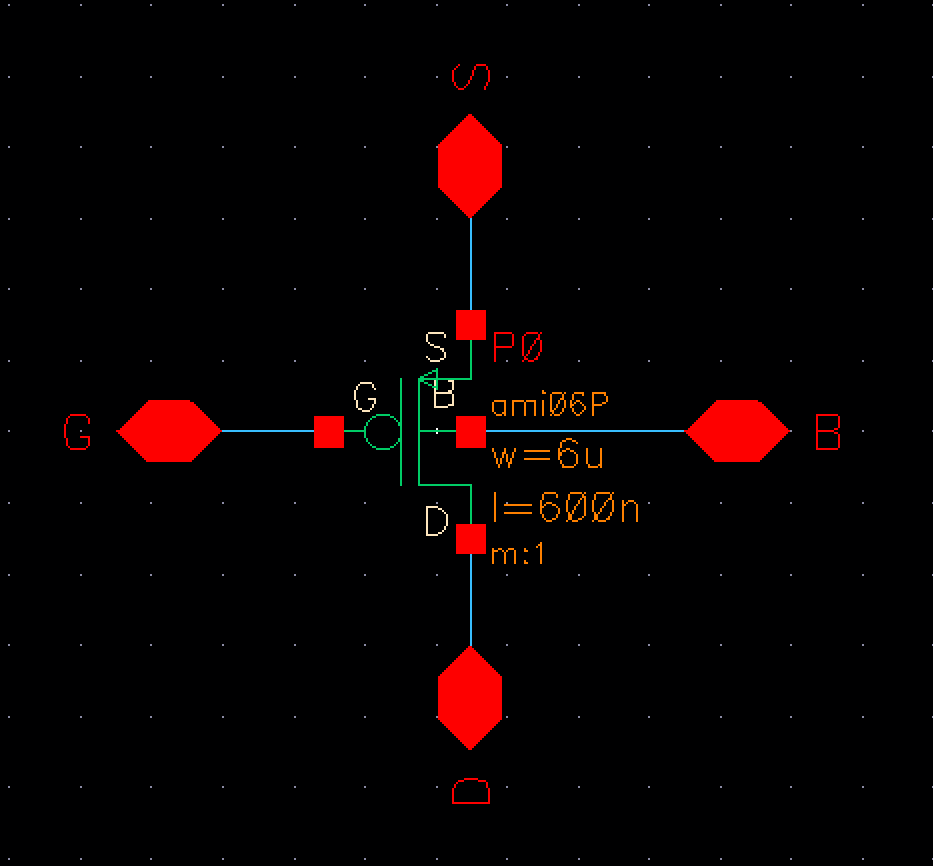

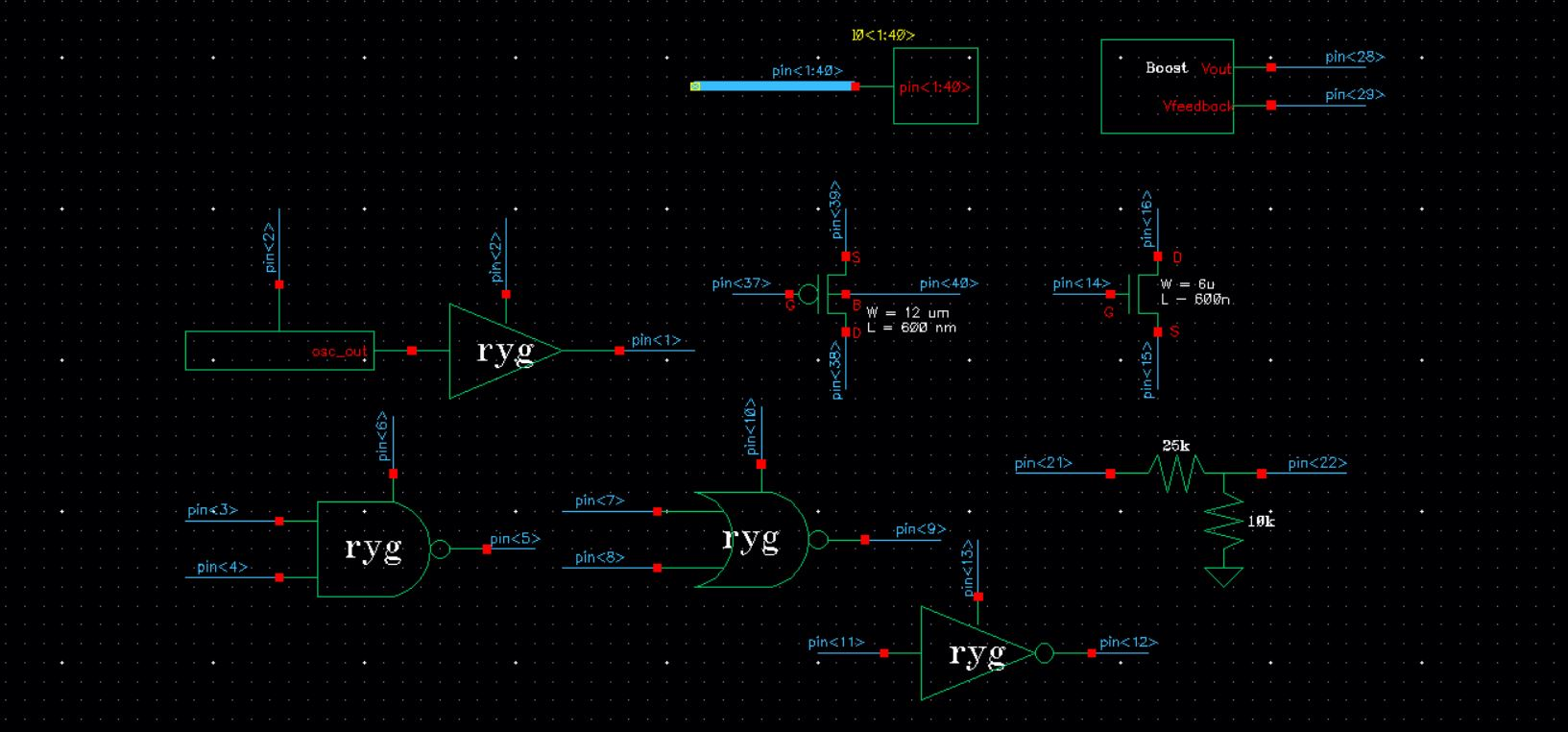

| PMOS 6u/0.6u: | |

|  |

|  |

G (Gate) -> Pin<37>

D (Drain) -> Pin<38>

S (Source) -> Pin<39>

B (Body) -> Pin<40>

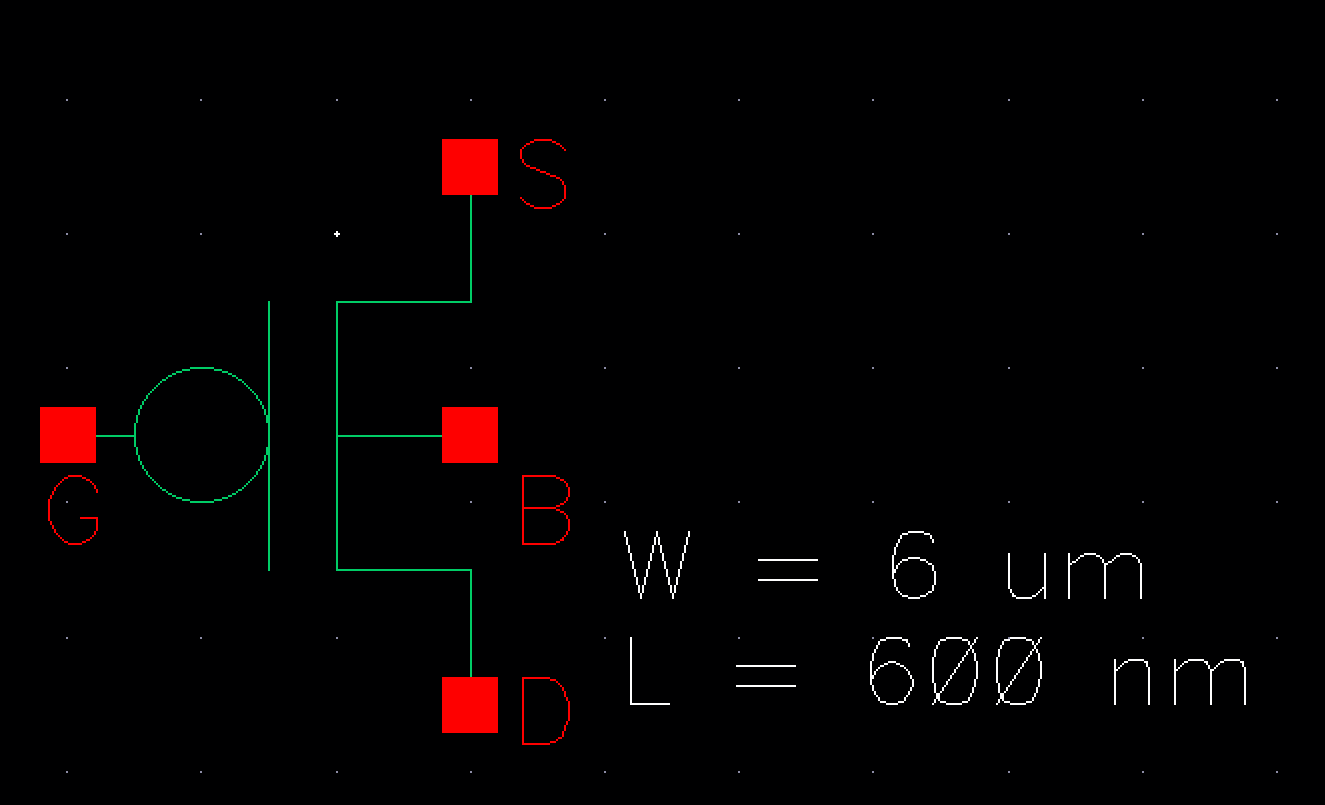

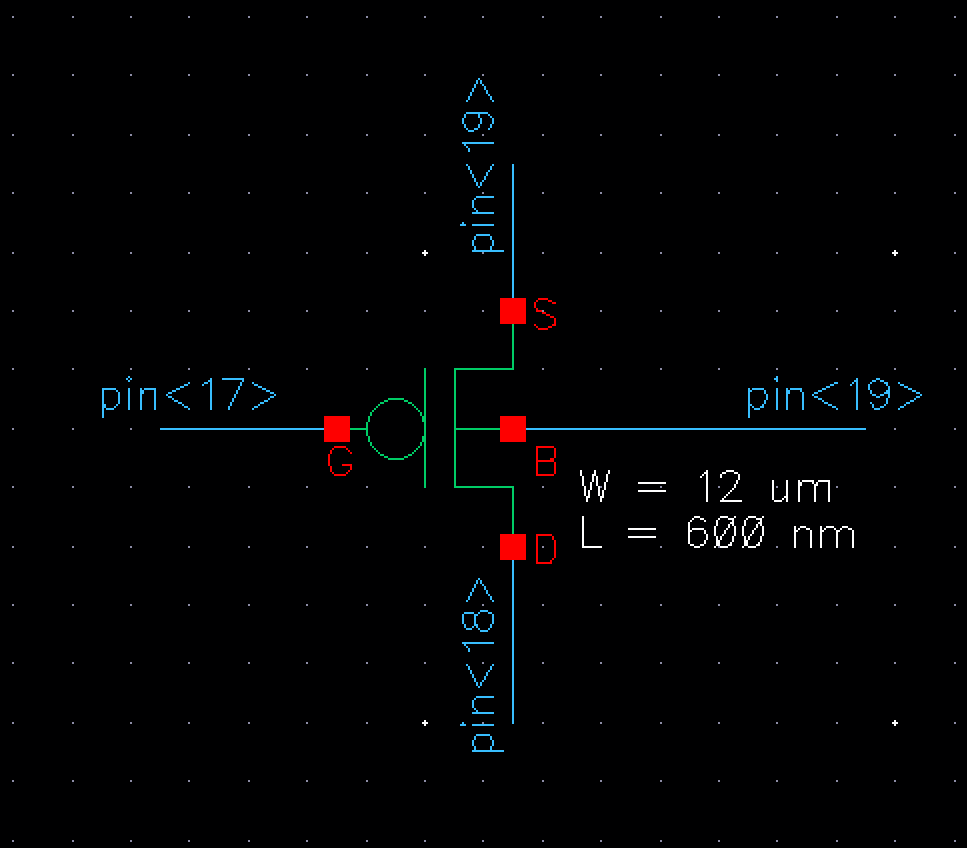

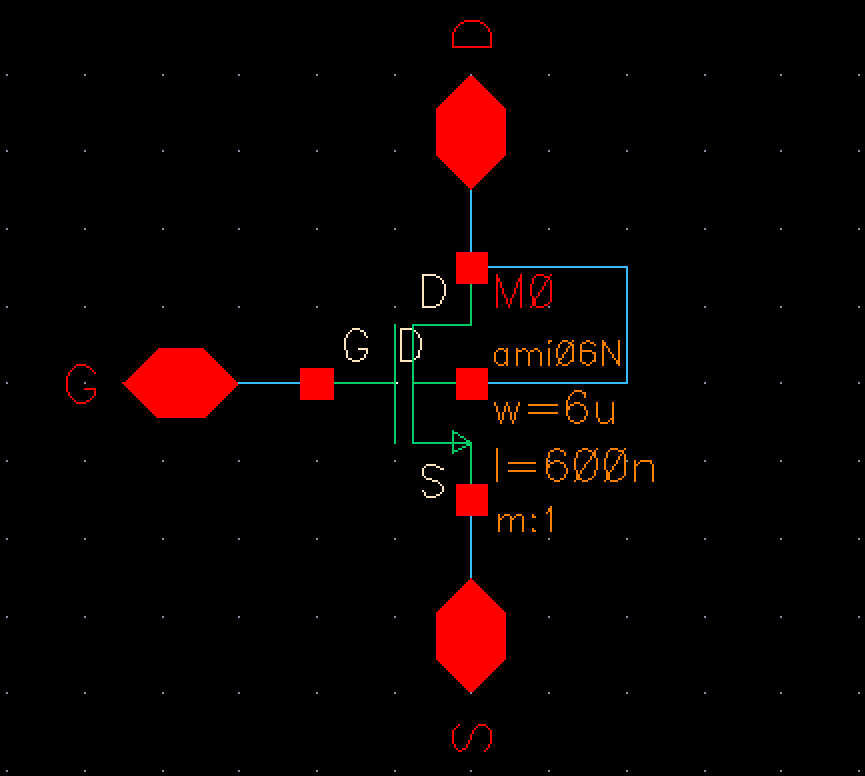

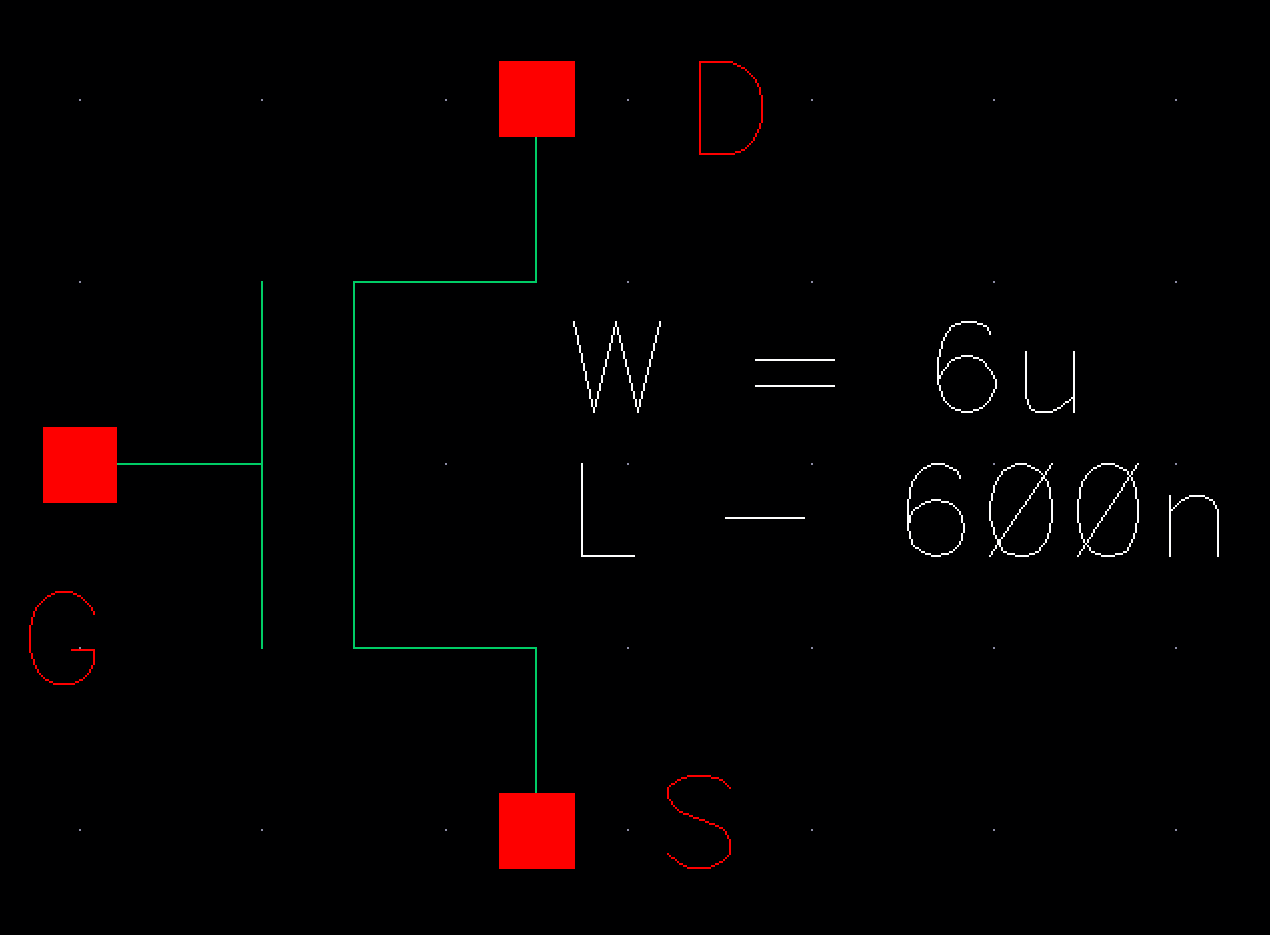

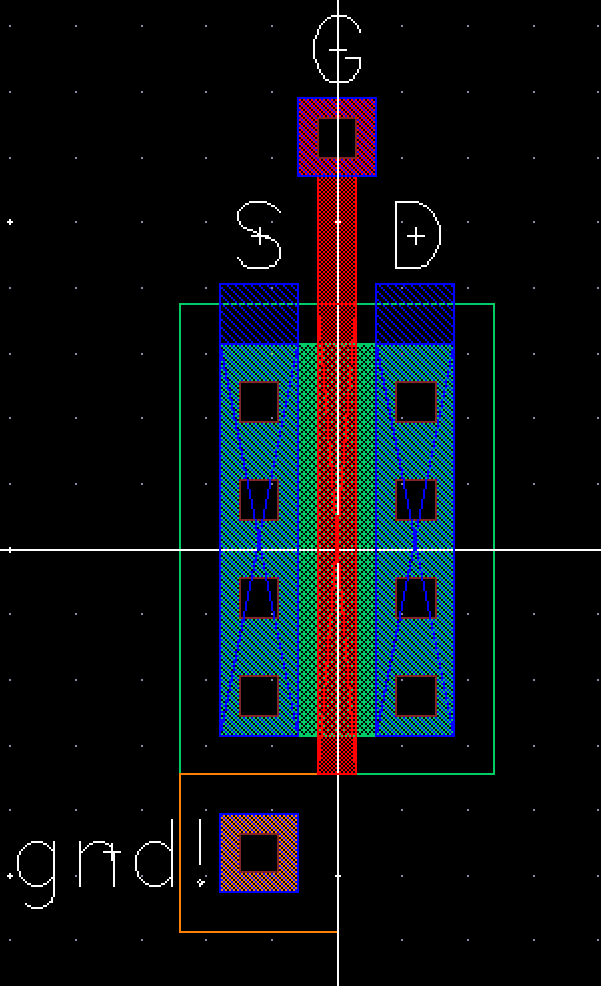

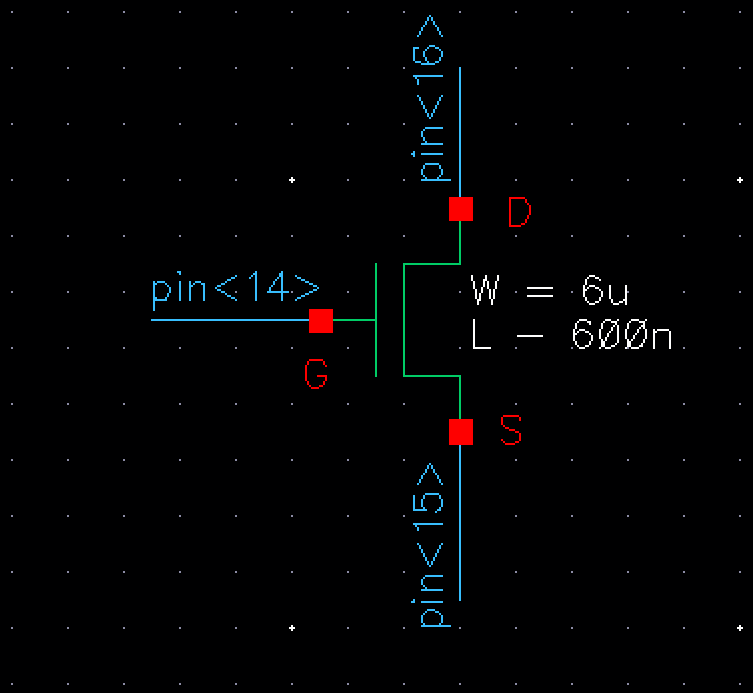

| NMOS 6u/0.6u: | |

|  |

|  |

G (Gate) -> Pin<14>

S (Source) -> Pin<15>

D (Drain) -> Pin<16>

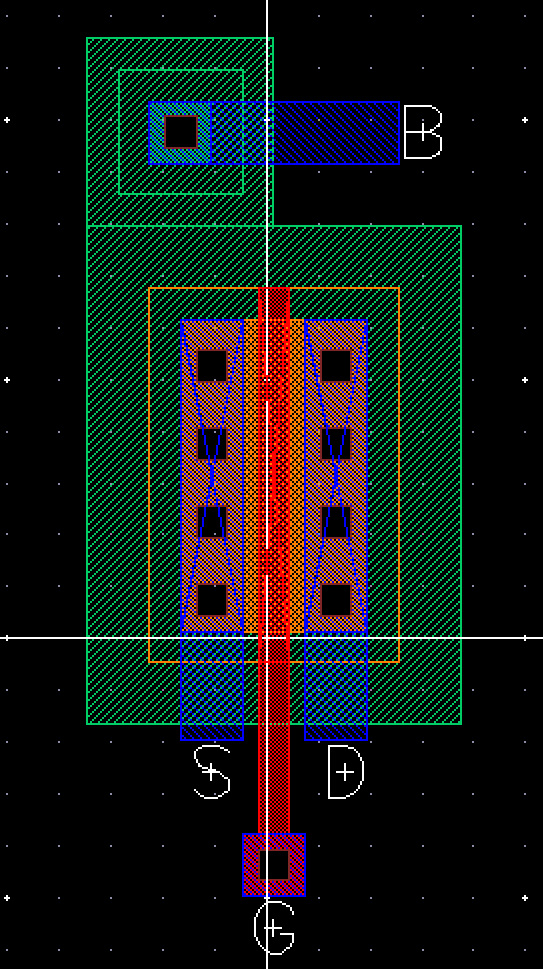

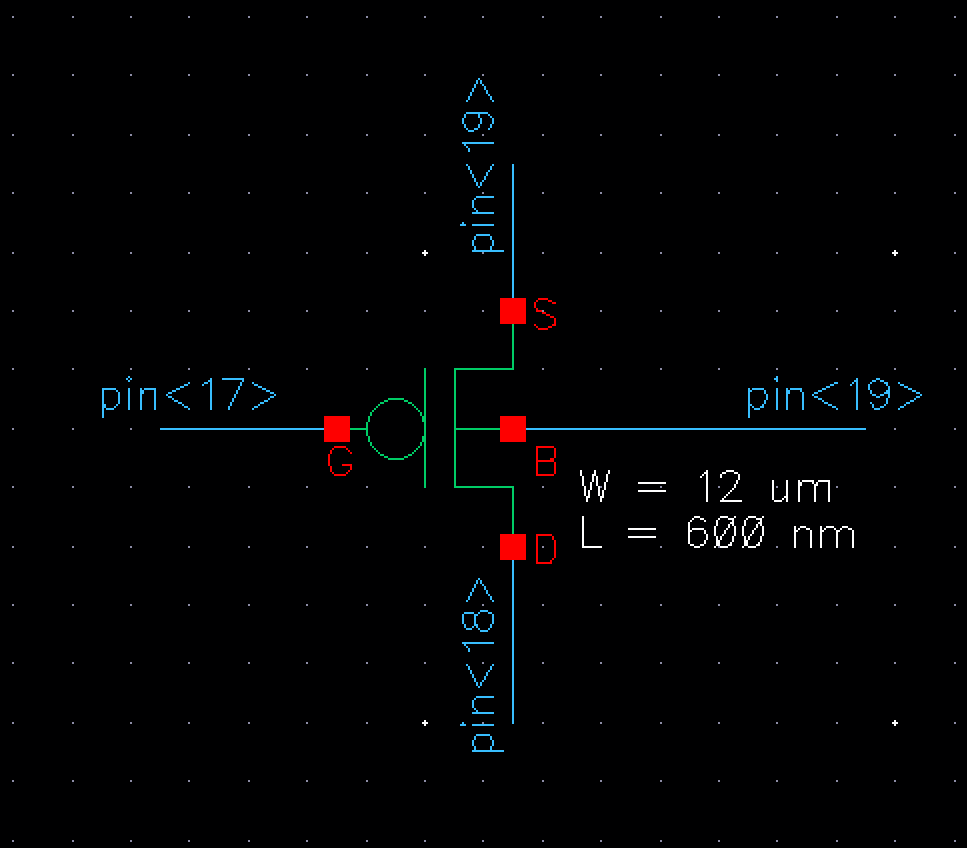

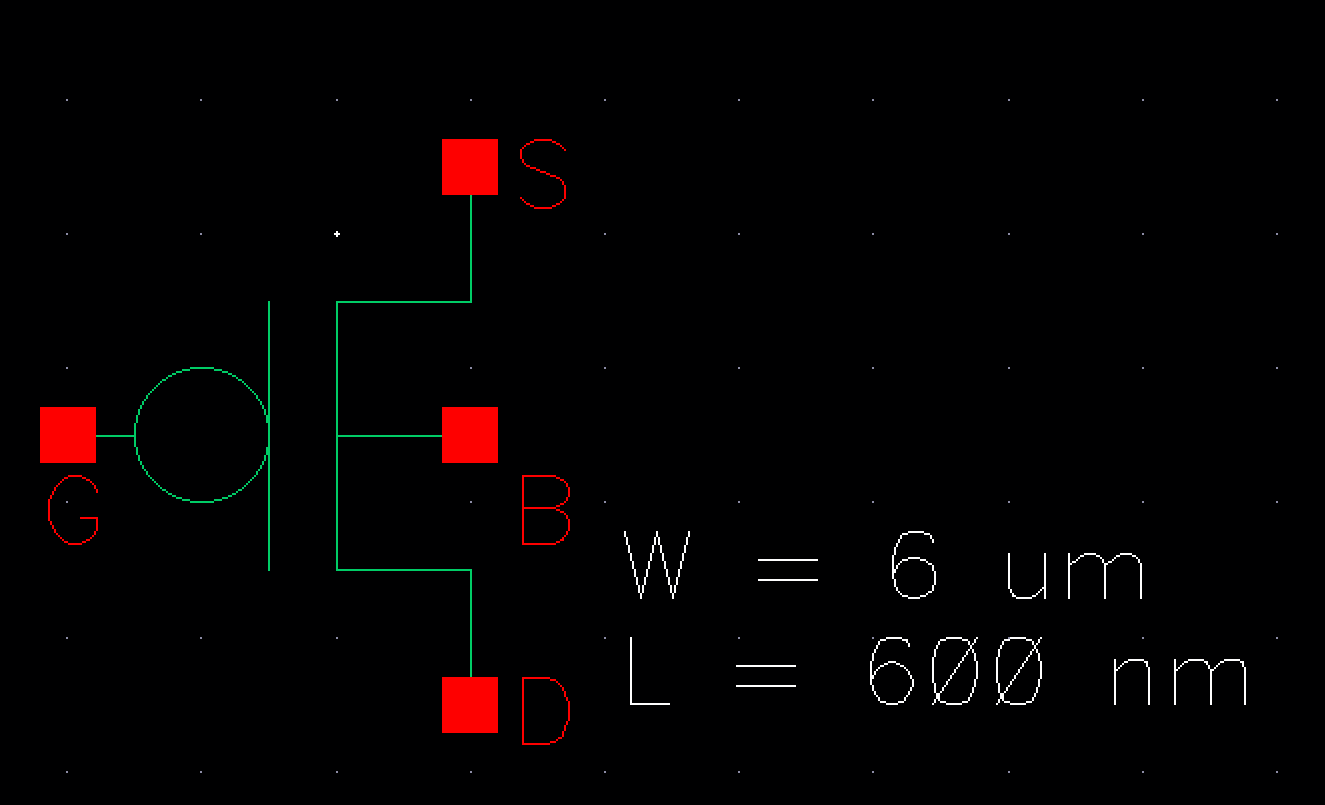

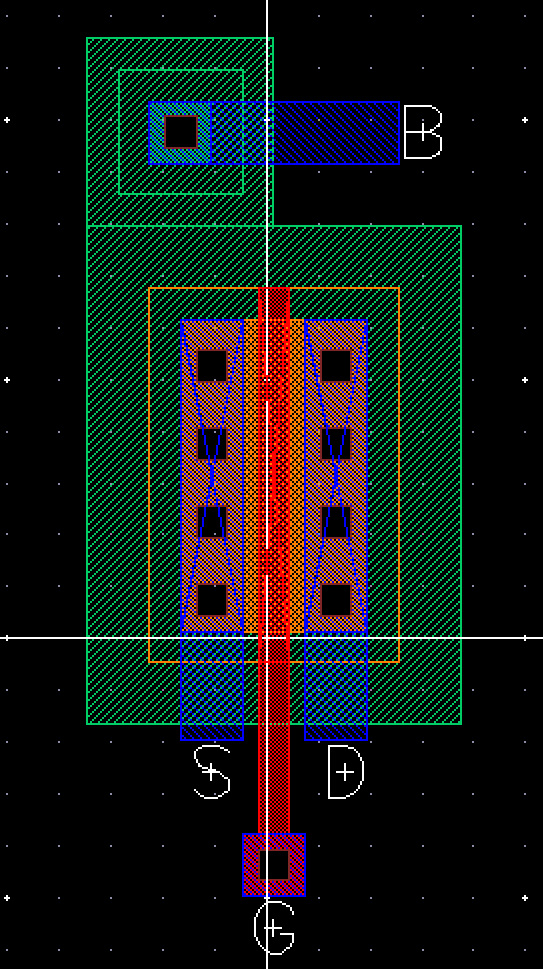

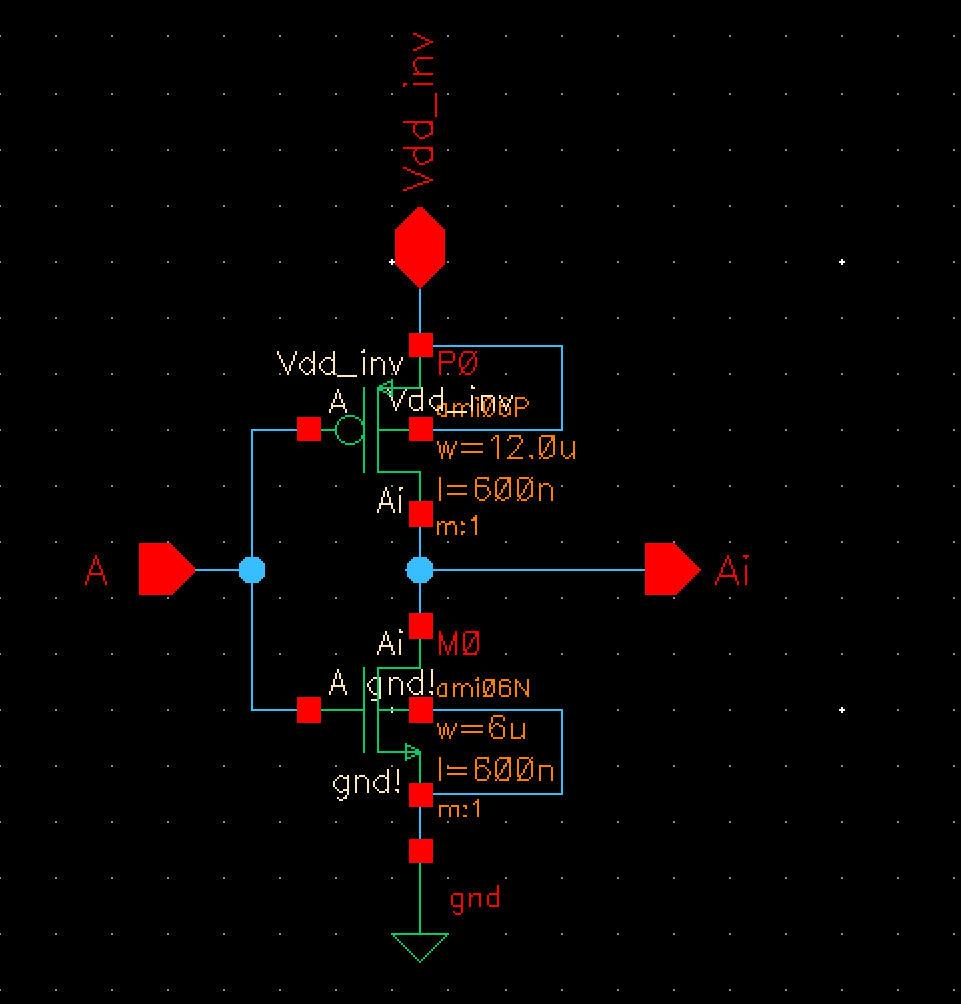

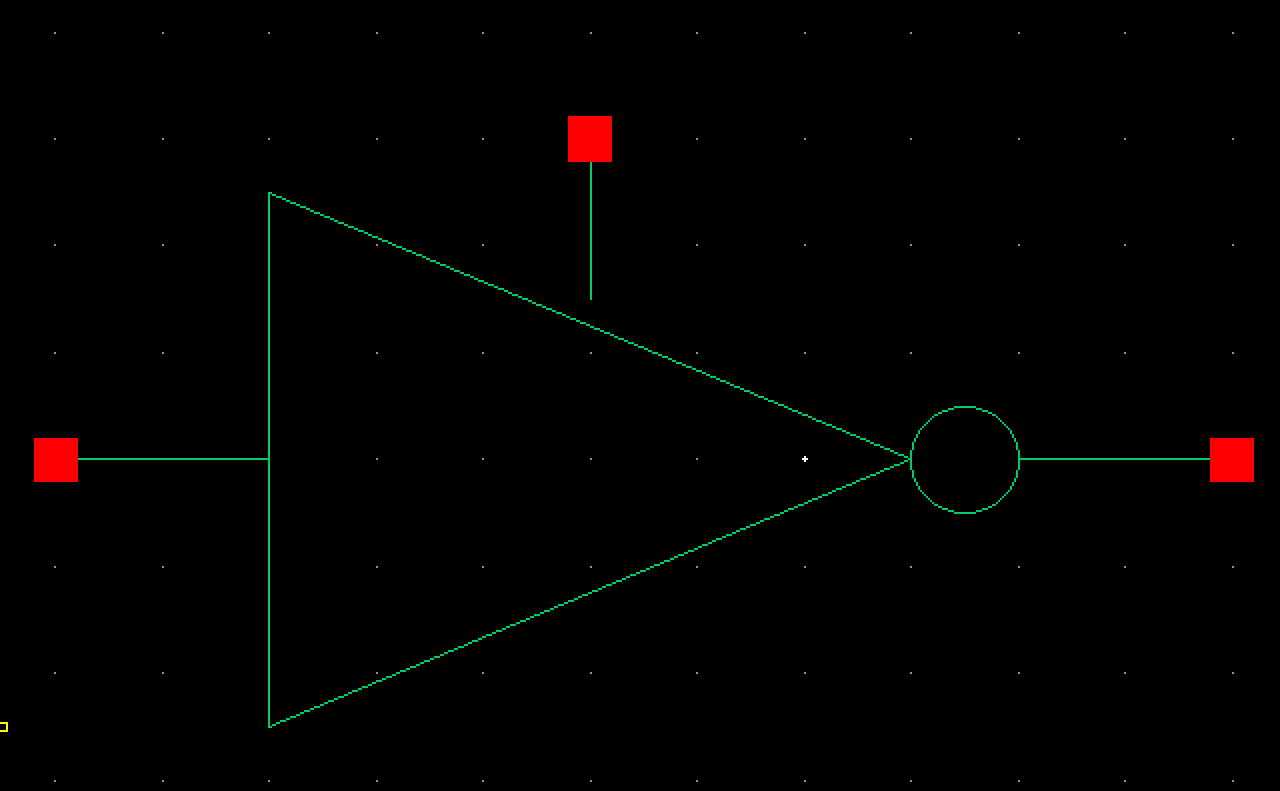

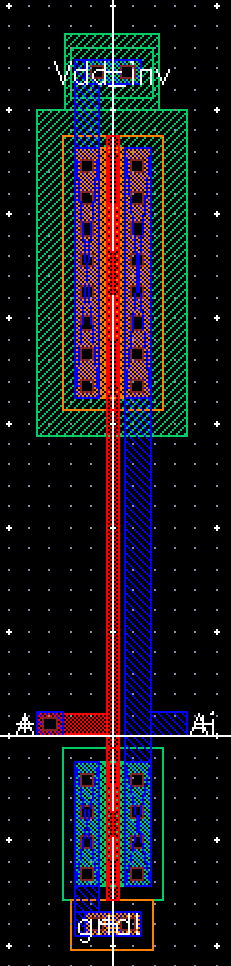

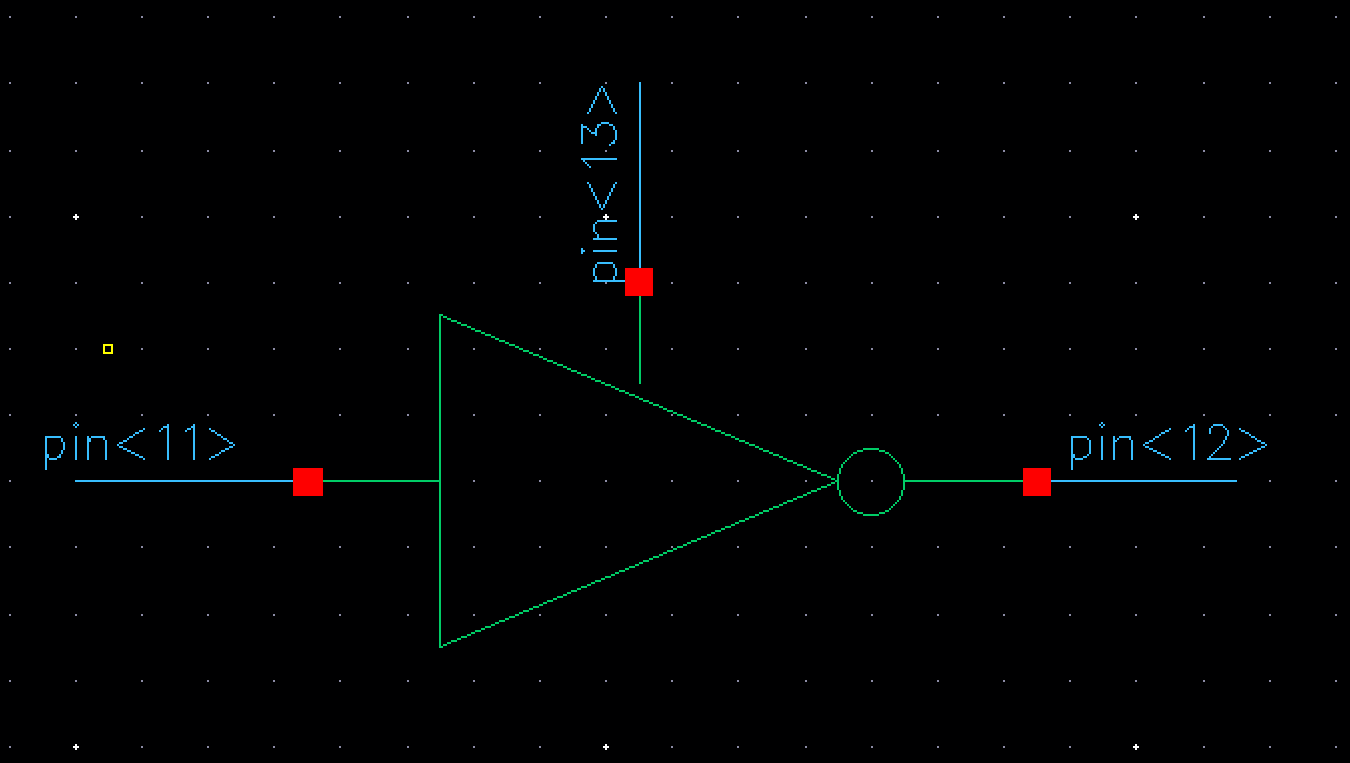

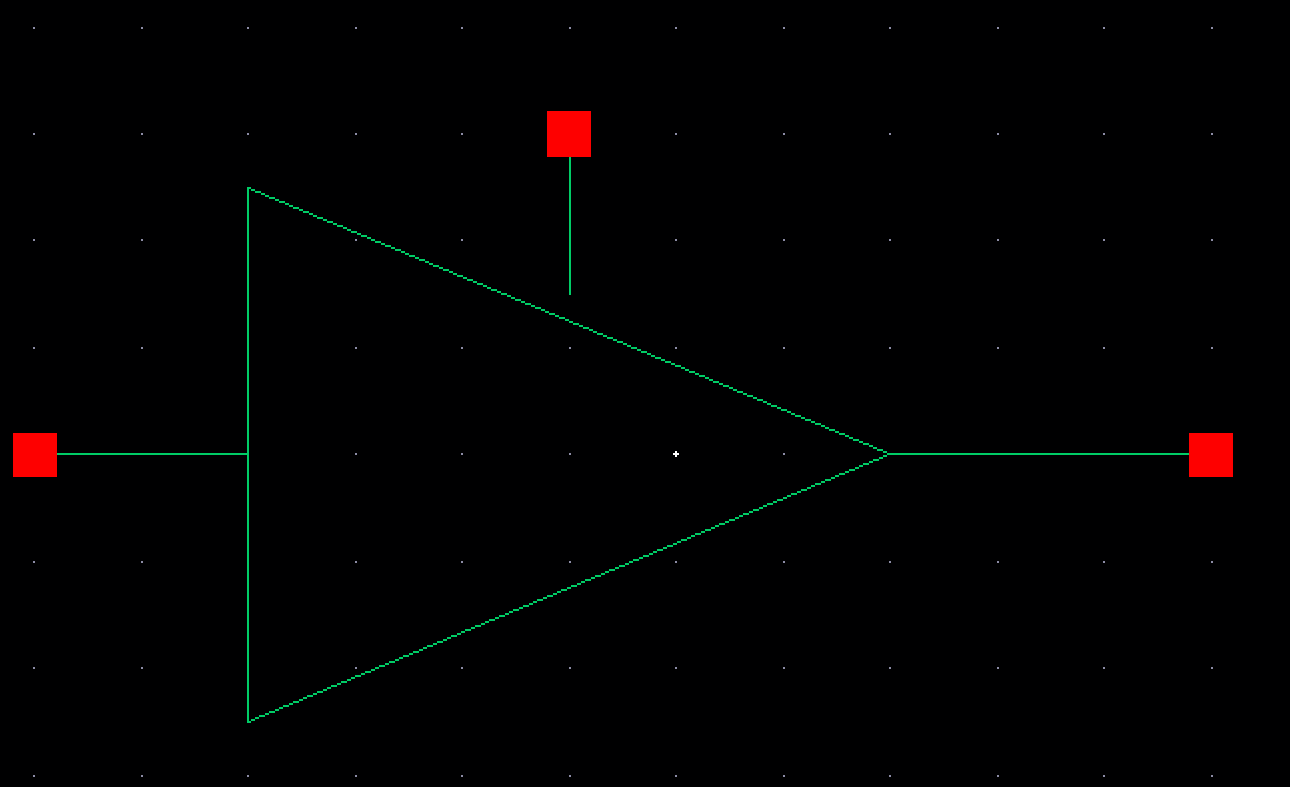

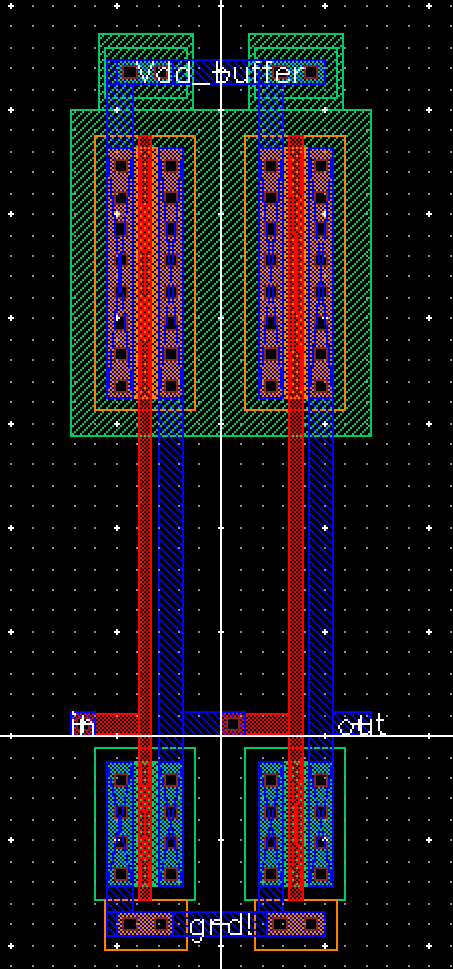

| Inverter 12u/6u: | |

|  |

|  |

A (Input) -> Pin<11>

Ai (Output) -> Pin<12>

Vdd_in -> Pin<13>

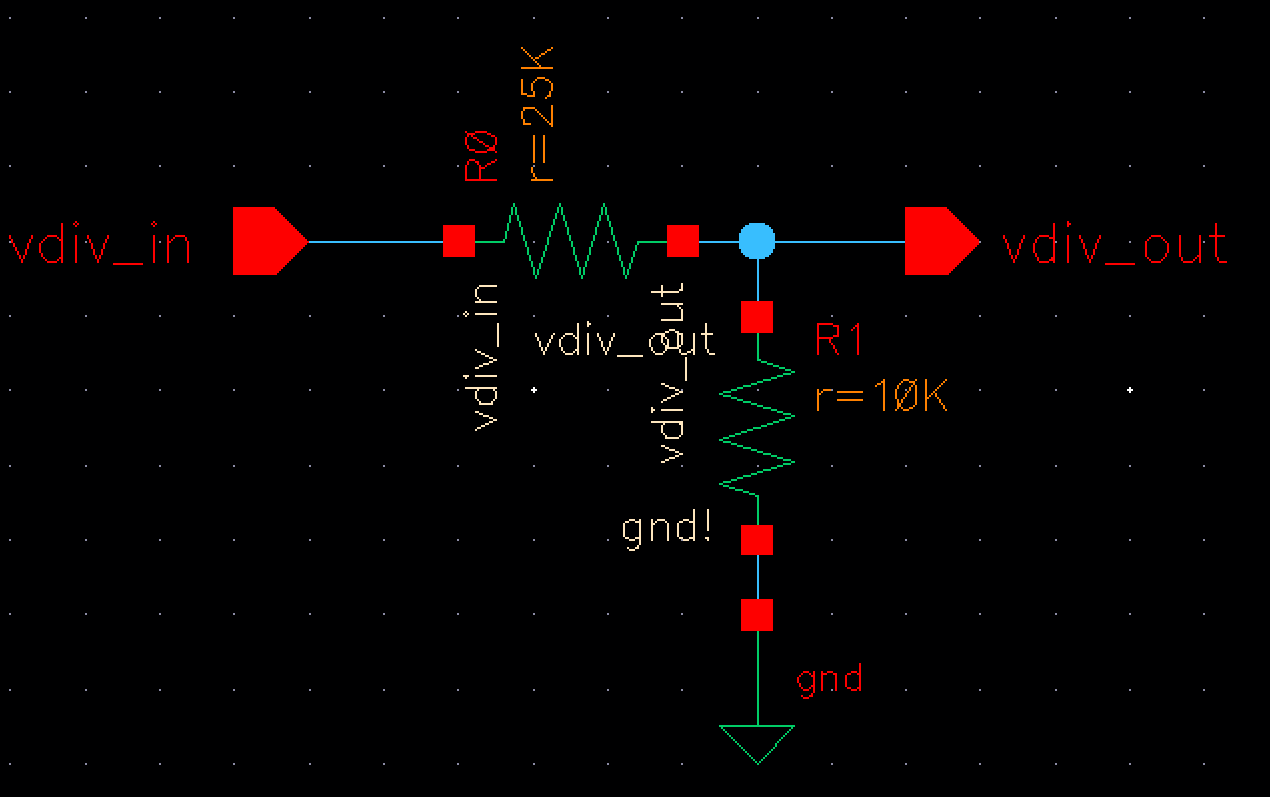

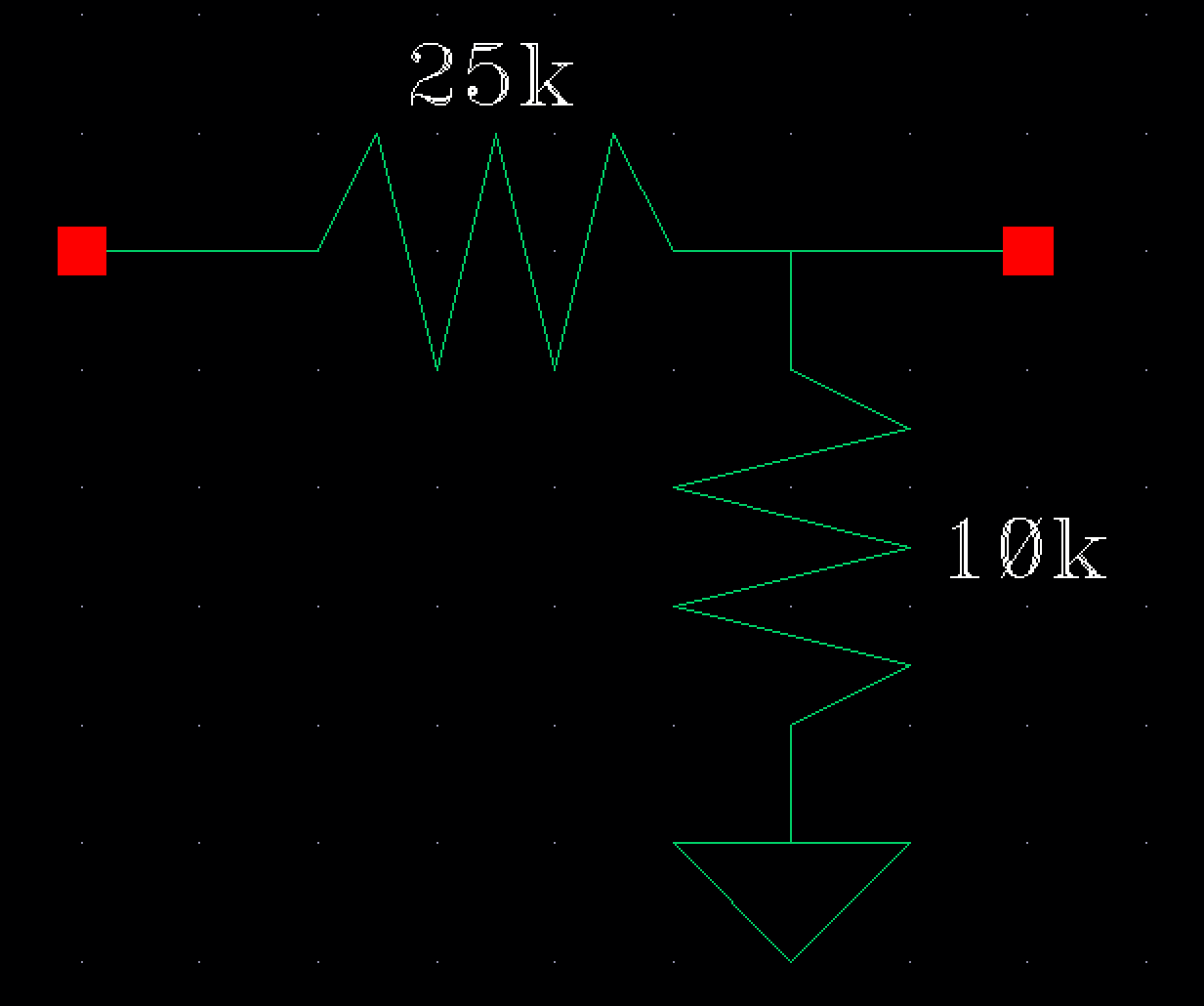

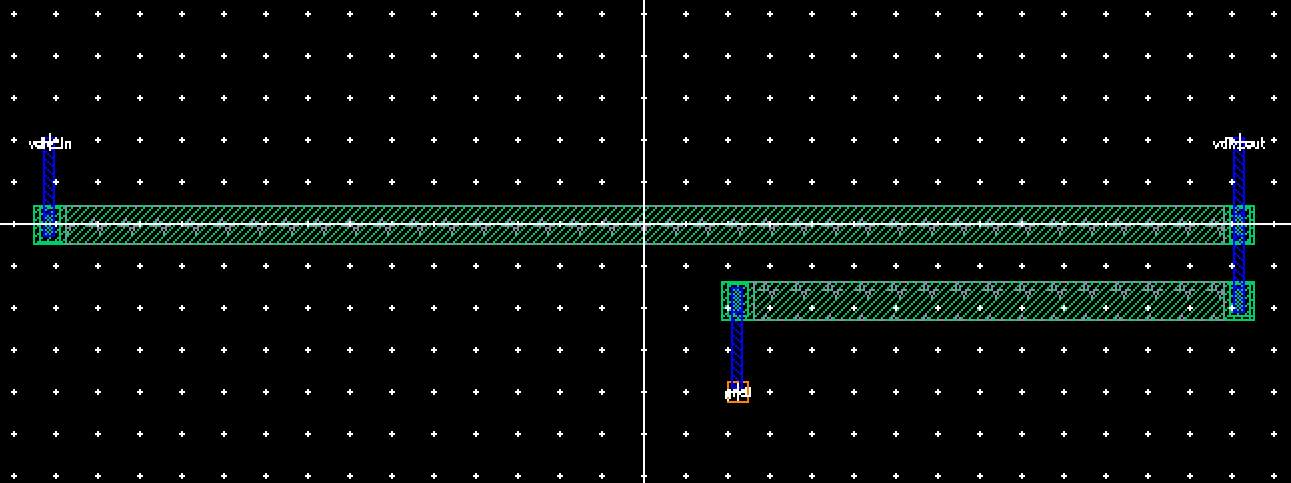

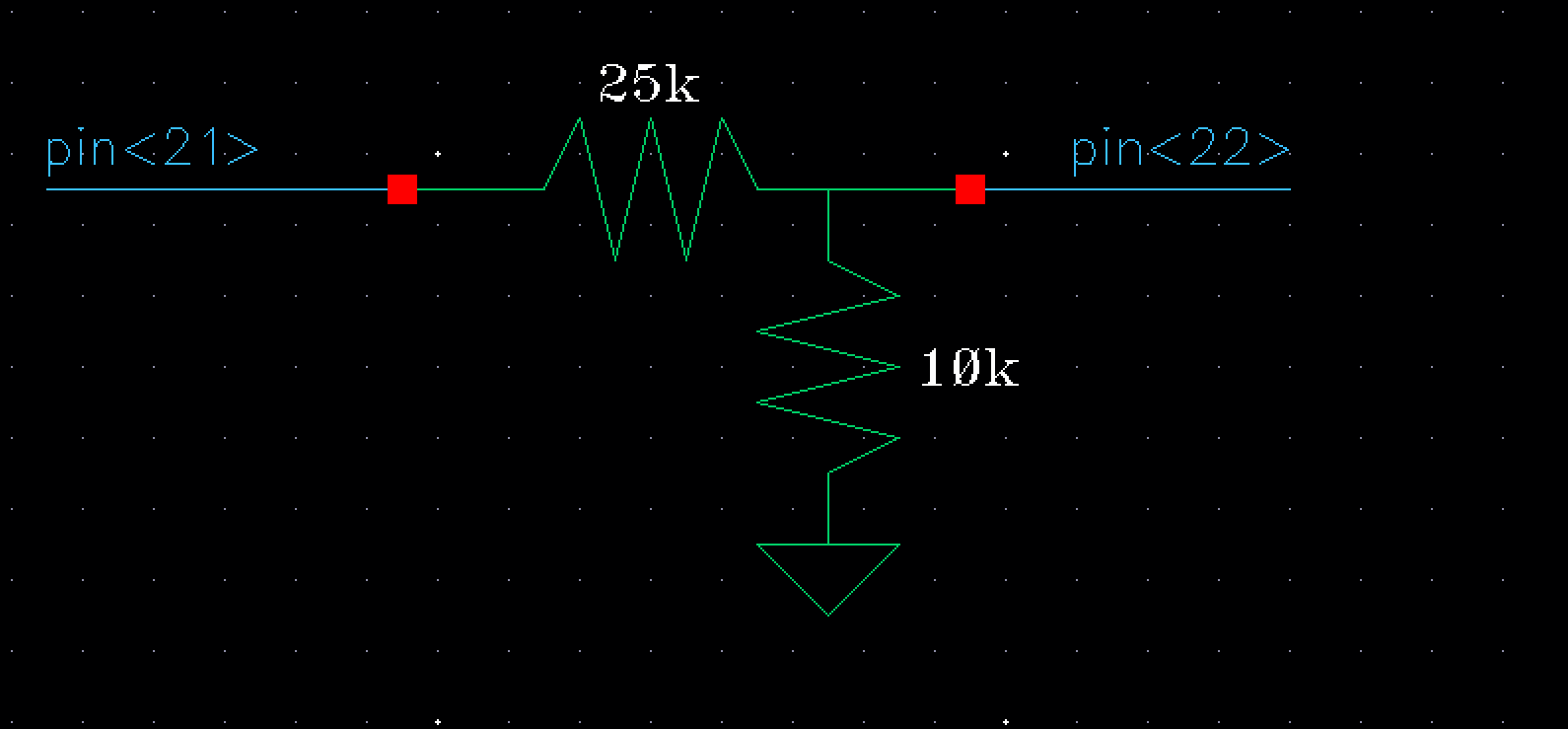

| Voltage Divider (25k and 10k): | |

|  |

|  |

Vdiv_in -> Pin<21>

Vdiv_out -> Pin<22>

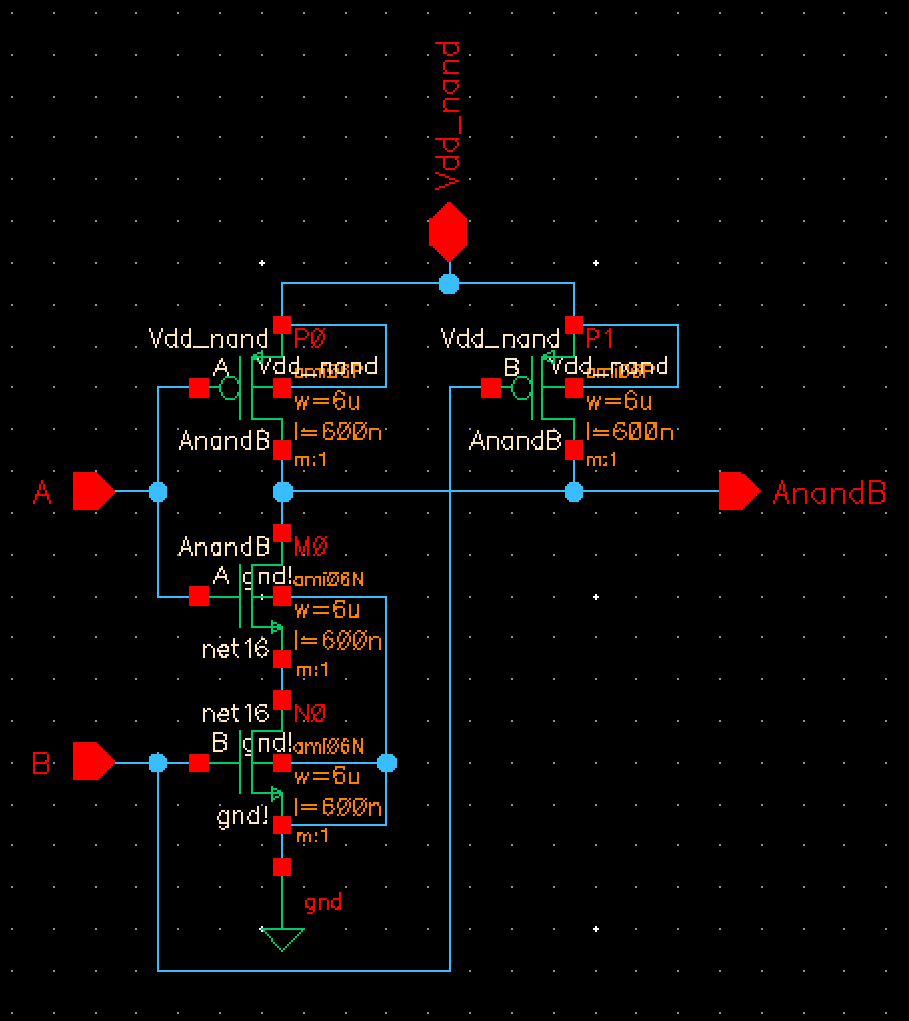

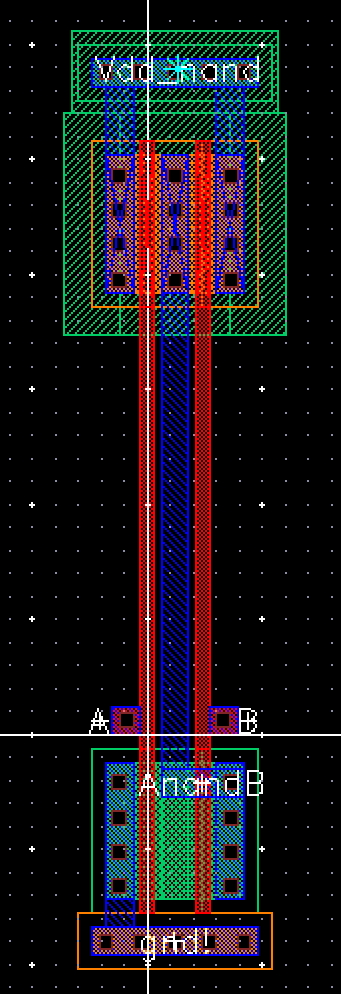

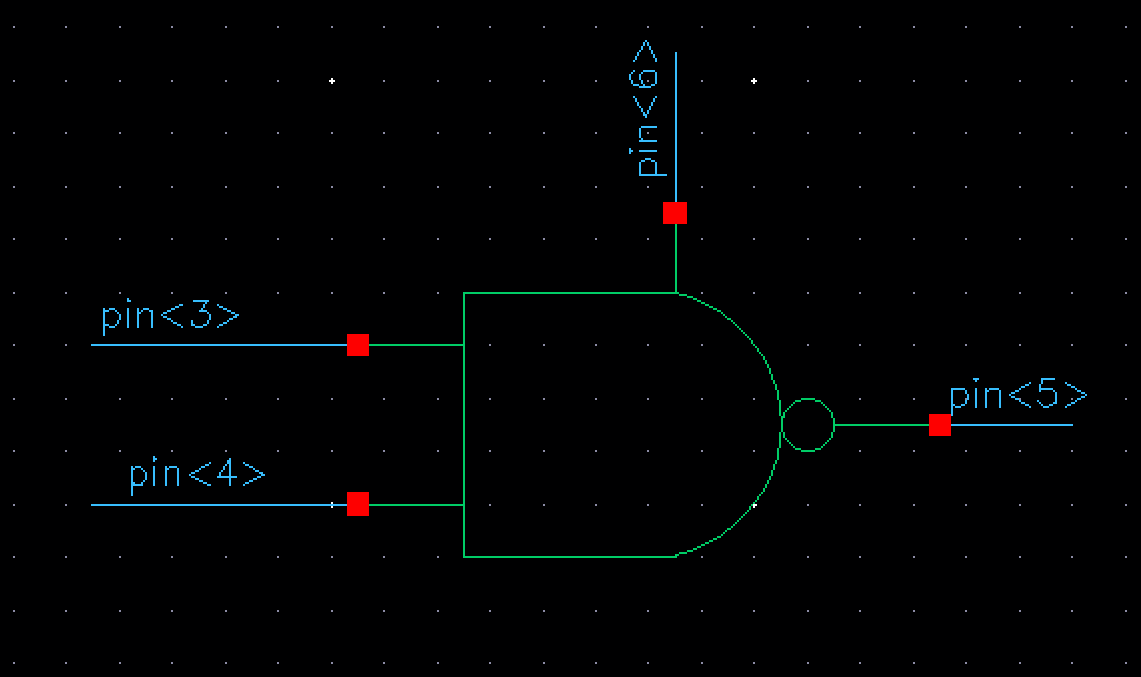

| NAND Gate 6u/6u: | |

|  |

|  |

A -> Pin<3>

B -> Pin<4>

AnandB -> Pin<5>

Vdd_nand -> Pin<6>

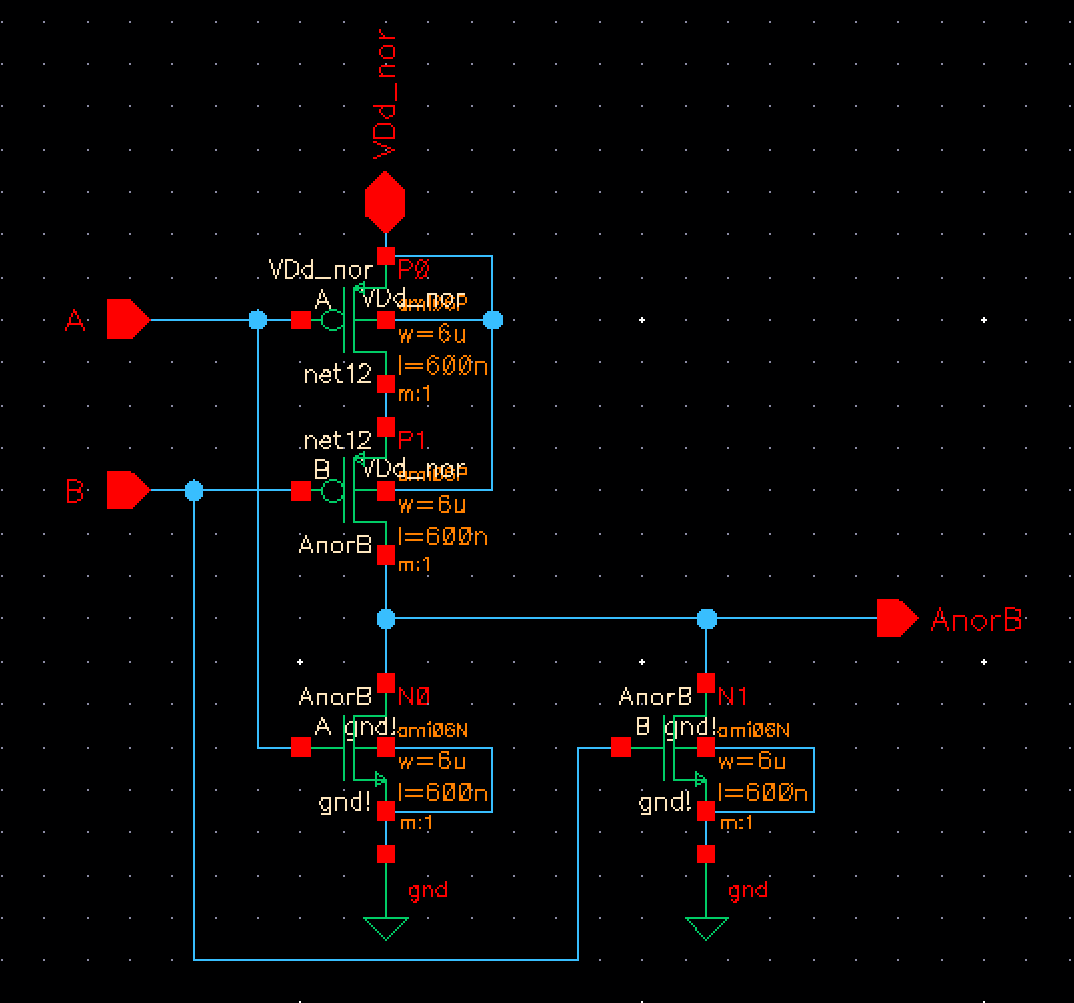

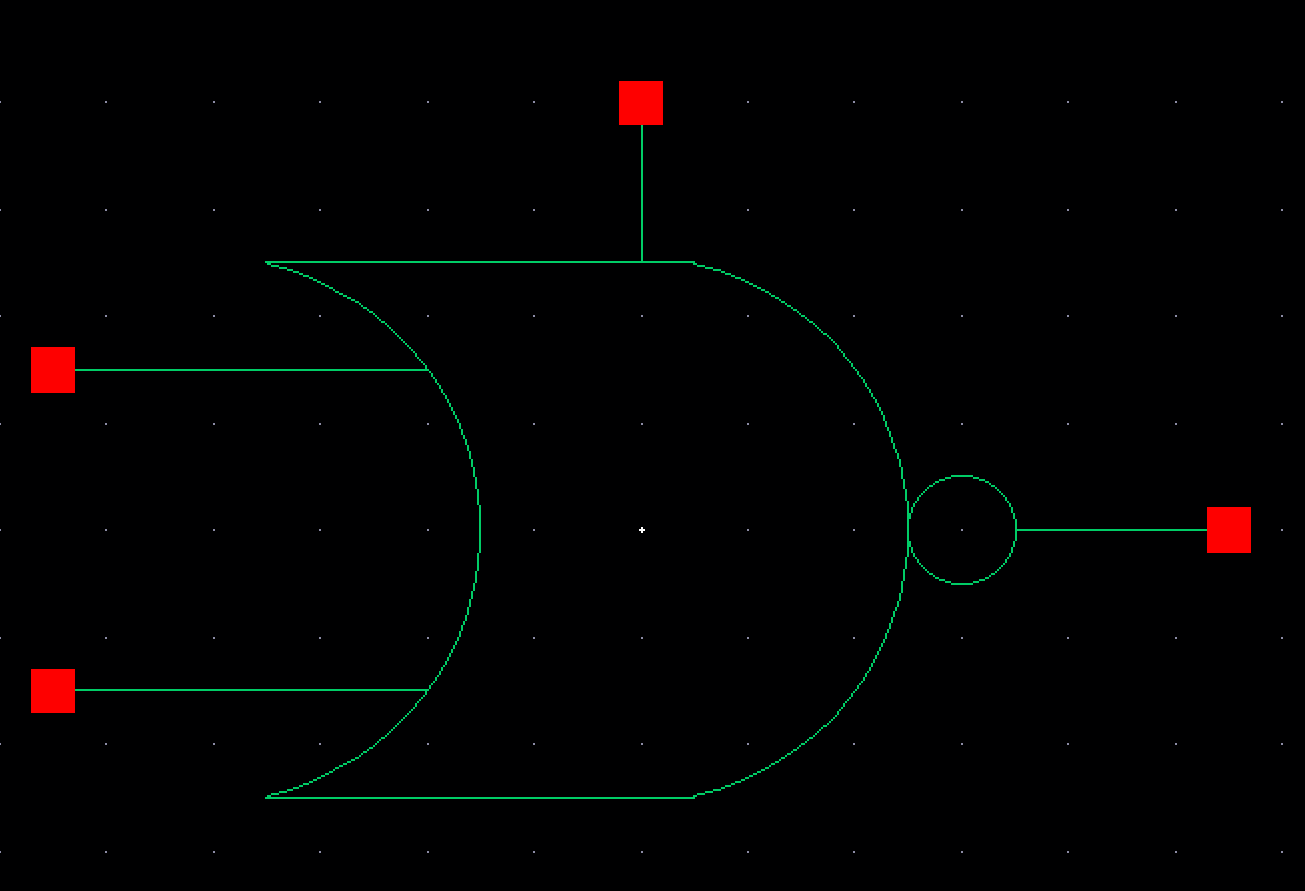

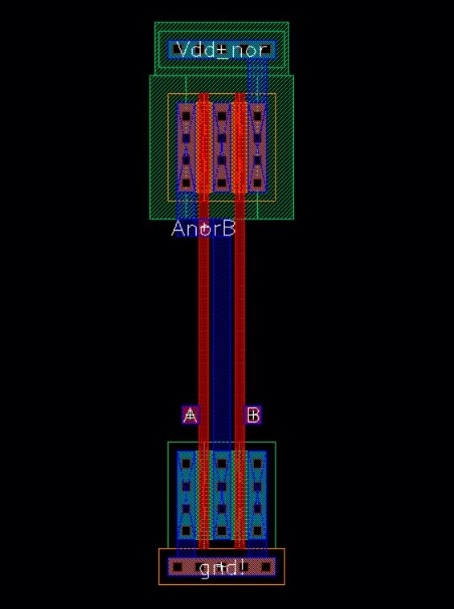

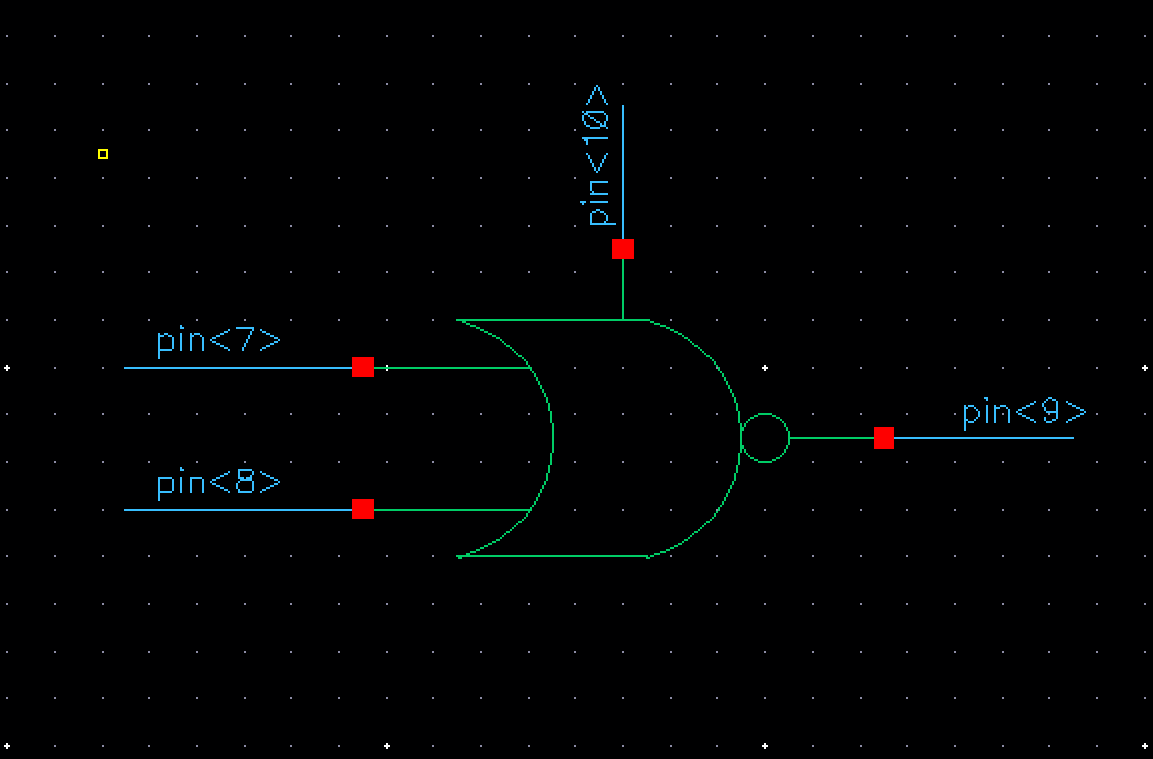

| NOR Gate 6u/6u: | |

|  |

|  |

A -> Pin<7>

B -> Pin<8>

AnandB -> Pin<9>

Vdd_nand -> Pin<10>

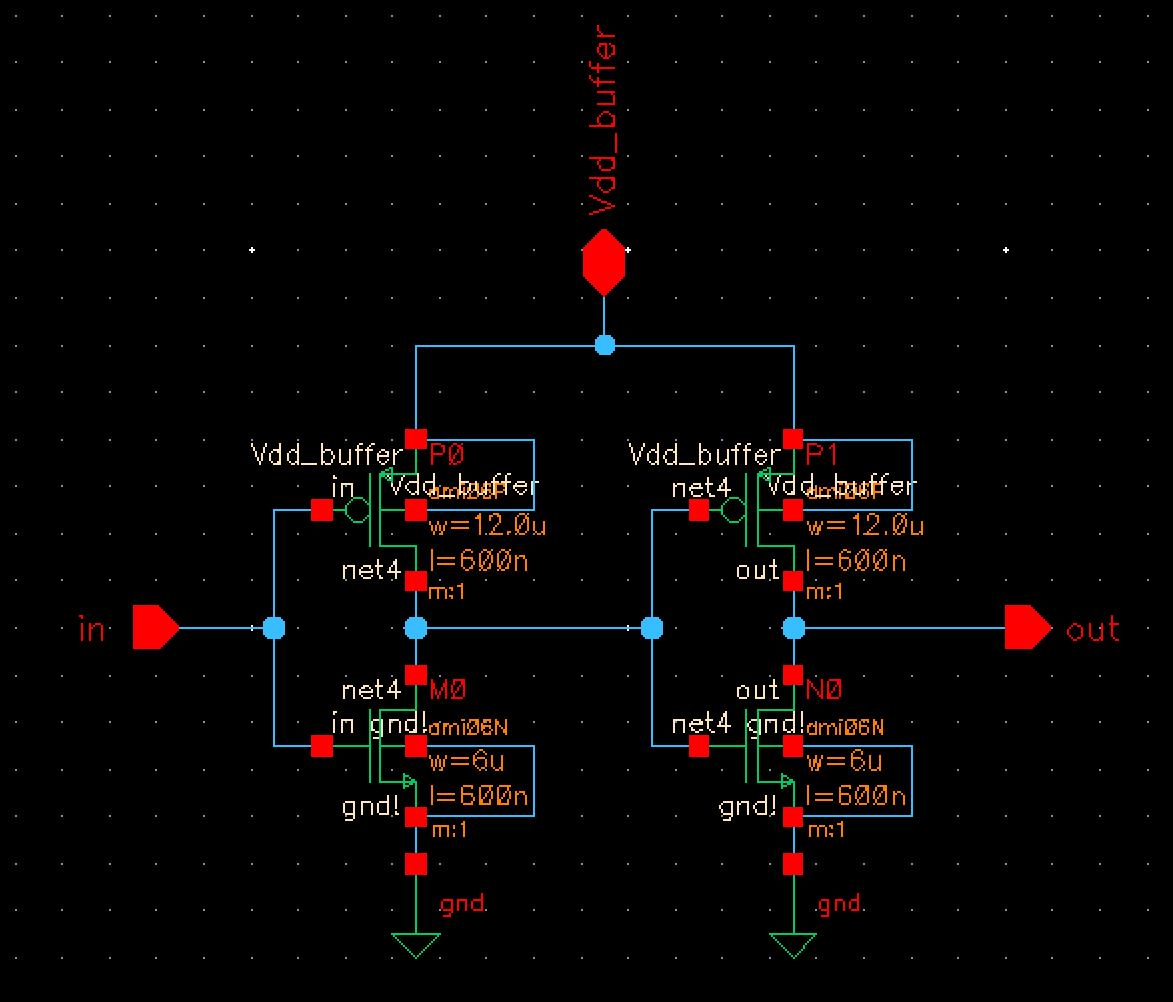

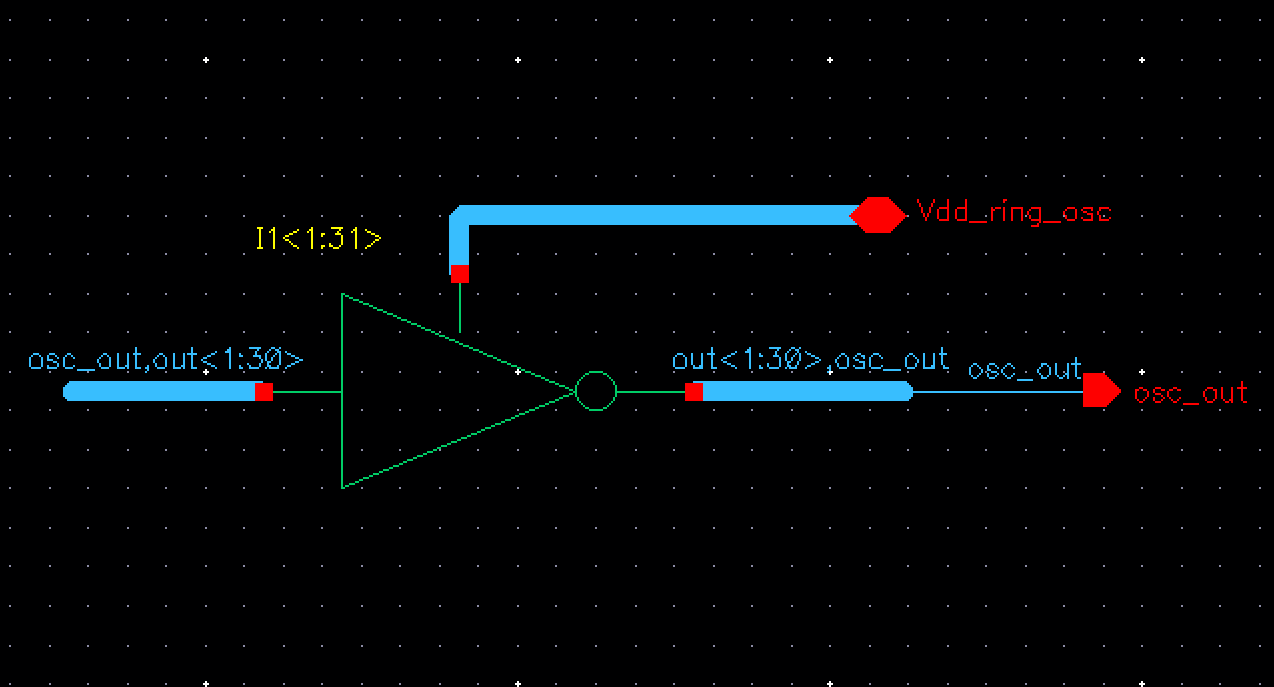

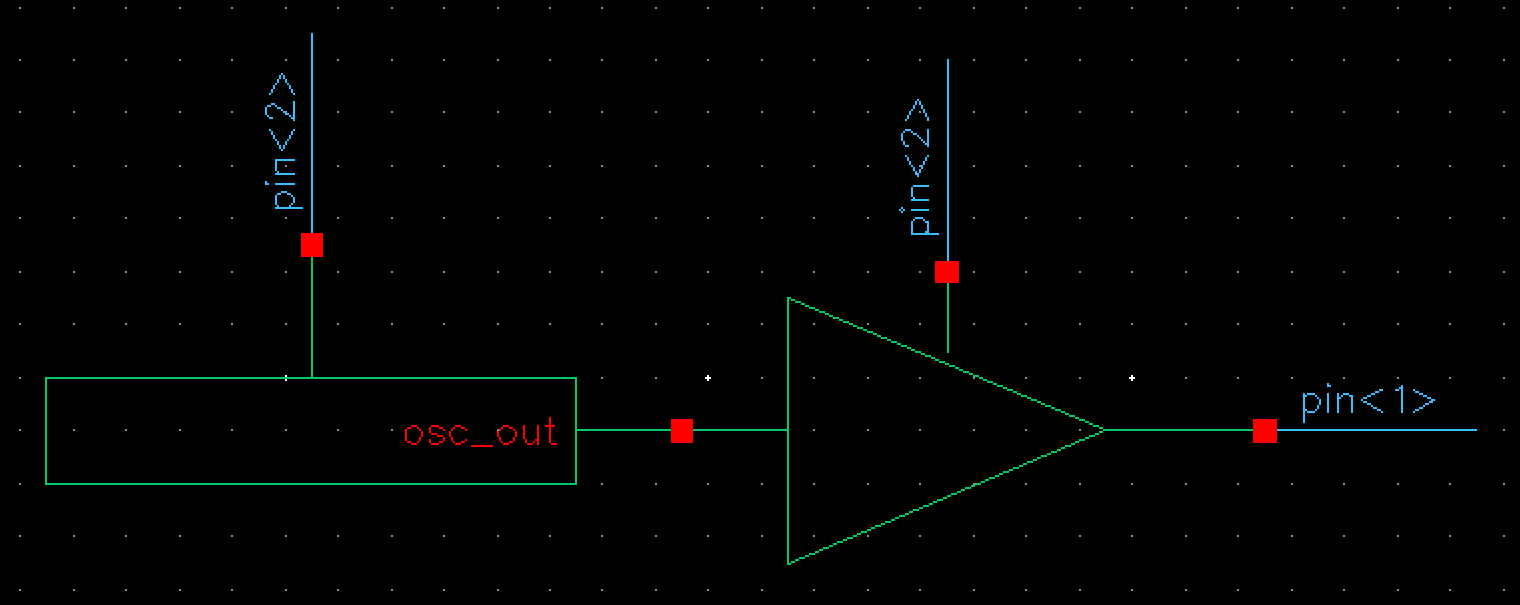

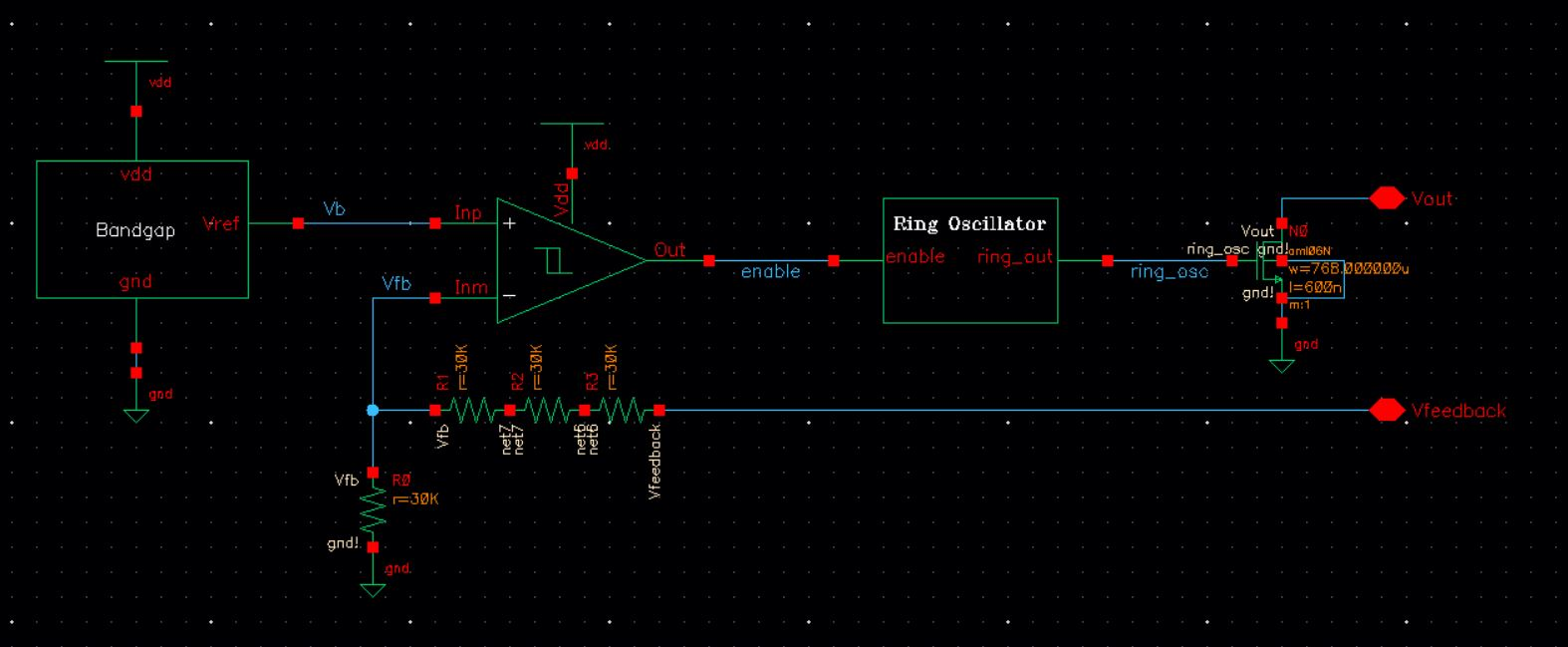

| 31-Stage Ring Oscillator w/ Buffer: | |

|  |

|  |

| |

|  |

pin_out -> Pin<1>

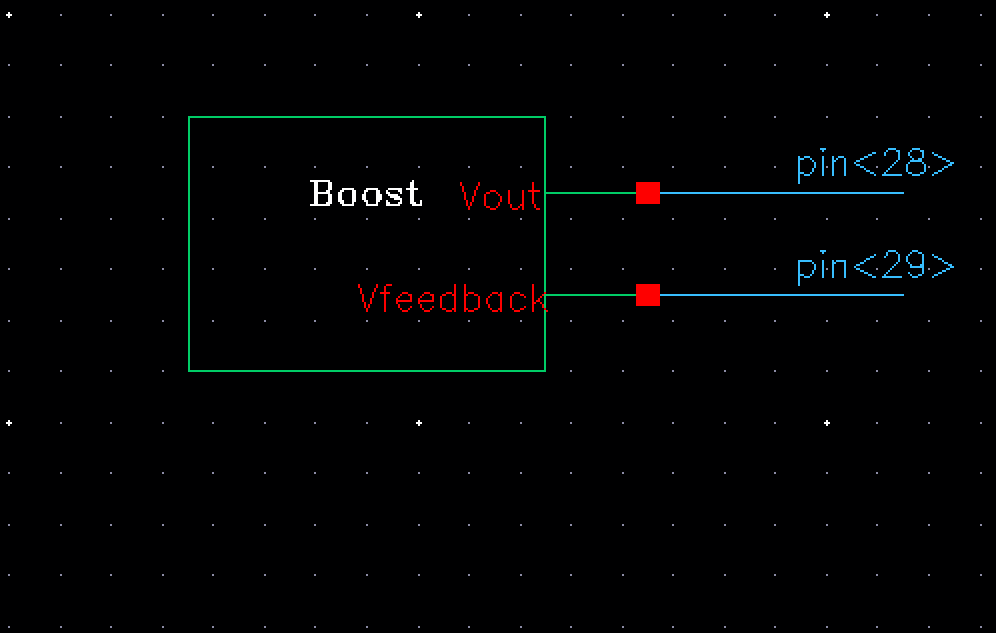

pin_in -> Pin<2>| Boost Converter: |

|

|

|

Vout -> Pin<28>

Vfeedback -> Pin<29>

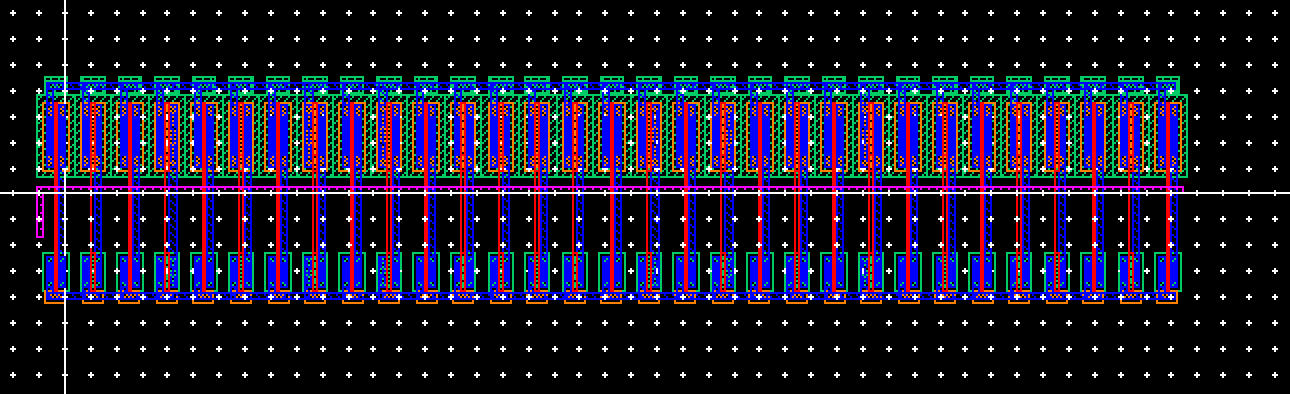

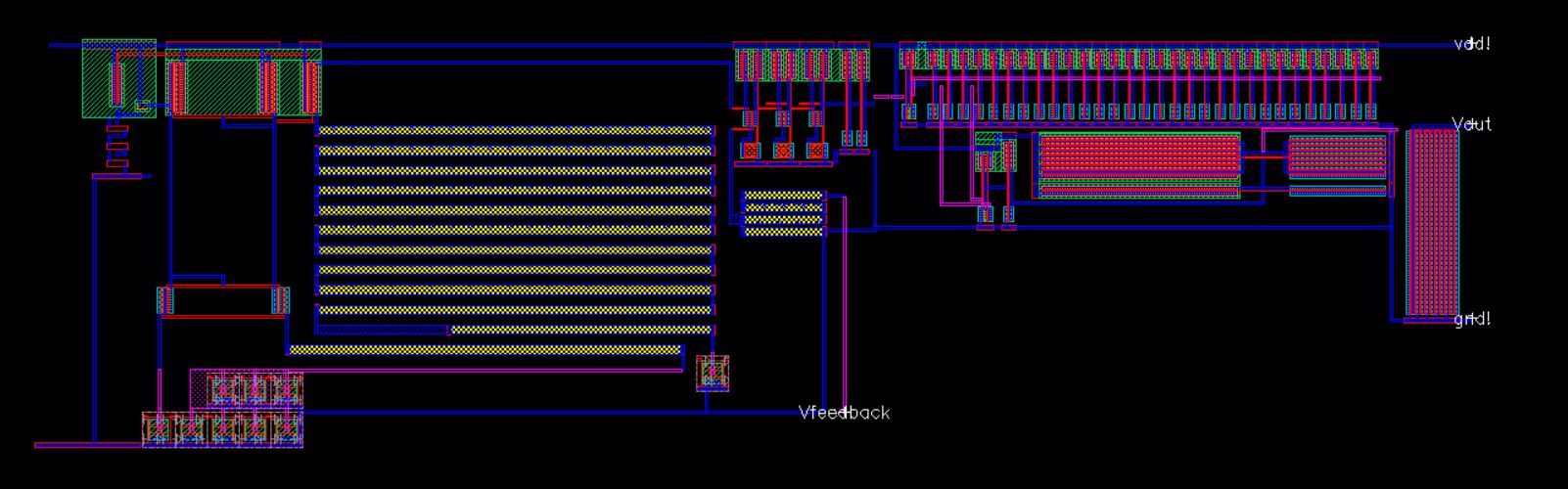

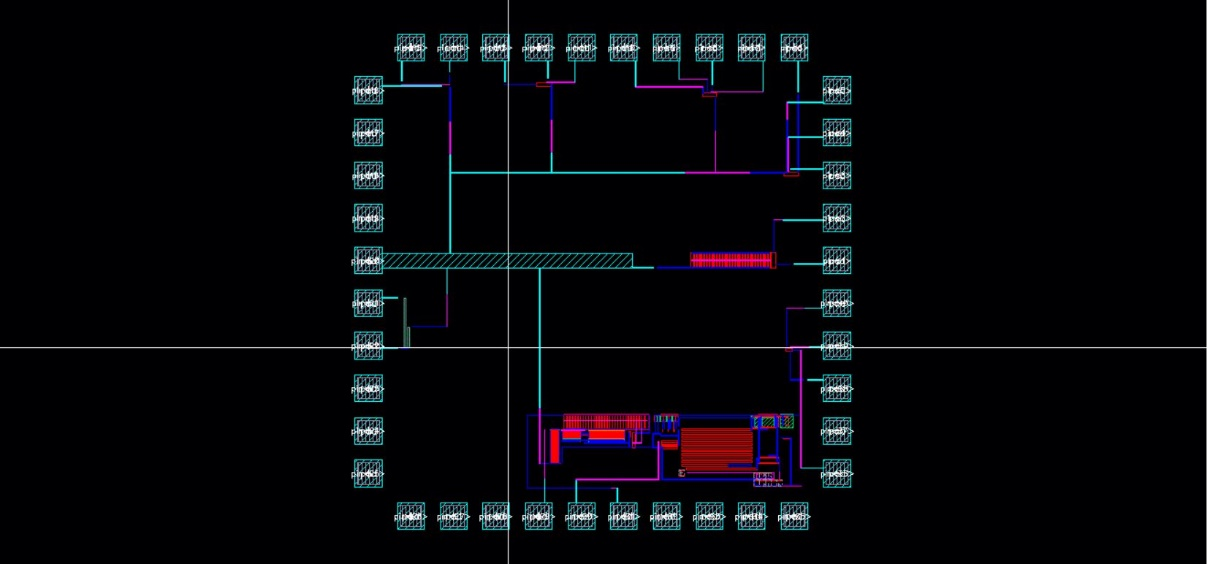

| Chip3 Design: |

|

|

Summary of Chip Design:

The Chip layout and Design can be downloaded through this link.

----------------------------------------------------------------------------------------------------

This Concludes the Lab 8 Report.