Lab 3 - EE 421L

Authored

by Angel Solis, Solisa1@unlv.nevada.edu

Today's

date : 9/12/17

Lab

description

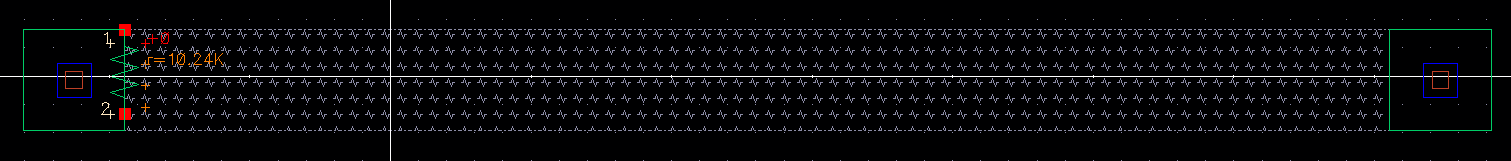

To

create an n-well 10k resistor in layout you have to decide on a length

and width. To save space a width of 3.6 microns is used as it is the

smallest allowable. This is because the manufacturing process we are working with uses 300nm.

12λ must be used for the width so this is why 3.6 microns is used.

L=10k/800*3.6 = 45 microns

Using this length we get a resistor with a value close to 10K as shown below.

This value is not exactly as expected as in layout R_square is around 820 ohms/square, where 800 was used in the equation.

The length of the n-well resistor can be checked by using the ruler tool (k) in cadence.

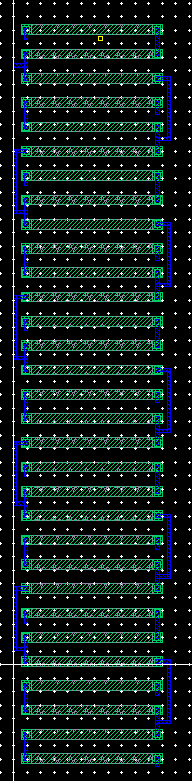

a) The same 10 bit DAC created in lab2 can be

implemented with n-well resistors laid out parallel to one another in layout as

shown below:

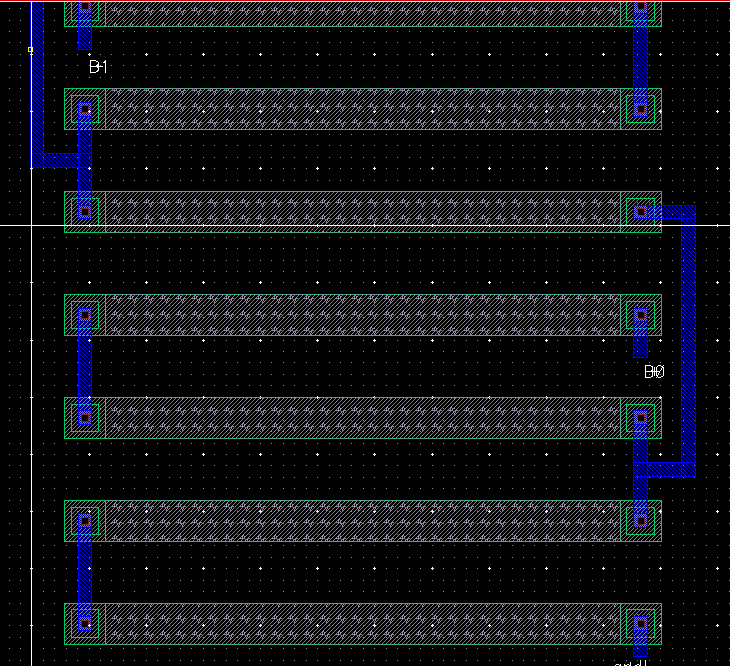

Below is a zoomed in view to show details.

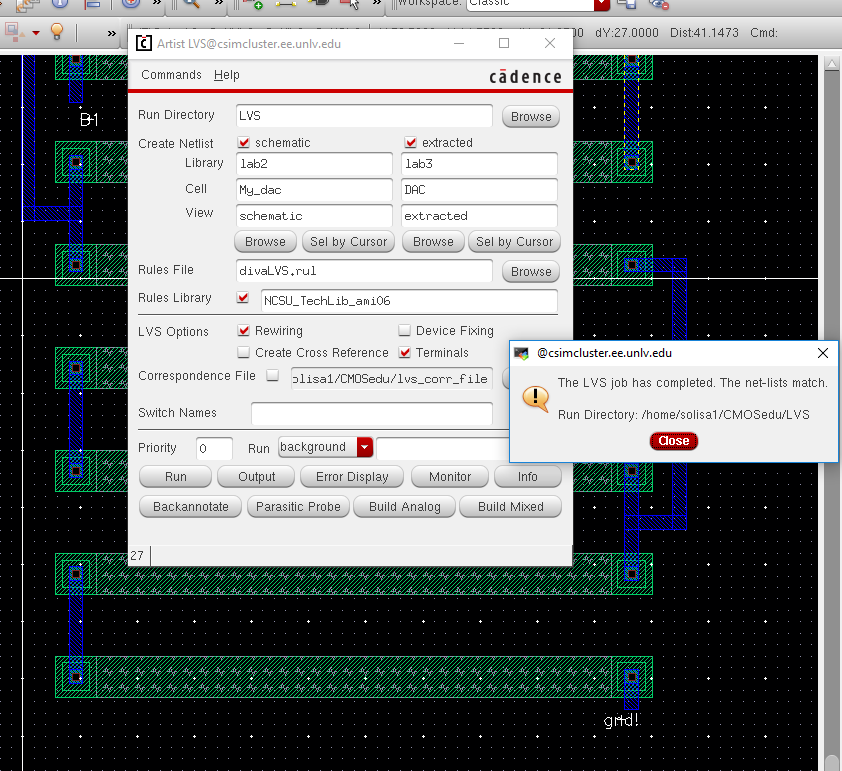

Lvs output can be found below:

Link to a detailed output from LVS

Link to Zip of lab 2 and 3

Return to EE 421L Labs