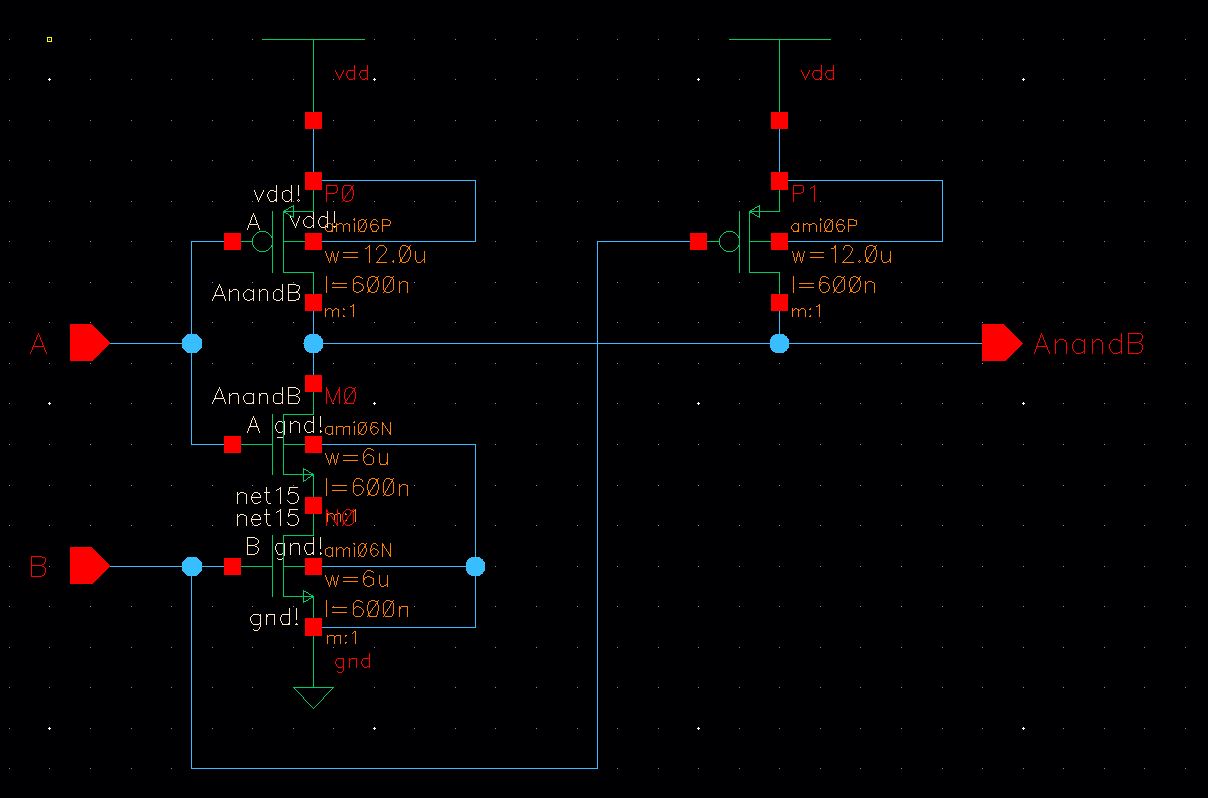

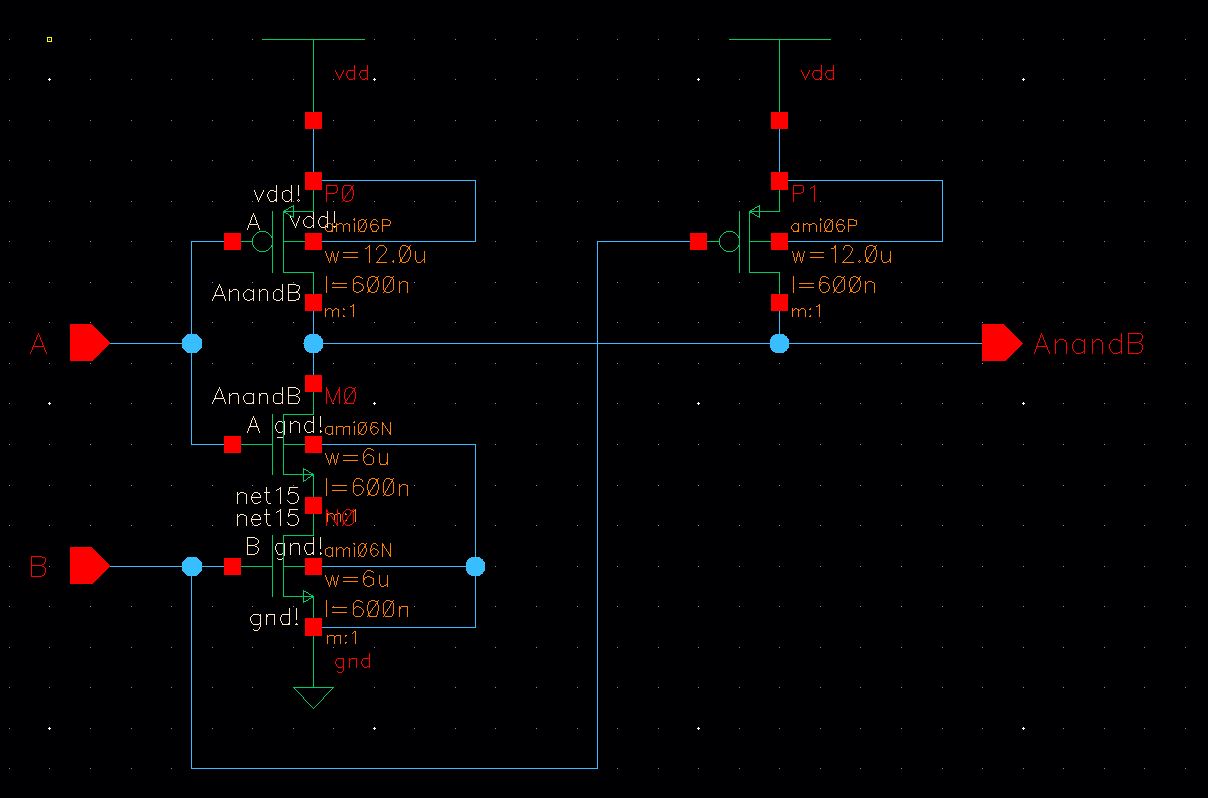

Nand Schematic View

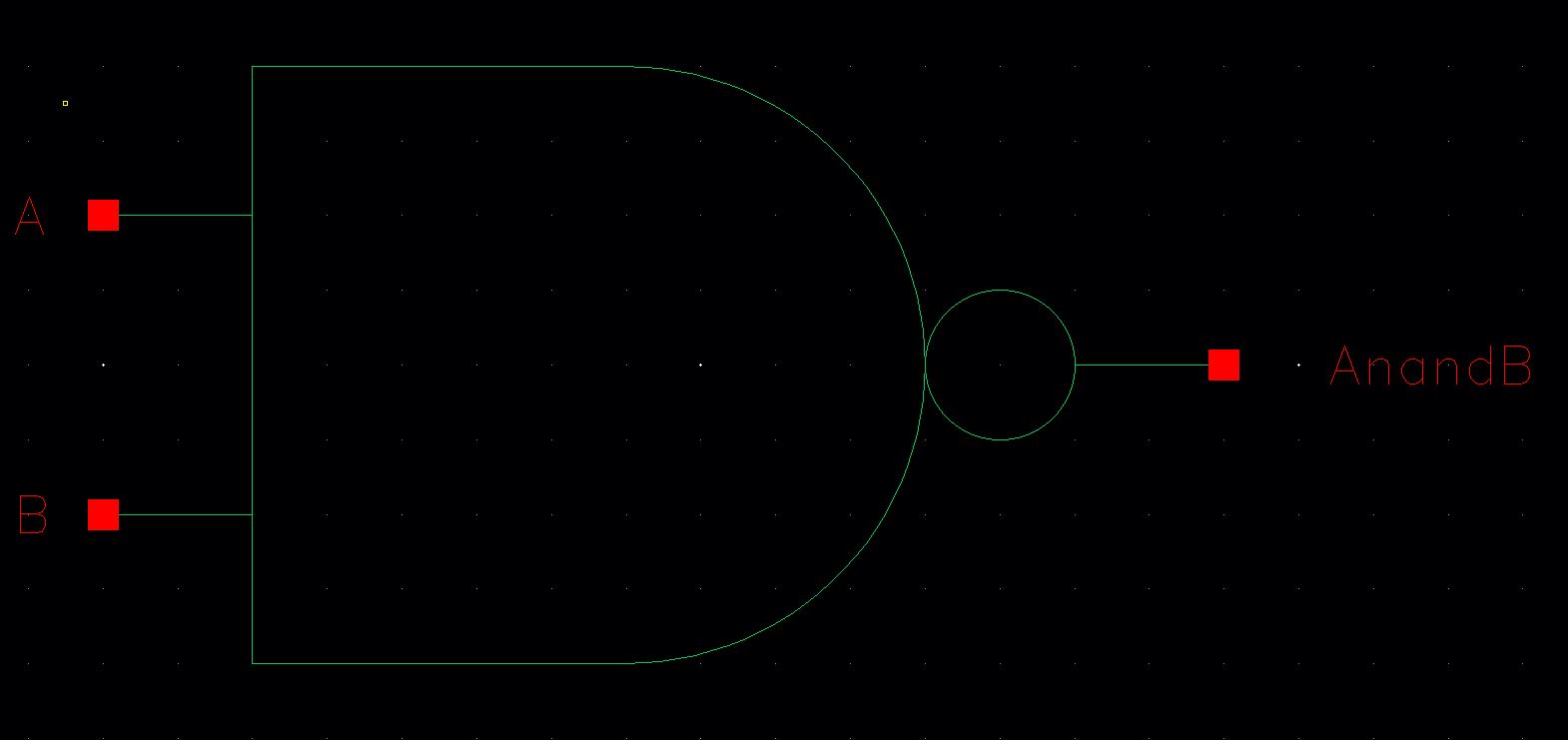

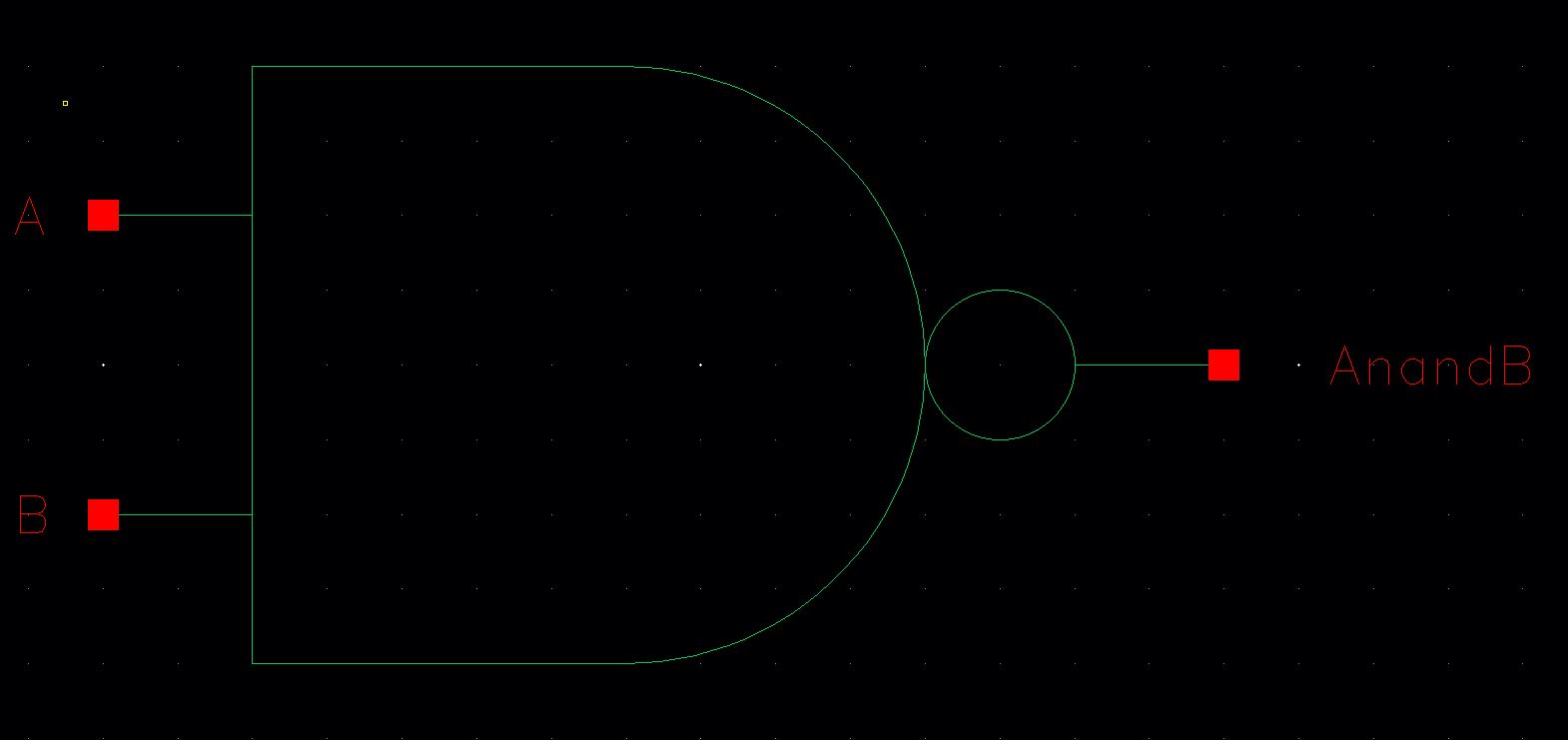

Nand Symbol View

Lab 06 - EE 421L

Nand Schematic View |  Nand Symbol View |

Nand Simulation Schematic |  Nand Simulation Results |

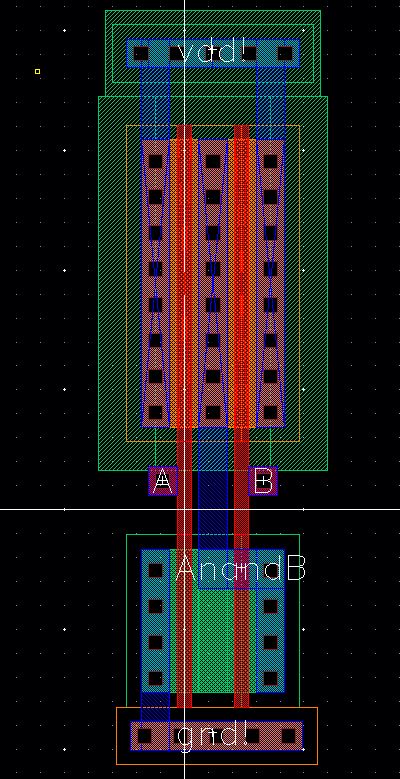

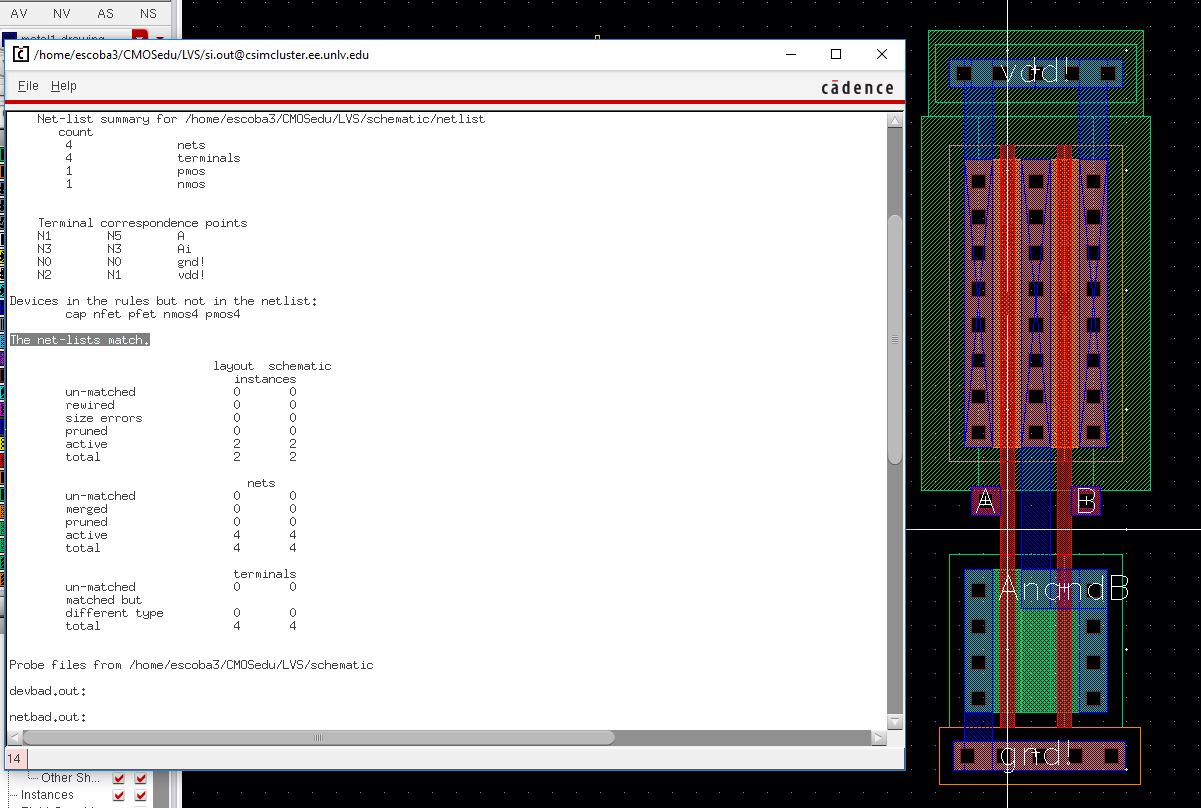

Layout view of Nand gate |  LVS layout - net lists match! |

XOR Schematic View |  XOR Symbol View |

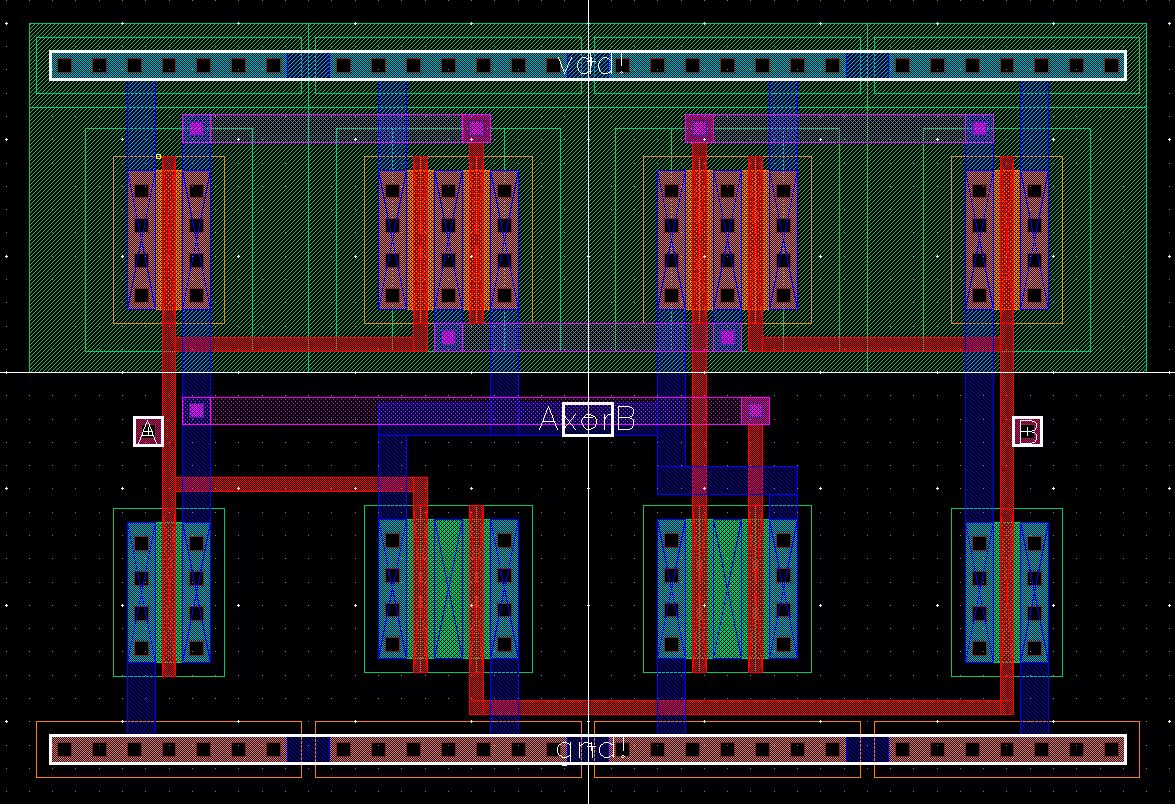

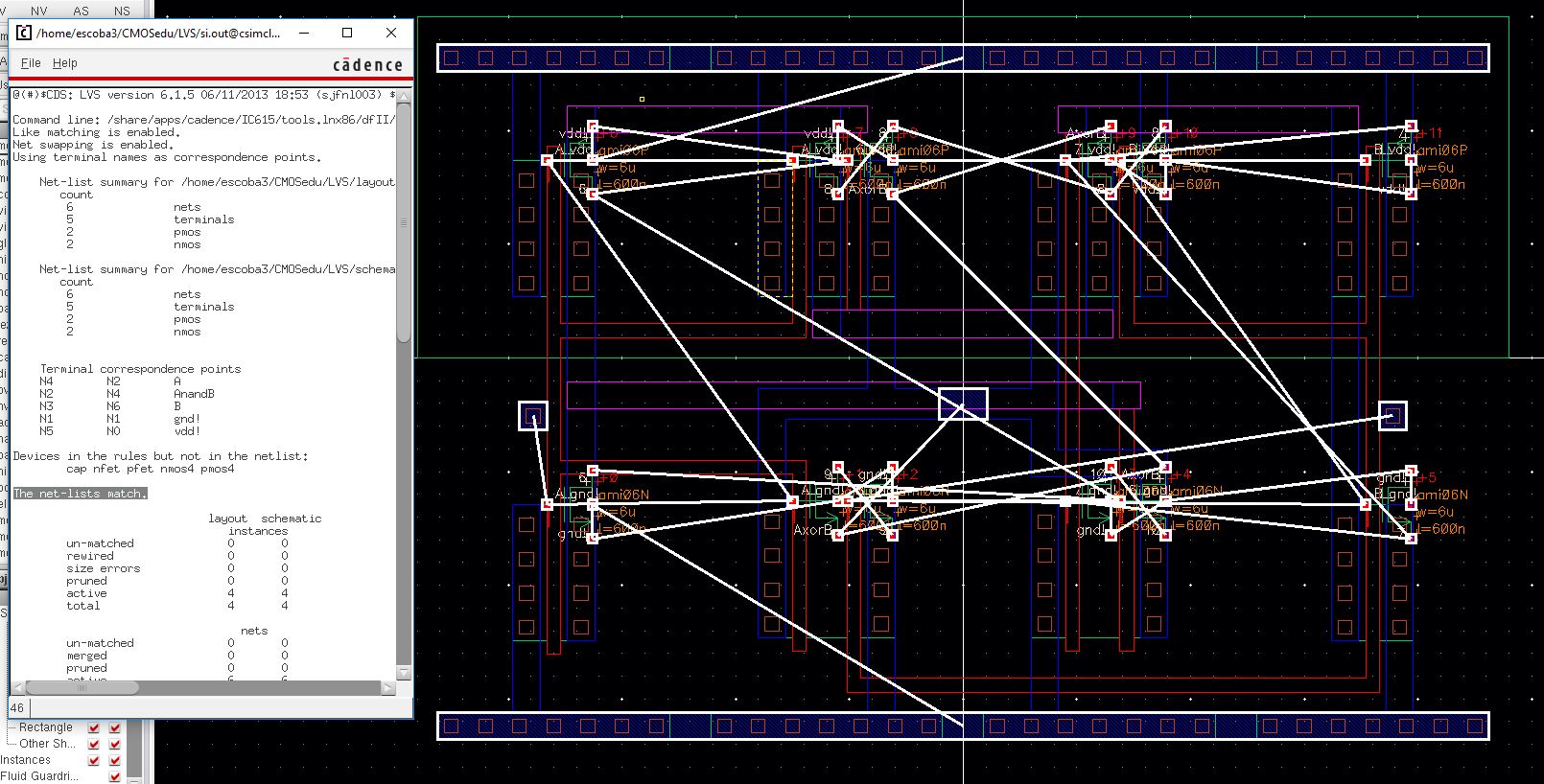

Layout of XOR Logic gate using standard cell frames |  A passed LVS |

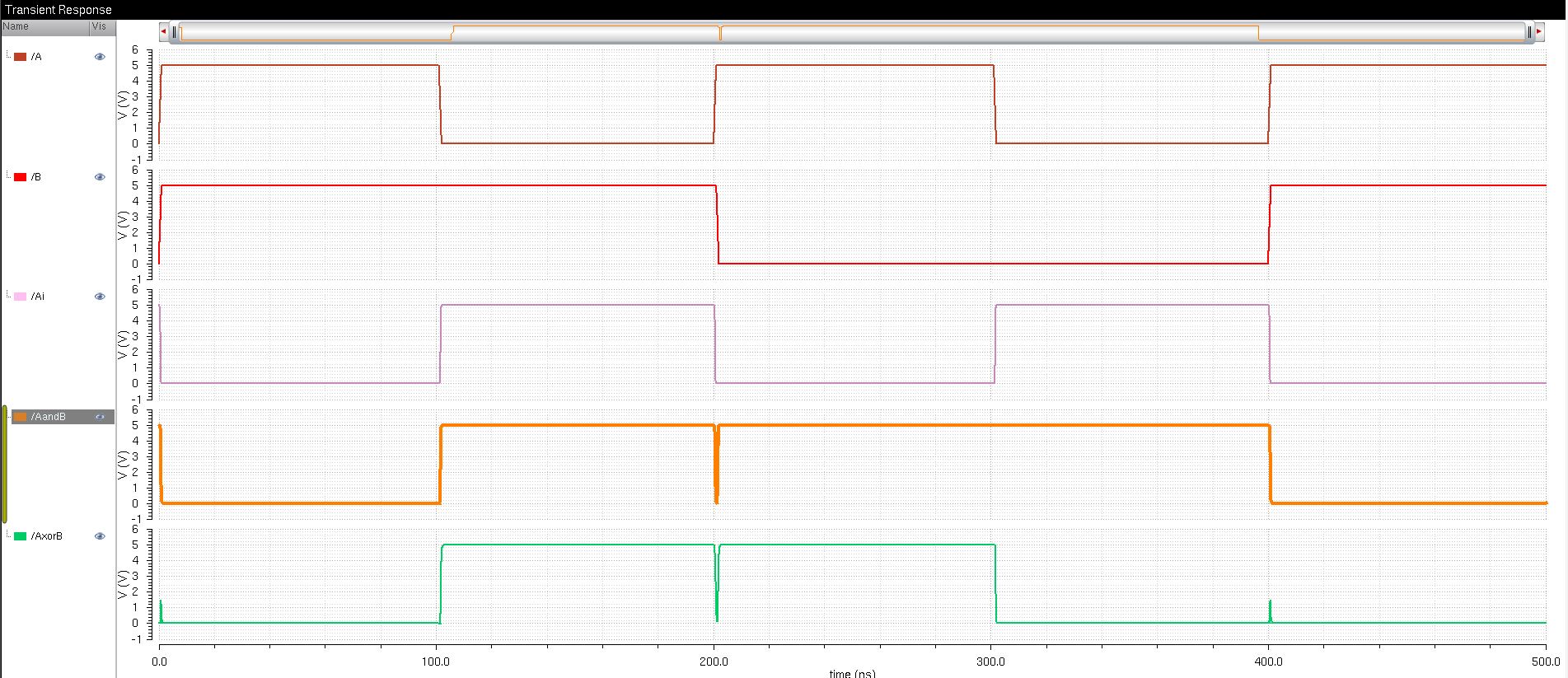

Inverter, Nand, Xor Simulation Schematic |  Simulation Results from Nand, Xor, and Inverter Schematic |

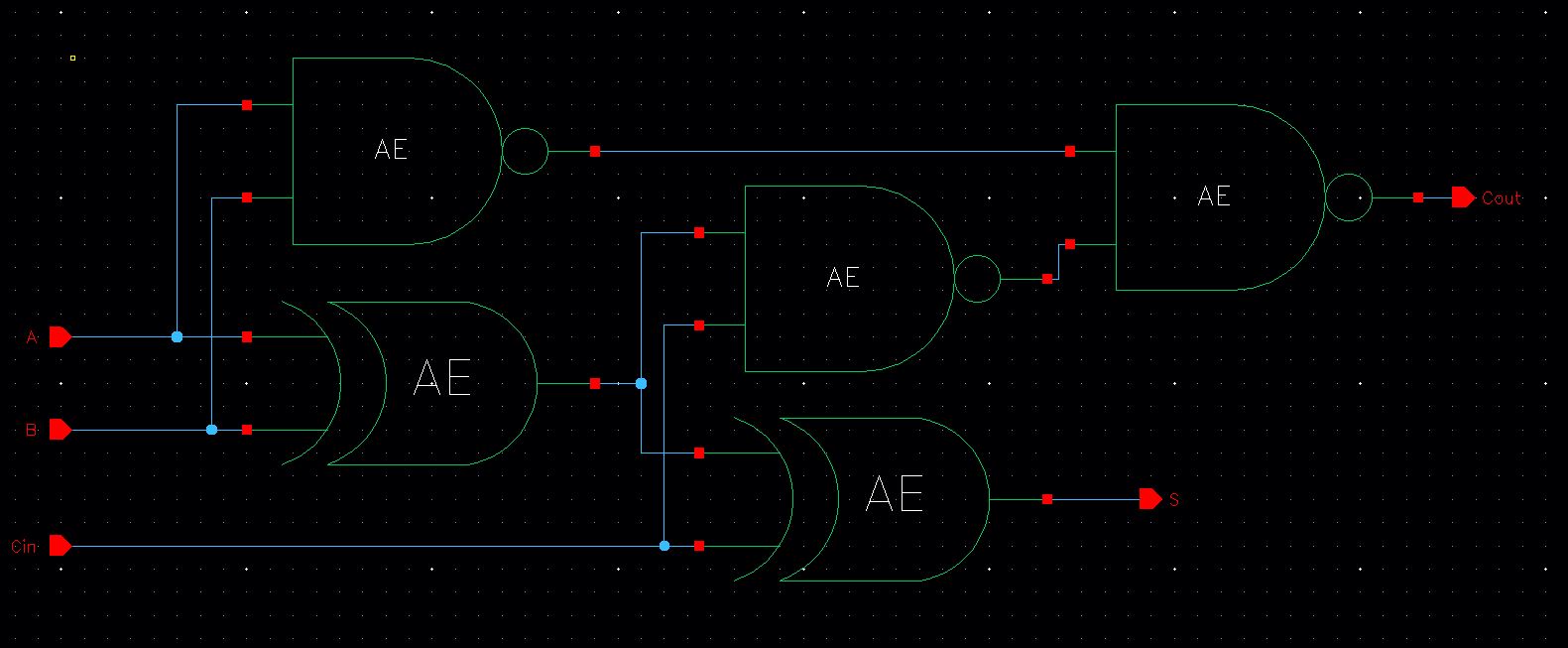

| A | B | Cin | S | Cout | |

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 |

Full adder Schematic |  Full adder symbol |