Lab 5 - ECE 421L

Authored

by Preston Donovan,

donovp1@unlv.nevada.edu

September 11, 2017

Prelab:

Back up work

Do Tutorial 3

Postlab:

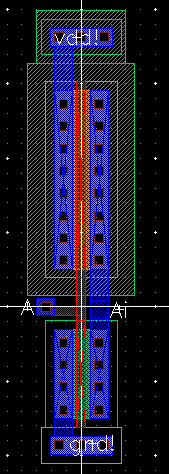

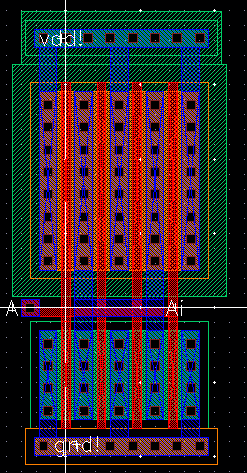

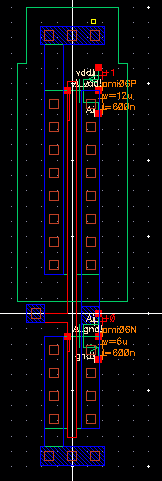

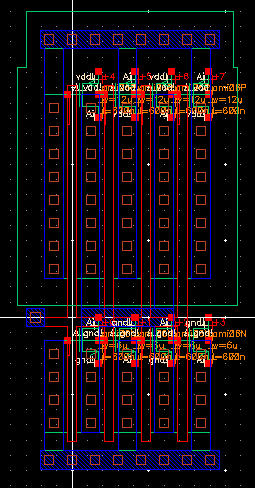

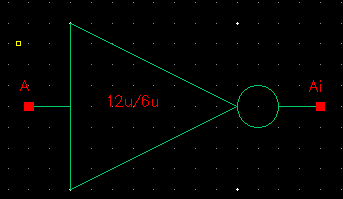

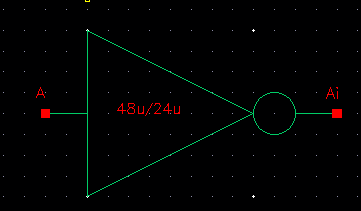

I made a 12u/6u and a 48u/24u inverter and created a chematic, layout, and symbol for each.

Here is the layouts

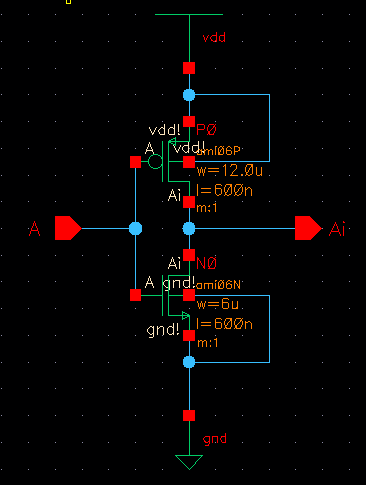

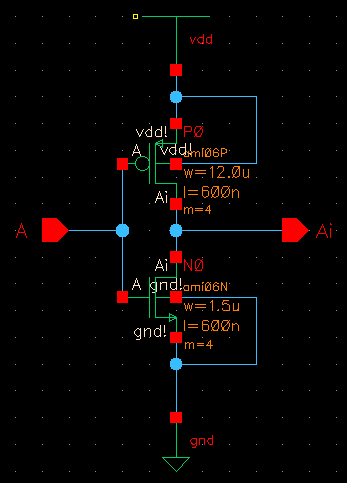

Here are Extracted views of these layouts

Here are schematics

Here are symbols

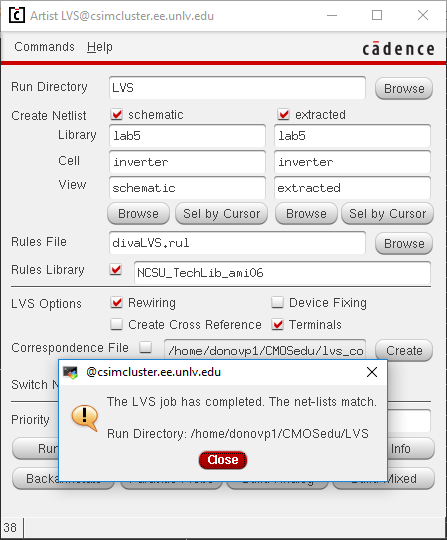

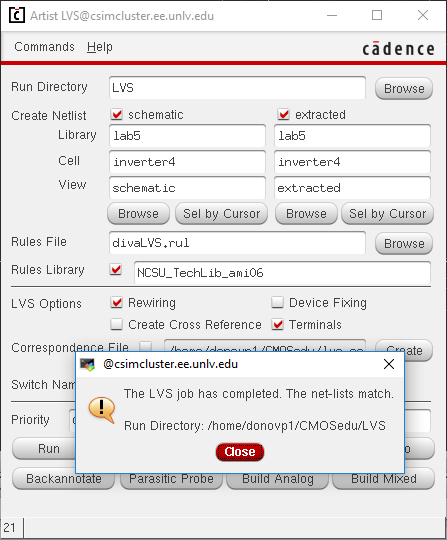

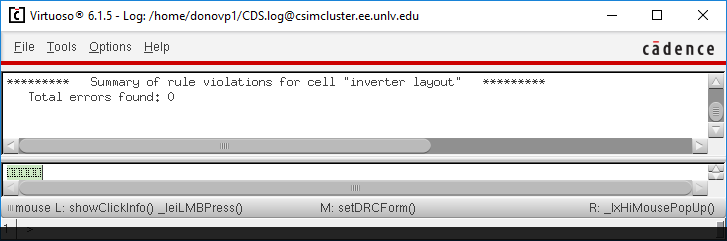

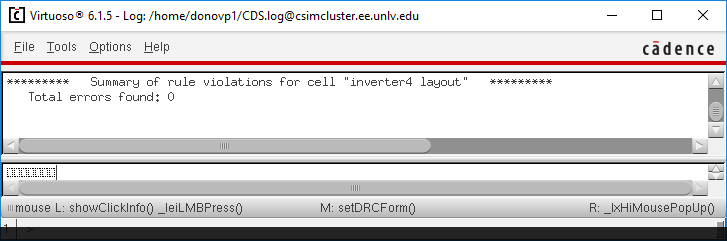

I then LVSd and DRCd both inverters

They both pass.

After creating these I ran simulations driving a 100fF, 1pF, 10pF, 100pF

Starting with the 12u/6u:

Adding

on capacitence reduced the fall time of the output. At 100pf the fall

time is so large it doesnt even loose half of the starting voltage,

that is becasue larger capacitors take longer to discharge.

And 48u/24u:

These outputs are very comparable to the 12u/6u inverter but the fall time seems to be increased even more.

Lab 5 zip including my Layouts and schematic files can found here

Return to EE 421L Labs