Lab 6 - ECE 421L

To prepare for the layout portion of the lab, first I laid out a standard cell frame.

This provides us with a predefined area to lay out our PMOS and NMOS device

as well as VDD and ground rails lining the top and bottom of the frame respectively.

If we need more space we can quickly paste copies of the frame horizontally.

For this lab we also configure vpulse sources to act as our digital inputs when we test the components.

It is important the Rise and Fall times are << Pulse width or we will see unexpected behavior when the inputs switch.

NAND gate layoutand Extracted view. A LVS was performed to be sure our layout and schematic matched.

Next I instantiated the NAND symbol made earlier and used pulse sources as discussed in the beginning of the lab to simulate and verify our design.

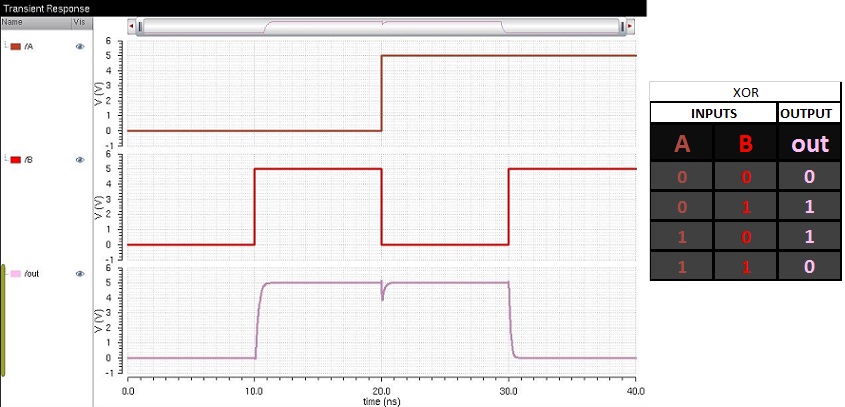

Next, I drafted the provided schematic for an XOR gate and made the corresponding symbol

The XOR gate layout was quite a bit more challenging than the NAND gate simply due to the increase in transisters required.

In the more crowded areas I used and metal2 to ease the difficulty of the layout.

Again our symbol was instantiated with pulse sources to run a simulation to confirm our gate is working as designed.

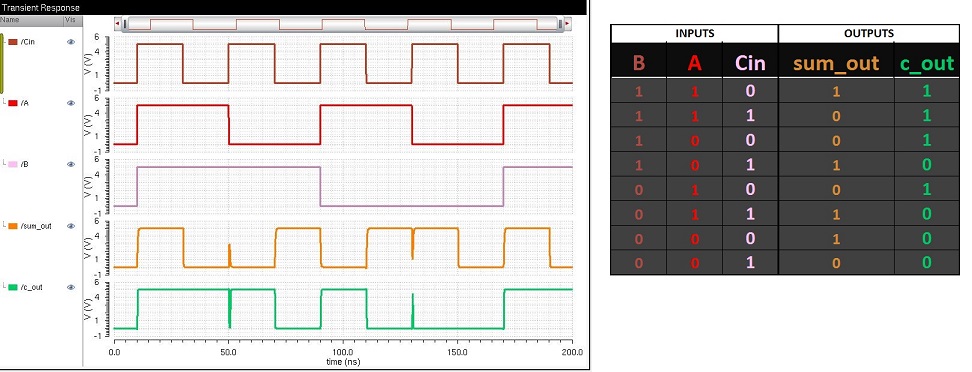

The last part of the lab required us to use the two gates created in the first two parts of the lab to implement a Full-adder.

For the layout of the full adder I used metal2 much more liberally to avoid having to route around

metal1 and poly. At this point I realized my standard cell frame probably should have been taller,

because anything larger than the full adder would almost certainly not fit in my frame.

Extracted view and LVS RESULTS

Click the link to download a zipped up copy of the library created for this lab report: ---> lab6.zip <-----

Return to other EE421L students labs