Lab 5 - EE 421L

Authored by Surafel Abera

Abera@unlv.nevada.edu

October 11, 2017

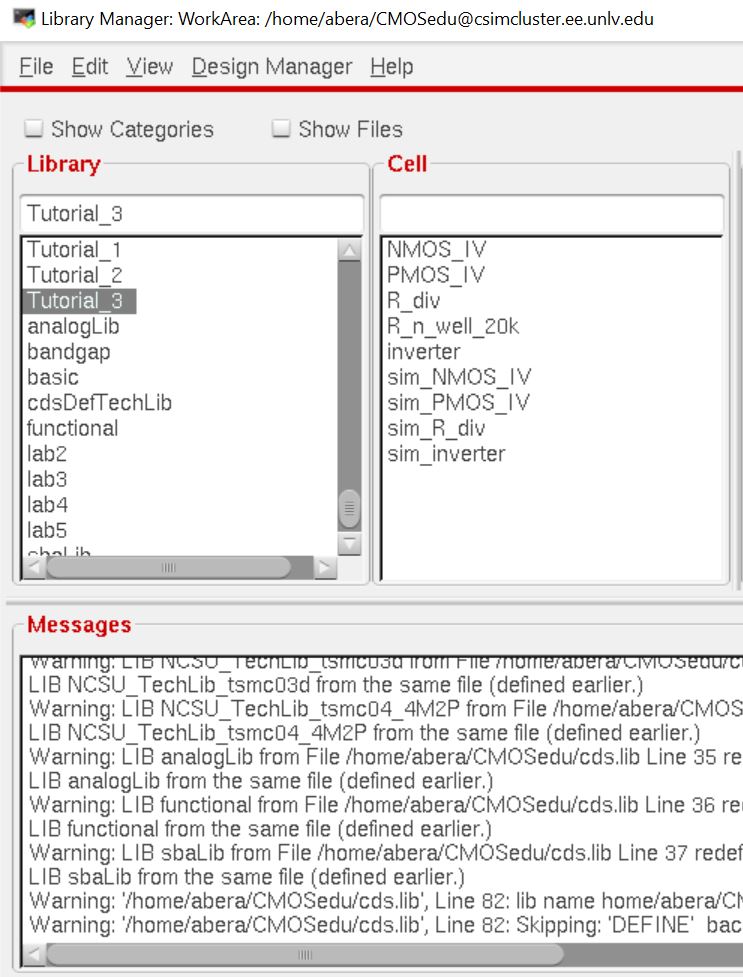

Pre-lab work:

| Lab

work Back-up | Tutorial 3 completed |

|  |

Lab work:

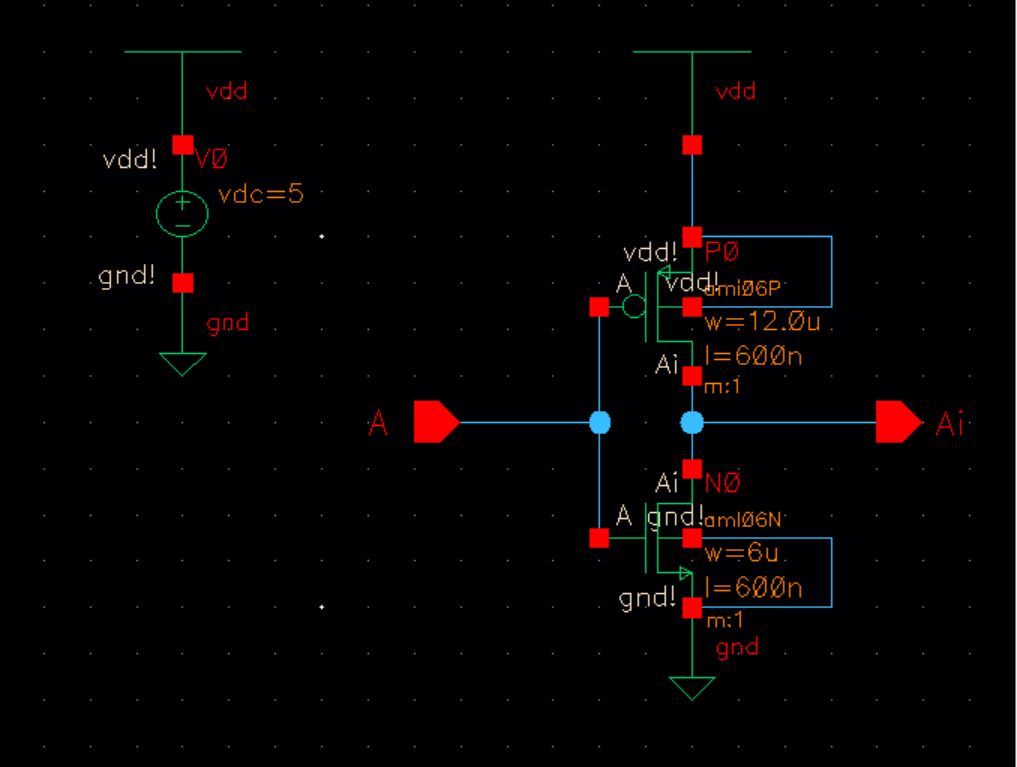

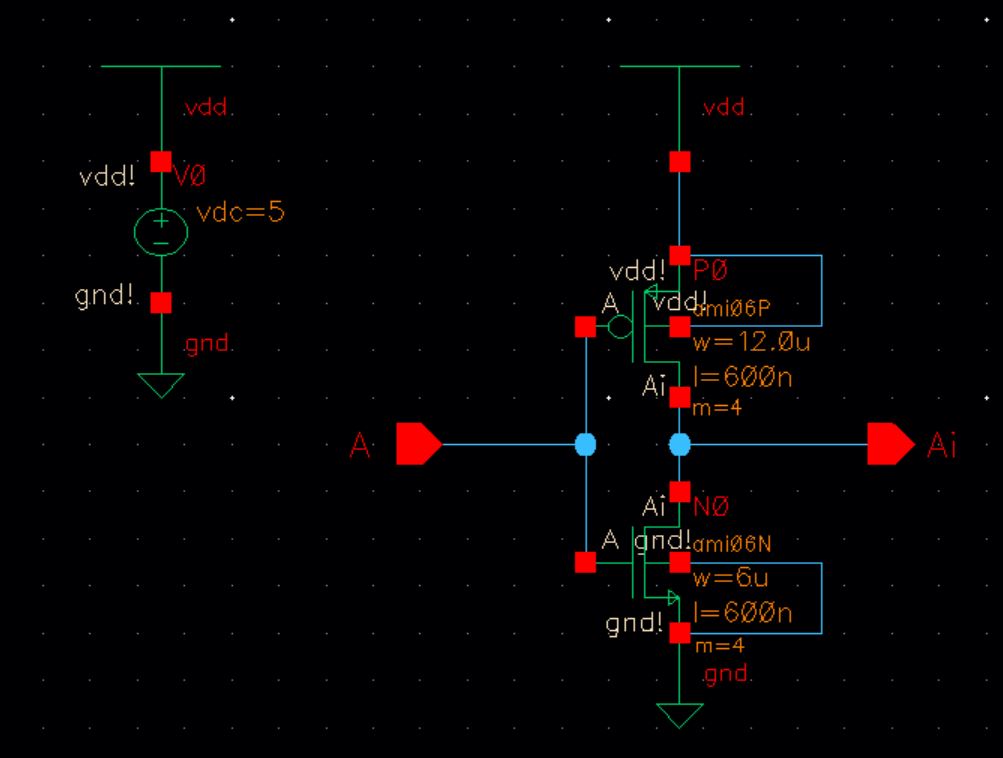

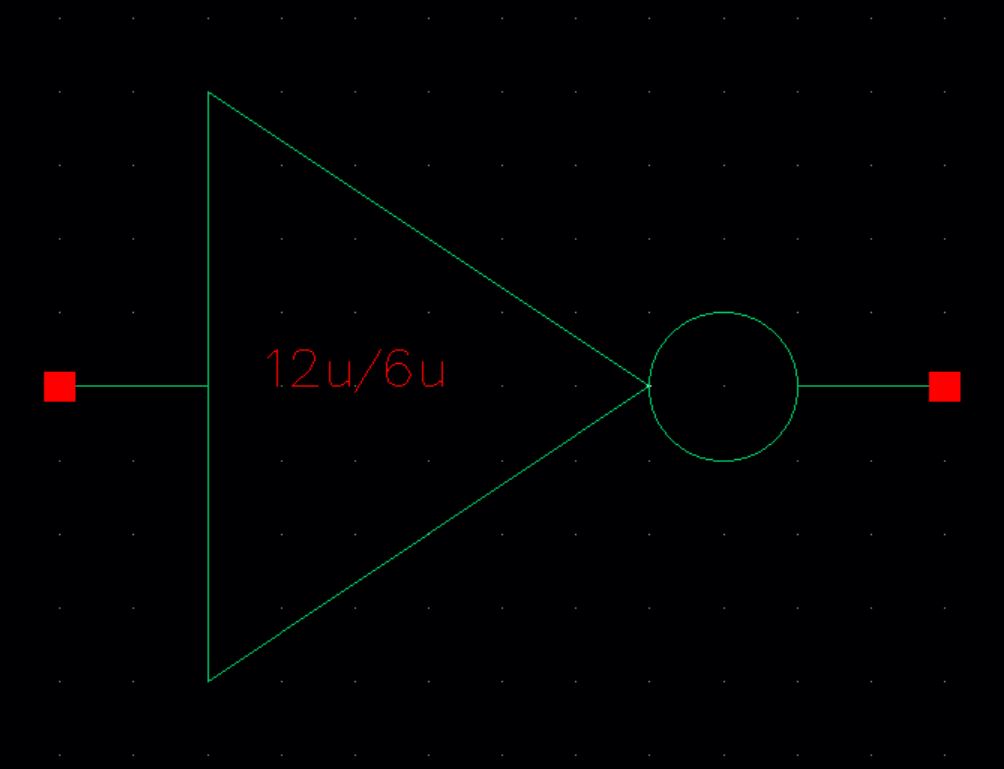

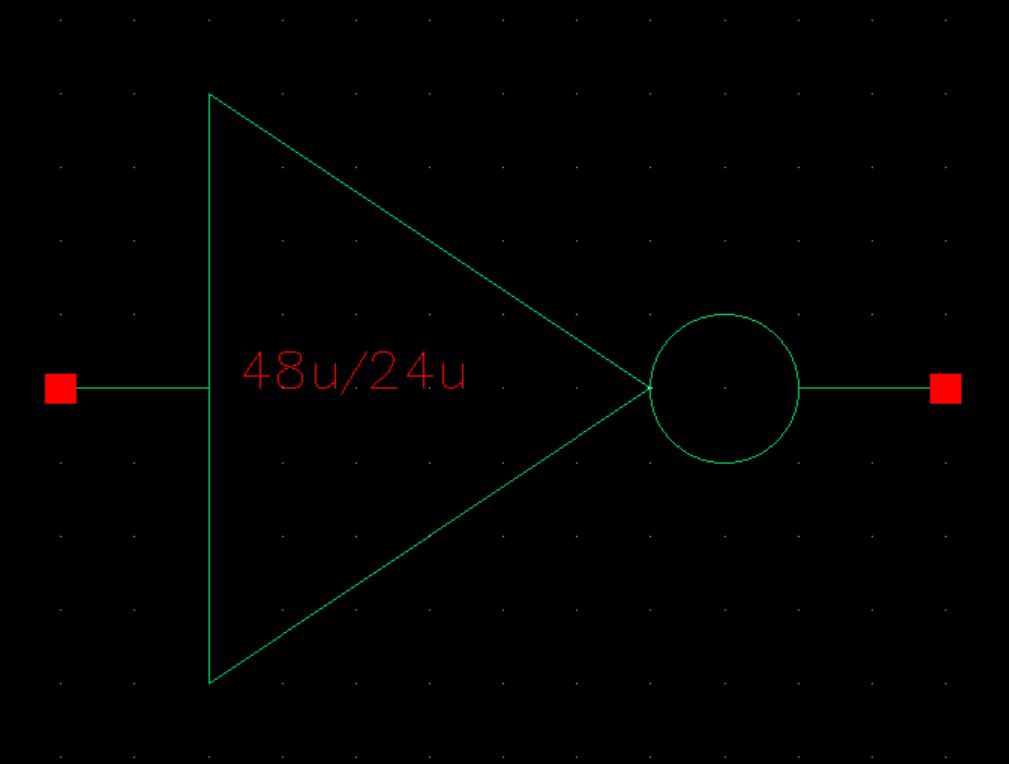

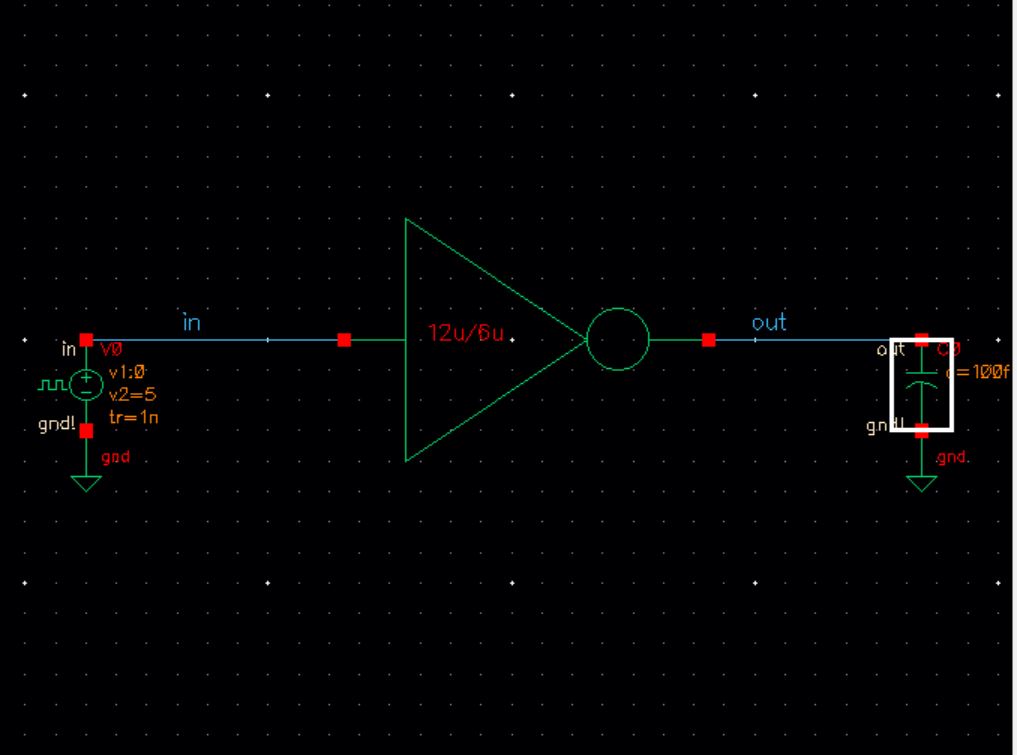

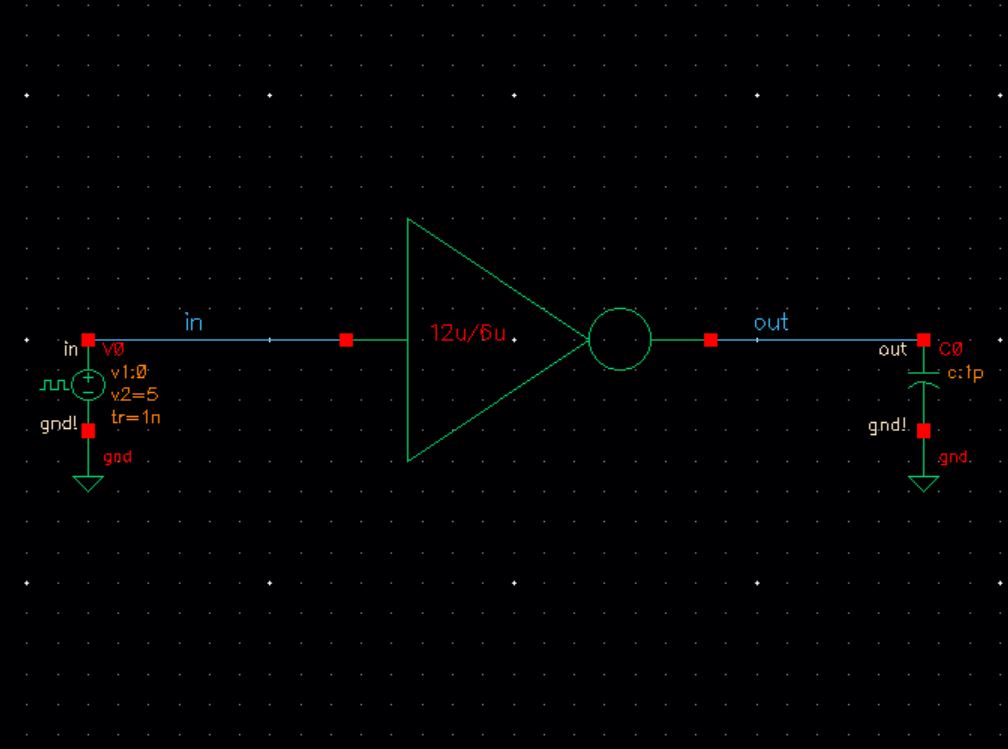

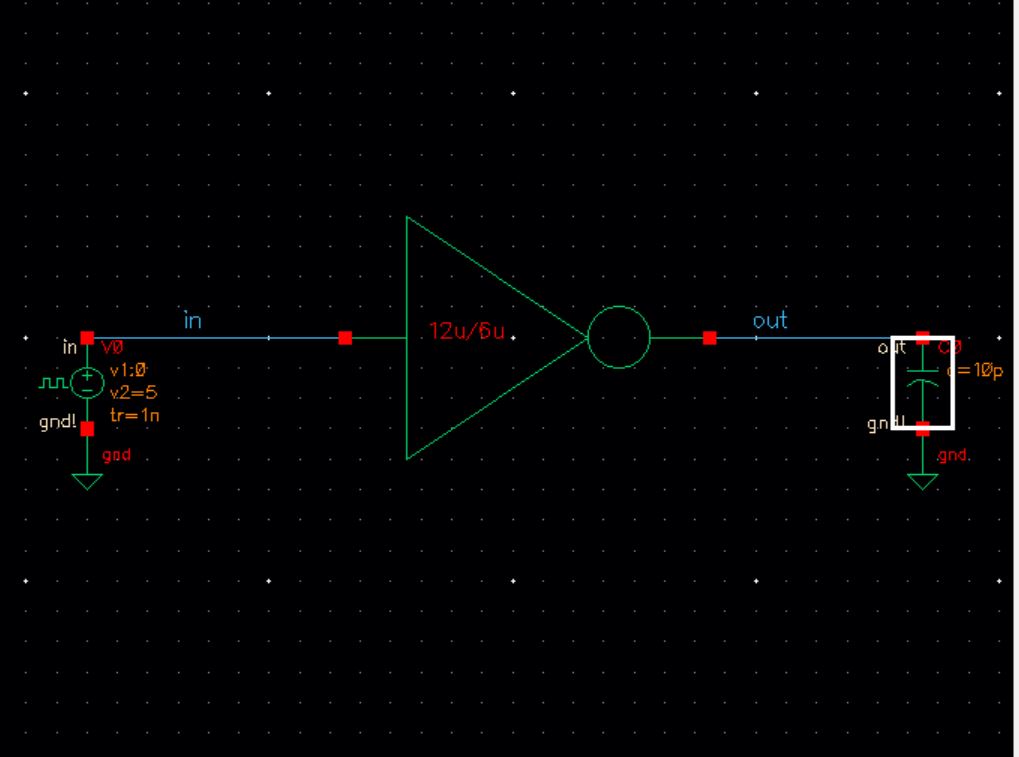

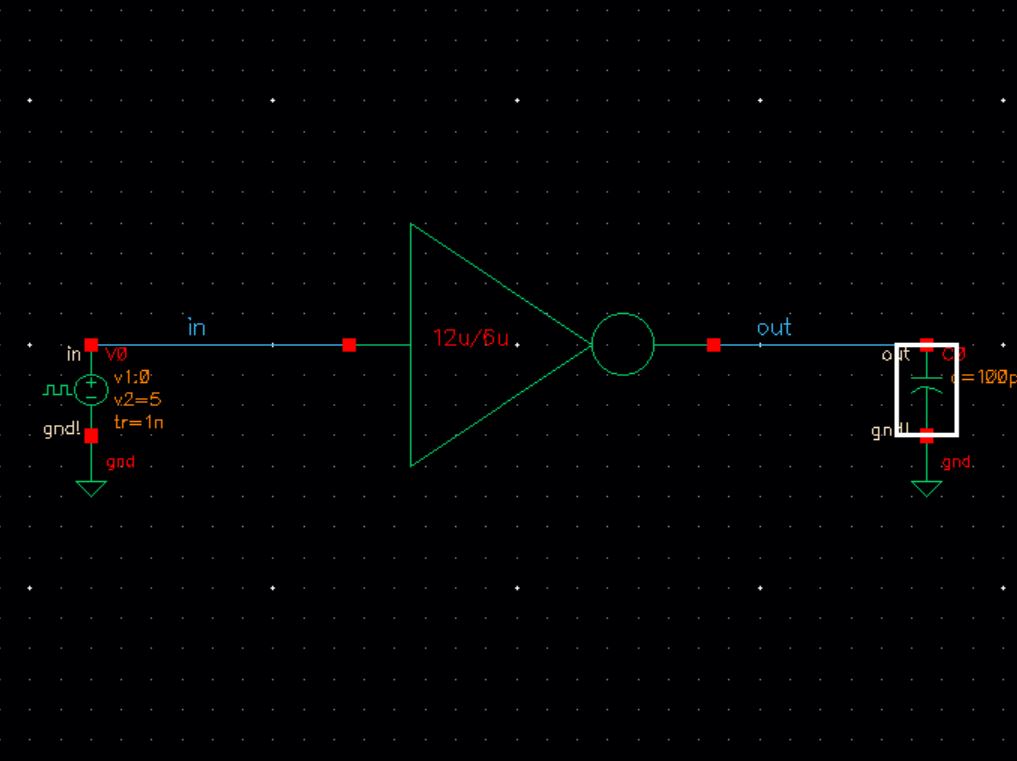

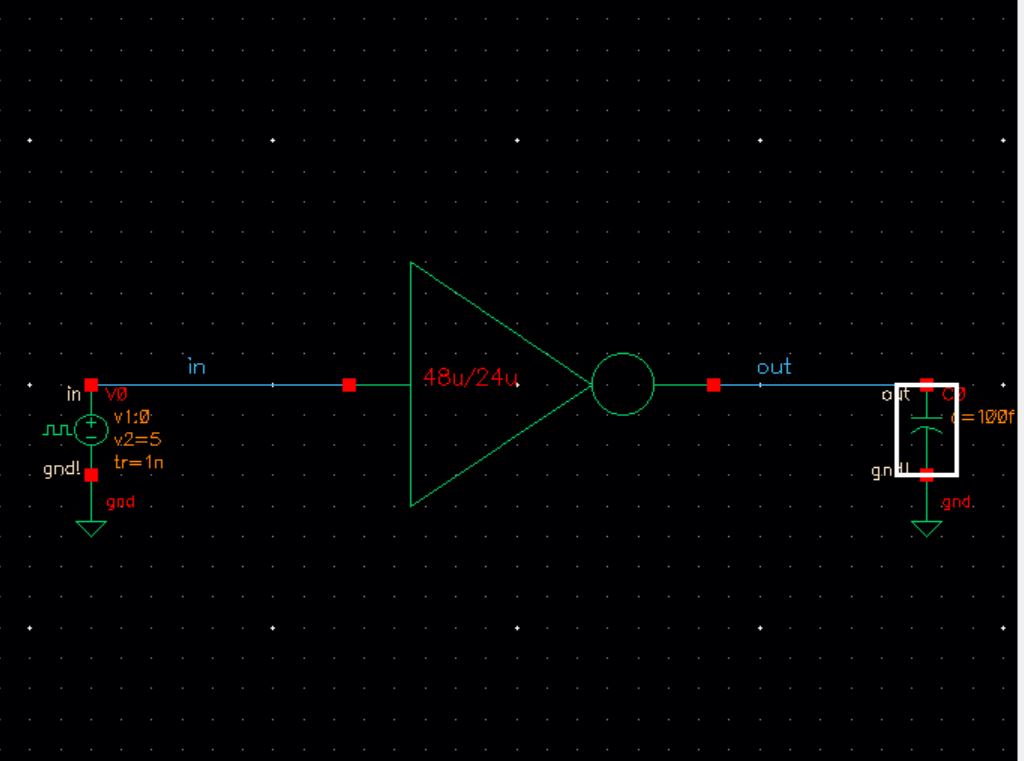

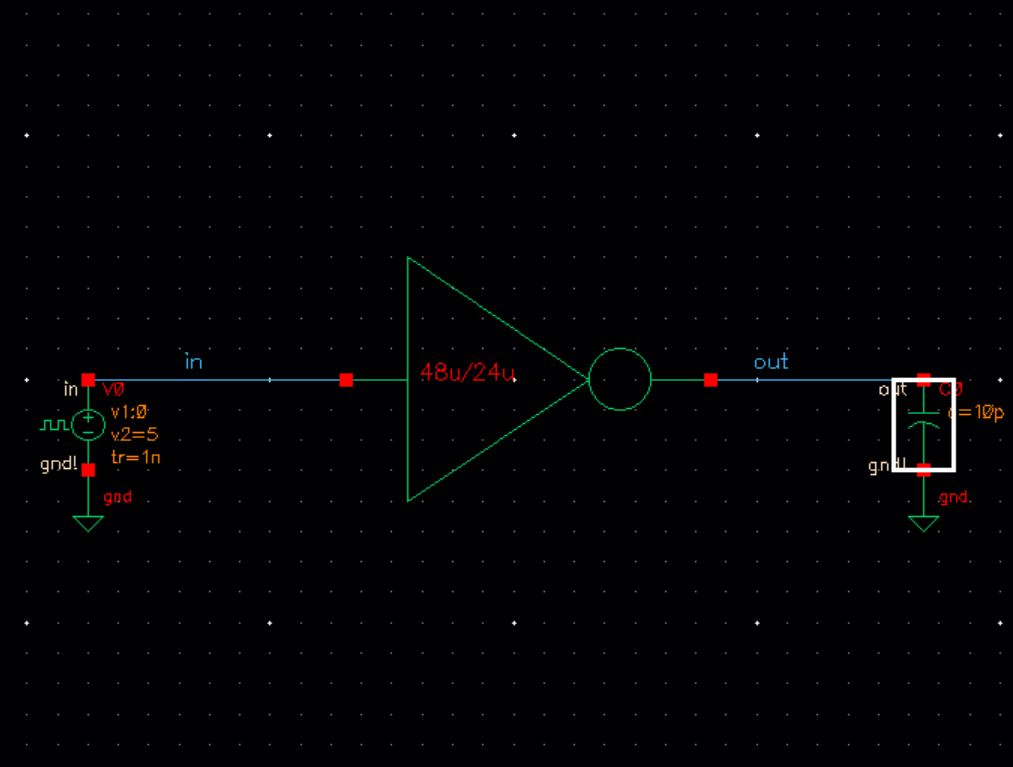

Inverter Schematics

| 12u/6u inverter | 48u/24u inverter |

|

|

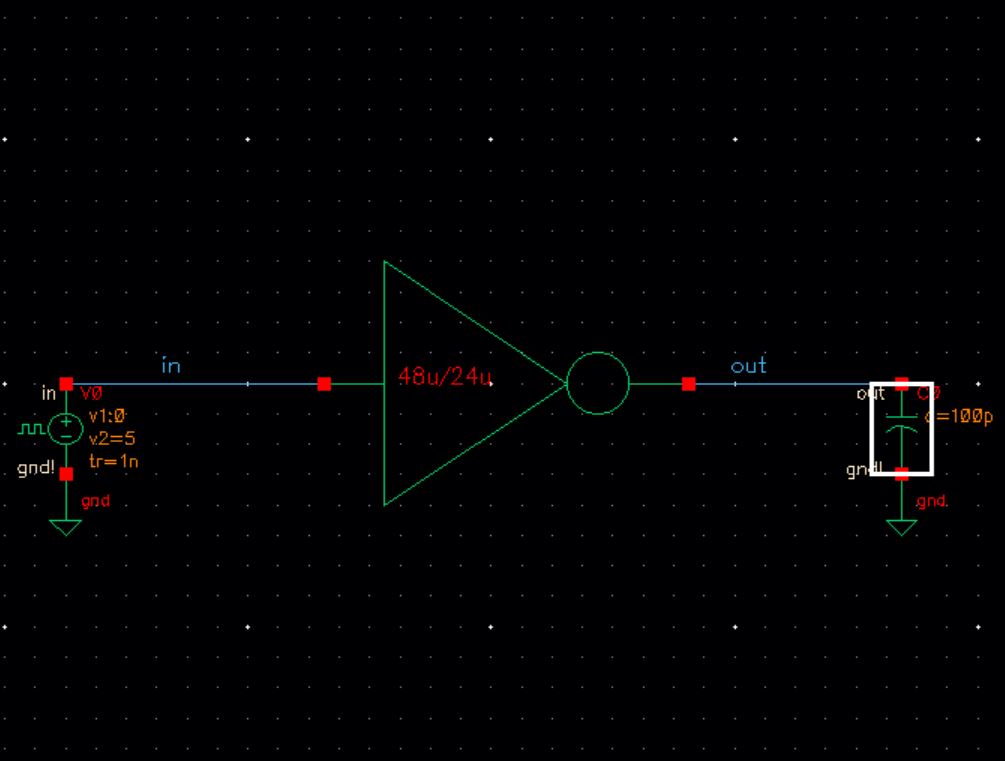

The

schematic on the right is four inverters in parallel [4* (12u/6u) =

(48u/6u)]. Each inverter NMOS W=6u L=0.6u , PMOS W=12u, L=0.6u.

The 48u/24u inverter performs 4 times better than the 12u/6u inverter.

| 12u/6u Symbol | 48u/24u Symbol |

|

|

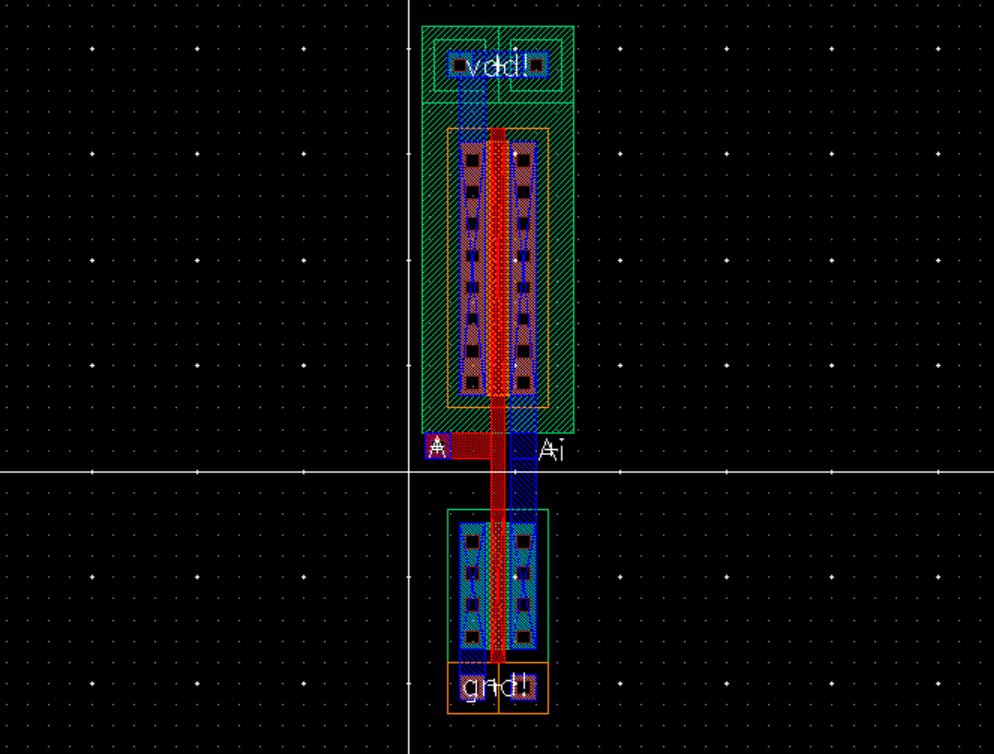

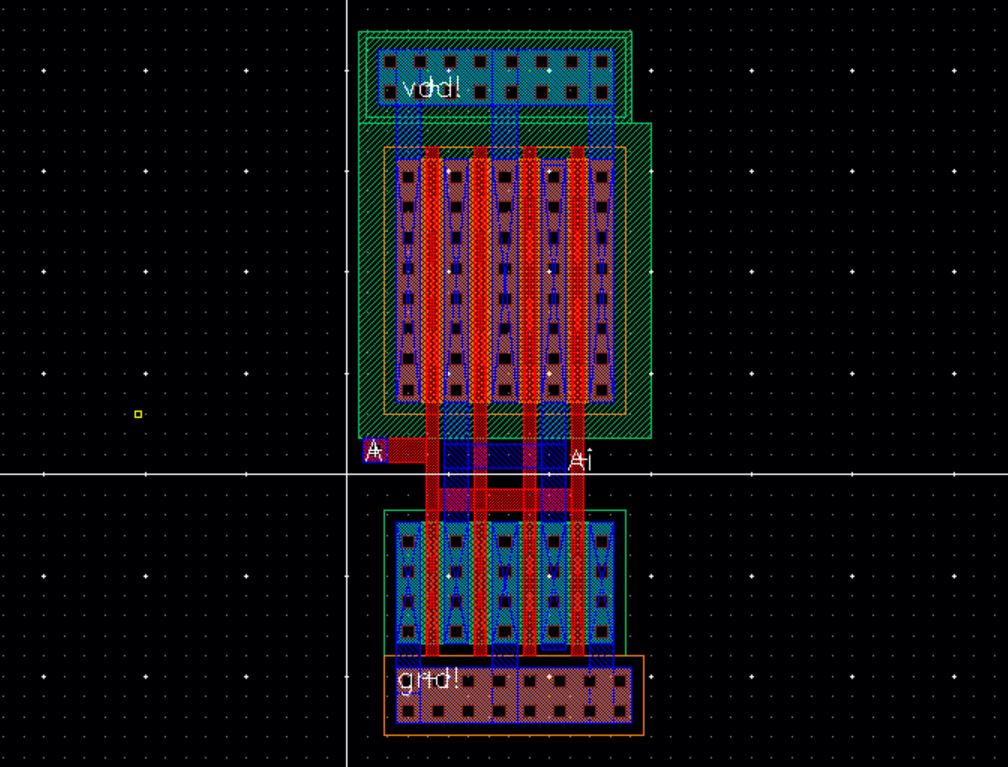

| 12u/6u Layout | 48u/24u Layout |

|

|

In the layout the inverter terminals are handled differently than the schematics.

The body of the Pmos is connected to global vdd! through ntap.

The body of the Nmos is connected to ground (gnd!).

The layout of 48u/12u has 4 gates, sources, and drains that are connected together.

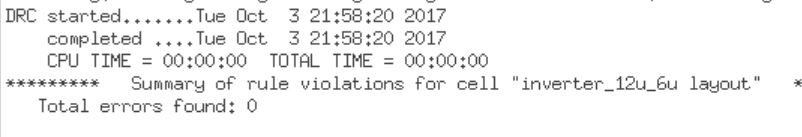

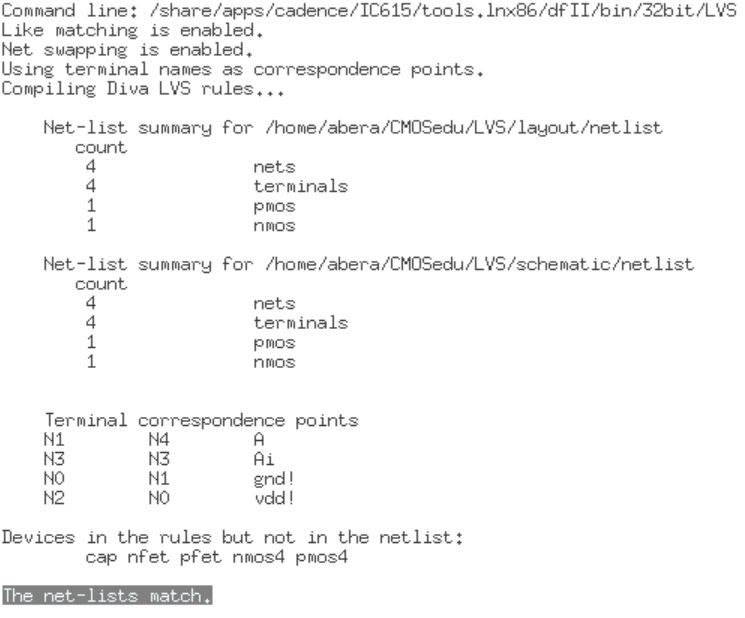

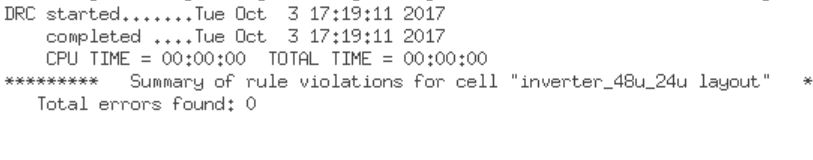

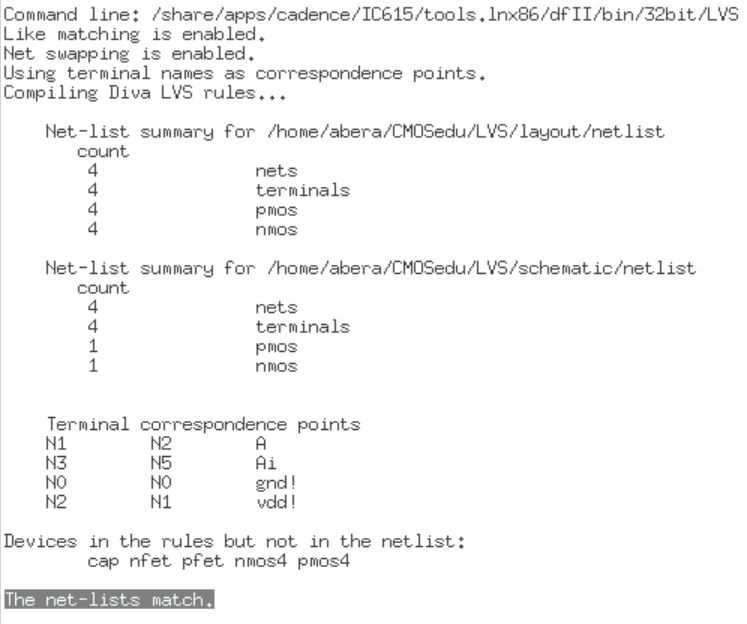

| 12u/6u DRC and LVS | 48u/24u DRC and LVS |

|

|

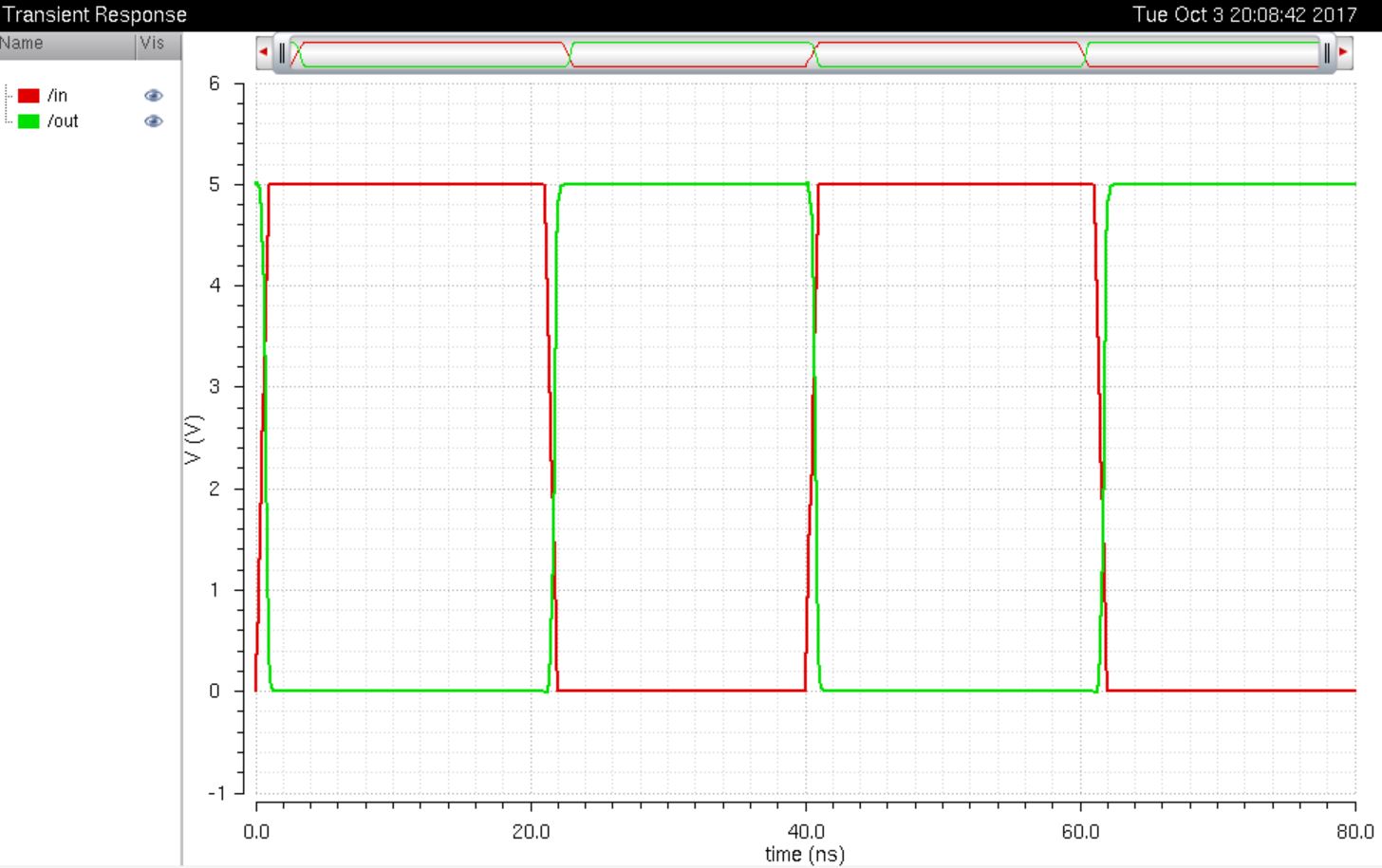

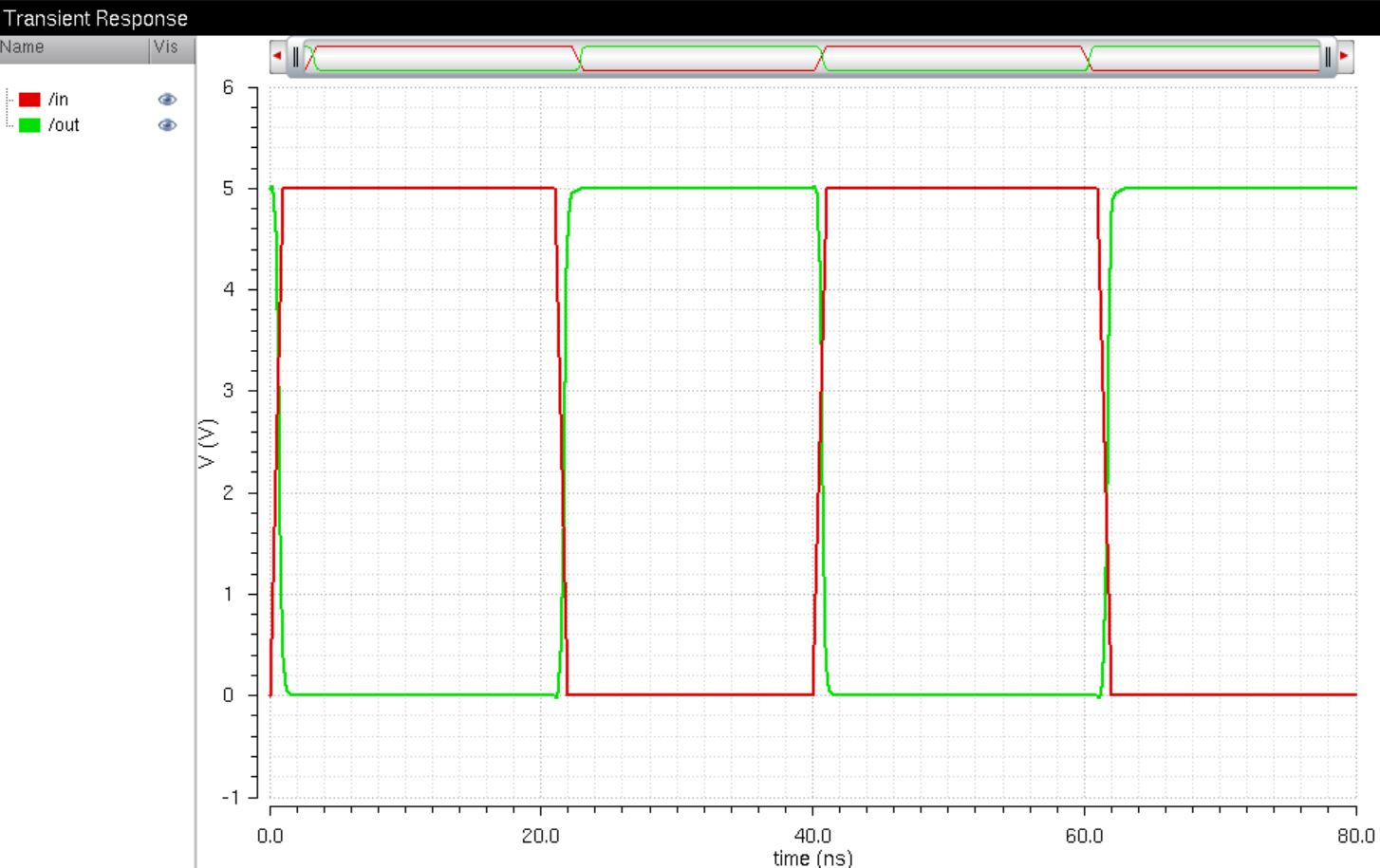

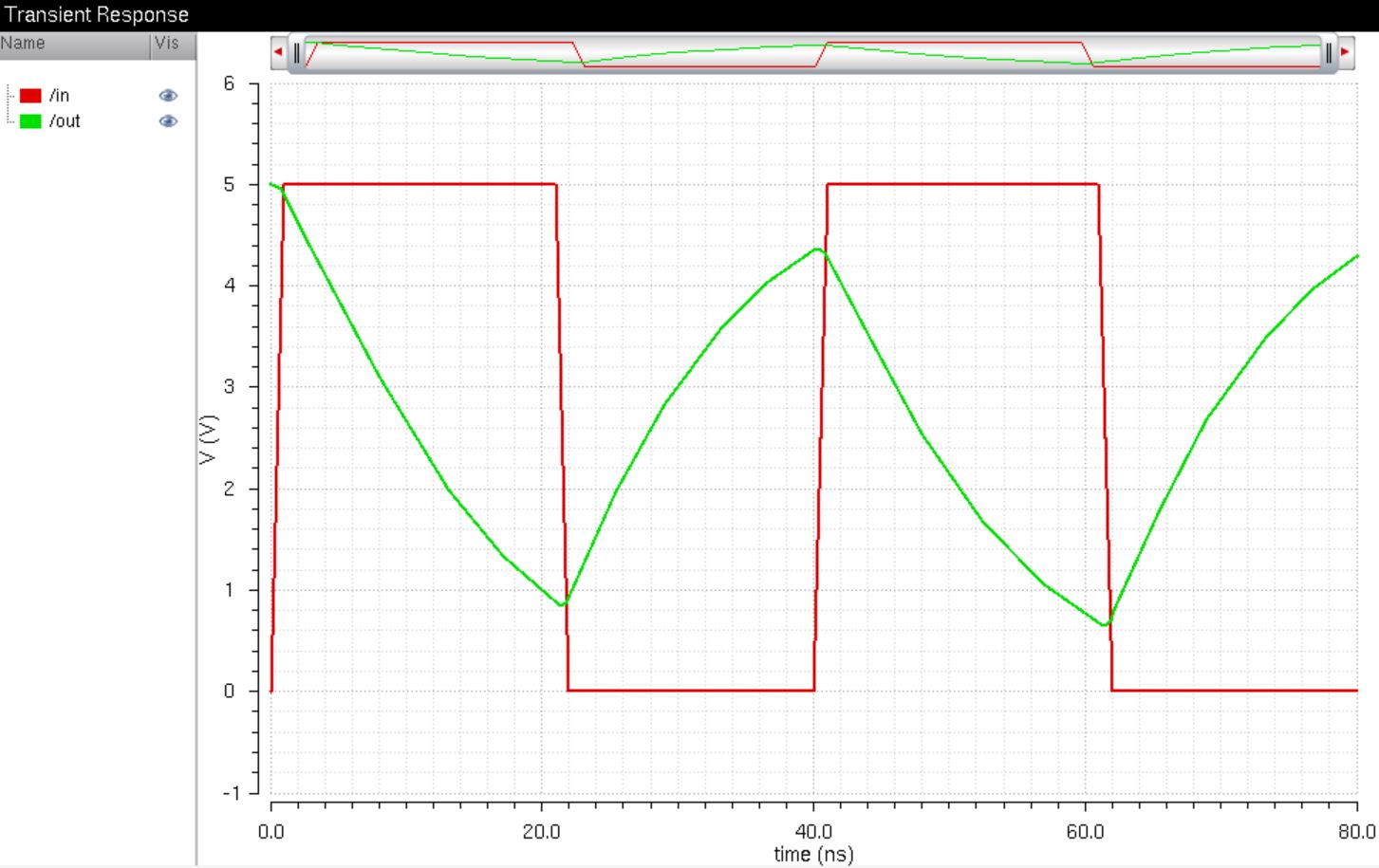

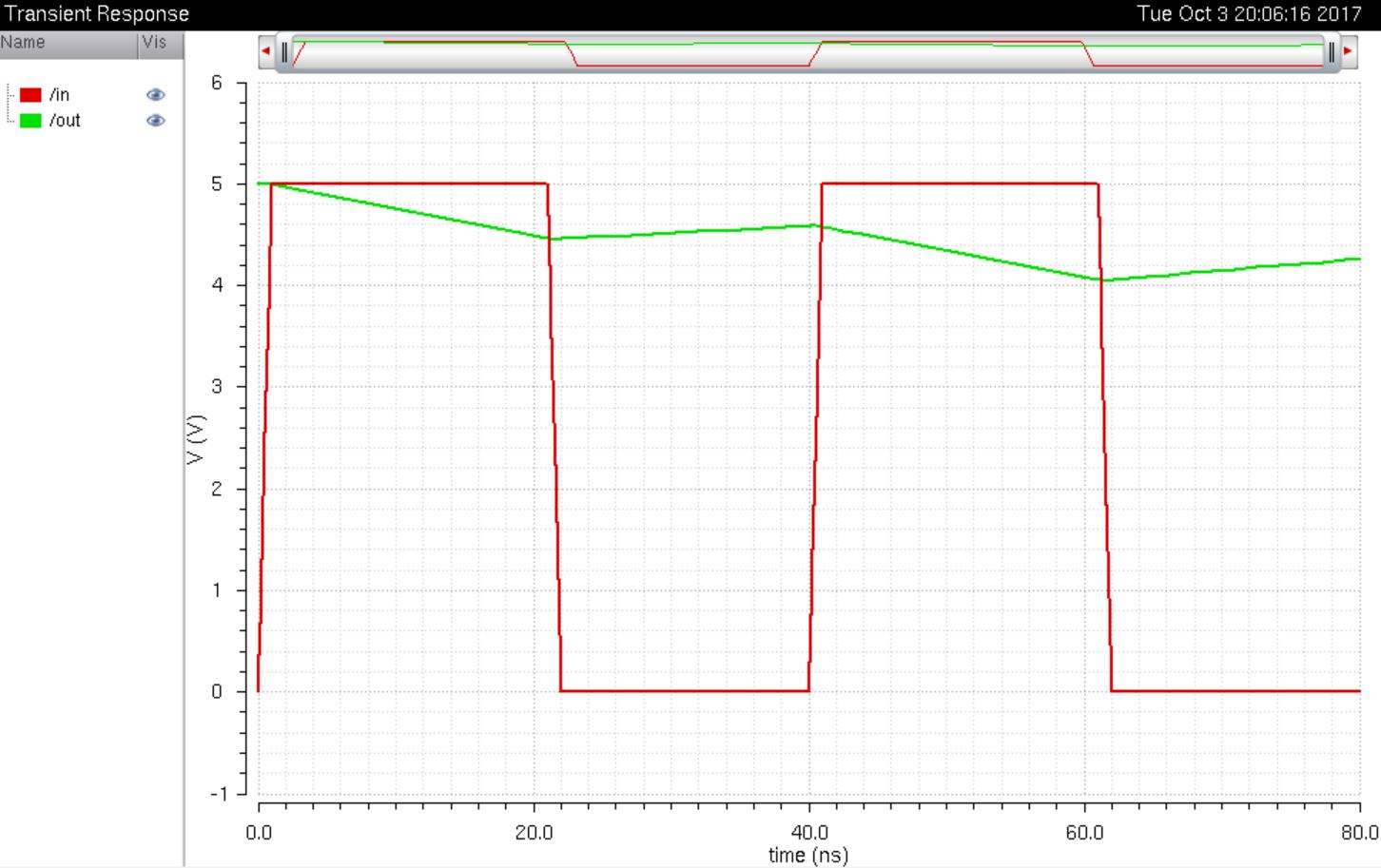

Specter and UltraSim Simulation of 12u/6u inverter

| 12u/6u inverter driving 100fF capacitor | Simulated using Specter | Simulated using UltraSim |

|

|  |

| 12u/6u inverter driving 1pF capacitor | Simulated using Specter | Simulated using UltraSim |

|  |  |

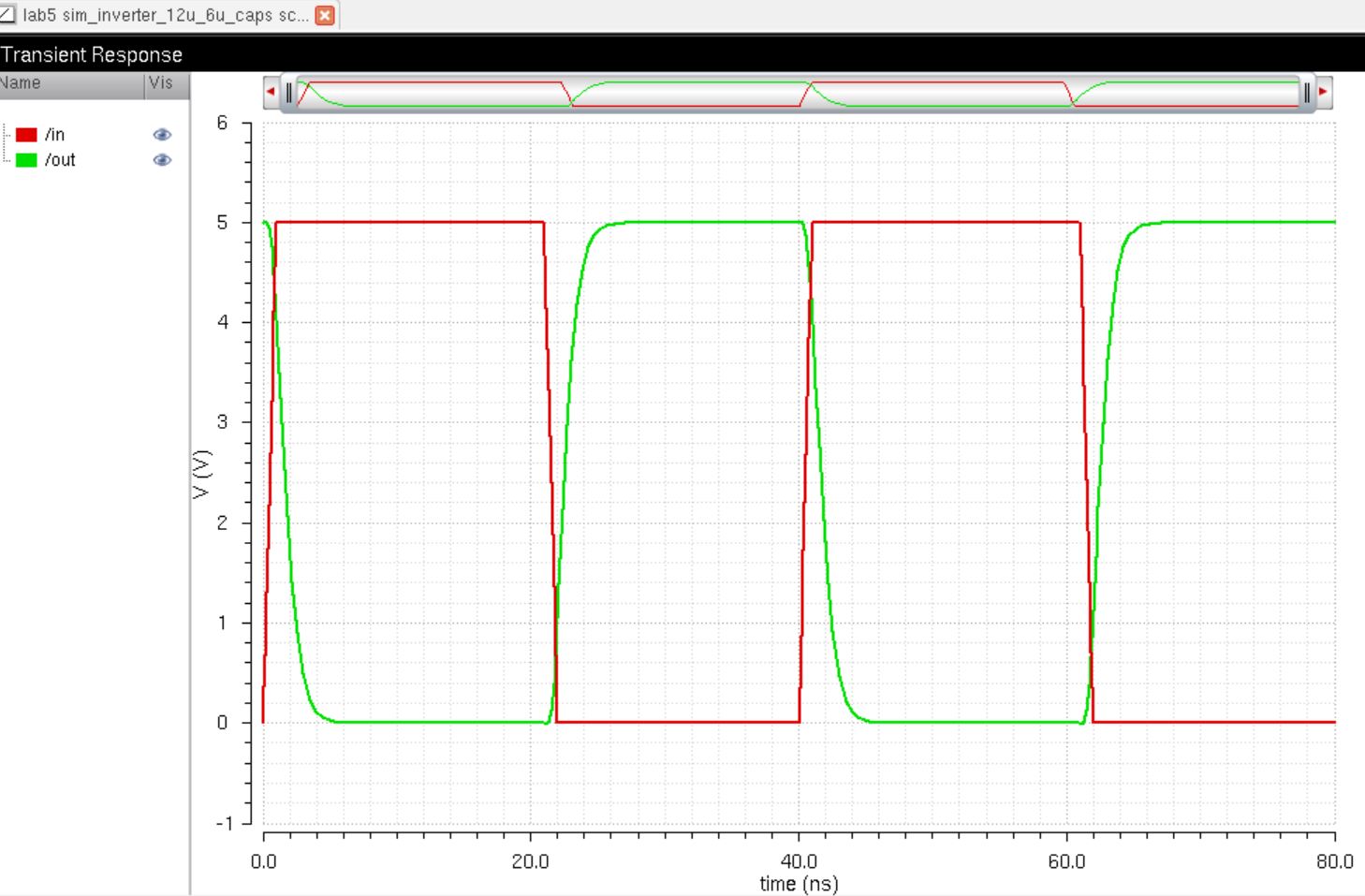

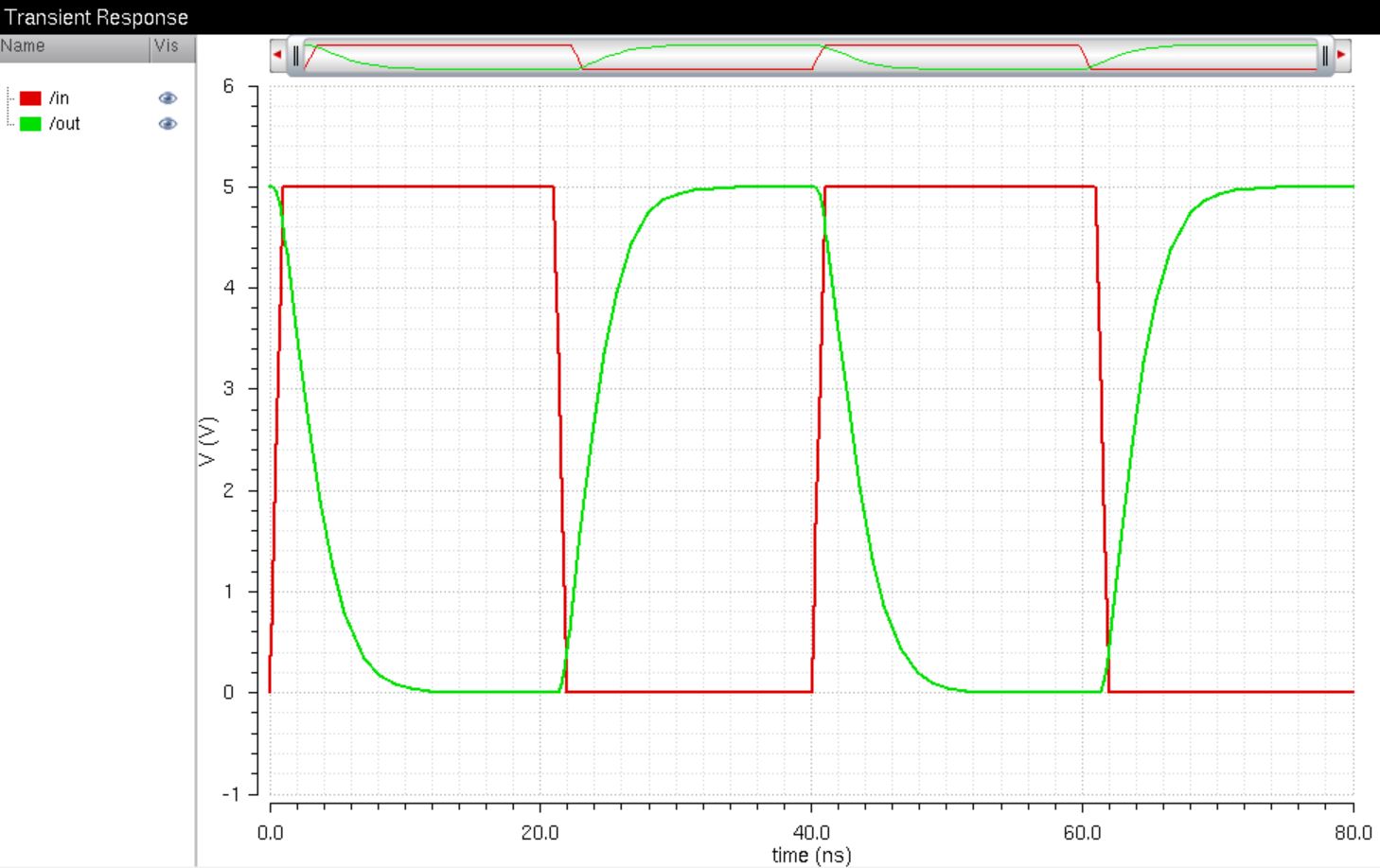

| 12u/6u inverter driving 10pF capacitor | Simulated using Specter | Simulated using UltraSim |

|  |  |

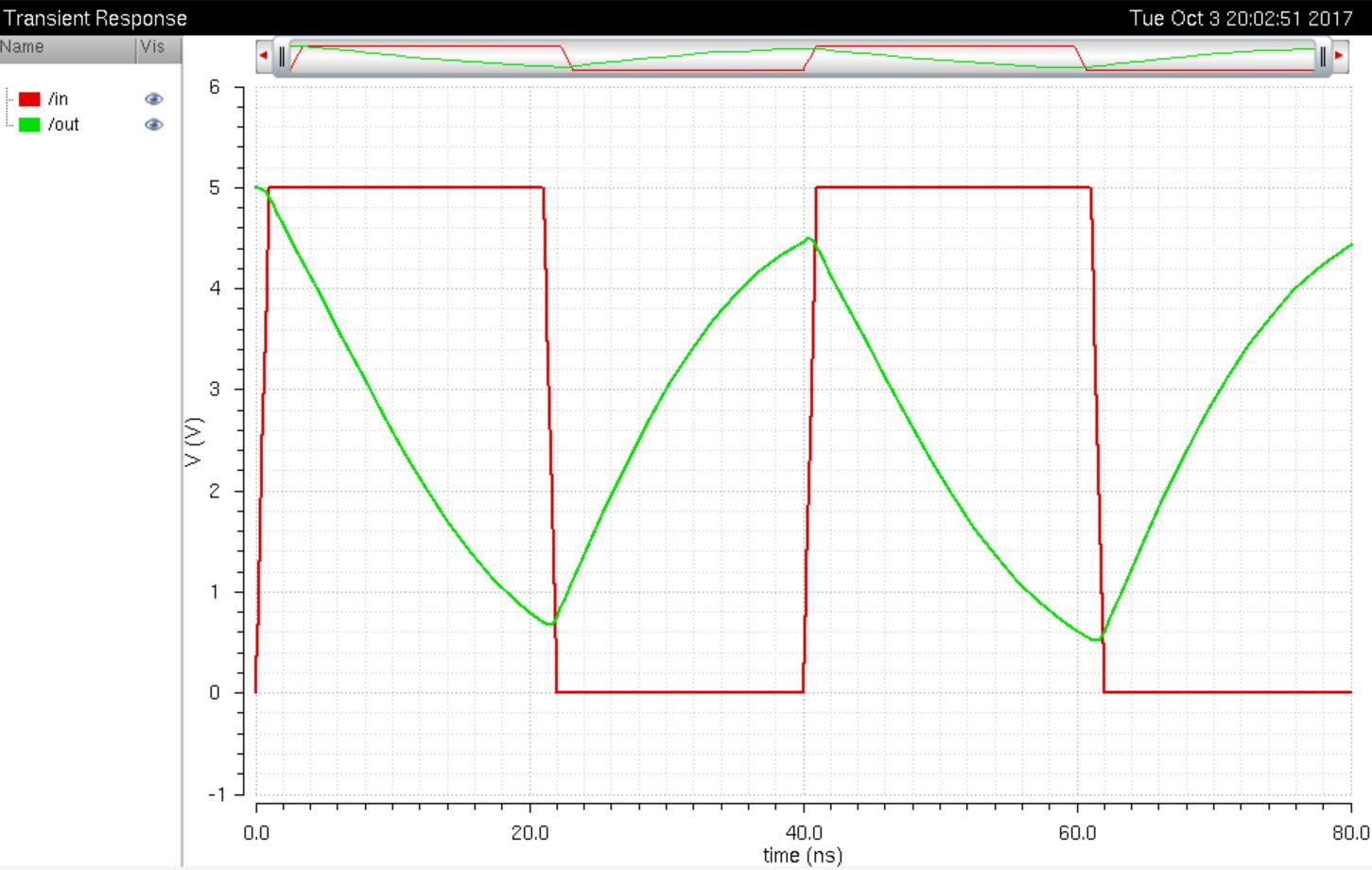

| 12u/6u inverter driving 100pF capacitor | Simulated using Specter | Simulated using UltraSim |

|  |  |

The

12u/6u inverter drives the smaller capacitor loads one time, but as the

load capacitance is increased it took longer time to charge the

larger capacitor.

The plots of the Specter and UltraSim plots are equal. |

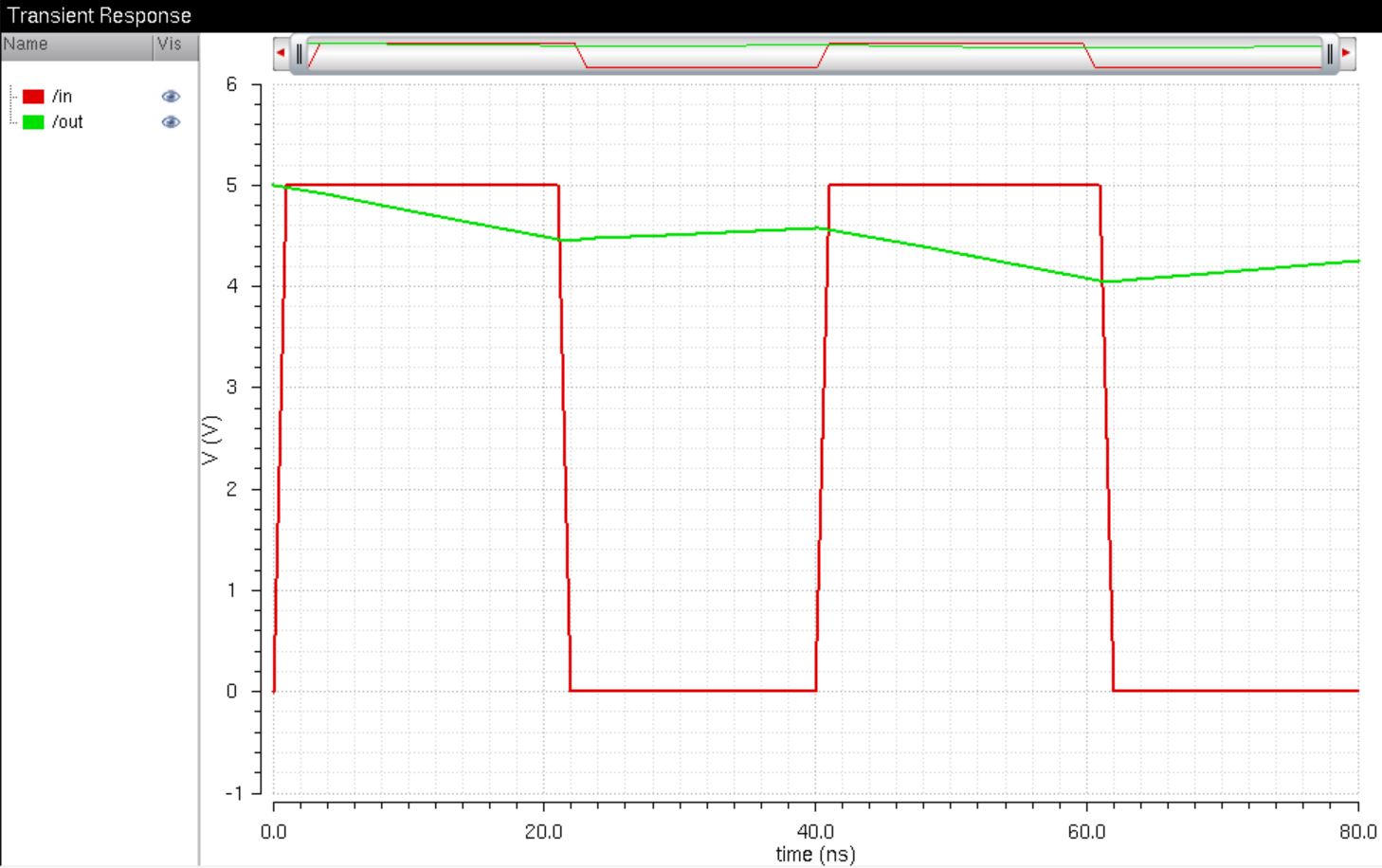

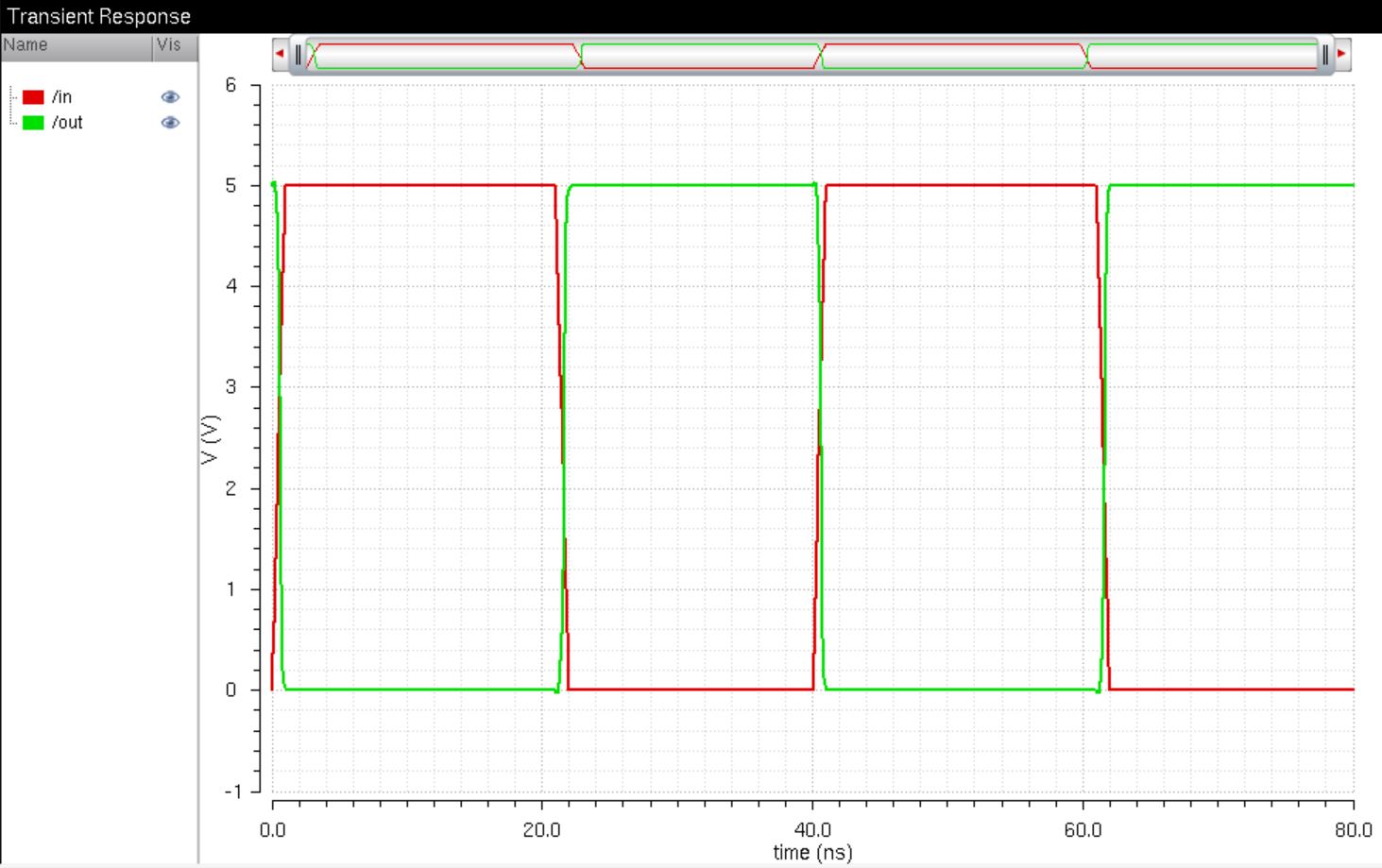

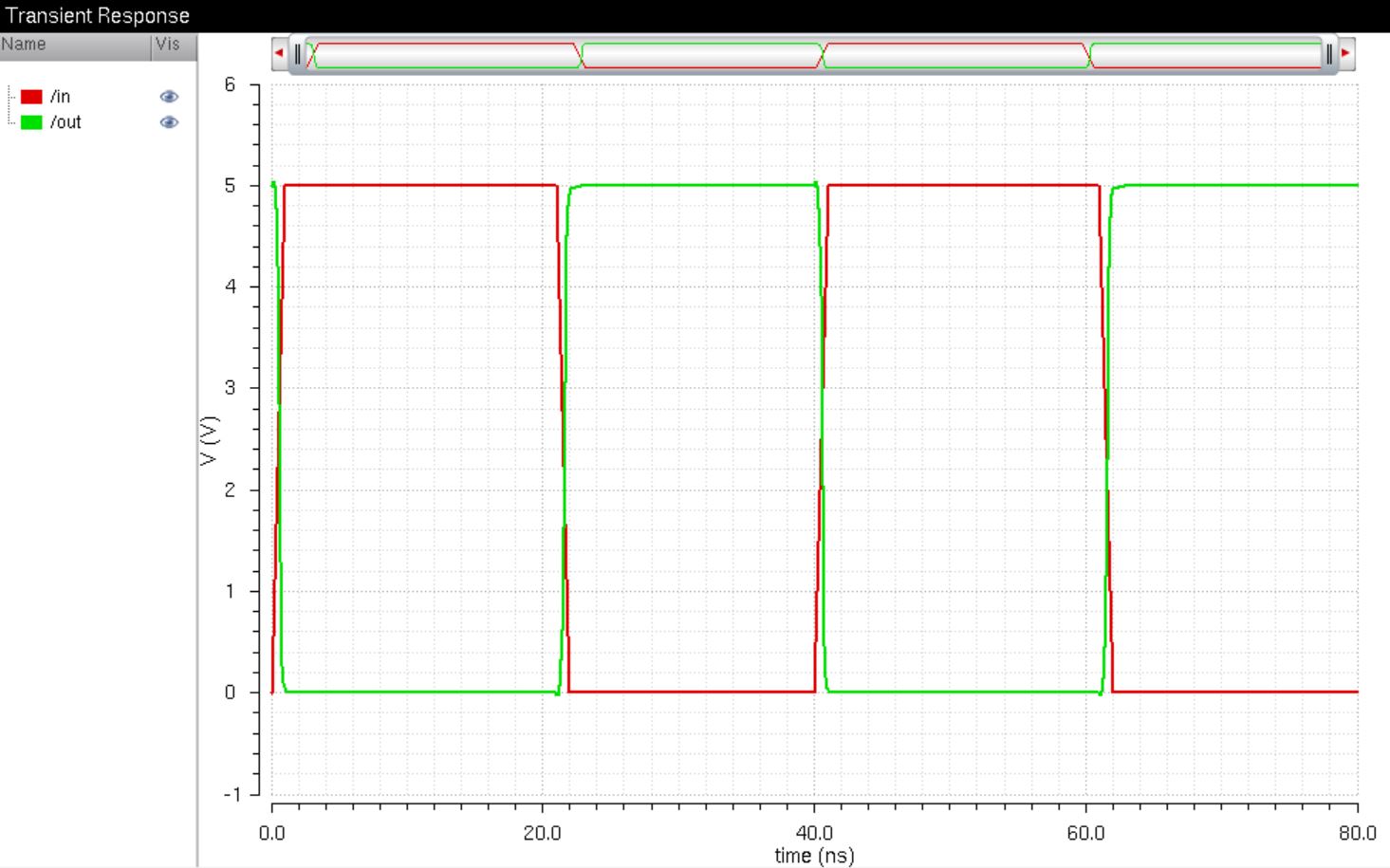

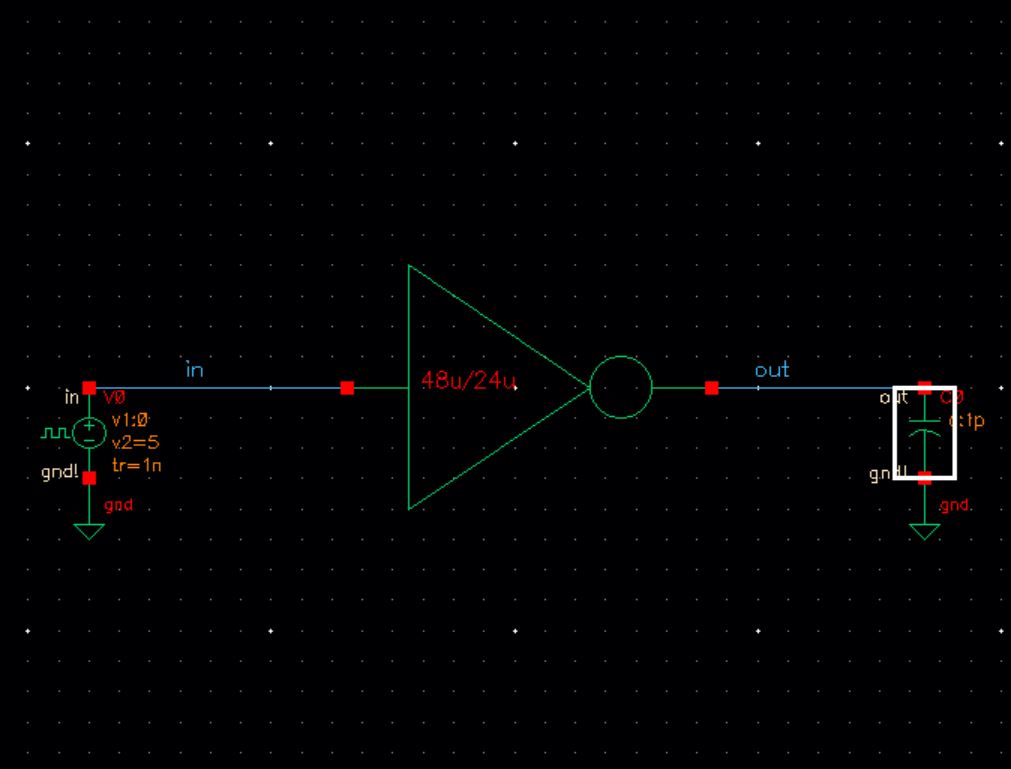

Specter and UltraSim Simulation of 48u/24u inverter

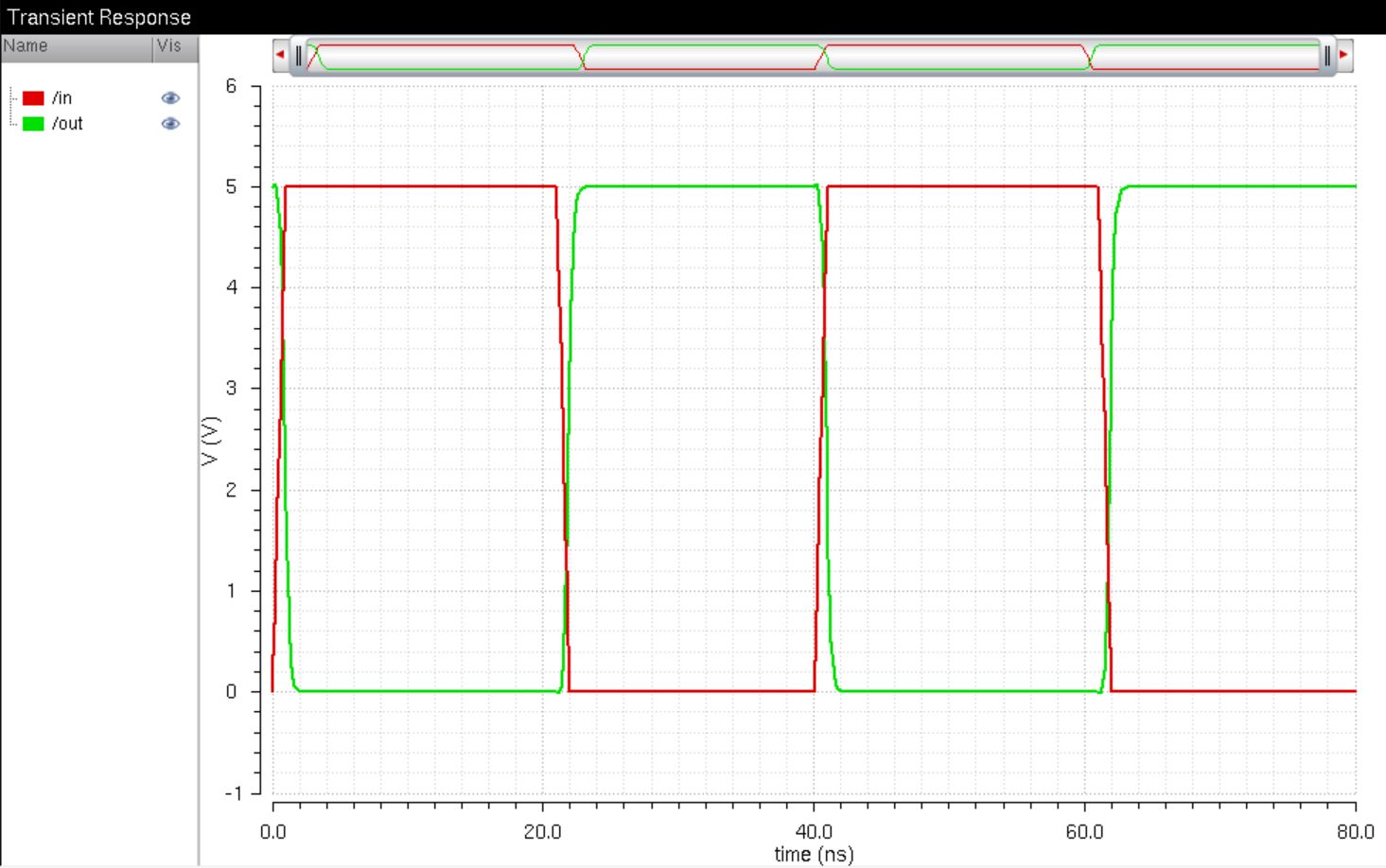

| 48u/24u inverter driving 100fF capacitor | Simulated using Specter | Simulated using UltraSim |

|  |  |

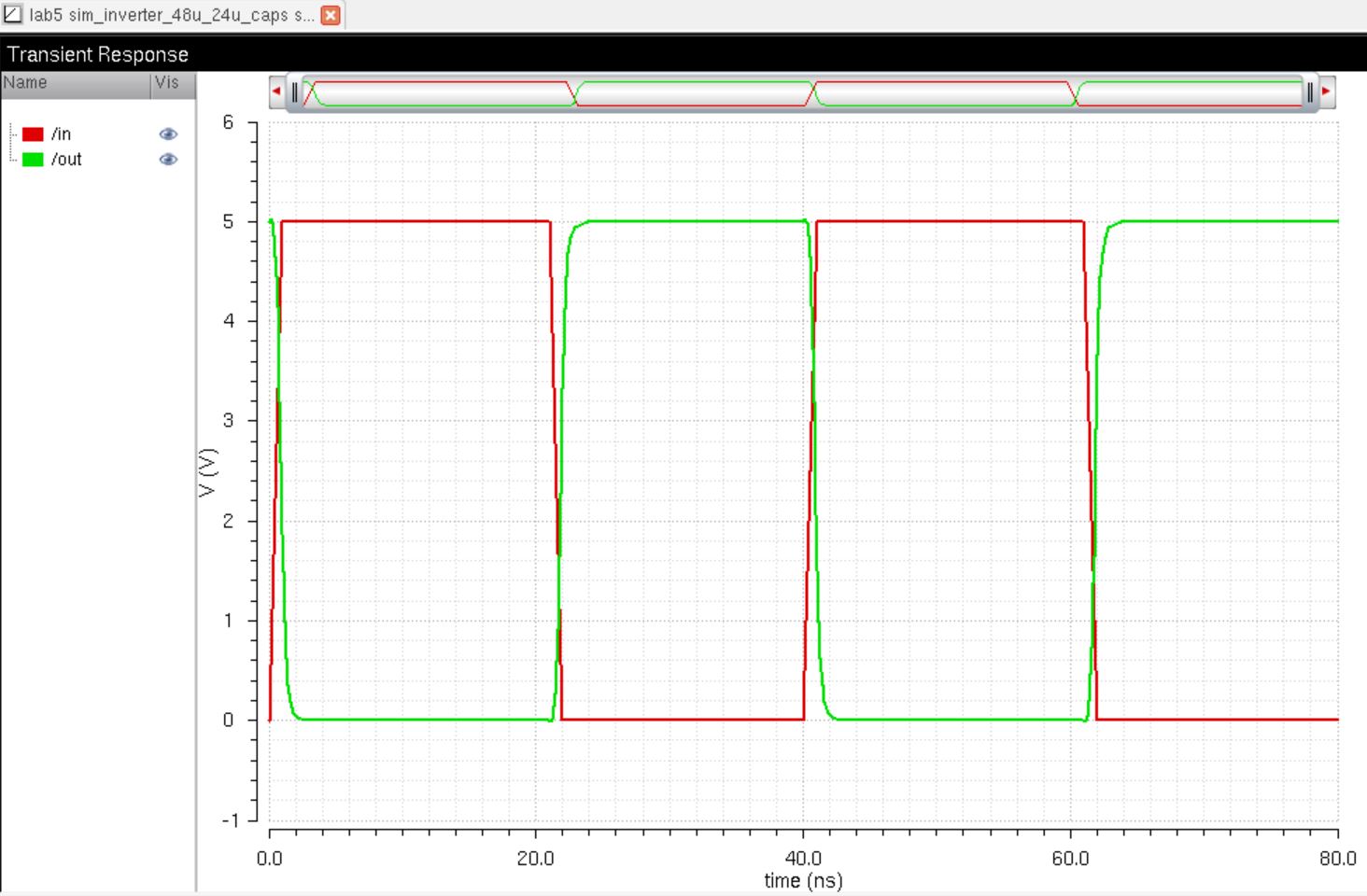

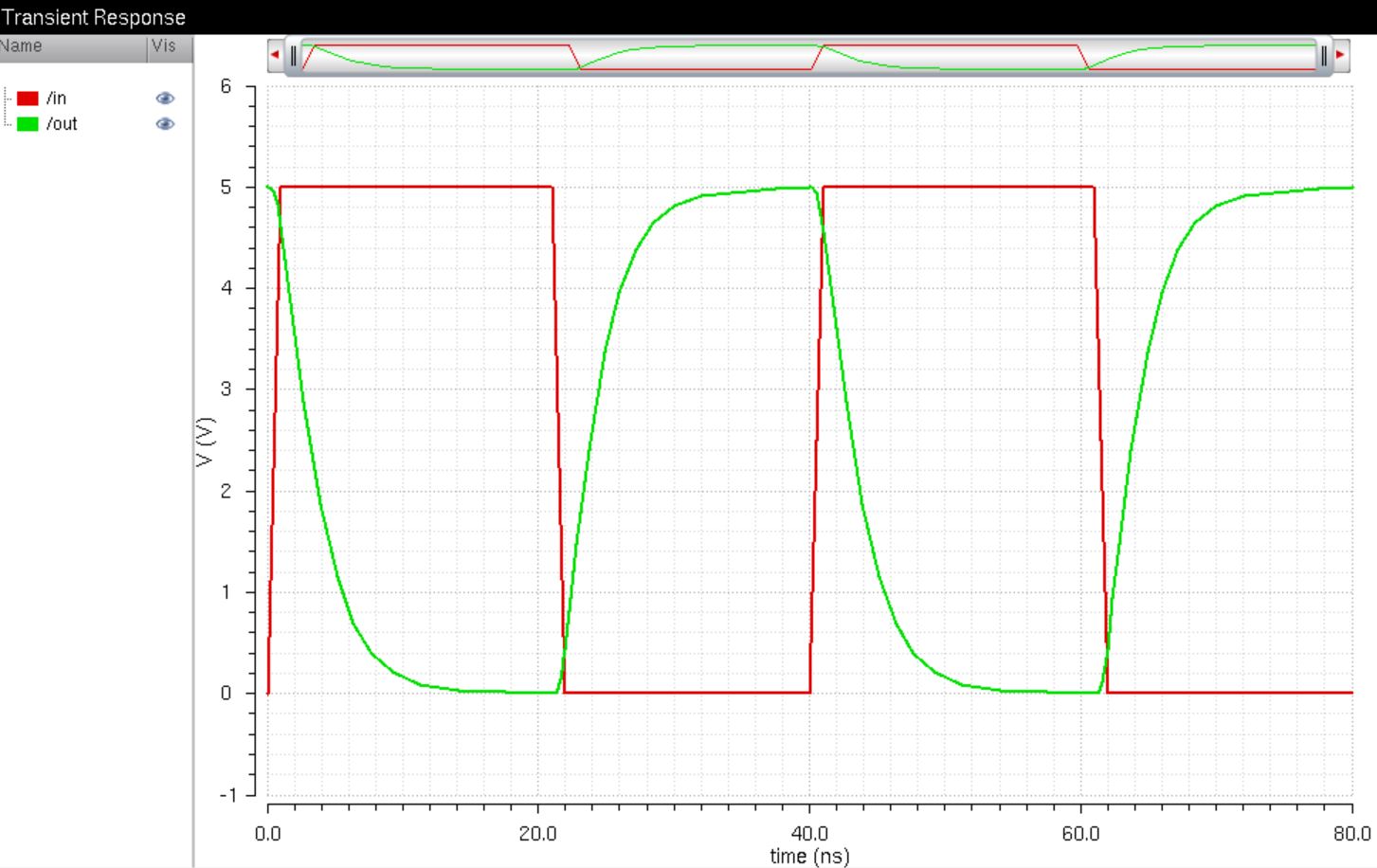

| 48u/24u inverter driving 1pF capacitor | Simulated using Specter | Simulated using UltraSim |

|

|  |

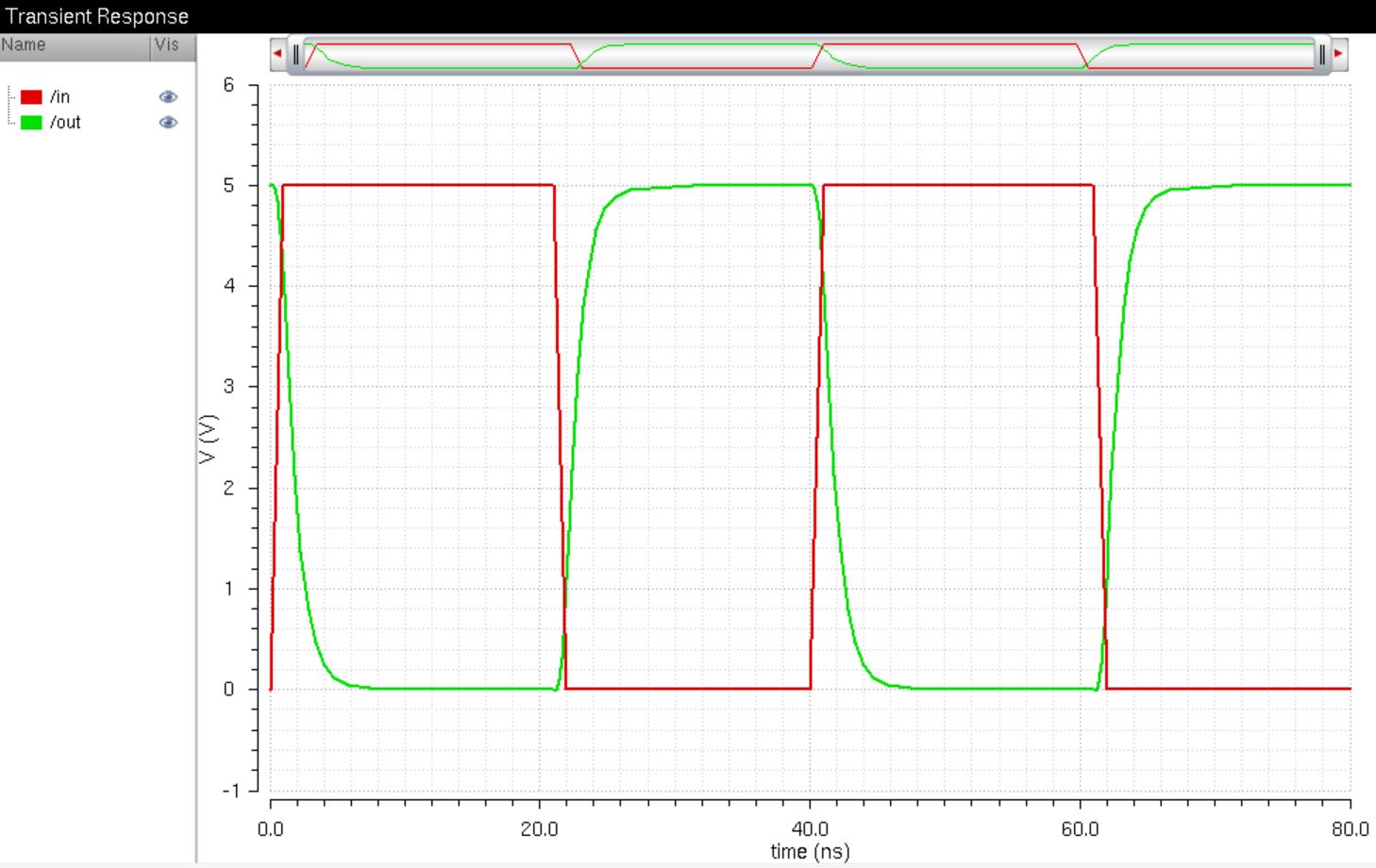

| 48u/24u inverter driving 10pF capacitor | Simulated using Specter | Simulated using UltraSim |

|  |  |

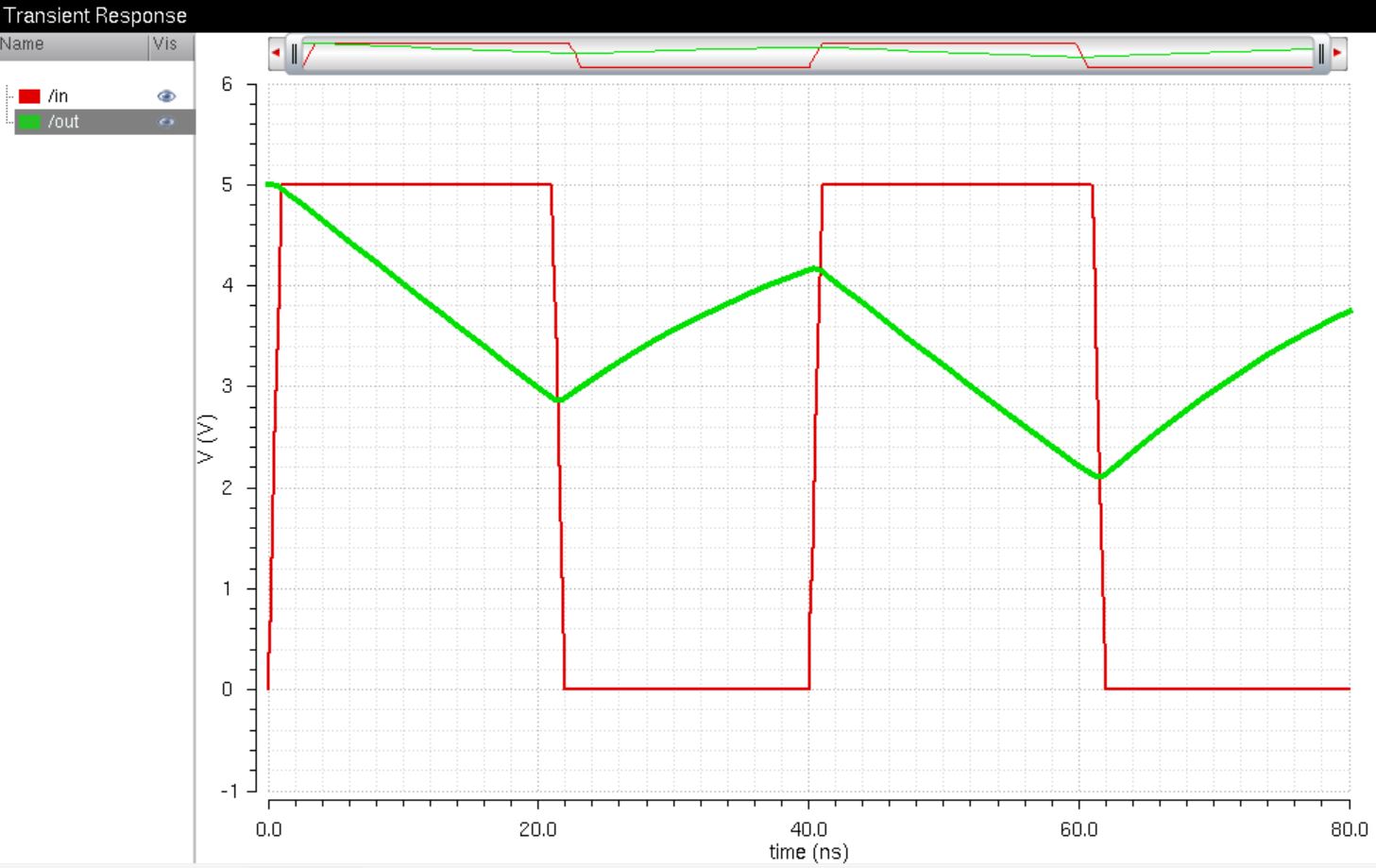

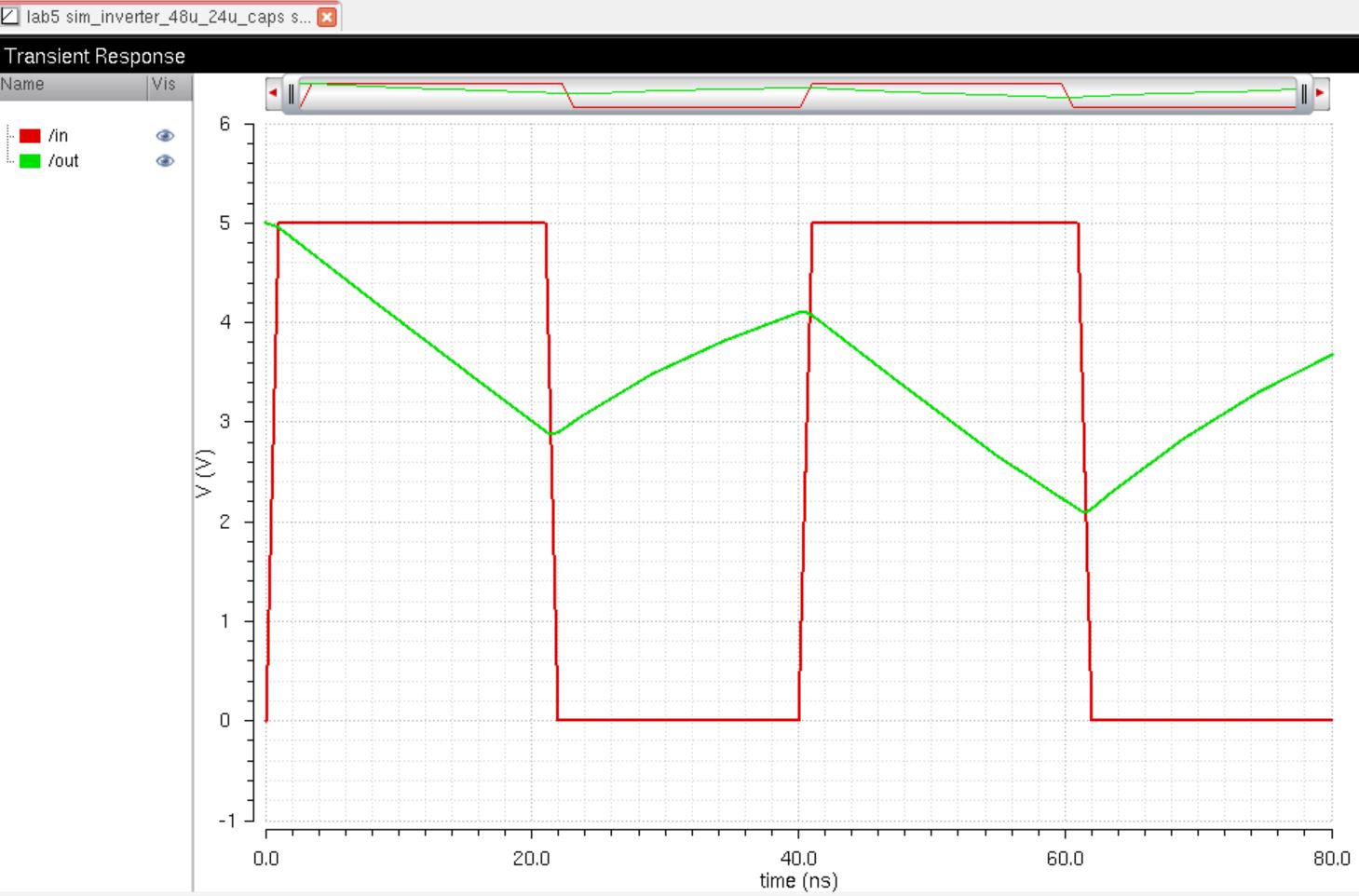

| 48u/24u inverter driving 100pF capacitor | Simulated using Specter | Simulated using UltraSim |

|  |  |

The

48u/24u inverter performs better than the 12u/6u inverter in driving

the different size of capacitors because it has he larger channel to

conduct current.

The plots of the Specter and UltraSim plots are equal. |

Lab5 files

Return to Abera lab

Return to EE 421L Labs