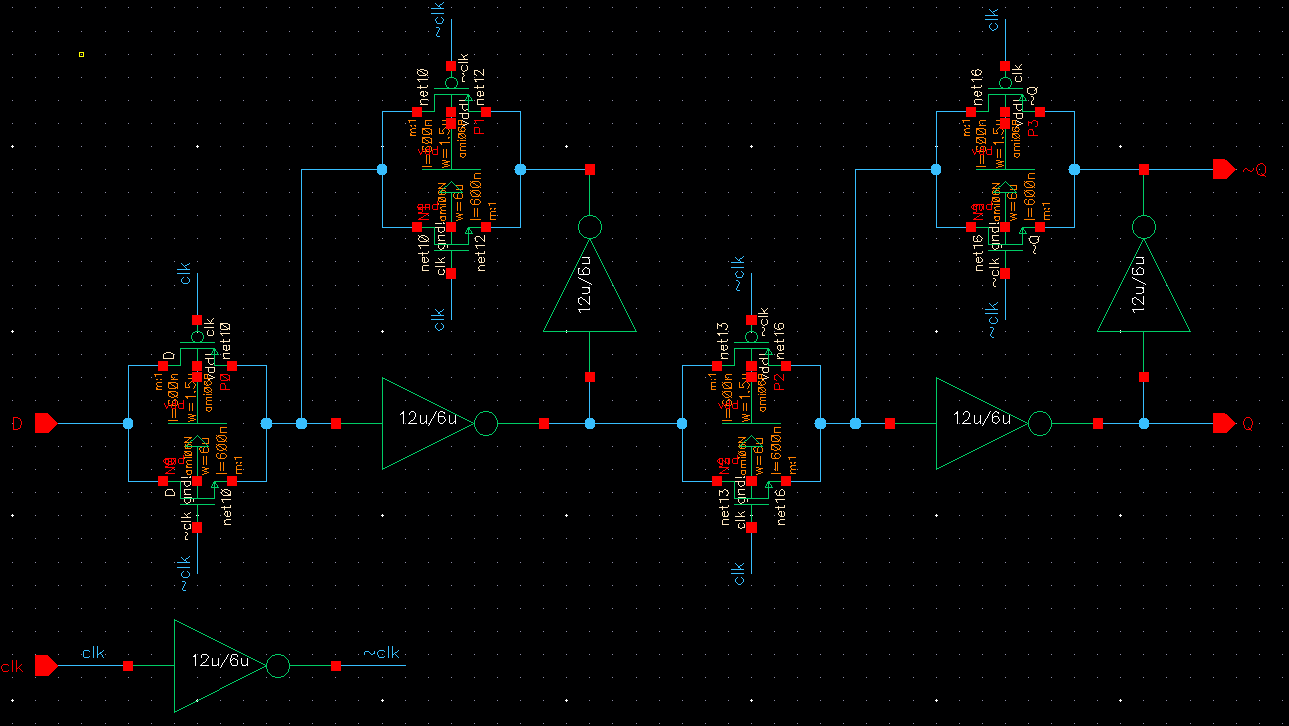

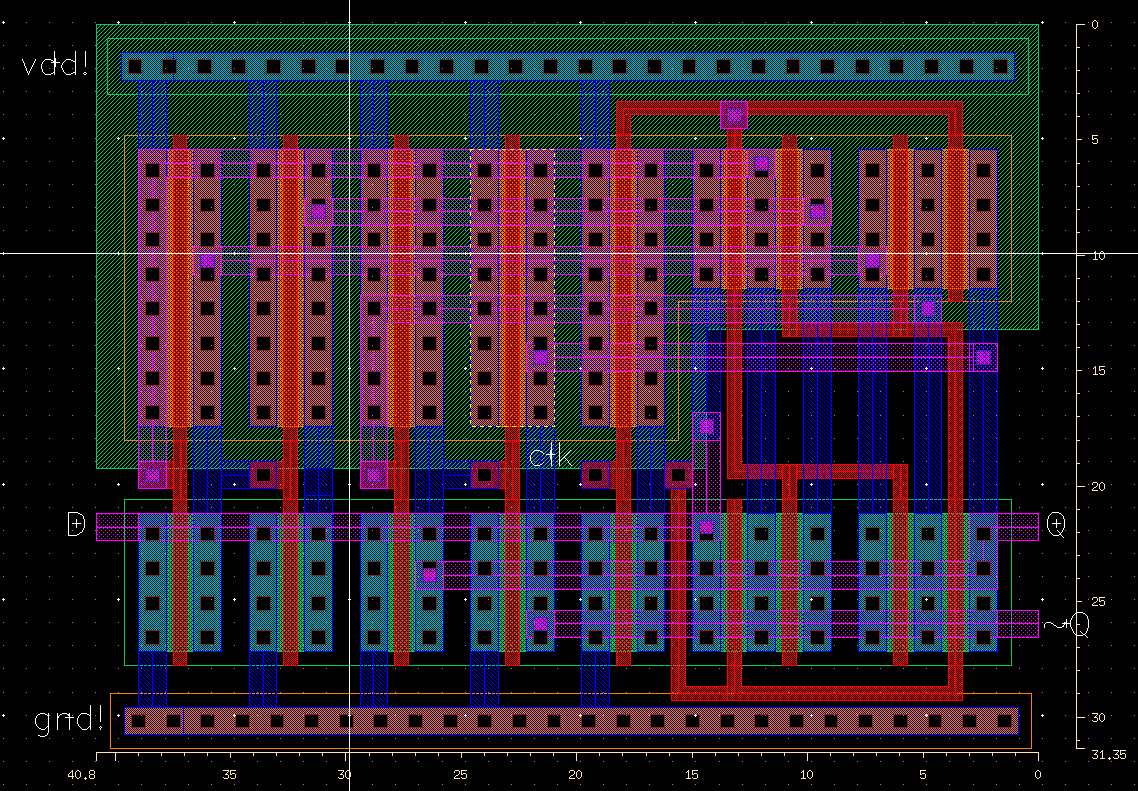

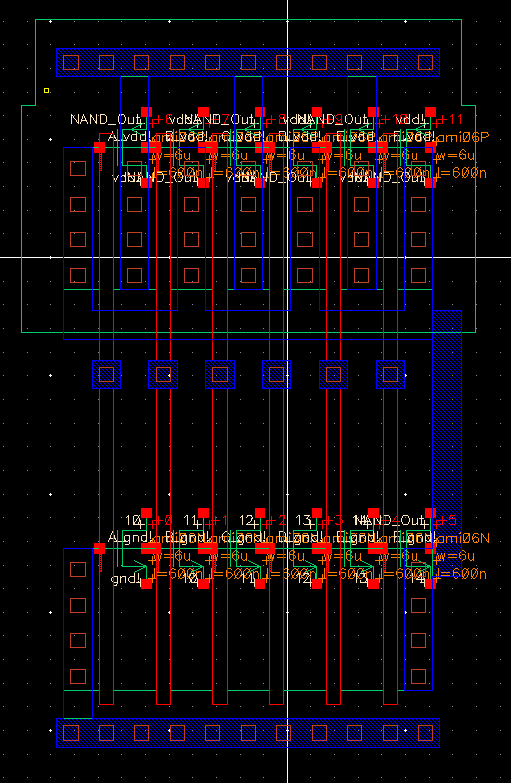

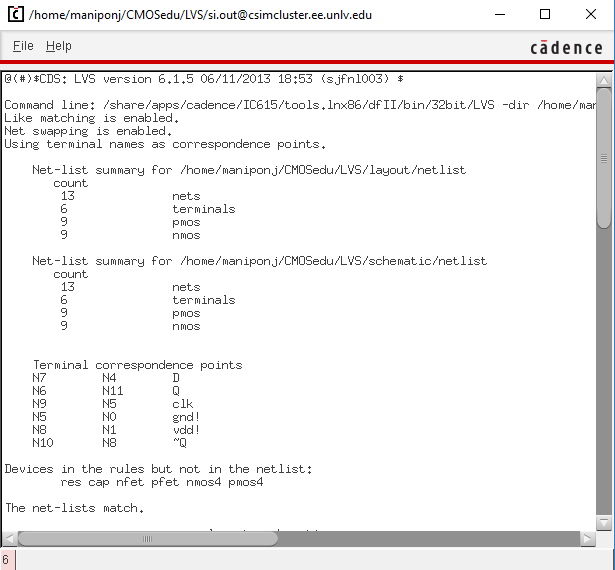

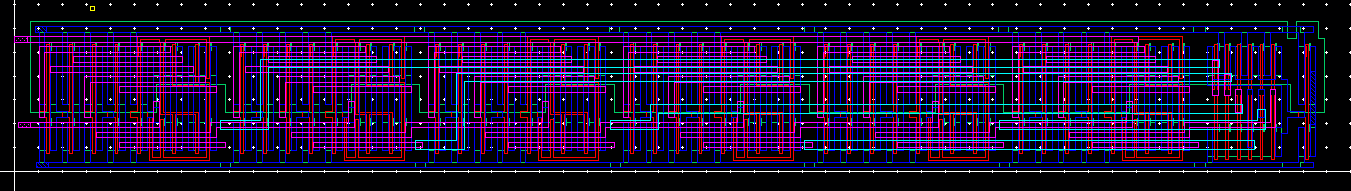

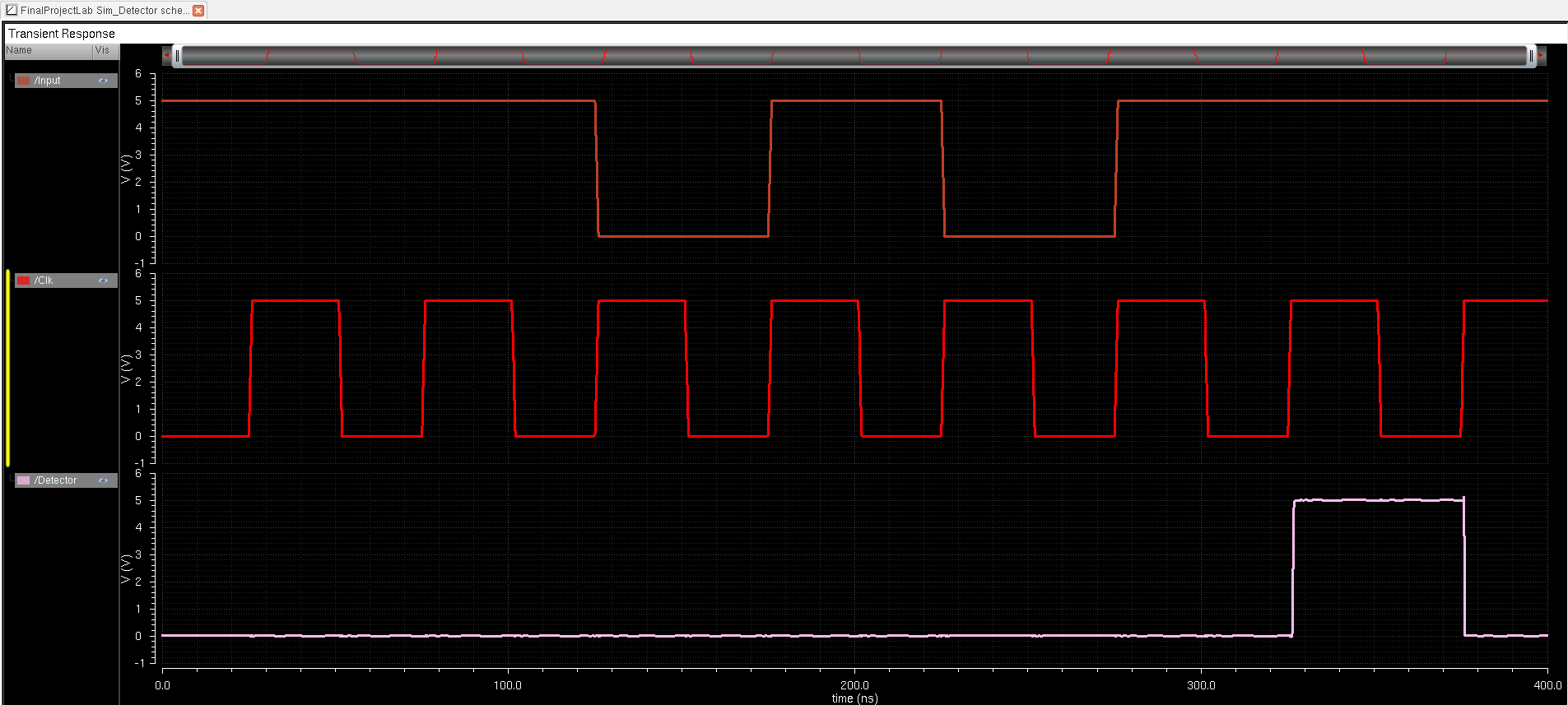

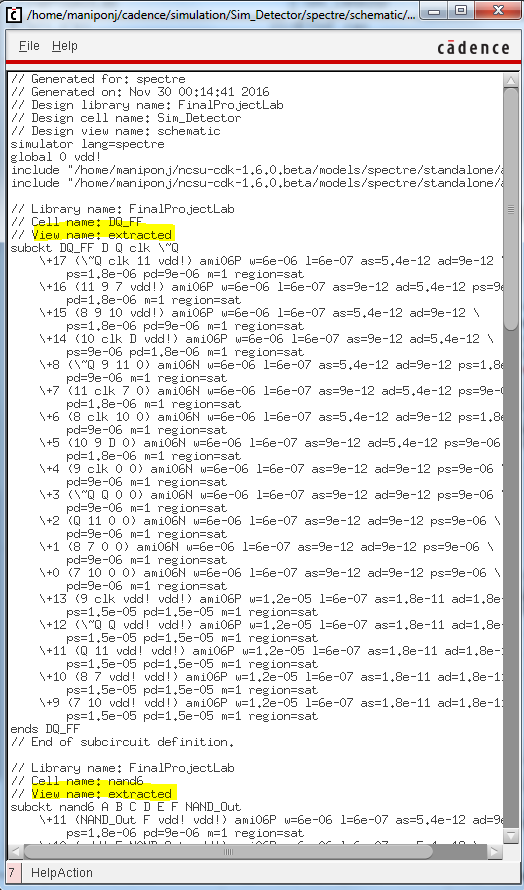

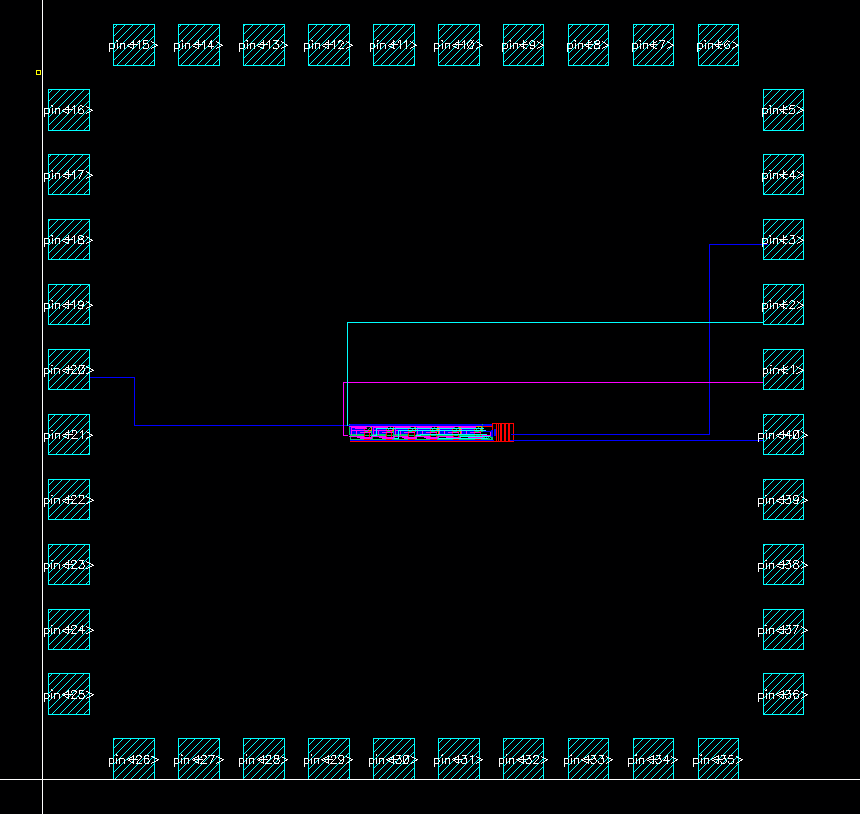

| Comments | - The D Flip Flop is organized with all my Inverters on the left side and my Transmission Gates are on the right side. The

inverters are organized left to right based on the schematic. The

Transmission Gates were able to be combined due to the source or drains

were connected based also on the schematic

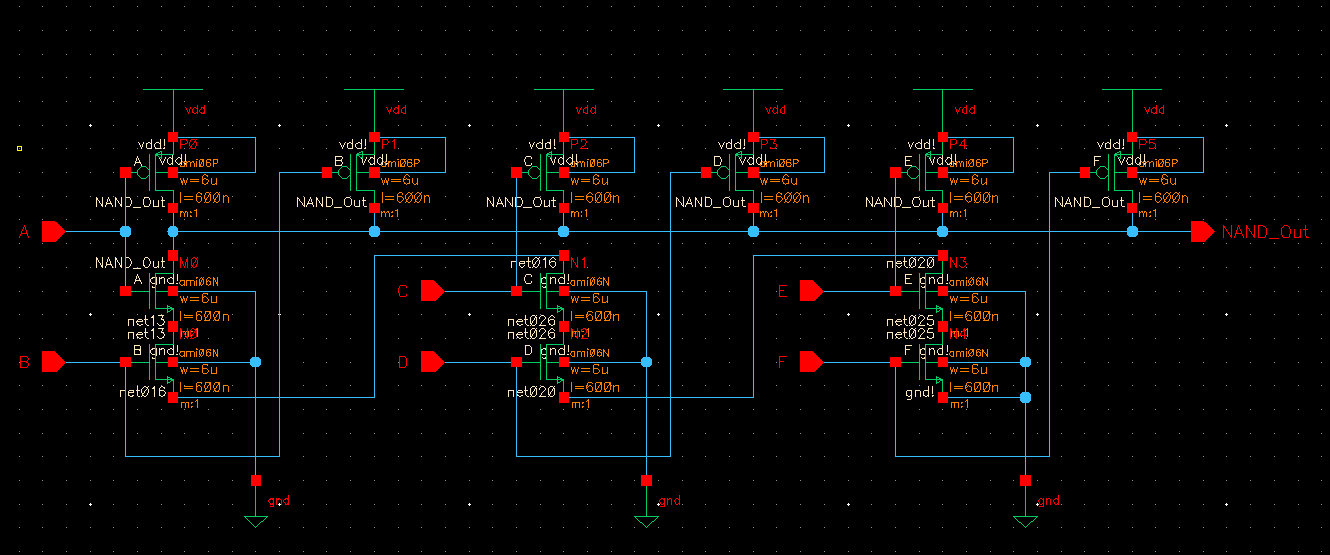

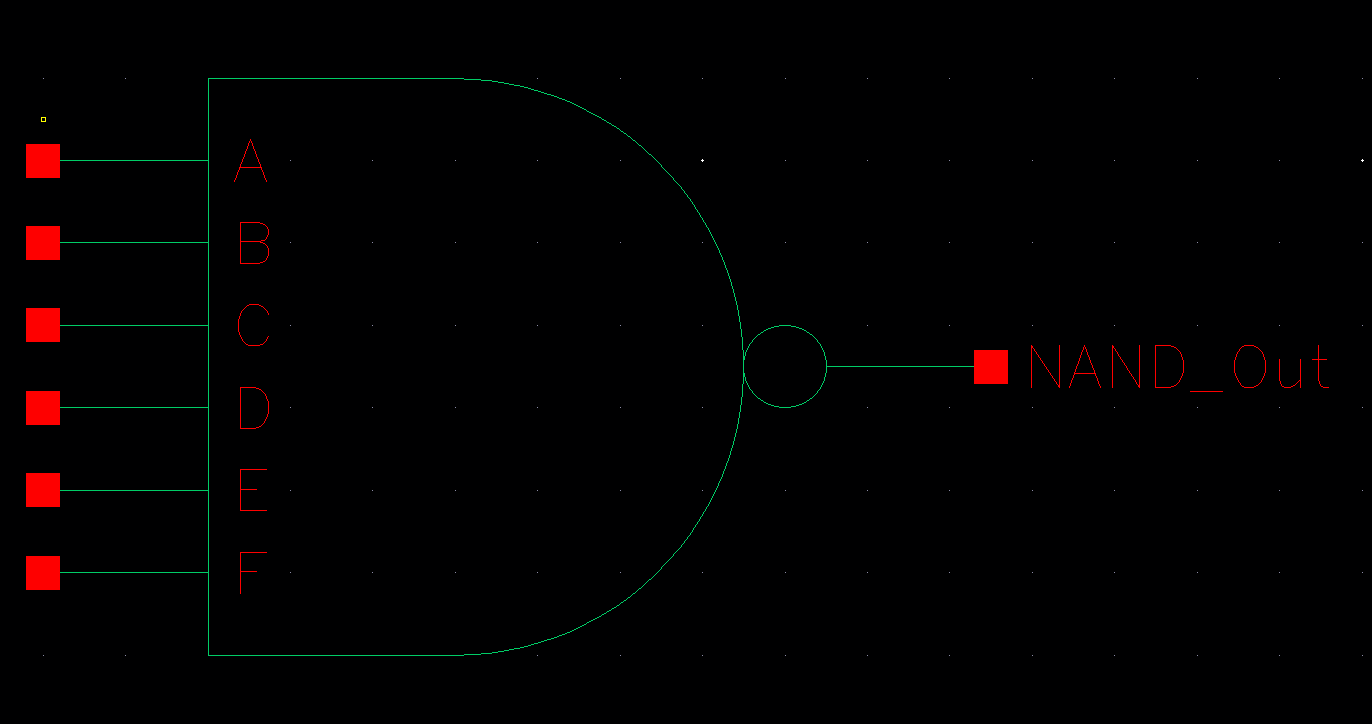

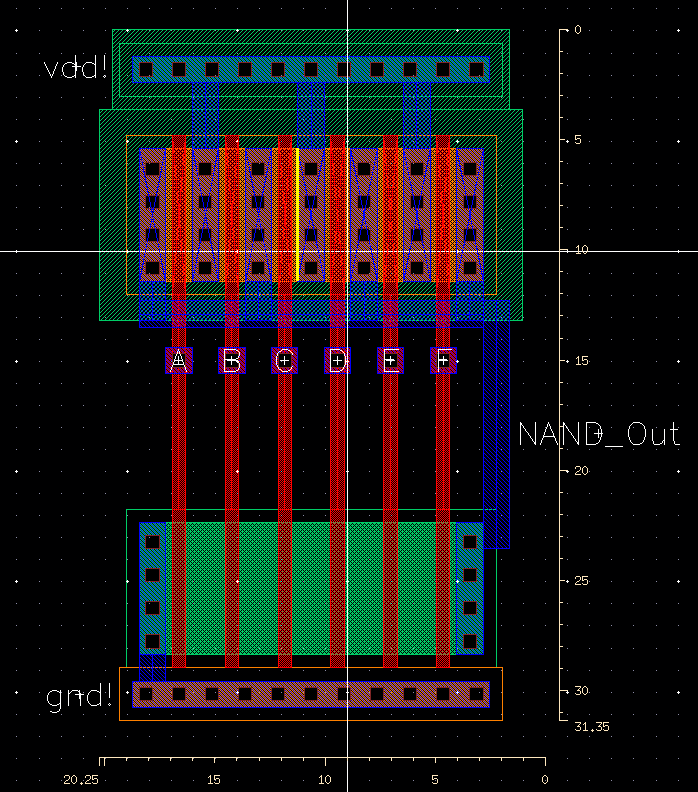

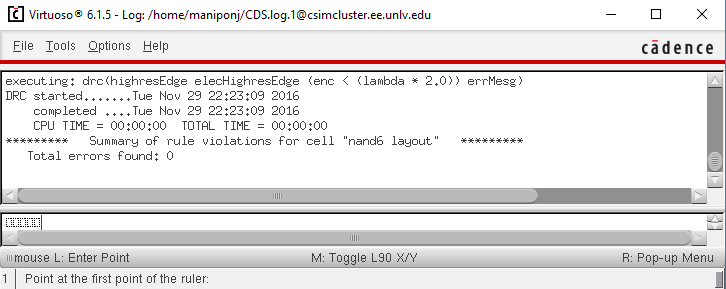

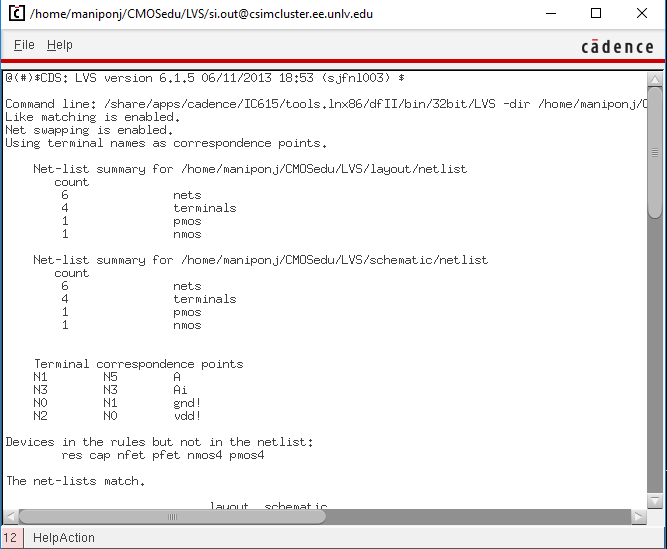

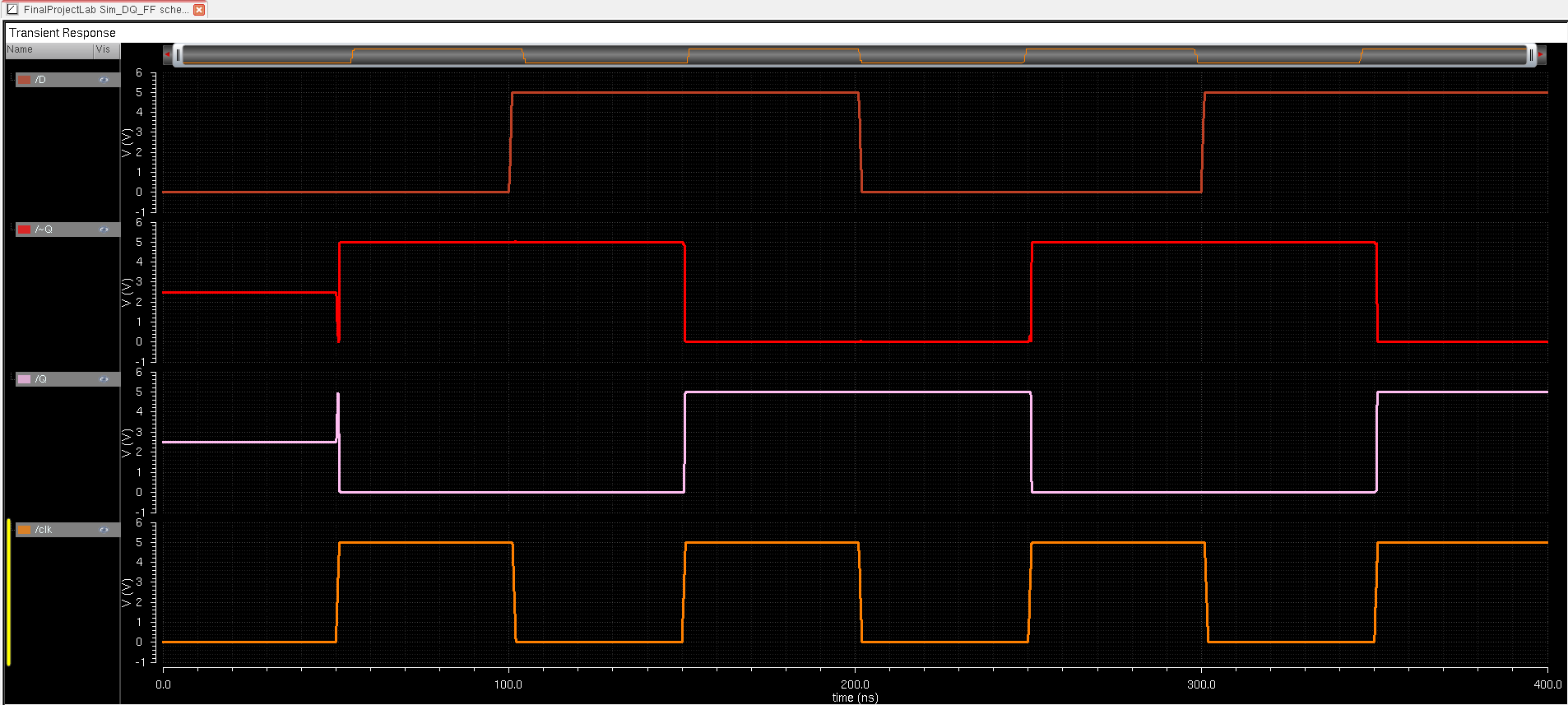

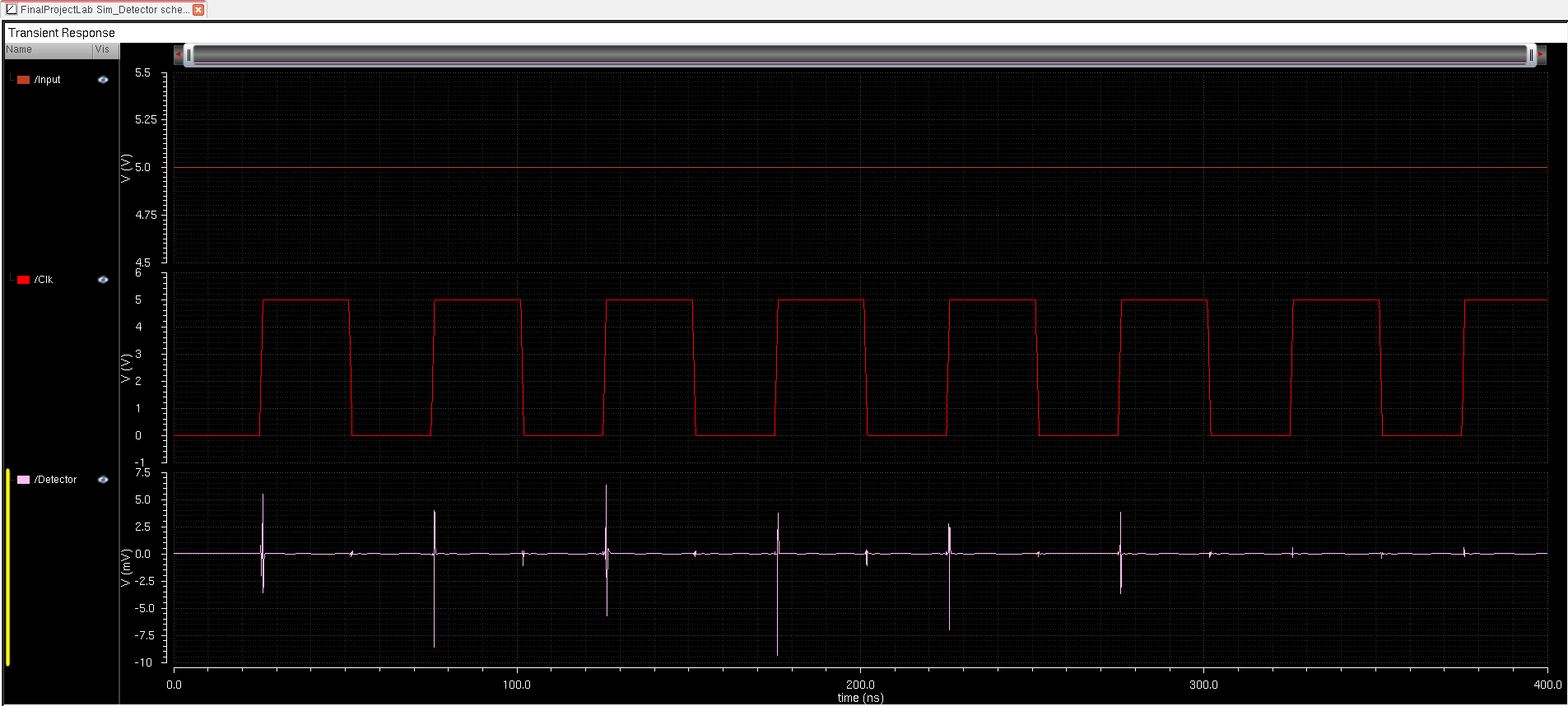

| - With

the NAND gate, I based it on the previous 2 Input NAND gate from

previous labs. I increased the multiplier to 6 on both the NMOS and

PMOS due to an increase of inputs.

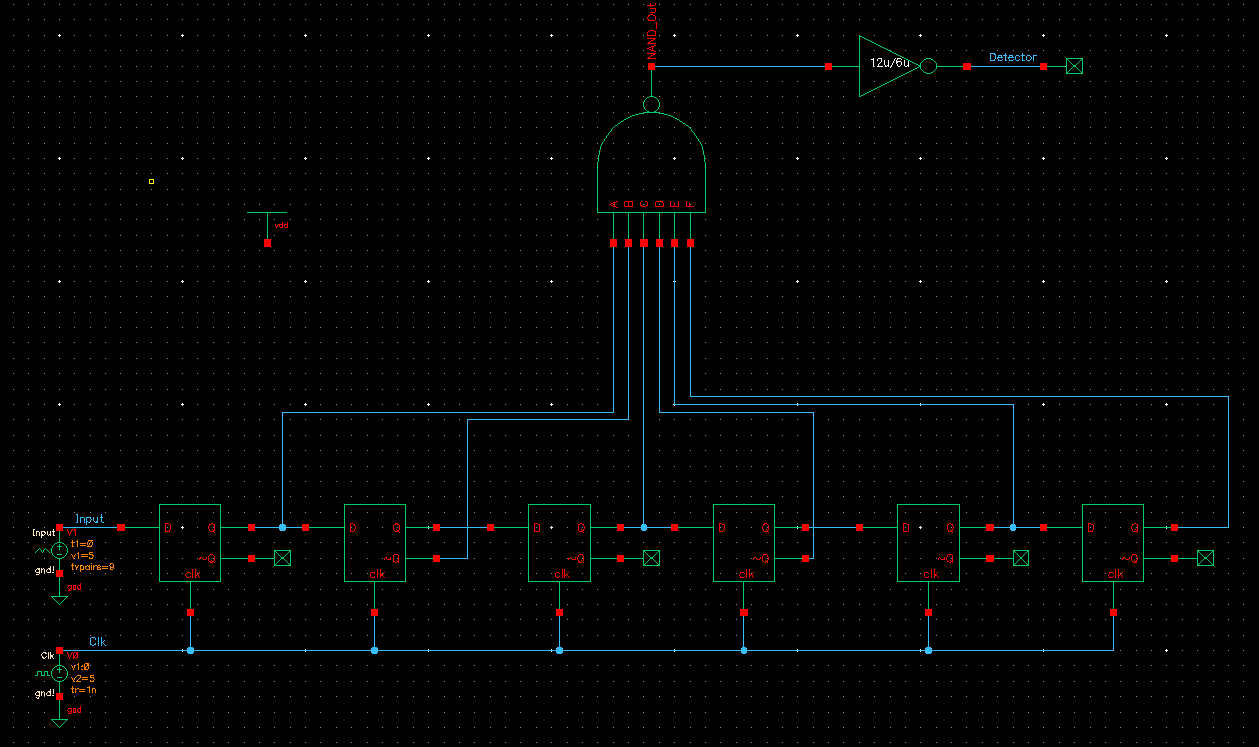

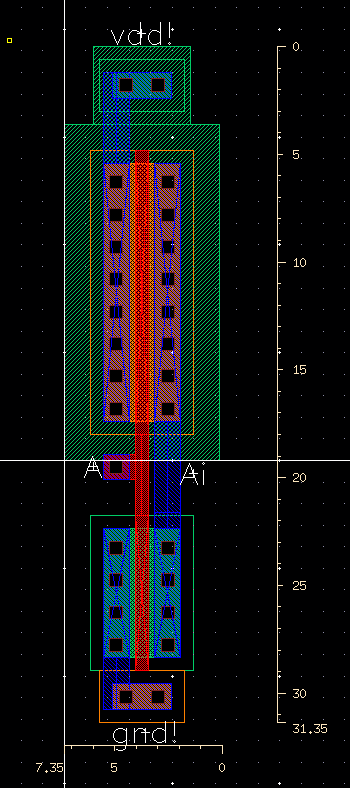

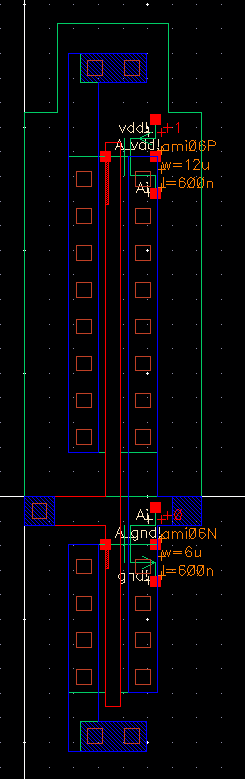

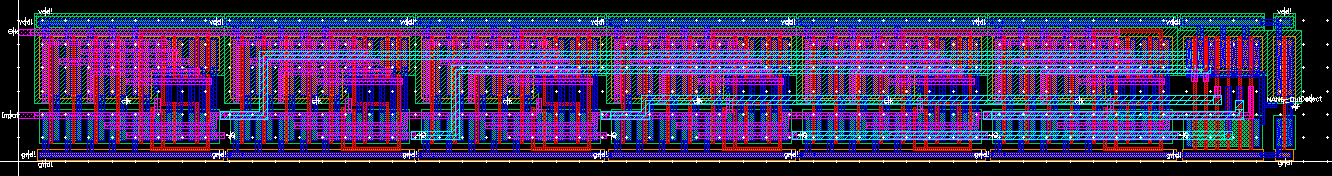

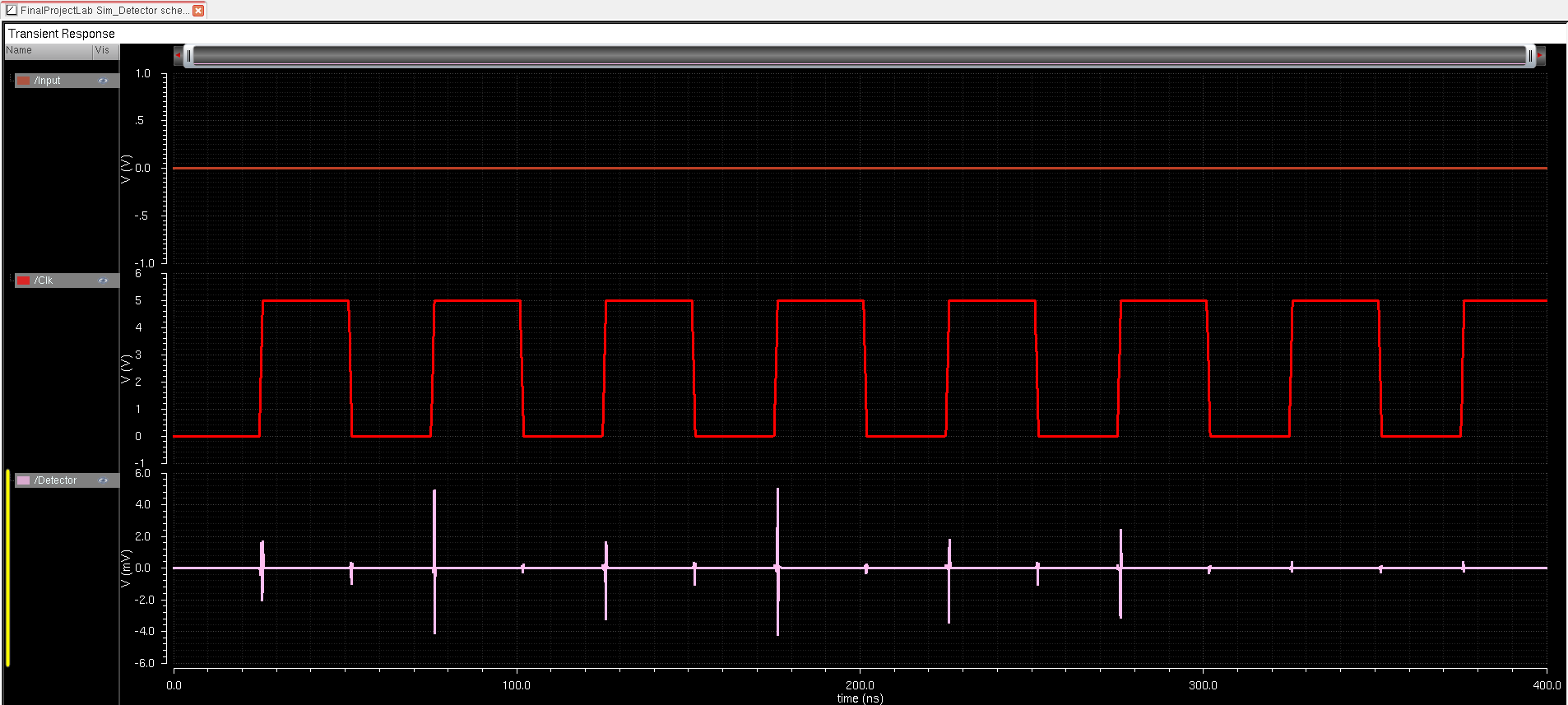

| - This

inverter was created from my previous labs and was needed for the

output of the NAND gate in order to have it output high when the

sequence was detected

|