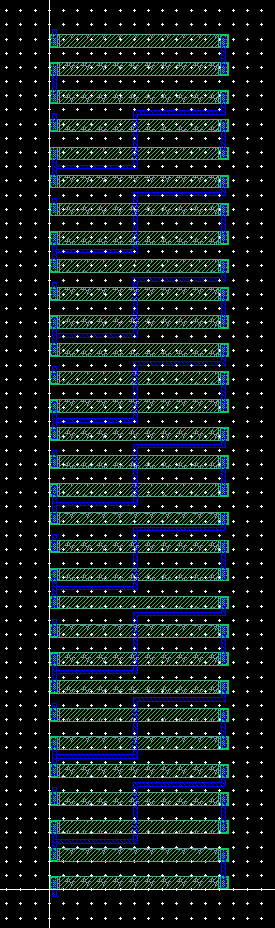

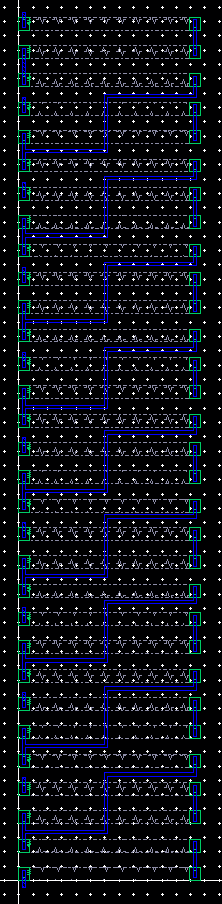

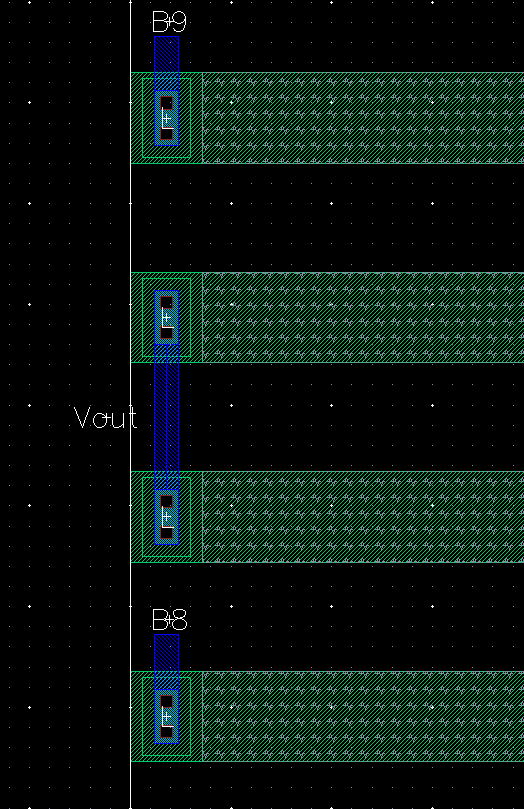

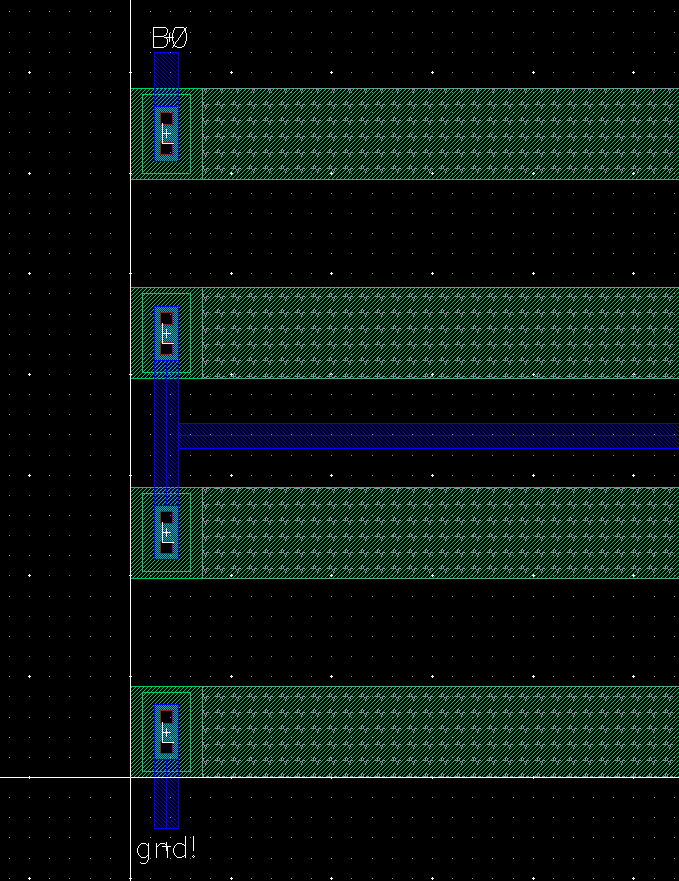

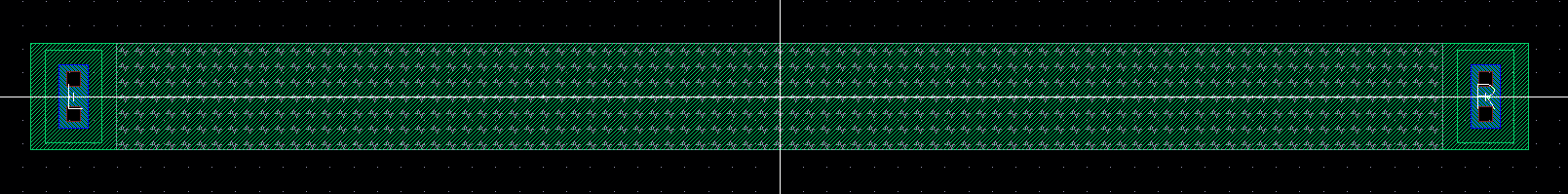

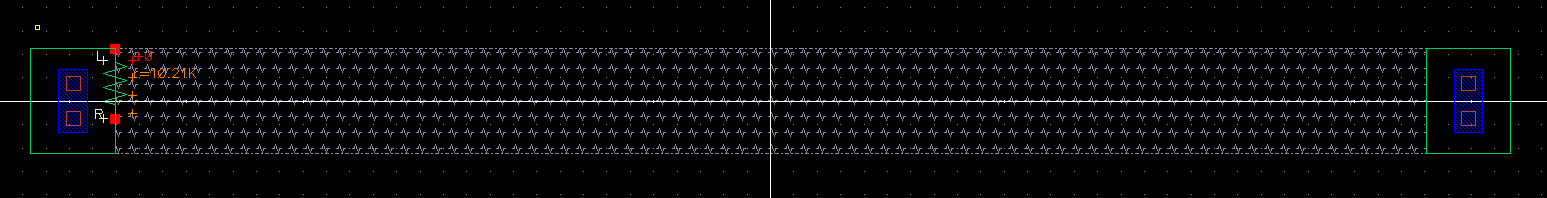

L = (10K*4.5u)/800

L = 56.25um

This is how I calculated the length of the N-Well. In the tutorial, it asks you to put in a length of 56um however 56um does not land in the .15um grid per the DRC. So I had to add the .1um in order to make it land on the grid. 56.25um would also work since 56.25/.15 = 375.

L = 56.25um

This is how I calculated the length of the N-Well. In the tutorial, it asks you to put in a length of 56um however 56um does not land in the .15um grid per the DRC. So I had to add the .1um in order to make it land on the grid. 56.25um would also work since 56.25/.15 = 375.