Lab 7 - ECE 421L

8-bit inverter schematic 8-bit inverter symbol

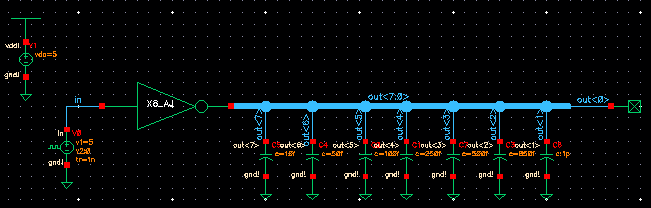

8-bit inverter simulation schematic

| A | Ai |

| 0 | 1 |

| 1 | 0 |

8-bit inverter simulation results

8-bit NAND schematic 8-bit NAND symbol

| A | B | AnandB |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

NAND Truth Table

8-bit NAND simulation results

8-bit NOR schematic 8-bit NOR symbol

| A | B | AnorB |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

NOR Truth Table

8-bit NOR simulation results

8-bit AND schematic 8-bit AND symbol

| A | B | AandB |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

AND Truth Table

8-bit AND simulation results

8-bit OR schematic 8-bit OR symbol

| A | B | AorB |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

OR Truth Table

8-bit OR simulation results

For the next part of the lab I designed a 2-to-1 MUX/DEMUX. The MUX works as a selector to choose one input or another depending on the value of S. The circuit (shown below) can also work as DEMUX by simply making the output the input and the inputs the outputs. That way the value of S determines to which output the input will go to. Once this was designed a symbol was made for it a simulation was done to check its performance. Below are the images of the MUX/DEMUX, its symbol and the simulation results with a truth table.

MUX/DEMUX schematic MUX/DEMUX symbol

| A | B | S | Z |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

MUX/DEMUX Truth Table

MUX/DEMUX simulation results

The 8-bit MUX/DEMUX was designed similar to the gates. However, the Si input was removed and was replace with an inverter on the S input. Below are images of the 8-bit MUX/DEMUX schematic, the represented symbol and the simulation schematic and results.

8-bit MUX/DEMUX schematic 8-bit MUX/DEMUX symbol

8-bit MUX/DEMUX simulation schematic

8-bit MUX/DEMUX simulation results

For the final part of the lab I had to draft a full-adder from Fig. 12.20 of the CMOS textbook. The drafted schematic, full adder symbol, simulation results and a truth table for the full adder are shown below.

full-adder schematic full-adder simulation schematic with symbol

| A | B | C | S | C+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

full-adder Truth Table

Full-adder simulation results

The 8-bit full adder was drafted along with the symbol. For the full adder to work the carry out of one adder has to connect to the carry in of the next full adder, so the looping on the carry in in made in the 8-bit full adder schematic. So for the symbol there is only one carry in input. The schematic, symbol and simulation results are shown below.

8-bit full-adder schematic 8-bit full-adder symbol

8-bit full adder simulation schematic

8-bit full adder simulation results

A layout was done of the 8-bit full adder and an DRC and LVS were performed on the layout. Below are images of a single full adder layout, the 8-bit full adder layout and the LVS and DRC for the 8-bit full adder layout.

1-bit full-adder layout

8-bit full-adder layout

8-bit full-adder DRC 8-bit full-adder LVS