Lab 5 -

ECE 421L

Design, layout, and simulation of a CMOS inverter

Authored

by Tyler Huddleston, huddle10@unlv.nevada.edu

10/4/2016

This

lab involves constructing and simulating CMOS inverters of two

different sizes. The inverter schematics and layouts were

designed and then simulated with varying capacitive loads to observe

how the switching delay is affected.

Pre-lab Work

- Back-up

all of your work from the lab and the course: My work is backed

up on to my Dropbox account (seen on left of image) and my hard drive.

- Go through Tutorial 3: Tutorial 3 was completed and the 12u/6u inverter from it was used in this lab.

Lab Work:- Draft schematics, layouts, and symbols for two inverters having sizes of:

- 12u/6u (= width of the PMOS / width of the NMOS with both devices having minimum lengths of 0.6u)

- 12u/6u inverter schematic:

- 12u/6u inverter layout:

- 12u/6u inverter symbol:

- 48u/24u where the devices use a multiplier, M = 4 (set along with the width and length of the MOSFET, image), as seen below

- 48u/24u inverter schematic:

- 48u/24u inverter layout:

- 48u/24u inverter symbol:

- Meets specifications

- Power is run on the top of the cell via metal1 and ground is run on the bottom of the cell also via metal1

- Power (vdd!) is connected to the n-well using the ntap cell

- Ground (gnd!) is connected to the p-substrate using the ptap cell

- Running power and ground with a single row of contacts, instead of 2 as seen below, is fine to reduce layout size

- Your schematics should have two pins: A and Ai

- Your layouts should have 4 pins: A, Ai, vdd!, and gnd! (note how lowercase letters are used for power and ground)

- Your

lab reports should document your efforts and results including showing

that the extracted layouts and schematics LVS correctly

- 12u/6u inverter LVS:

- 48u/24u inverter LVS:

- Zip up these cells in a directory call lab5_rjb.zip (last two or three letters are your initials) and link to your lab report

- Using SPICE simulate the operation of both of your inverters showing each driving a 100 fF, 1 pF, 10 pF, and 100 pF capacitive load

- Comment, in your report, on the results

- 12u/6u inverter simulation schematic:

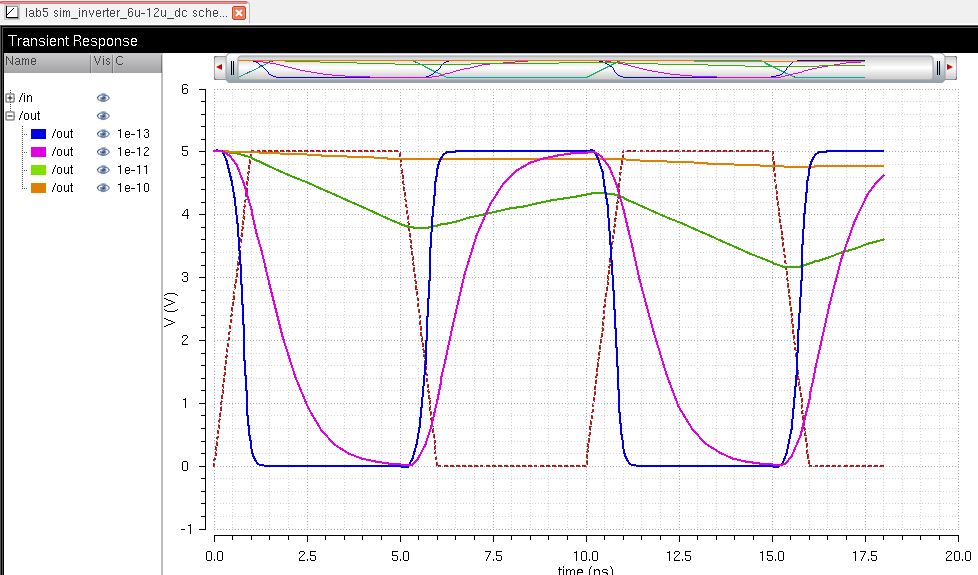

- Varying capacitor C to 100fF, 1pF, 10pF, and 100pF is done with parametric analysis to have each simulation on one graph:

- 12u/6u inverter simulation results:

- Red: inverter input, Blue: 100fF output, Purple: 1pF output, Green: 10pF output, Orange: 100pF output

- The

larger the capacitive load, the worse the output of the inverter.

At 10pF and above this inverter doesn't even act like an inverter

at the period of T=10ns. The output is recified by the capacitor,

because the capacitor supplies extra current when the inverter voltage

changes, and keeps the output voltage from changing too greatly.

The 1pF capcitor makes the inverter output switch very slow.

100fF is fast enough of a capacitive load for this inverter.

- The output capacitance should be as small as possible for an inverter to get close to ideal switching.

- 48u/24u inverter simulation schematic:

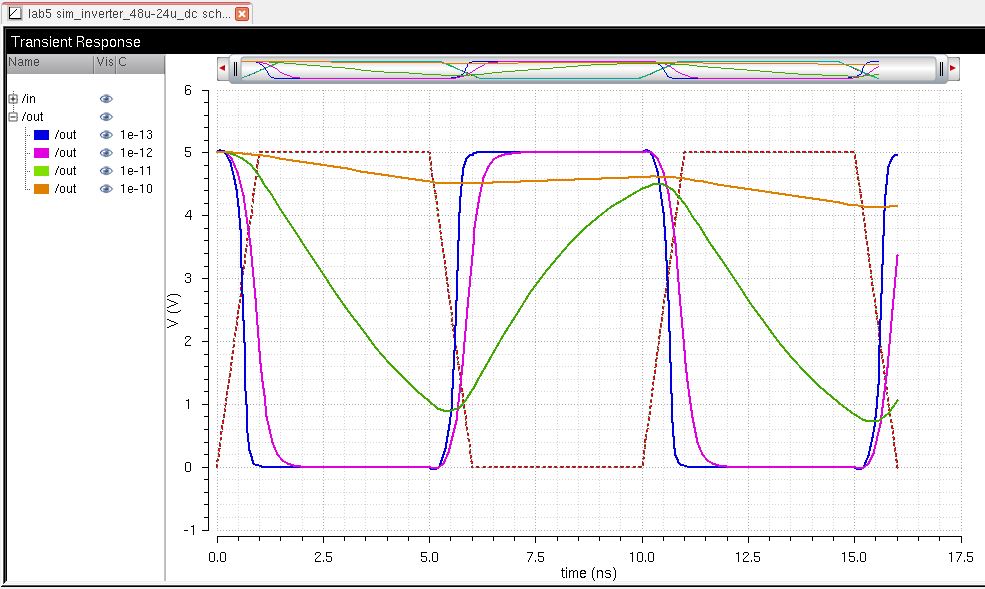

- 48u/24u inverter simulation results:

- Red: inverter input, Blue: 100fF output, Purple: 1pF output, Green: 10pF output, Orange: 100pF output

- Compared

to the 12u/6u inverter, the 48u/24u inverter has faster rising times

with varying capacitive loads. In thi case, the 10pF load would

be acceptable for this inverter but not for the 12u/6u inverter.

- Use UltraSim (Cadence's fast SPICE simulator for larger circuits at the cost of accuracy) and repeat the above simulations

- 12u/6u inverter UltraSim results:

- 48u/24u inverter UltraSim results:

- The

UltraSim simulations look almost identical to the Spectre ones, except

the curves are a bit more jagged. This is because UltraSim may be

more useful for larger schematics and these inverter schematics are not

too big.

Return

to EE 421L Labs

Return

to my Labs Index