Lab 3 - EE 421L

Prelab:

Read through & finish tutorial 1

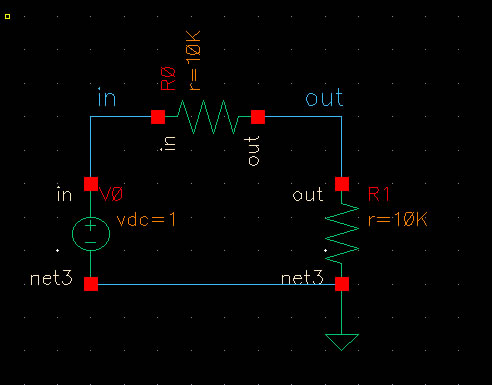

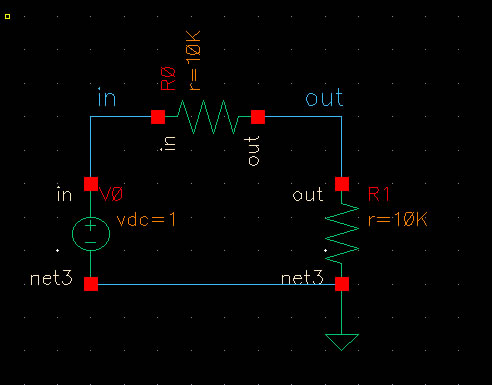

Original schematic

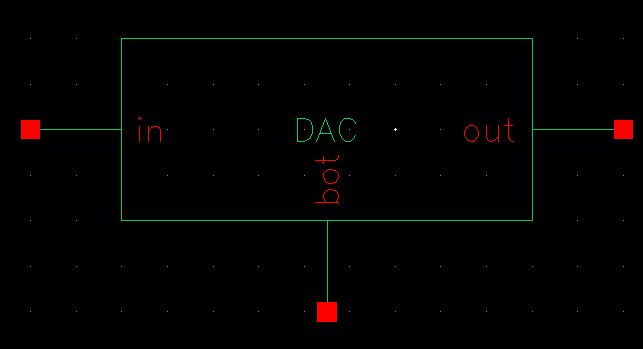

After checking and saving, the circuit is going to be made into a symbol for the convenience of having it as an instance. Go to Create -> Cellview -> From Cellview, draw your symbol and check & save.

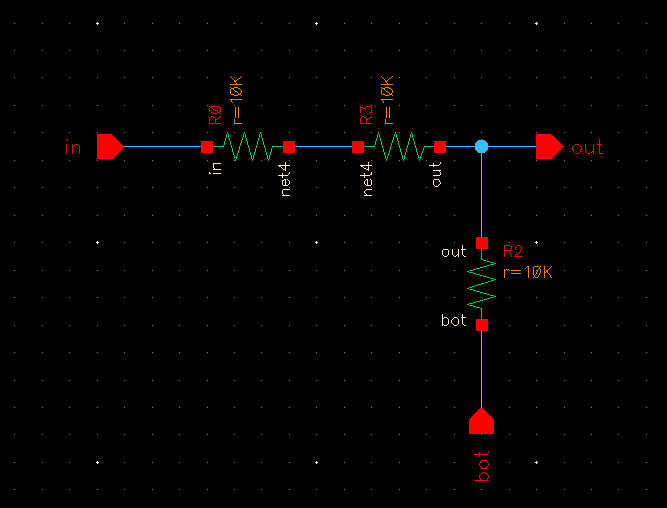

DAC symbol

Then go to lab3, open the copy of the r_div schematic that you finished (with the pins), and delete everything in the cell. Import the symbol and attach a 1v source and wires to in & out then check & save. You will get floating errors, just ignore them so you can check & save.

Launch

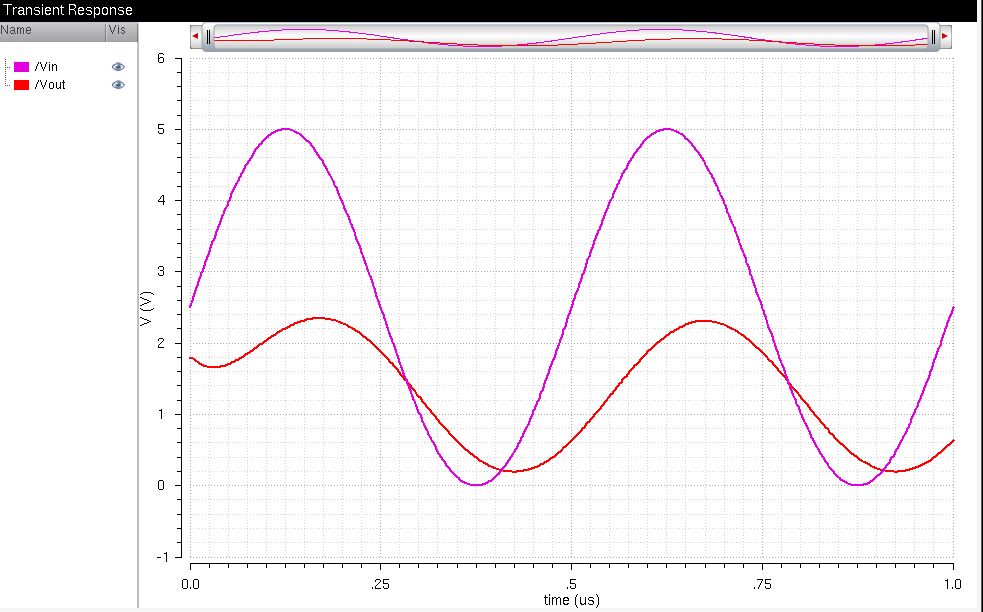

ADE and load the state from cellview and run the transient response.

You should get the same graph from your resistor divider your made in

lab 1.

Save and close out of the copy_R_div.

Now create a new cellview for the layout of our divider. Ensure that all layers are visible (AV) in your layer selection window (LSW) and all select is on (AS).

Next go to Options -> Display (binkey e)

Select pin names in display controls & change display levels from start = 0 to stop = 10

Now we create the shape in our layout. We are going to create a 10k resistor using n-well in layout. The sheet resistance of the n-well in the c5 process is roughly 800ohms. As for the design rules, the min width is 12 lambda (3.6u with lambda being 300nm or .3u). Our resistor width will be 4.5um & our length will be 56 um.

Create a new lout cellview call it R_n_well_10k. Select your nwell material in the LSW & press R to create a rectangle, draw any shape, then click the rectangle & press Q. This will open the rectangle properties where we want to set width to 56 & height to 4.5. Then DRC & save, it will have 4 errors, this is because the edge is not on grid. The rectangle needs to fit on a scale of .15u you can verify with the rule (bindkey k & bindkey shiftkey + k to remove).

Run DRC and you will receive no errors.

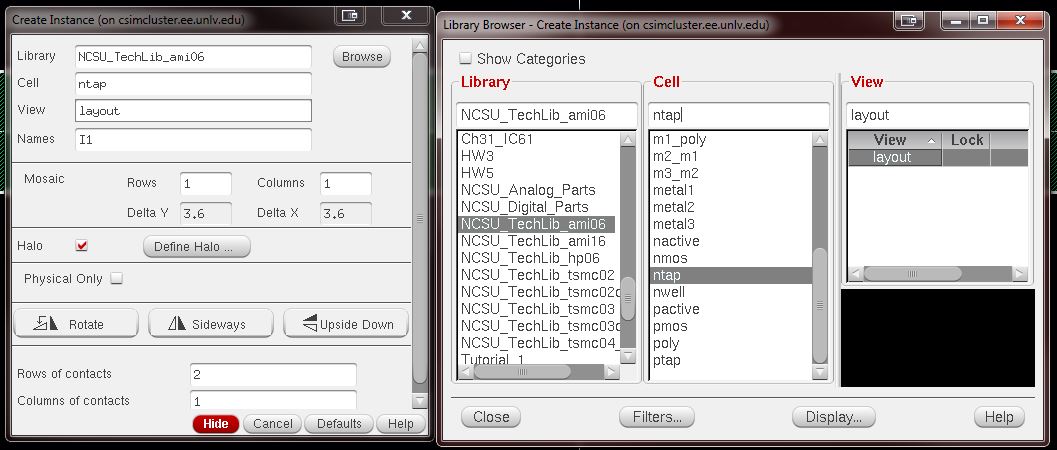

Now to add connections to the end of our n-well resistor. Press i to create an instance and navigate to ntap which is in the NSCU_TechLib_ami06 library.

Make sure you are changing the rows of contact to 2.

Now go to verify -> extract & click OK to find our resistance value.

Go to your library manager & open the extracted view in your R_n_well_10k cell. Zoom in and you will see your resistor's value is 10.21k

Close the extracted view and the layout view of your resistor.

Create a new layout named mydesign_10-bit_DAC_layout

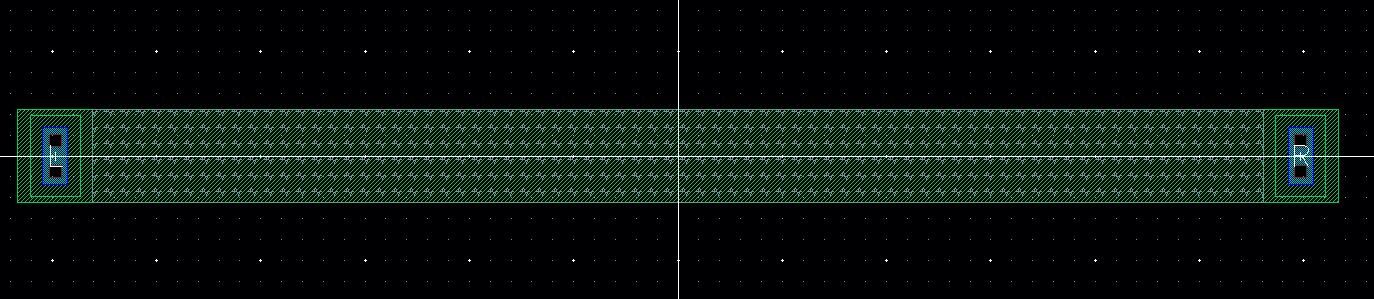

Istantiate two more 10k n-well resistor layouts. DRC your layout & ensure you have enough spacing between your resistors. Draw metal 1 rectangles from each resistor in series & one in parallel between the L of the 2nd resistor & the L of the 3rd resistor to simulate the out of the 1-bit DAC. These three resistors are essentially our 1-bit DAC or 2R-2R divider. Label & draw over the metal 1 rectangle on the top L pin as b0.

1 bit of the layout

If we rearrange the equation looking for L/W = R/Rsq

Where R = 10k ohms and Rsq = 800 ohms

We get the ratio of L/W to be 12.5

Letting us really pick any value of length and width be whatever aslong as the ratio is around 12.5

For our 10k n-well resistor we used 56.1 microns for the length and 4.5 microns for the width which is 56.1/4.5 = 12.4666

Since we used the 10k n-well resistor we created for the 10-bit DAC we already know the measurements of each 10k resistor.

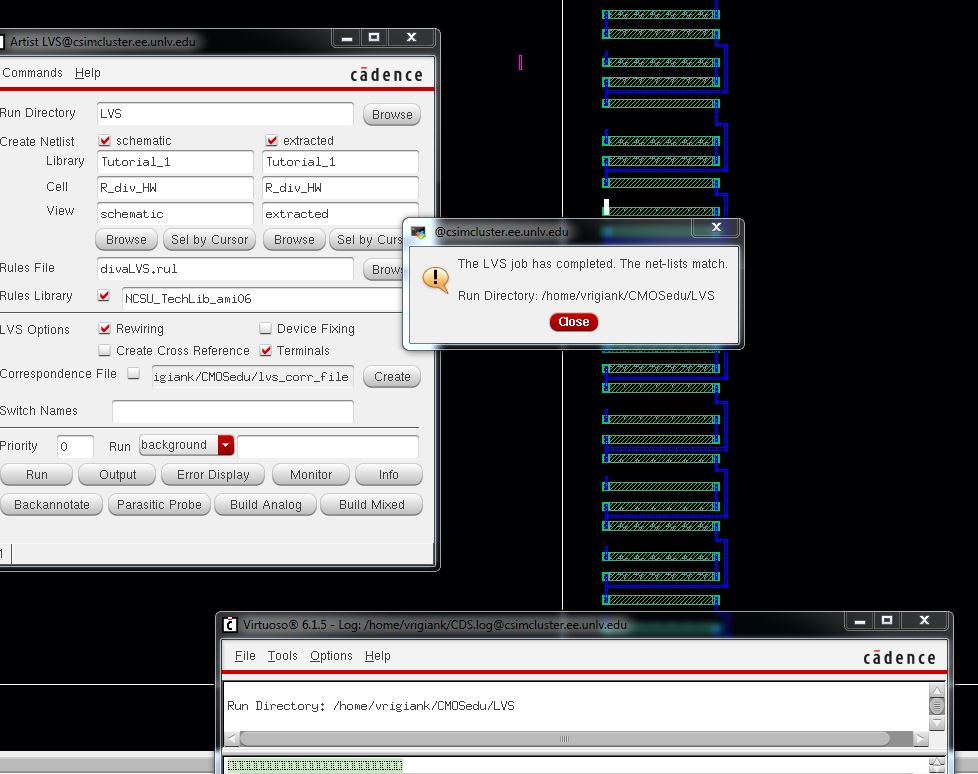

If we edit our simulation options to run the extracted before our simulation we can test & compare our results to our lab 2 DAC. Our results should be and are very similar. You can do this by clicking ADE L -> Setup -> Environment and typing "extracted" before schematic in the box.

ADE L settings

Simulation results of our extracted layout driving the same 10pF capacitor and 10kOhm resistor. Results are the same from lab2

Lab 3 extracted results

Return to EE 421L Labs

Return to EE 421L Labs