Lab 2 - EE 421L Fall 2015

Design of a 10-bit digital-to-analog converter (DAC)

1. Download lab2.zip to your desktop. This contains a simulation example using an ideal 10-bit Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC).

2. Upload this zip file to the design directory on Cadence.

3. Unzip this directory and add, to your

cds.lib in the design directory, the following statement:

4. Once Cadence is running, use the Library Manager and navigate to the lab2 library, then open the schematic view of the cell sim_Ideal_ADC_DAC.

Schematic.

5. Run the simulation (Launch the ADE, Session -> Load State -> Cellview -> OK.

6. Run the simulation.

If the input sinewave execeeds the circuit's limits, in this case 5V, the output will be clipped.

In this case the input was change from 5V to 7V.

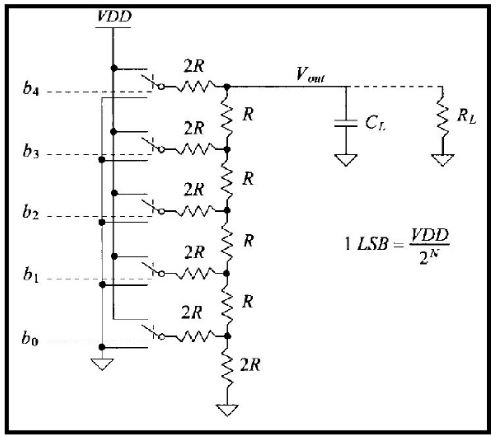

The equation to find the LSB is 1LSB=VDD/(2^n) were n is the number of bits of the DAC. In this example 1LSB= 5V/(2^10)= 4.88 mV.

Post-Lab

In this

lab I'll use n-well resistors to implement a 10-bit DAC.

1. The design is based upon the topology seen in the following figure.

2. The output resitance of the DAC is determine by combining 2R||2R = R, then R + R = 2R and finally we get R for the as seen in the picture:

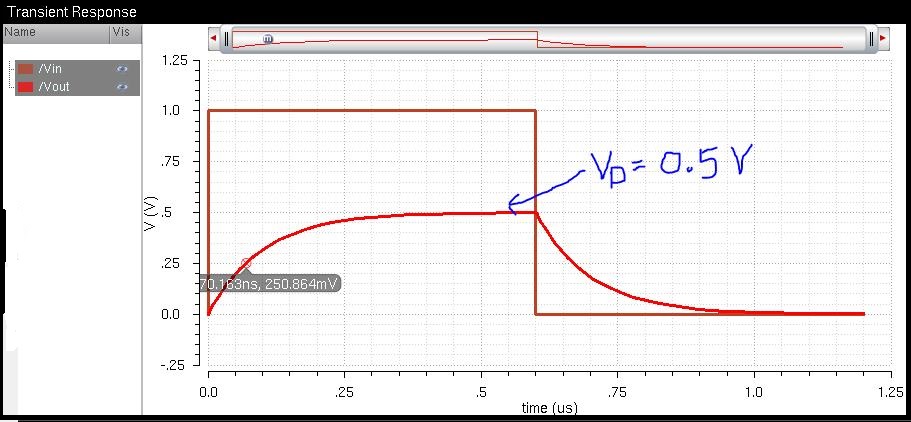

3. Using Td = 0.7*R*C, we can predict the delay of the DAC. Td = 0.7*10k*10p= 70 ns. Since Vp = 1*512/1024 = 500 mV and 50% of Vp is 250 mV.

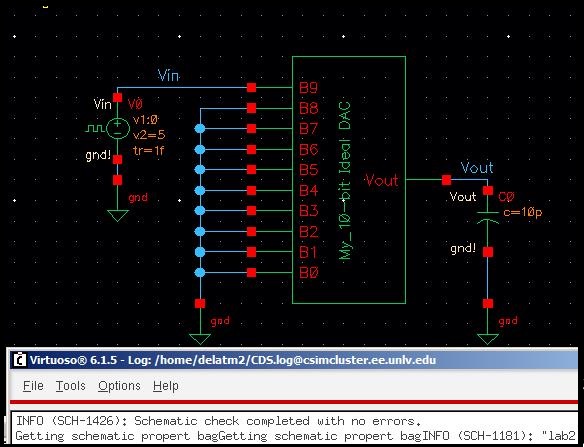

4. To create the a symbol view for the design using the exact same footprint as the Ideal_10-bit_DAC symbol view.

a. A copy of the cell Ideal_DACbit was re-name My_Ideal_DACbit and the shematic was replace with this circuit.

Then a new symbol was created from the circuit

b. Once the DAC bit was created, a copy of the Ideal_10-bit_DAC was made and renamed My_Ideal_10-bit_DAC. By using the DAC bit symbols this circuit was made.

5. Simulations and verification of the circuit. The output was almost identical except for the blue circle on the waveform.

6. Circuit driving different loads.

a. The DAC driving a R load. The output of the DAC is about half of the input because the 10k resistor load is connected in series with the 10k equivalent resistance of the DAC circuit. It is acting like a voltage divider with a ratio of 0.5.

b. With the capacitor the output it's smoother but less amplitude because the capactive reactance (Xc).

c. With the RC load the output is even less because the combination of the copacitor and resistor.

In a real circuit the switches seen above (the outputs of the ADC) are implemented with transistors (MOSFETs). If the resistance of the switches is not small compared to the resistance of the voltage divider circuit, the output voltage of the DAC will be less because there will be a voltage drop across SWres.

Backing up my work.

1. A zip folder will be created Lab2.

2. Then the zipped folder will be store on my google drive.