Lab 1 - EE 421L Fall 2015

Part 1:

Steps to step up Cadence to do DRC, Extract and LVS layouts.

A) In the directory $HOME/ncsu-cdk-1.6.0.beta/lib/NCSU_TechLib_ami06 delete the files divaDRC.rul, divaEXT.rul, and divaLVS.rul.

B) Save diva_rul_files.zip to your desktop.

C) Extract the files in this zip to your desktop.

D) Upload the extracted files (divaDRC.rul, divaEXT.rul, and divaLVS.rul) into $HOME/ncsu-cdk-1.6.0.beta/lib/NCSU_TechLib_ami06 in the deleted files’ places.

The following step

will show how to design and simulate a voltage divider circuit:

1. Open a terminal window and change directories to CMOSedu by typing cd CMOSedu to change the directory then type virtuoso & to start Cadence's Virtuoso.

2. In the Library Manager window, click File -> New -> Library and name it "Tutorial_1". Click on Attach to existing tech library and select "AMI 0.60u C5(3M, 2P, high-res)" from the drop menu, then click OK.

3. In the Library Manager window select the Tutorial_1 libary. Click file, new, and cell view. This will bring up the following window, name the cell R_div then click OK. Now we are ready to build the schematic.

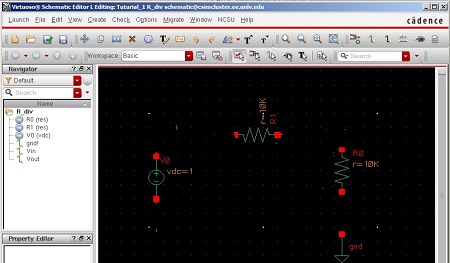

4. On the new window

with the black background press "i" to add the resistors. To

do this you click on "Browse" then Library you select

NCSU_Analog_Parts, then R_L_C, then select "res" and finally enter

the value.

Select the "res" and enter 10k for the value:

Schematic with two resistors.

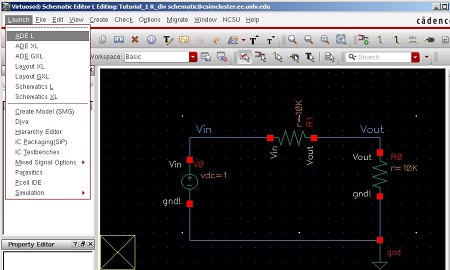

5. Similarly, to add the ground and power supply:

6. Add wires by pressing "w" and label the input and output nodes by pressing "L" lower case and then click "check and save" button.

Now we are ready to simulate the circuit.

7. Click Launch, and ADE L.

8. On the Virtuoso Analog Design Environment (ADE) window go to Analyses -> Choose and select a transient analysis (tran), a stop time of 1 second, and Enabled as seen below.

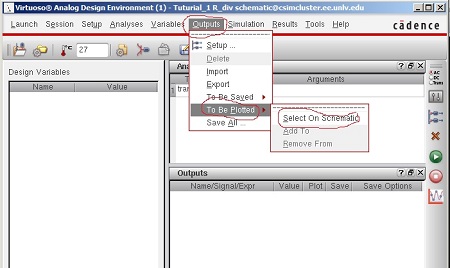

9. Next select the signals we want to plot. Click on Outputs -> To Be Plotted -> Select On Schematic.

10. Select the points on the schematic.

11. Click Run.

12. Verify output and done.

Sample of a table

Part 2:

Procedure on how to backup my work.

1. A zip folder will be created labX.

2. Then the zipped folder will be store on my google drive.