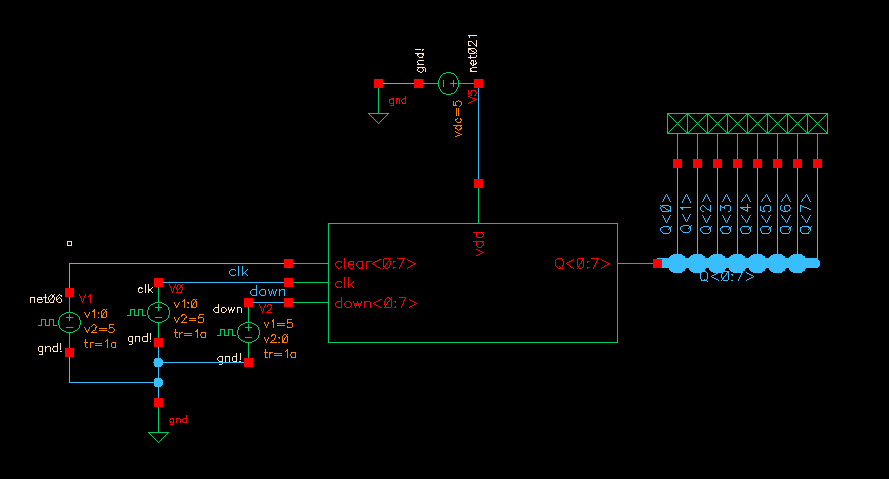

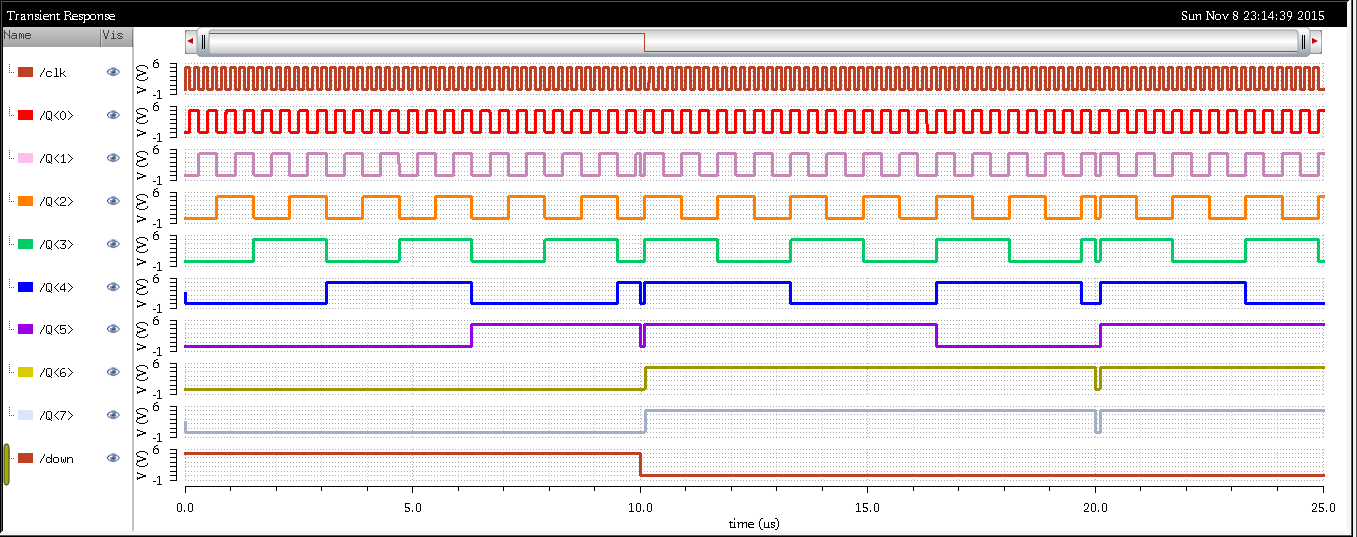

- Design of an 8-bit resettable (input "clear") up/down counter

- 8 Bit Counter:

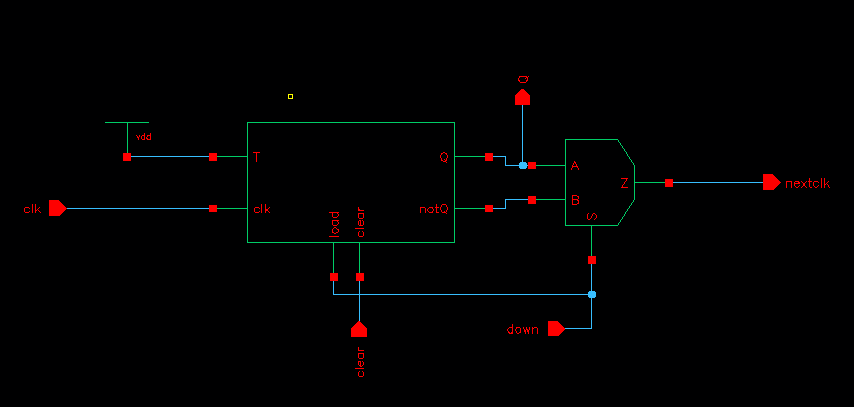

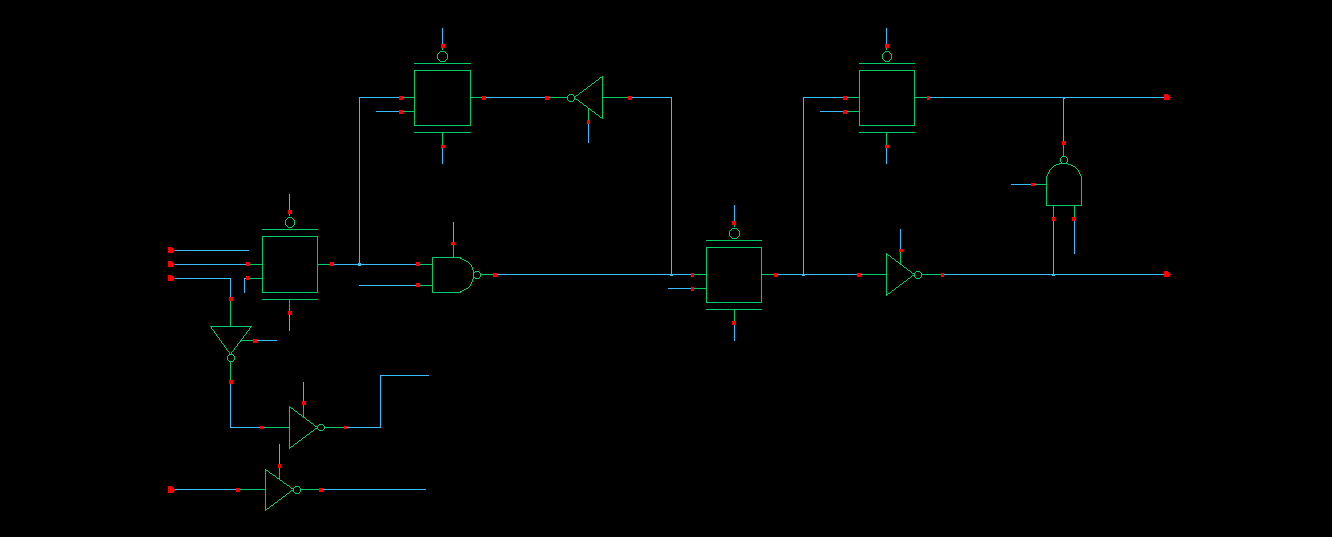

- 1 Bit Counter:

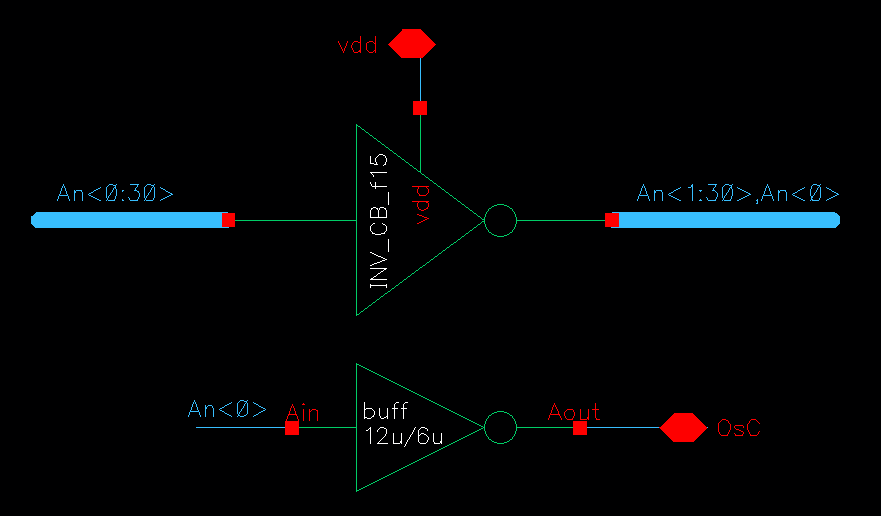

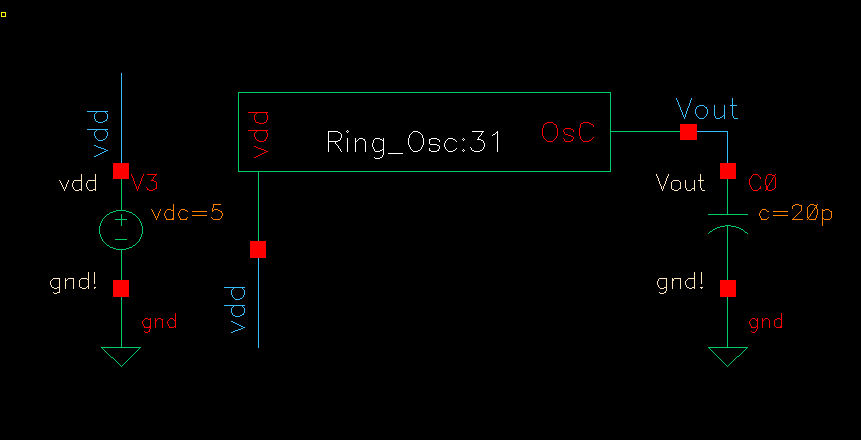

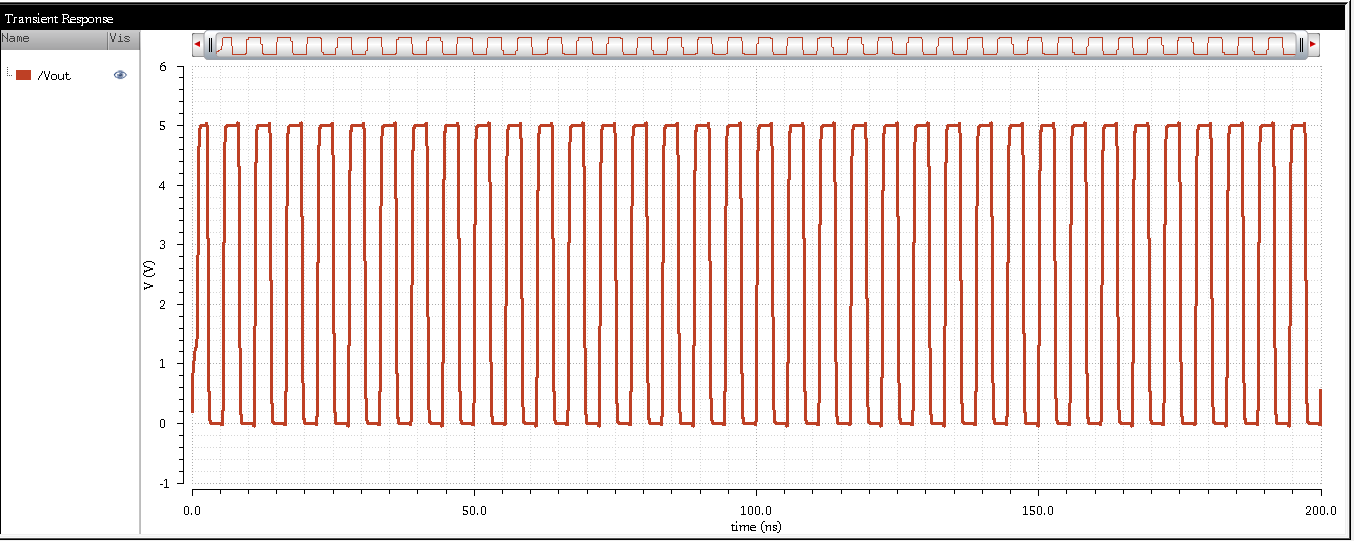

- A 31-stage ring oscillator with a buffer for driving a 20 pF off-chip load

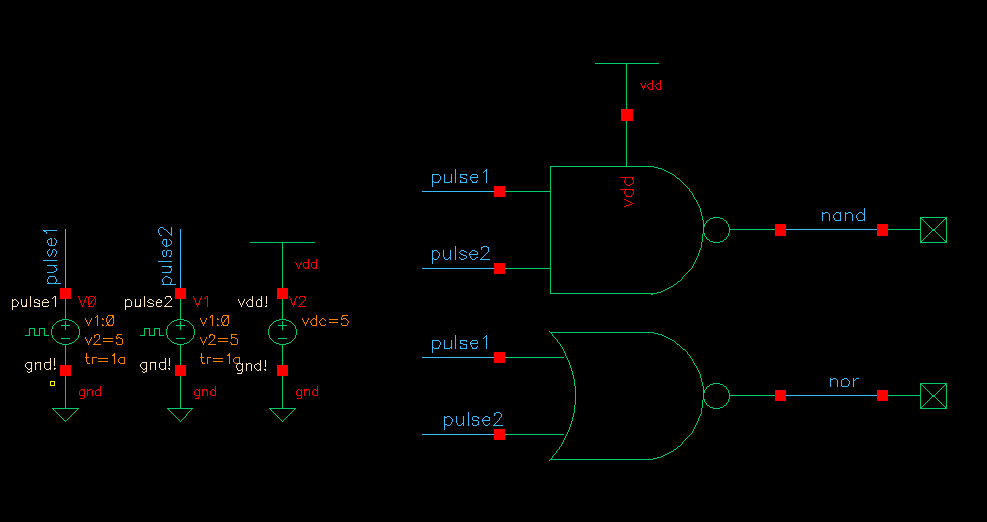

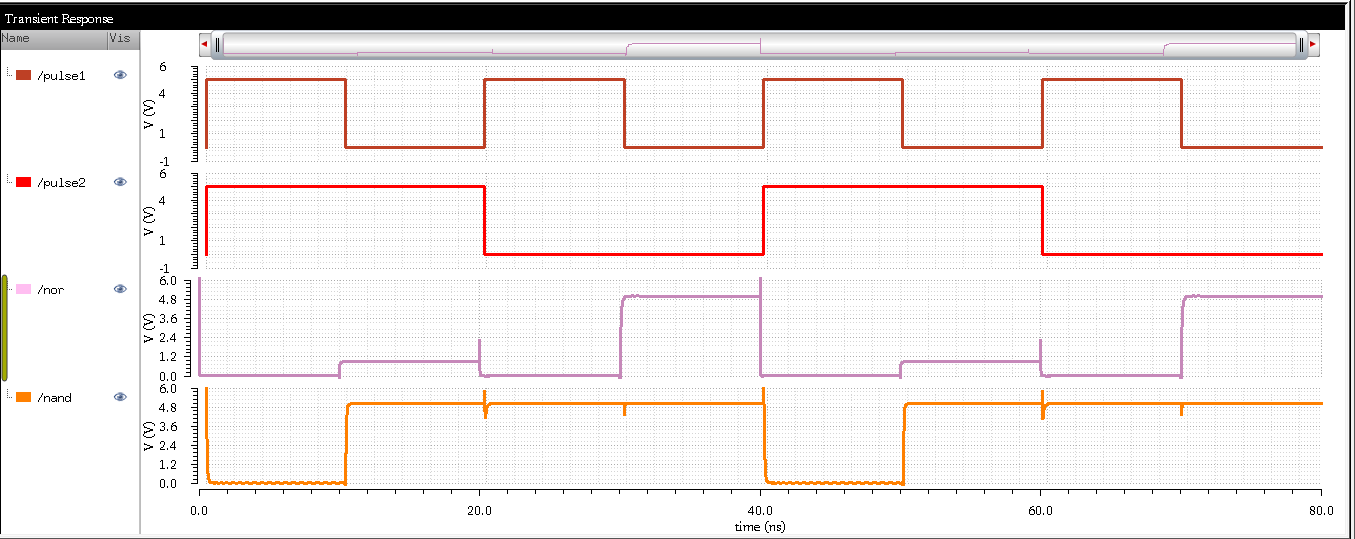

- NAND and NOR gates using 6/0.6 NMOSs and PMOSs

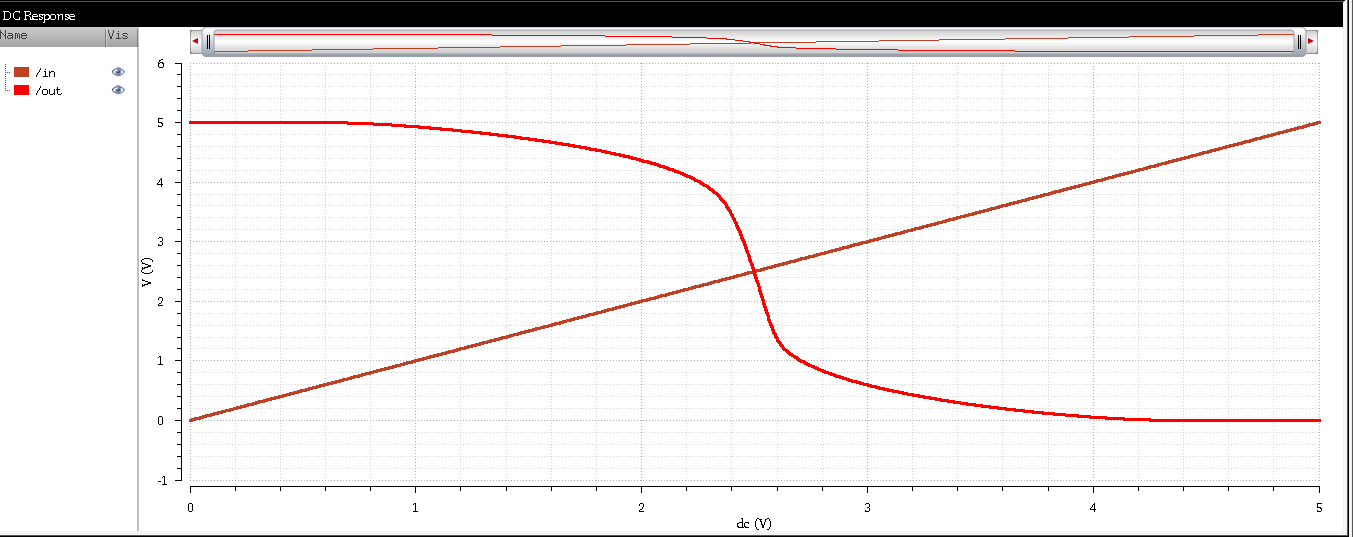

- An inverter made with a 6/0.6 NMOS and a 12/0.6 PMOS

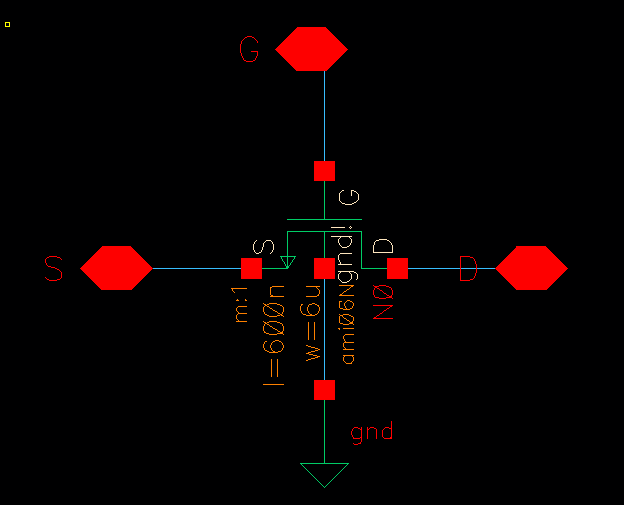

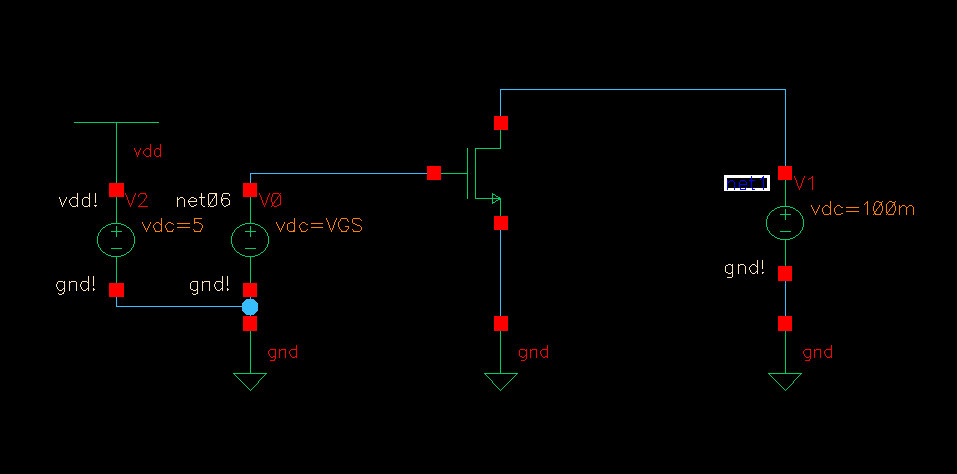

- Transistors, both PMOS and NMOS, measuring 6u/0.6u where all 4 terminals of each device are connected to bond pads

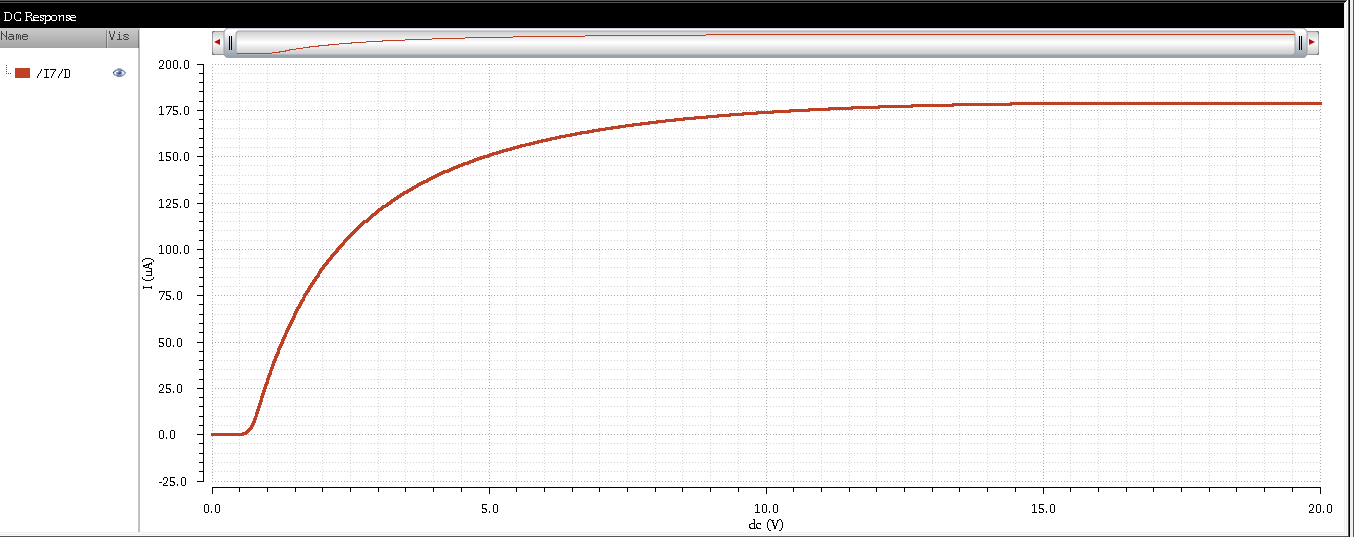

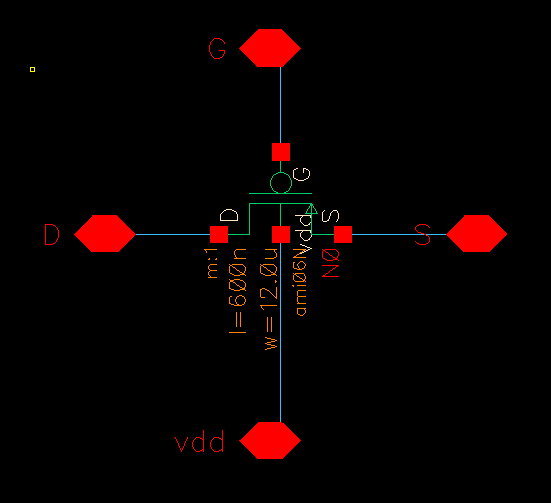

- NMOS:

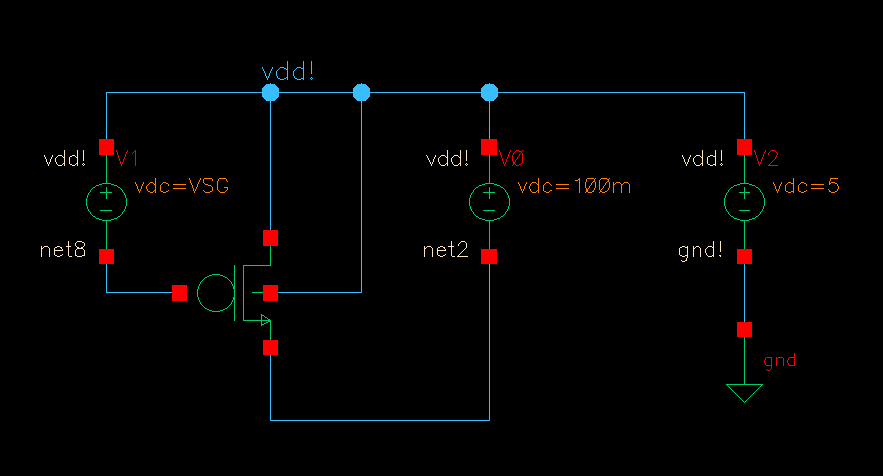

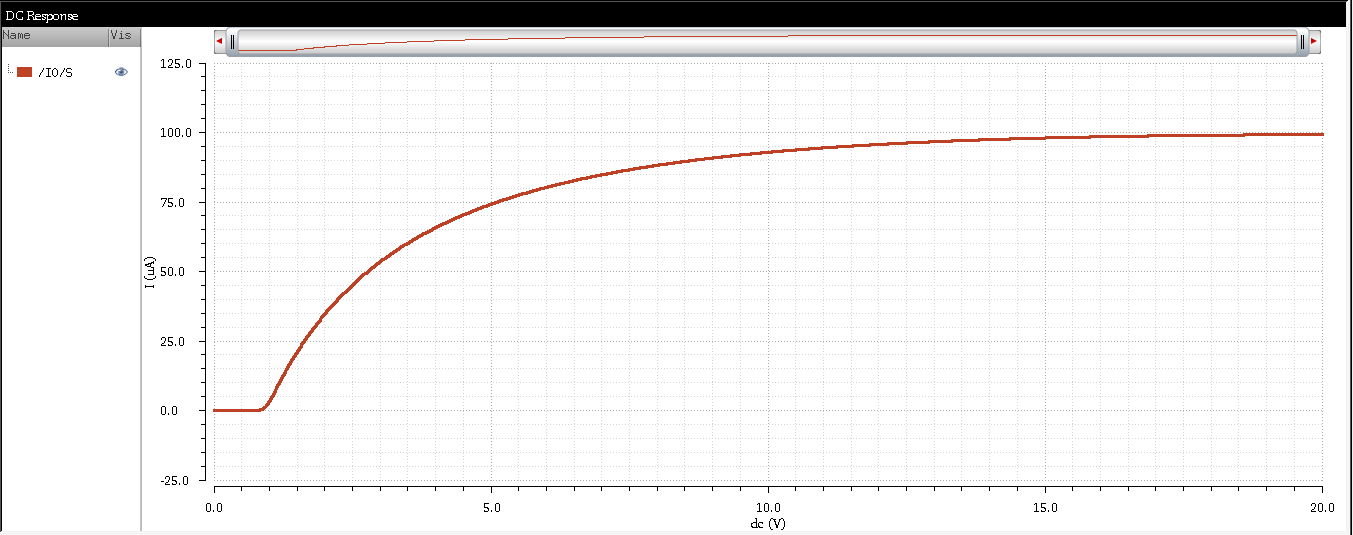

- PMOS:

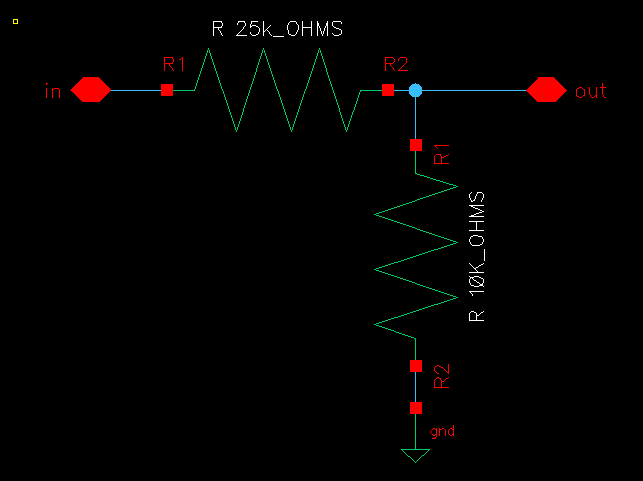

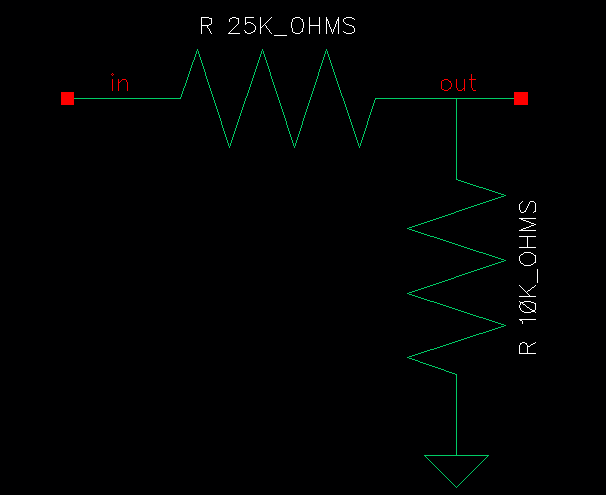

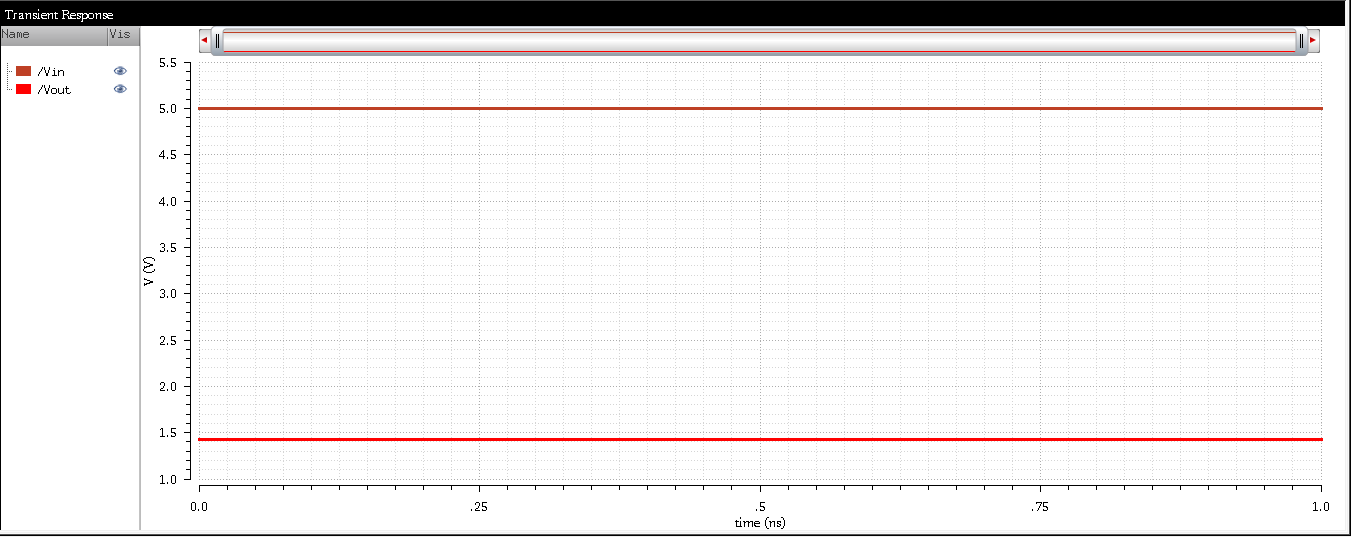

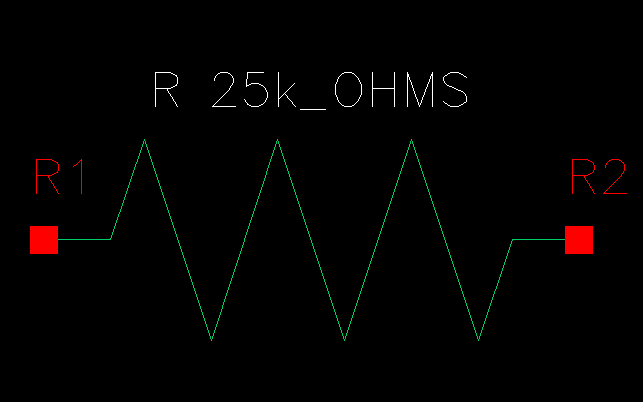

- Using the 25k resistor laid out below and a 10k resistor implement a voltage divider

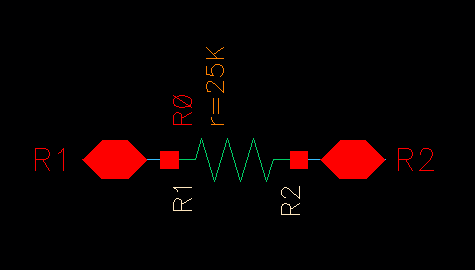

- A 25k resistor implemented using the n-well

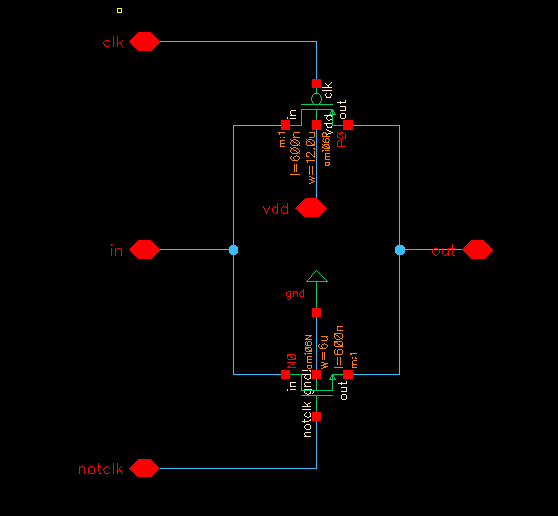

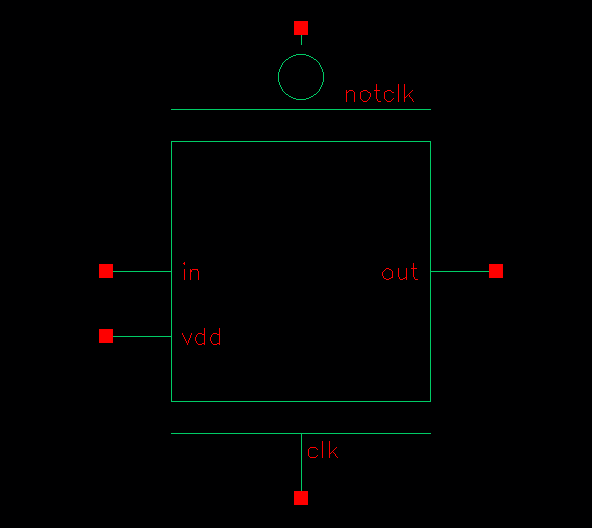

- Transmission Gate

Above is a schematic that was used to simulate the functionality of the up/down counter. At 10us the counter clears and switches from counting up to counting down.

To the left is a schematic of a one bit counter. To the right is the implementation of a D-Flip-Flop.

Above are the schematics that correspond to the ring oscillator along with a simulation

Here are example runs of a NAND and NOR gate created with 6u/.6u MOSFETS.

Above is a schematic and a simulation of an ideal inverter. Notice how the switching point value is measure directly at 2.5 V.

Above are the schematics and the correspnding simulation of the NMOS transistor with a 6u/.6u width and length.

Above are the schematics and the correspnding simulation of the PMOS transistor with a 6u/.6u width and length.

Above is the voltage divider schematic, symbol, and simulation. Notice how the output voltage is a ratio of the input voltage that is determined by the values of the two resistors.

Here is the symbol and schematic of the 25k resistor

Above is the schematic of the transmission gate and also the corresponding symbols. The transmission gate allows us to pass distinguishable logic highs and logic lows.

Click the link below to download the project files

project files