Lab 6 - EE 421L

Design, layout, and simulation of a CMOS NAND gate, XOR gate, and Full-Adder

The objective of this lab is create shematics, layouts and simulations of a NAND, XOR and Full-Adder.

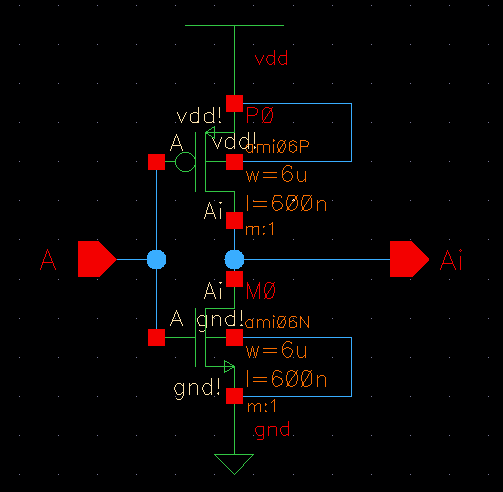

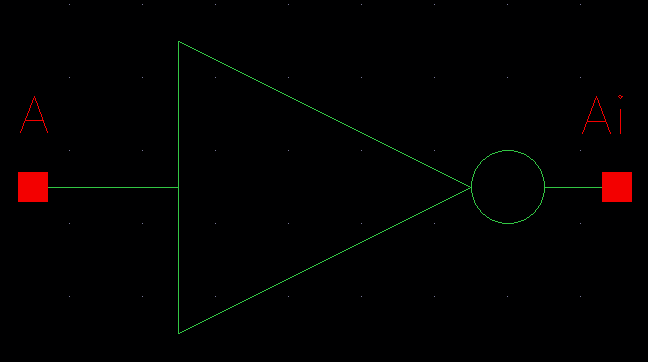

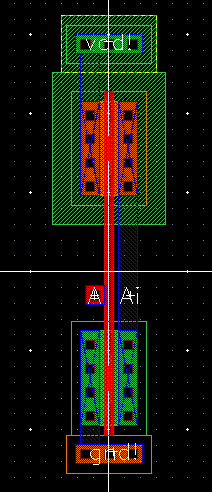

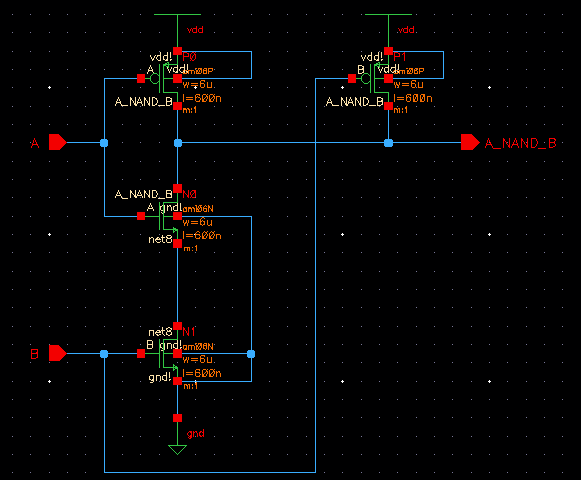

| Logic Gate | Schematic |

Symbol |

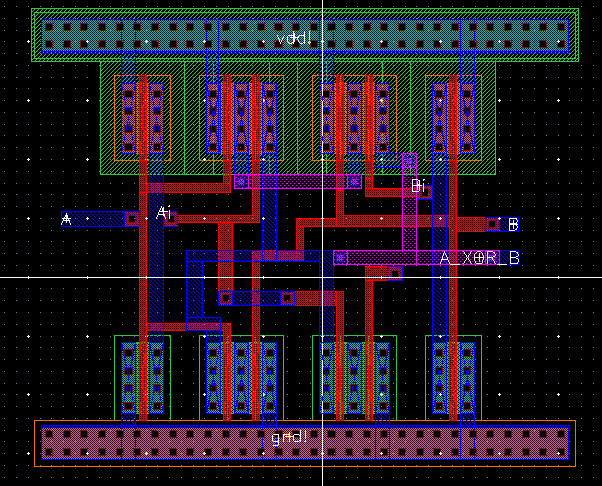

Layout |

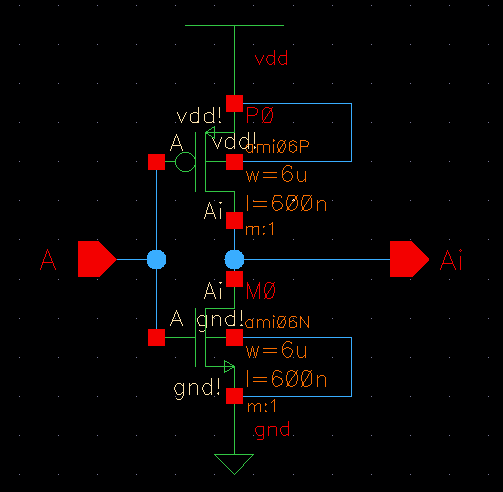

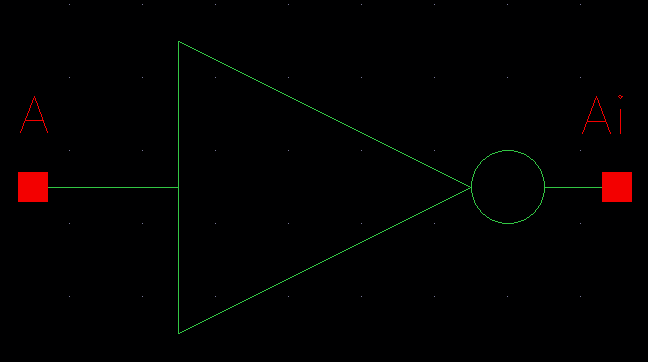

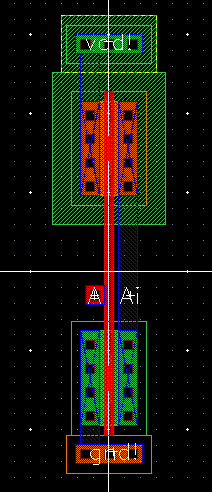

| Inverter |

|

|

|

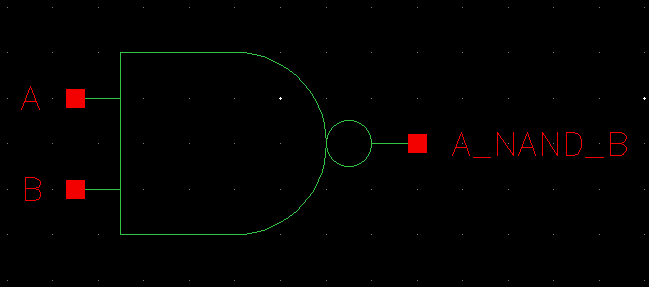

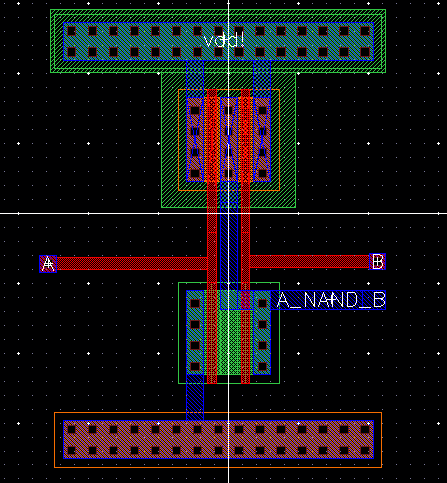

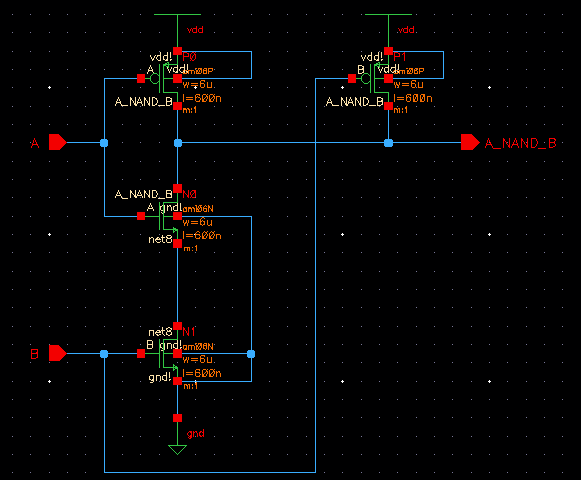

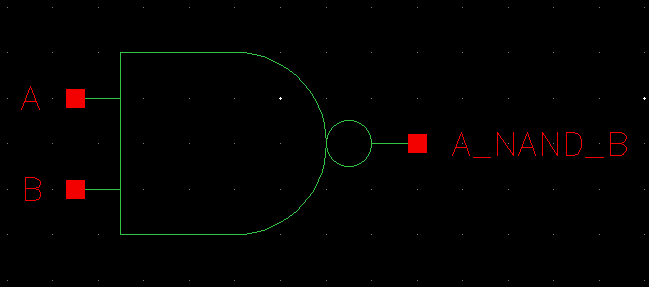

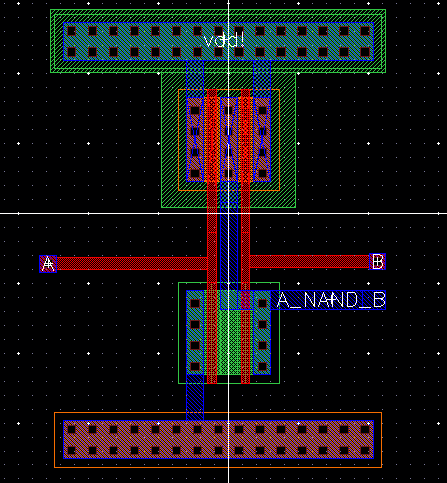

| Nand |

|

|

|

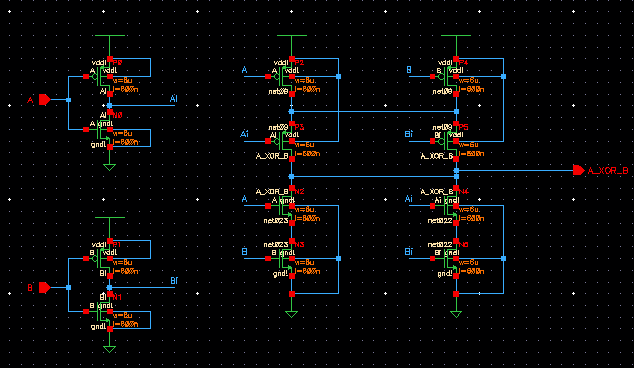

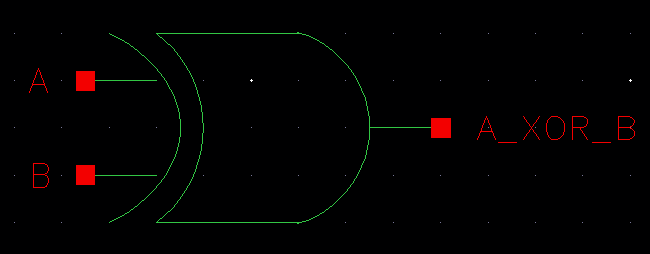

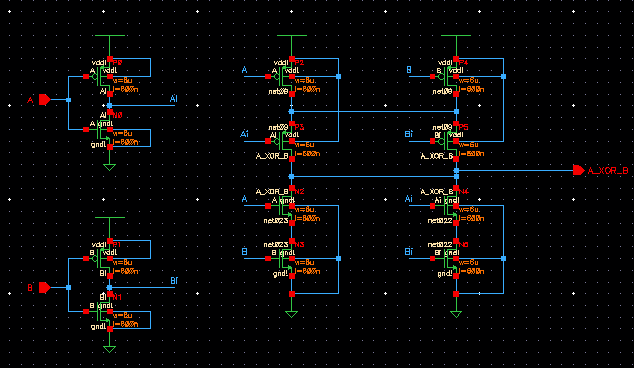

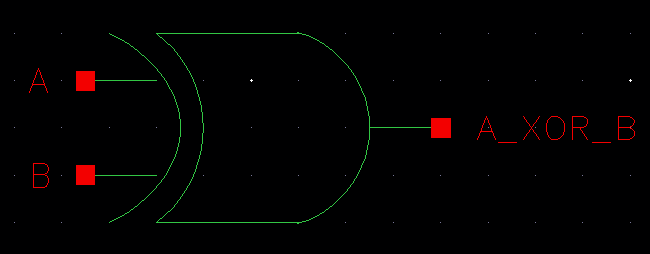

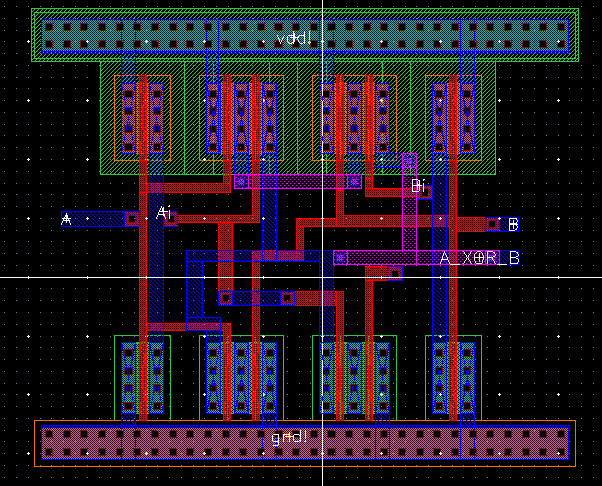

| Xor |

|

|

|

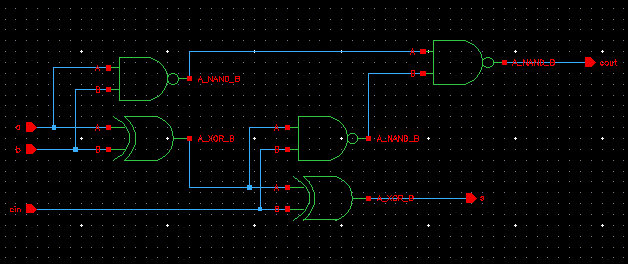

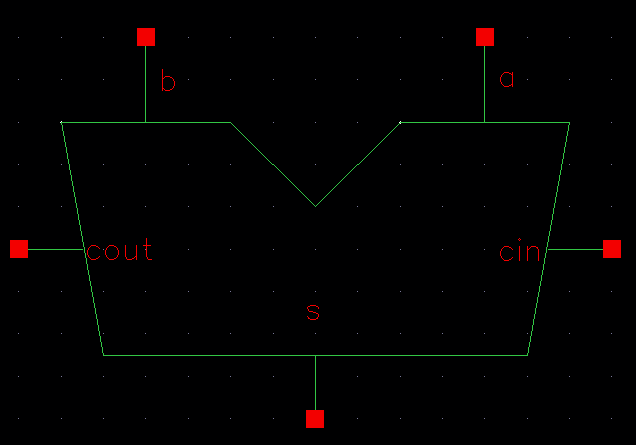

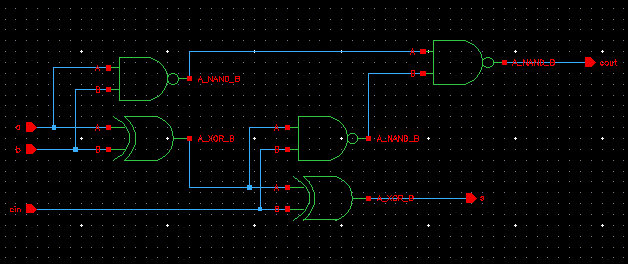

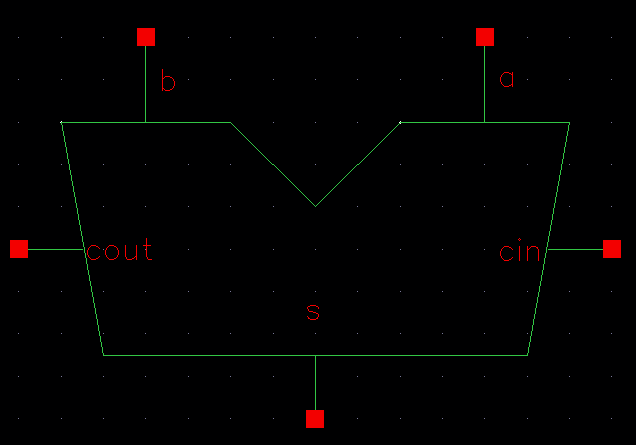

| Full-Adder |

|

|

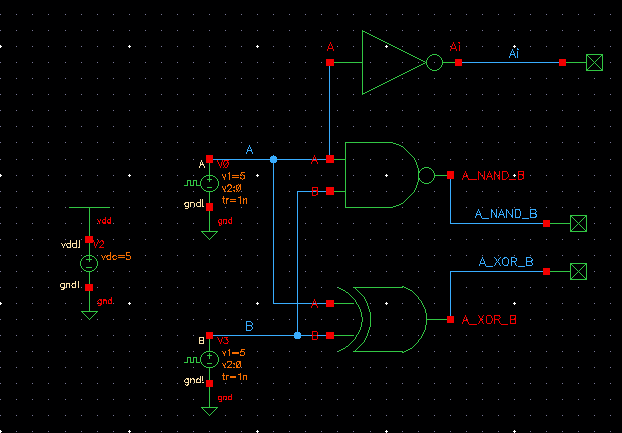

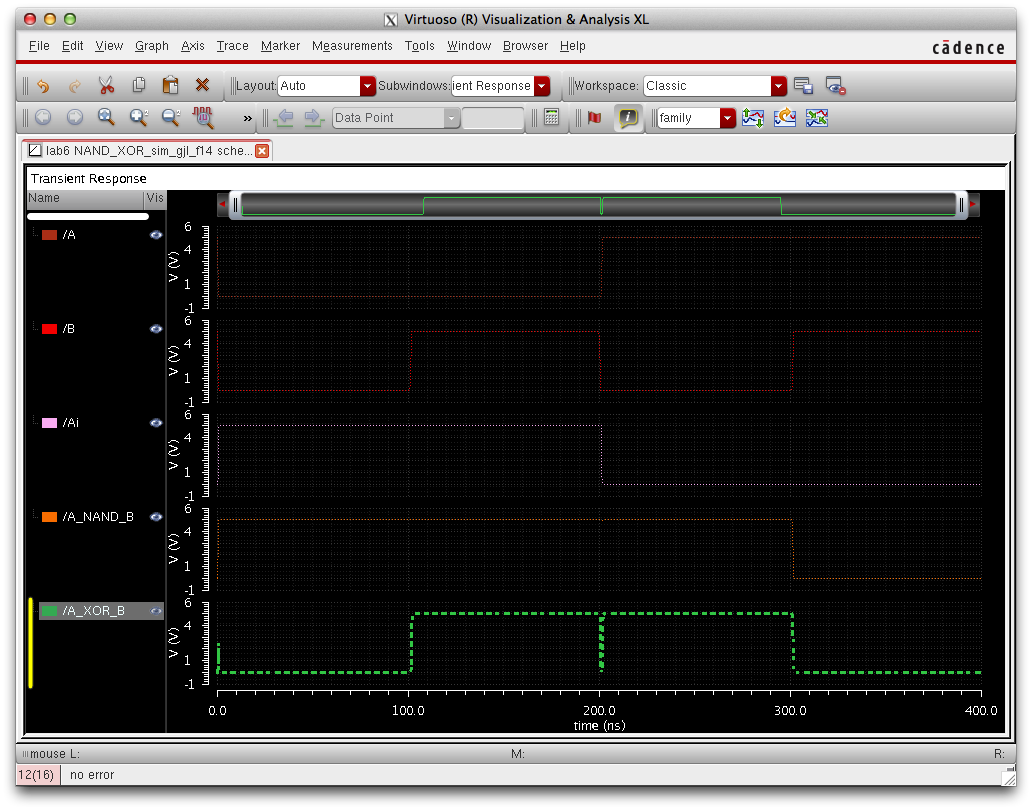

Simulating the Gates

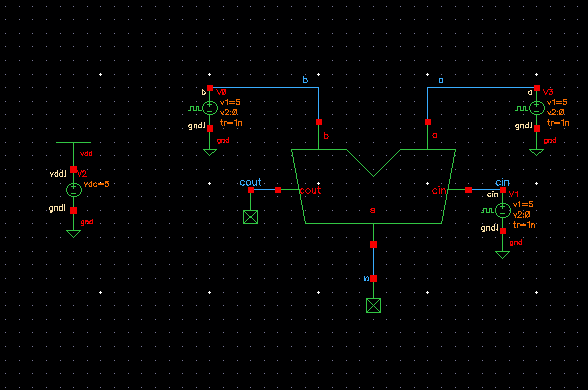

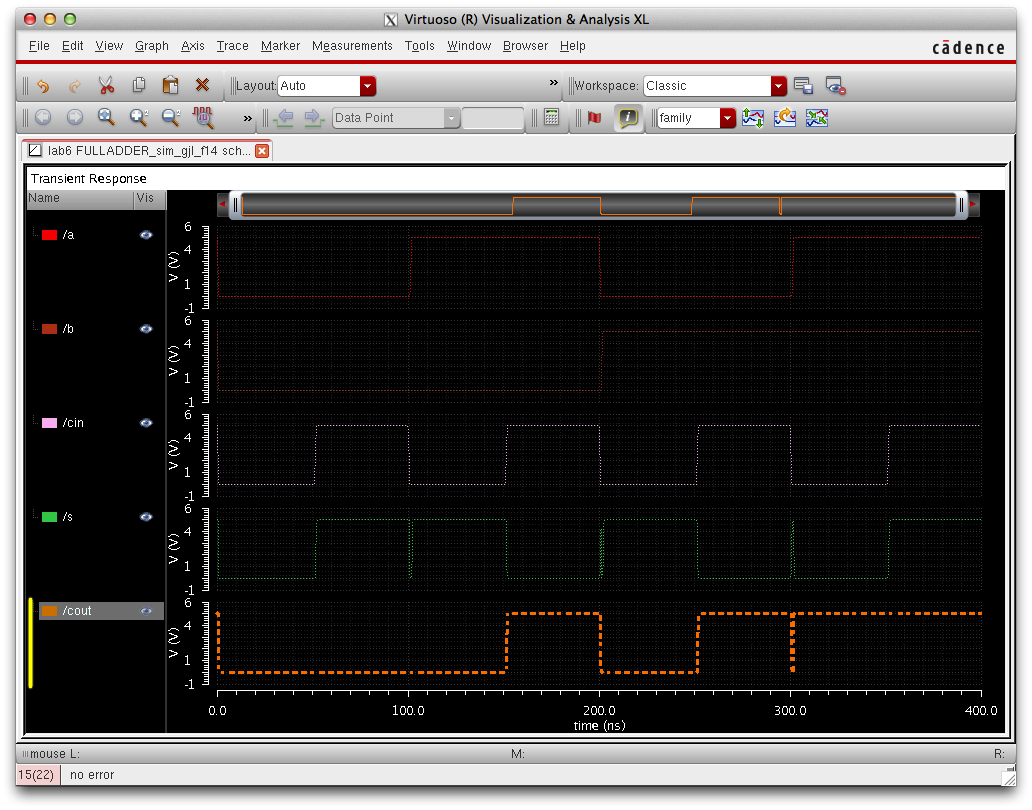

Simulating the Full-Adder

Here

are the simulations for the full adder, notice the blips due to the

timing delay of our signals this is due to the rise and fall time of

the input signal.

Back-Up shown below.

Design Files can be found here.