Project - ECE 421L

Authored

by Matt Mumm, mummm2@unlv.nevada.edu

November 22, 2013

Lab

description

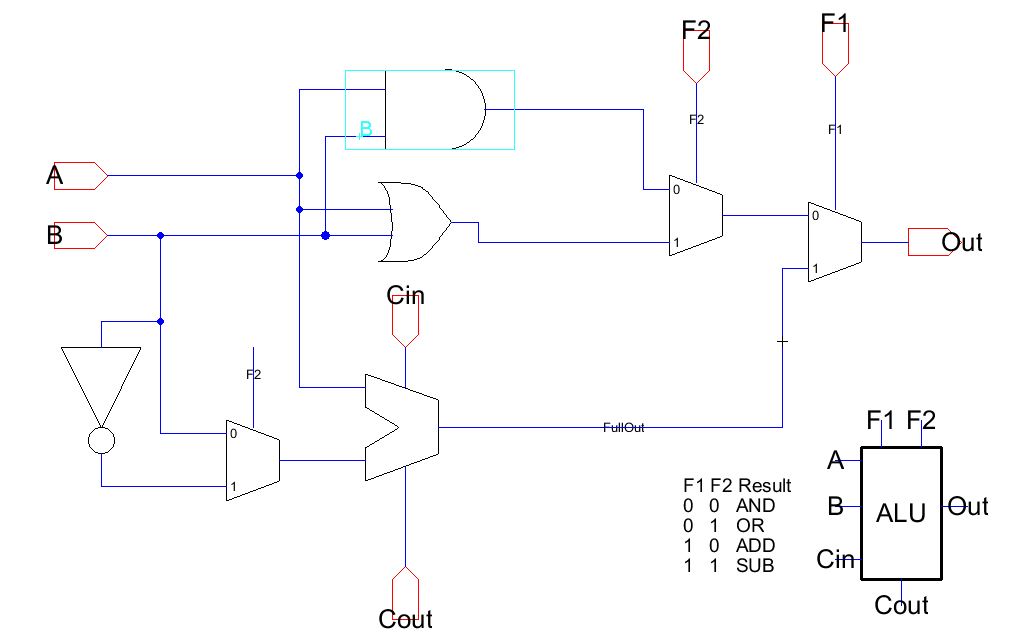

For this project I will be creating a 8 input ALU that can AND, OR, ADD and SUBTRACT.

The first part of this is to figure out how I can do all 4 functions at the same time and only select one of the results.

So I need 3 different gates. AND, OR and Full Adder.

Subtraction is just addition of the negative value. A-B = A+(-B) This is where 2's compliment comes into use. In

order to subtract a value in binary, we invert the second number and

then add 1. So using the full adder, we can invert B and then set

the carry in value as 1.

With

the 4 functions figured out, I now need to be able to select anyone of

them. With 4 options, I will need 2 control bits (F1 and F2).

| F1 | F2 | Result |

| 0 | 0 | AND |

| 0 | 1 | OR |

| 1 | 0 | ADD |

| 1 | 1 | SUB |

Using

2 muxs in series I can select my inputs/outputs. F2 will control

my first selection AND or OR. F2 will also be the control bit if

I want to invert the input for B into my full adder and if 1 gets added

or not.

F1 will control the final output between AND/OR and full adder.

Below is my schematic for a 2 input ALU.

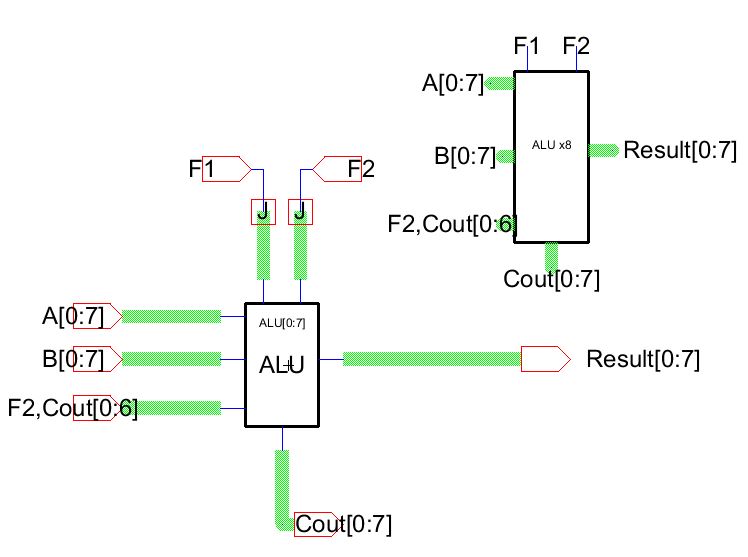

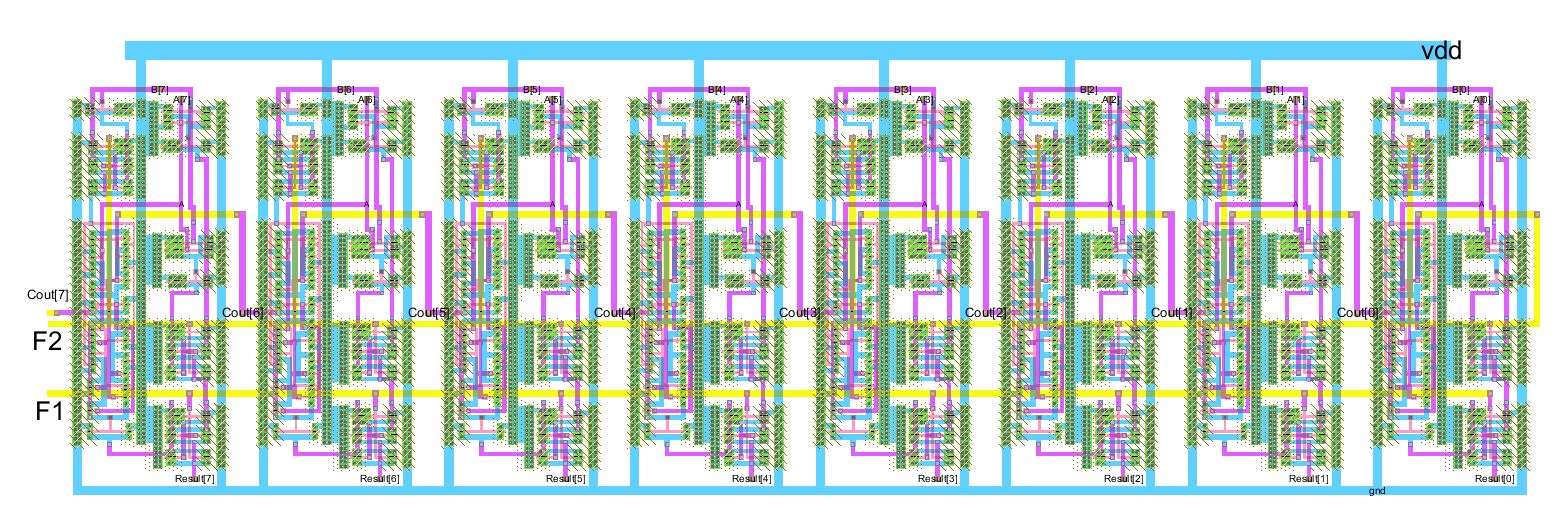

Now that I have that, I can just cascade the 2 input ALUs eight times to get an 8 input ALU.

Notice on the Carry ins, the first is from F2 (for the subtract feature) and the rest are from the previous carry outs.

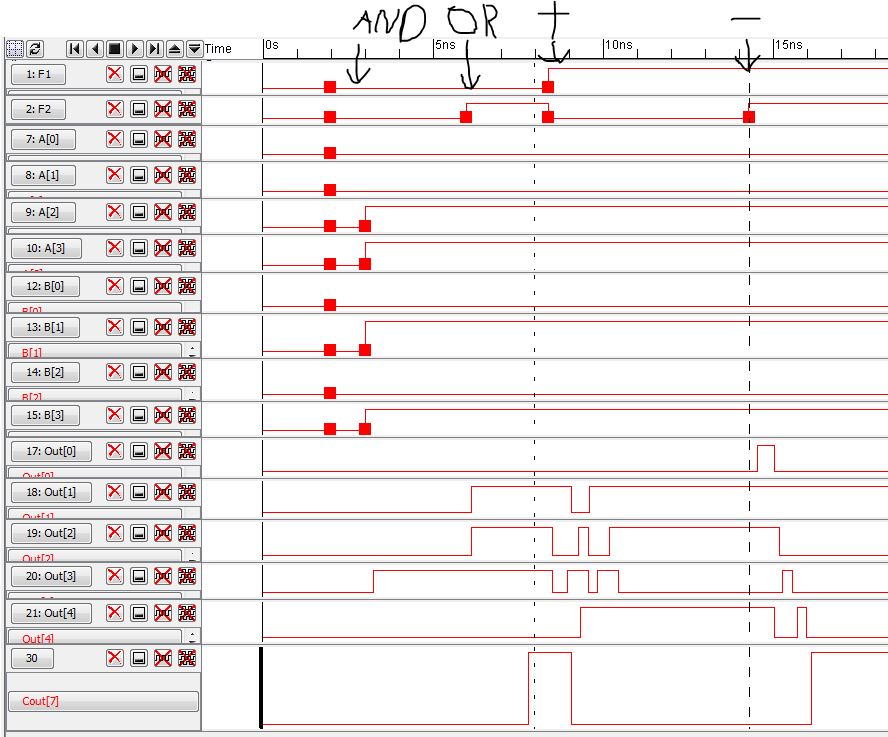

A[7:0]=0000 1100 (12)

B[7:0]=0000 1010 (10)

Bi[7:0]=1111 0110 (+246,-10)

| A and B | A or B | A + B | A - B |

| 0000 1000 | 0000 1110 | 0001 0110 (22) | 0000 0010 (2) |

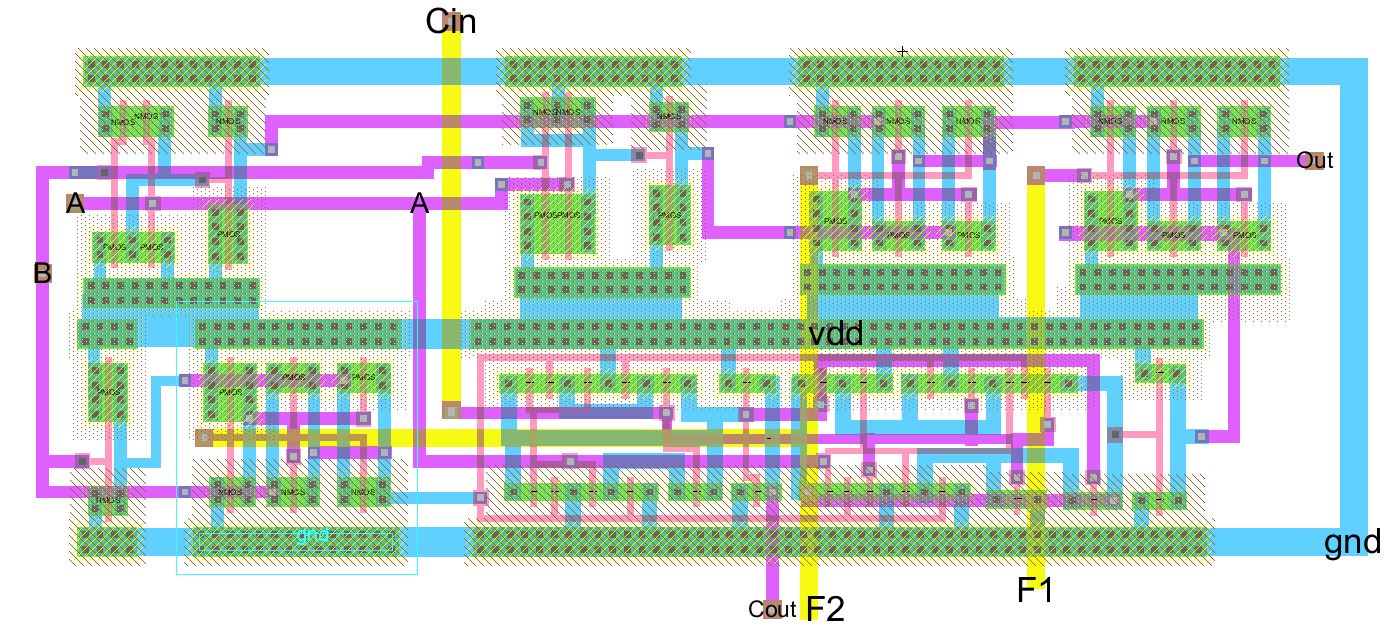

This is my layout for a 1 bit ALU.

This is my layout for a 1 bit ALU.

Now I can cascade my 1 bit ALUs together to get an 8bit ALU.

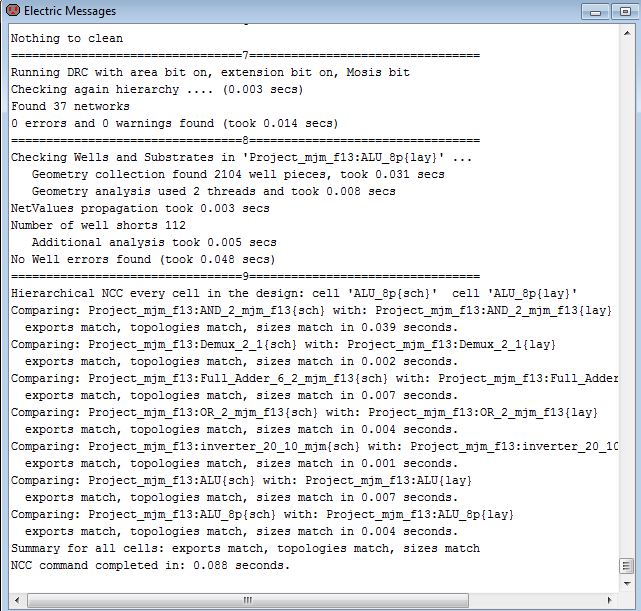

Finally I check for errors:

Be sure to backup your files.

My library file can be found here

More information can be found at cmosedu.com