Project

Report -

ECE 421L

Authored

by Stryder Loveday

loveday3@unlv.nevada.edu

November

08, 2013

In this project, we will

combine our components to form an 8-bit ALU. This ALU will be

8-bit, able to perform the AND, OR, Add, and Subtract commands.

First,

to avoid clutter, we will perform a cross-library copy and move only

the related files to a new library for use with the project. To

begin go to Cell -> Cross Library Copy.

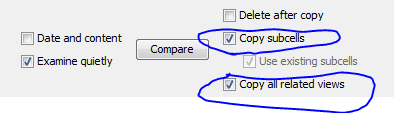

Remember to copy all related views and sub-cells. Include all cells for all components of the project.

Design/Schematic

The schematic for the ALU is seen below.

For

our testing, we set our A input to A=0x03. We set out B input to

B=0x07. Our F signal determines the output of our MUX, selecting

one of our four operations.

As a summary of our results:

| Inputs | F = 00 (ADD) | F = 01 (AND) | F = 10 (SUBTRACT) | F = 11 (OR) |

A = 0x03

B = 0x07 | 0x0A

Decimal 10 | 0x03

Decimal 3 | 0xFC

Decimal 252

Two's Compliment: -4 | 0x07

Decimal 7 |

Remember to back up all work, and keep a record of versions and changes for future reference.

A

link to my .jelib file is located here. A link to the testing vectors for IRSIM can be found here. Note that the simulation window will need to be zoomed out to see all results.

Note: Due to an unknown

issue, the .jelib for the project still references my original file

containing the majority of my work. I have uploaded that as well here. This will be removed once the issue has been resolved.

Layout

Now that we have designed our ALU, we will create the layout for the device itself.

To

keep things organized in such a large design, we will want to use a

standard form for our logic and keep everything lined up and organized.

In industry, space is money and designs are made as compact as

possible, but for learning design the standard cell method is an

excellent place to start.

To begin, here are the basic 1-bit components used in the layout.

OR gate (NOR + Inverter)

AND gate (NAND + Inverter)

XOR gate

Full Adder:

MUX(incomplete rework)

To

begin, we will lay out our logic components for a 1-bit device.

One general rule to keep in mind, is to keep things organized and

follow a pattern that will help keep the circuit clean. For

example, one common practice is to have metal1 and metal2 only run in

one direction each, being perpendicular to eachother. Doing this

keeps them from overlapping, and helps keep the modular setup of the

cells in order.

Once the devices for a single bit ALU are laid out, we can parallel and connect 8 together for form our 8-bit ALU.

This

concludes the final project for EE 421. Please direct

any comments or suggestions to Stryder Loveday, at the e-mail address

listed above.

Return

to EE 421L Labs