EE 421L Project

Electric

library: ML_ee421L_f13_Project.jelib

IRSIM

input vector: ML_ee421L_f13_Project_8_bit_ALU.cmd

-----

-------

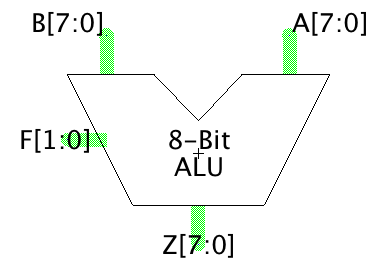

00

A AND B

01

A OR B

10

A + B

11

A -

B

Simulate ALU Schematic with IRSIM

Input vector for IRSIM: ML_ee421L_f13_Project_8_bit_ALU.cmd

Let A = 010111012 = 9310 = 0x5D (hex)

B = 010010112 = 7510

= 0x4B (hex)

F[1:0] = 00 (AND):

Z = A

AND B = 010010012 = 0x49 (hex)

F[1:0] = 01 (OR):

Z = A OR B = 010111112

= 0x5F (hex)

F[1:0] = 10 (Addtition):

Z = A + B = 93 + 75 = 168 = 0xA8 (hex)

F[1:0] = 11 (Subtraction): Z = A

- B = 93 - 75 = 18 = 0x12 (hex)

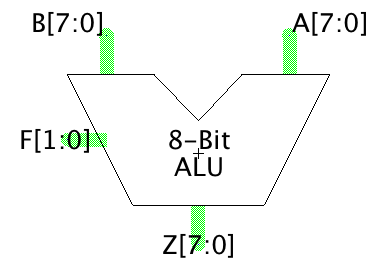

Layout

Simluate ALU Layout with IRSIM

Input vector for IRSIM: ML_ee421L_f13_Project_8_bit_ALU.cmd

Layout simulation uses the same input vector file.

Let A = 010111012 = 9310 = 0x5D (hex)

B = 010010112 = 7510

= 0x4B (hex)

F[1:0] = 00 (AND):

Z = A

AND B = 010010012 = 0x49 (hex)

F[1:0] = 01 (OR): Z = A OR B = 010111112 = 0x5F (hex)

F[1:0] = 10 (Addtition):

Z = A + B = 93 + 75 = 168 = 0xA8 (hex)

F[1:0] = 11 (Subtraction): Z = A - B = 93 - 75 = 18 = 0x12 (hex)

Result

matches that of the ALU schematic and is correct.

Backup your files