Lab 8 - EE 420L

Engineering Electronics II

Author:

Matthew Meza

Email:

mezam11@unlv.nevada.edu

March

20th, 2015

Characterization

of the CD4007 CMOS transistor array

Pre-lab work

- Review the datasheet for the CD4007.pdf CMOS transistor array.

- Ensure that you

understand how the bodies of the NMOS are tied to pin 7 (VSS, generally

the lowest potential in the circuit, say ground) and that the bodies of

the PMOS are tied to pin 14 (VDD, generally the highest potential in

the circuit, say + 5V).

Lab Description

In

this lab you will characterize the transistors in the CD4007 and

generate SPICE Level=1 models. Assume that the MOSFETs will be used in

the design of circuits powered by a single +5 V power supply. In other

words, don't characterize the devices at higher than +5 V voltages or

lower than ground potential.

- Experimentally

generate, for the NMOS device, plots of:

- ID v. VGS (0 < VGS < 3 V) with VDS = 3 V

- ID v. VDS (0 < VDS < 5 V) for VGS varying from 1 to 5 V

in 1 V steps, and

- ID v. VGS (0 < VGS < 5 V) with VDS = 5 V for VSB varying

from 0 to 3 V in 1 V steps.

- Note that for this

last one, if VSS (NMOS body) is ground (again, the Body, VB, is

grounded) then the source voltage will be varied from 0 to 3 V in 1 V

steps to realize VSB ( = VS - VB = VS) varying from 0 to 3 V in 1 V

steps. At the same time VGS will be varied from 0 to 3 V (when VS = 0),

1 to 4 V (when VS = 1 V), 2 to 5 V (when VS = 2 V), and 3 to 5 V

(when VS = 3 V). In other words, as VS is increased by 1 V the VGS has

to shift up by 1 V as well.

- Assuming that the

length of the NMOS is 5 um and its width is 500 um calculate the

oxide thickness if Cox (= C'ox*W*L) = 5 pF.

- From this measured

data create a Level = 1 MOSFET model with (only) parameters: VTO,

GAMMA, KP, and TOX.

- Compare the

experimentally measured data above (the 3 plots) to LTspice-generated

data (again, 3 plots) and adjust your model accordingly to get better

matching.

- Experimentally,

similar to what is seen on the datasheet (AC test circuits seen on page

3 of the datasheet), measure the delay of an inverter using these

devices (remember the loading of the scope probe is around 15 pF and

there is other stray capacitance, say another 10 pF).

- Using your model

simulate the delay of the inverter and compare to measured results.

Adjust your SPICE model to get better matching between the experimental

data and the measured data.

- Repeat the above

steps for the PMOS device where VDS, VGS, and VSB are replaced with

VSD, VSG, and VBS respectively.

Lab Data

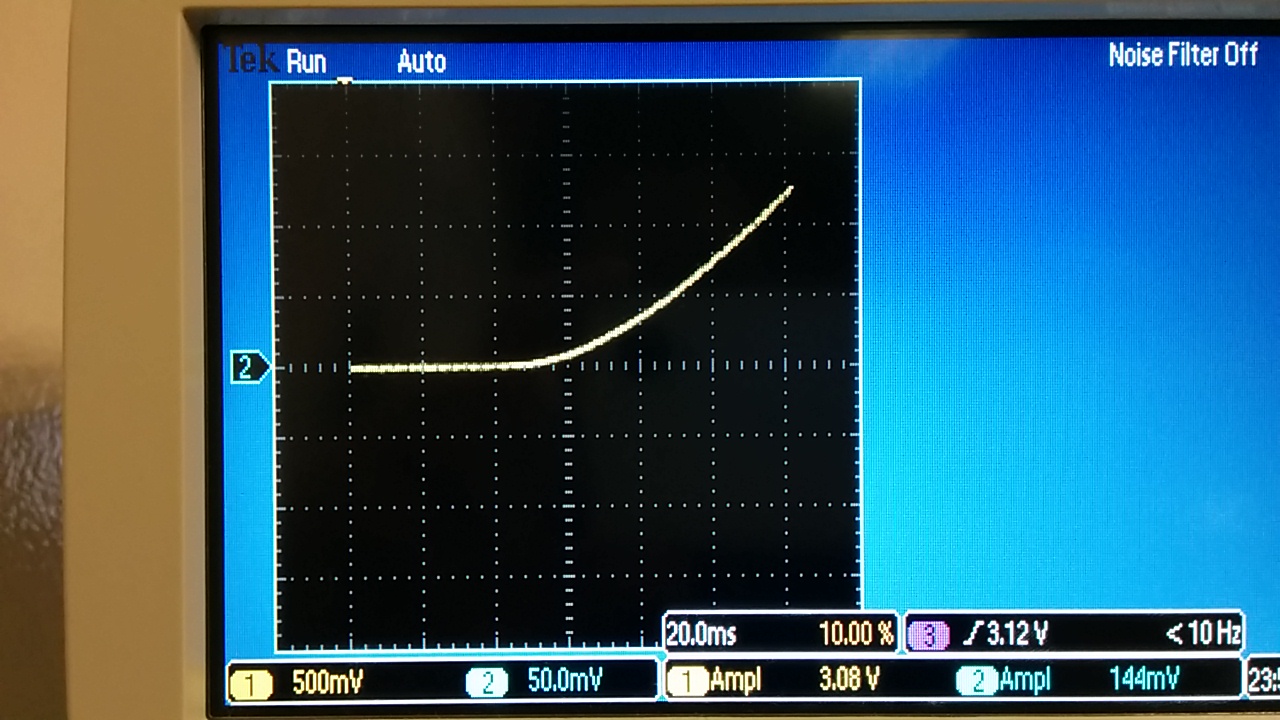

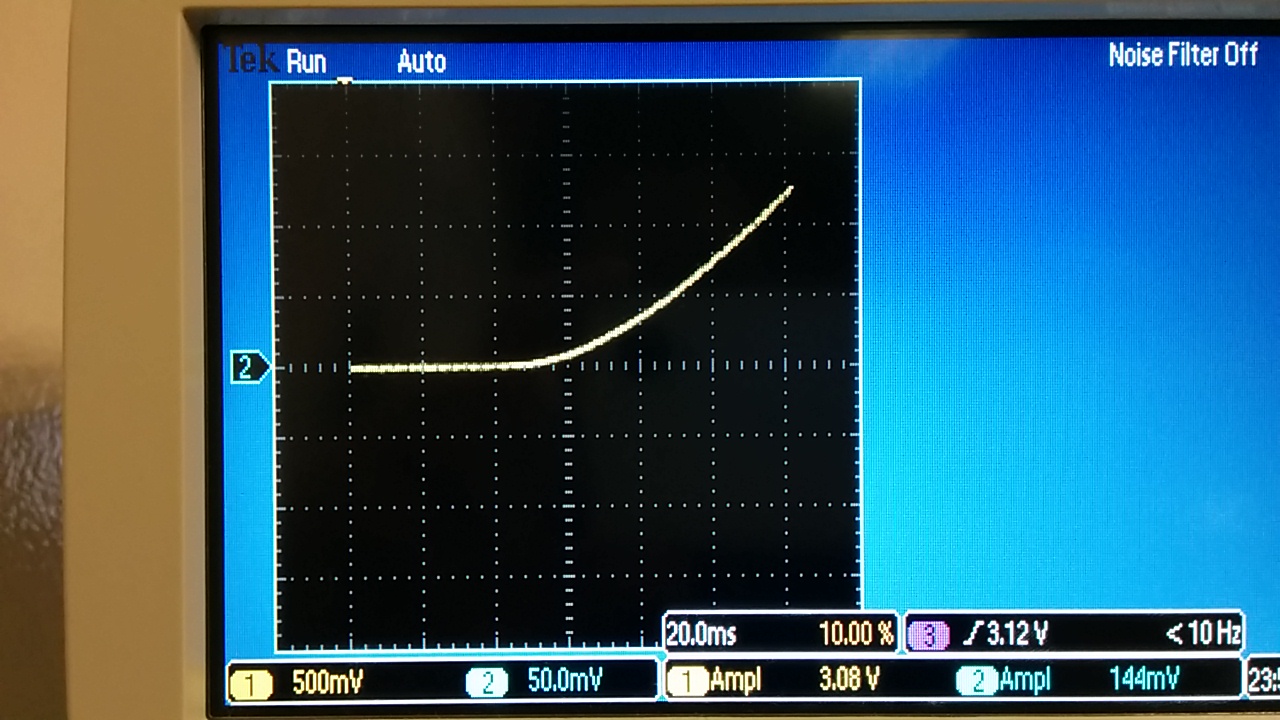

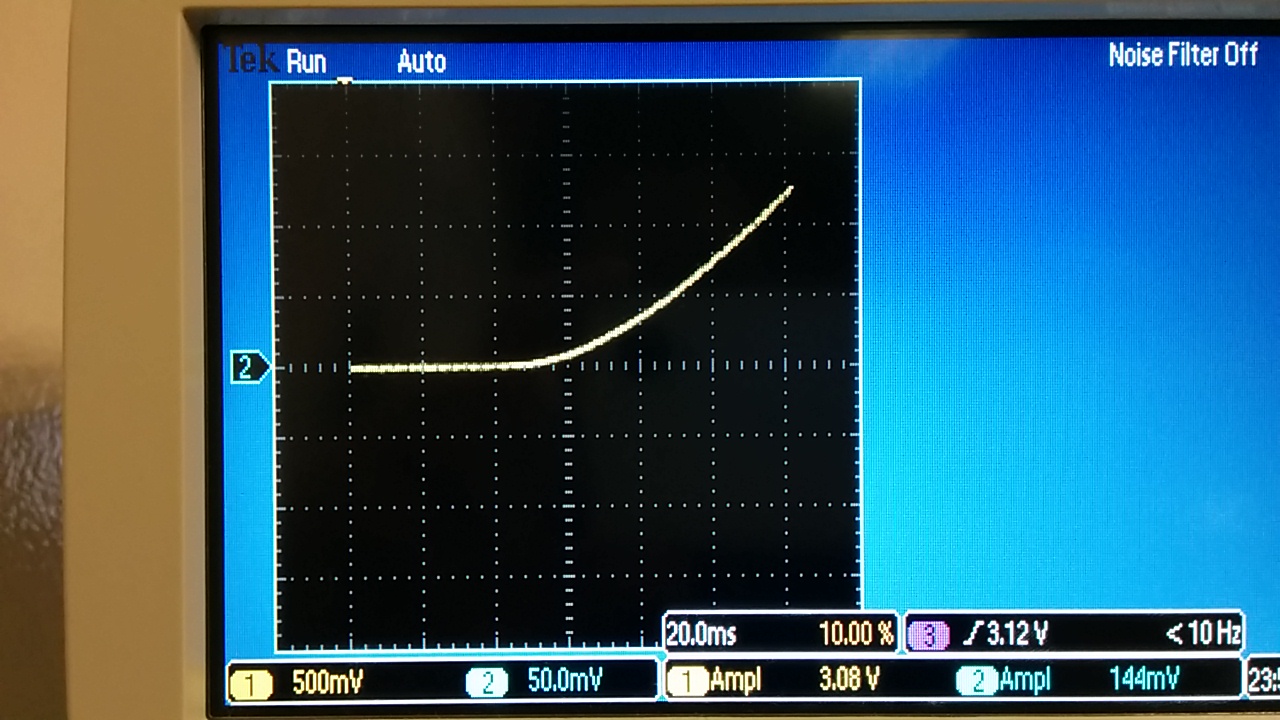

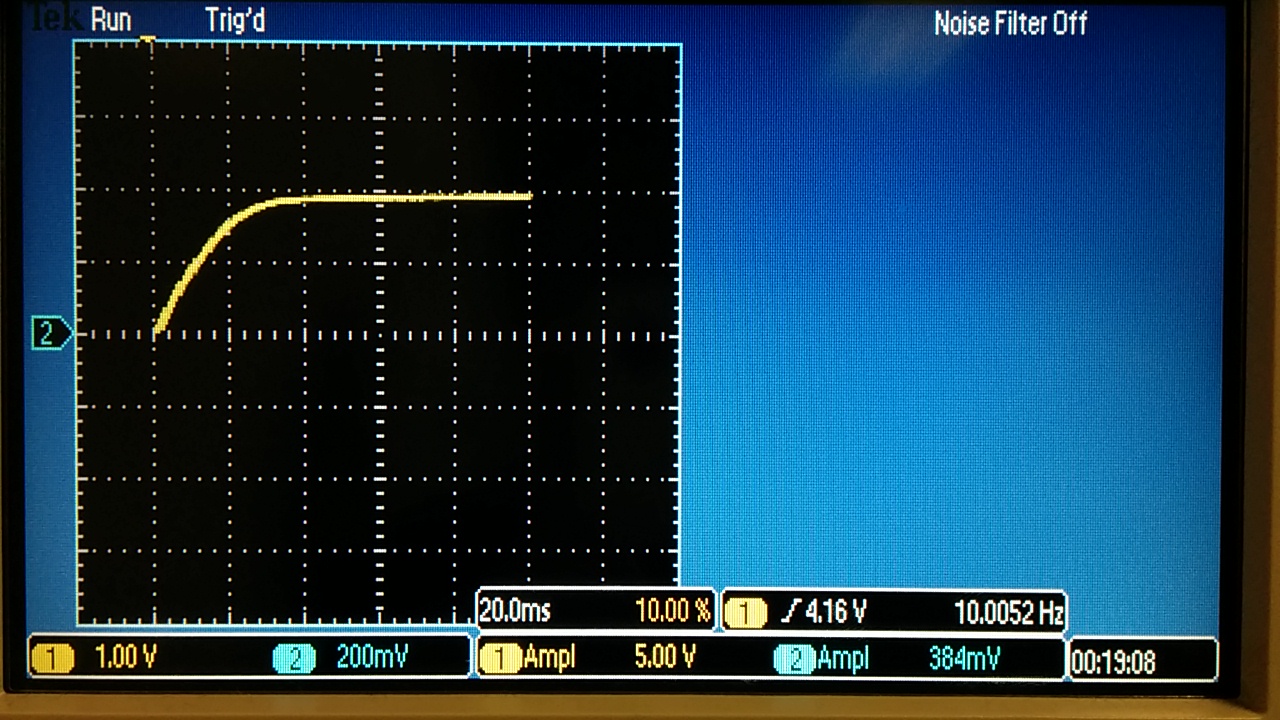

NMOS Experiment 1

Using a sample resistor of 100 Ohms

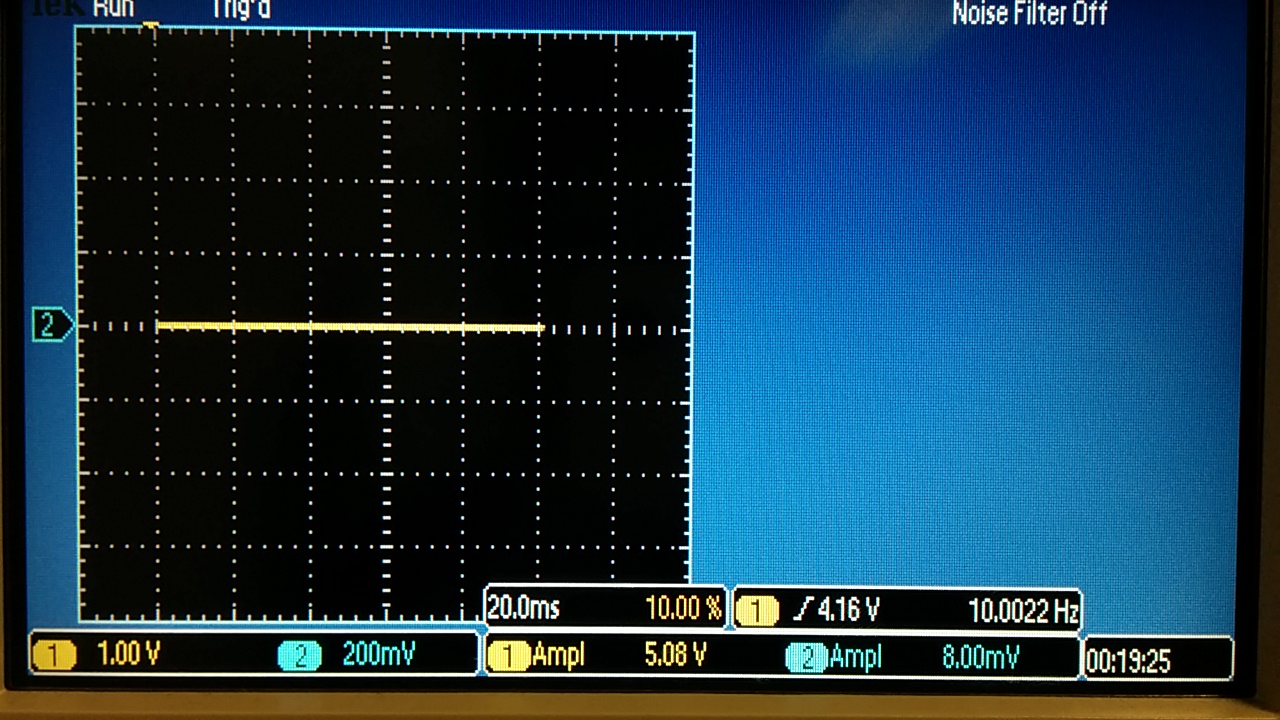

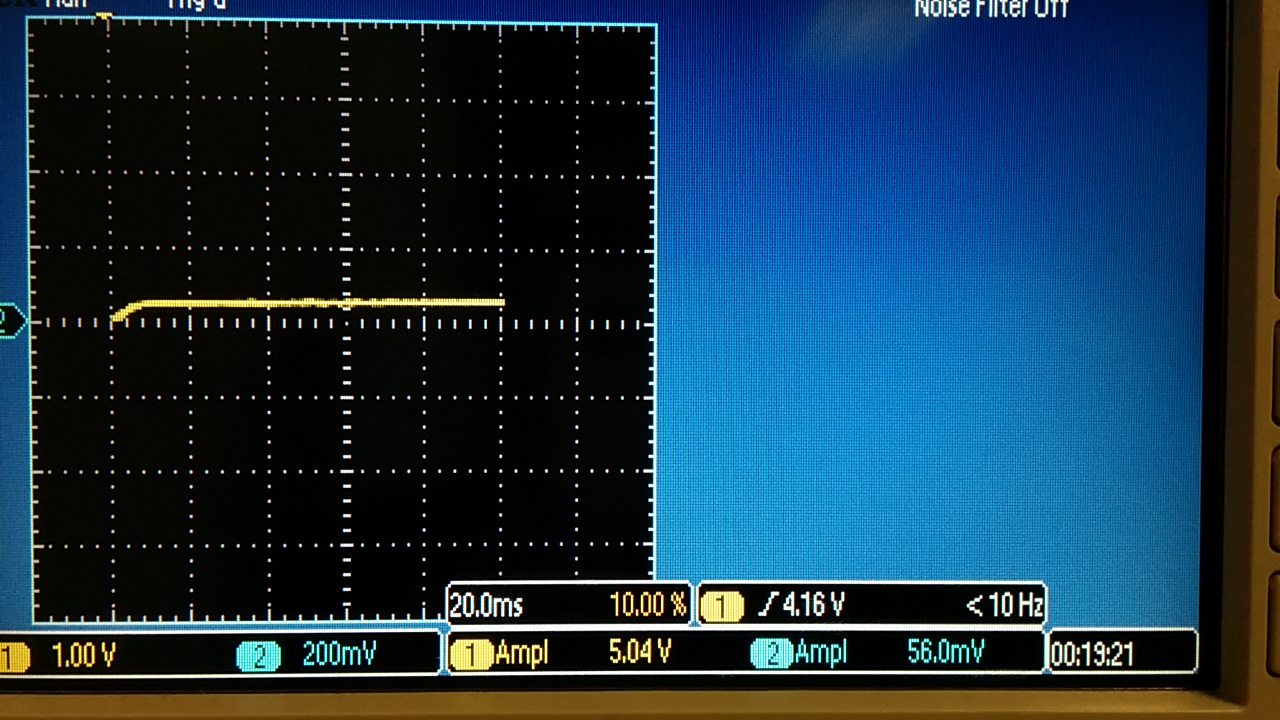

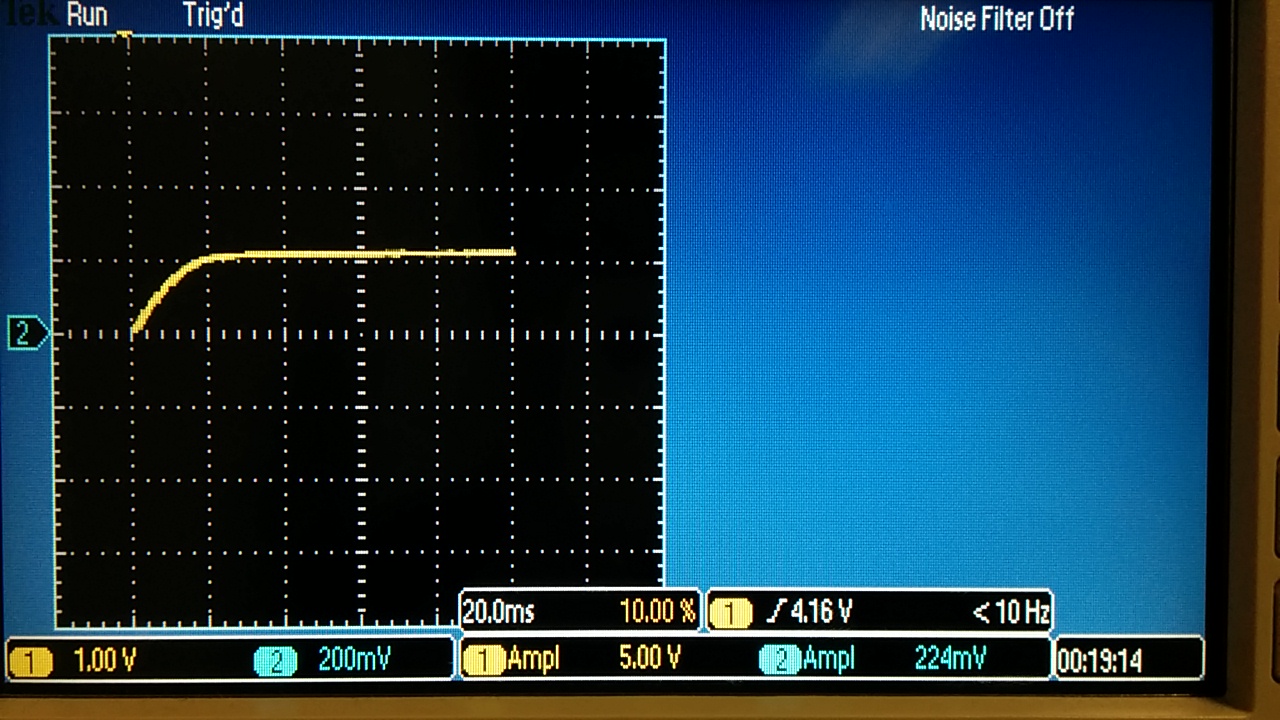

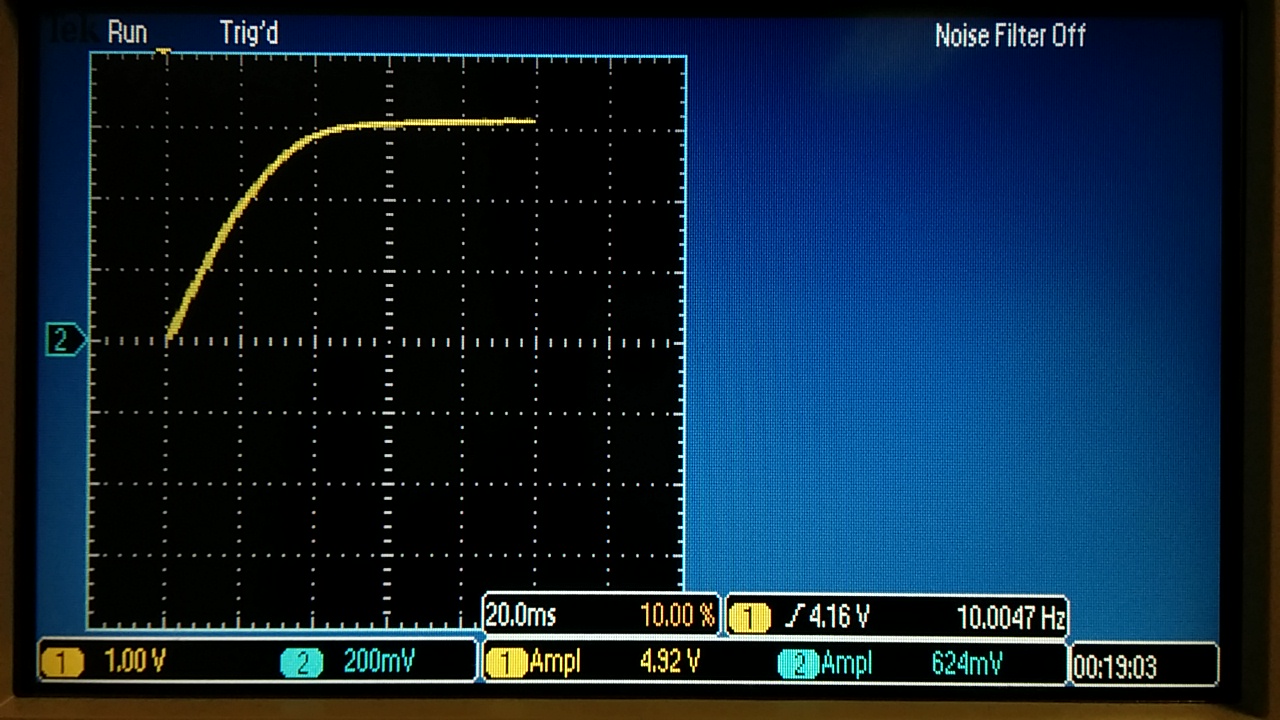

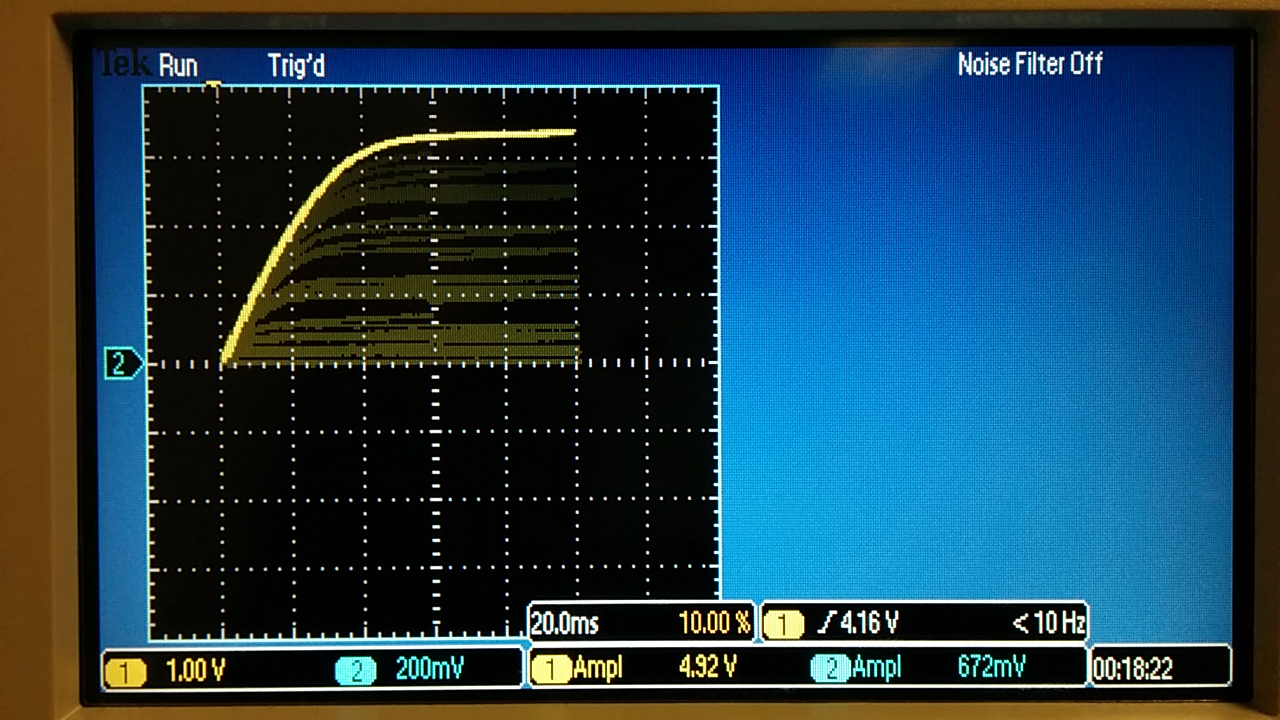

NMOS Experiment 2 using a sample resistor of 200 Ohms

VGS = 1V

VGS = 2V

VGS = 3V

VGS = 4V

VGS = 5V

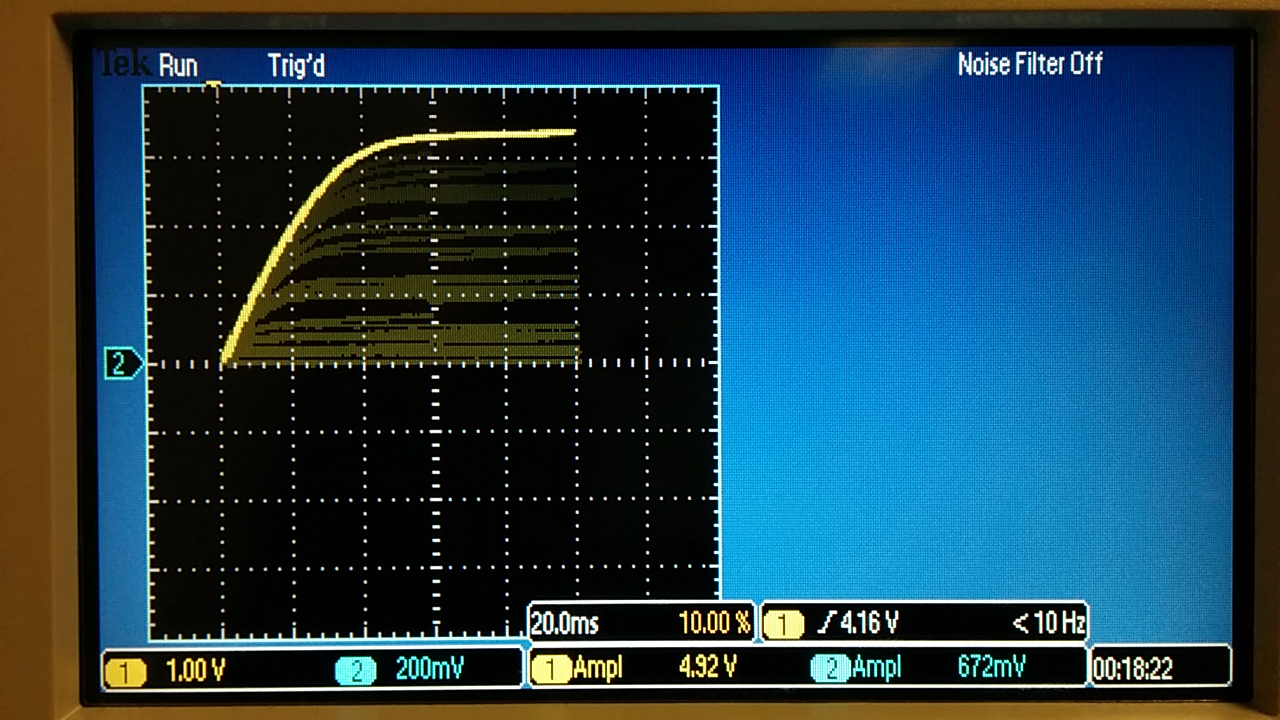

VGS Combined

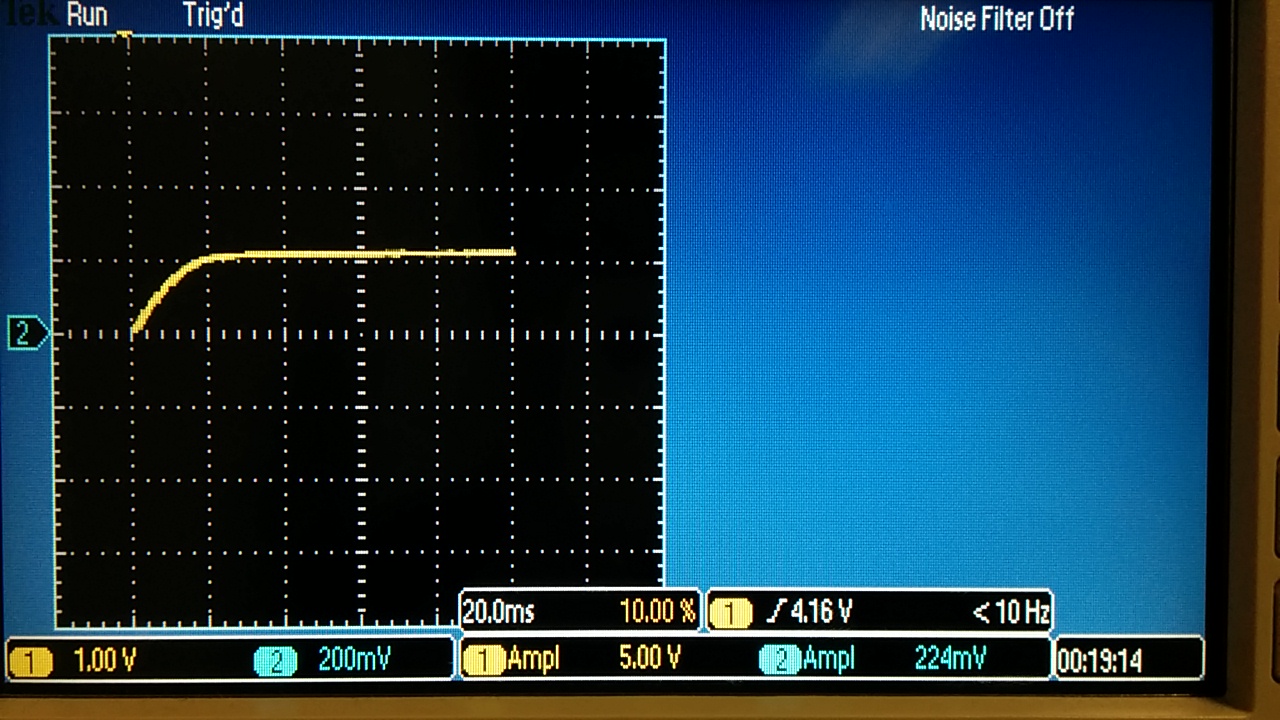

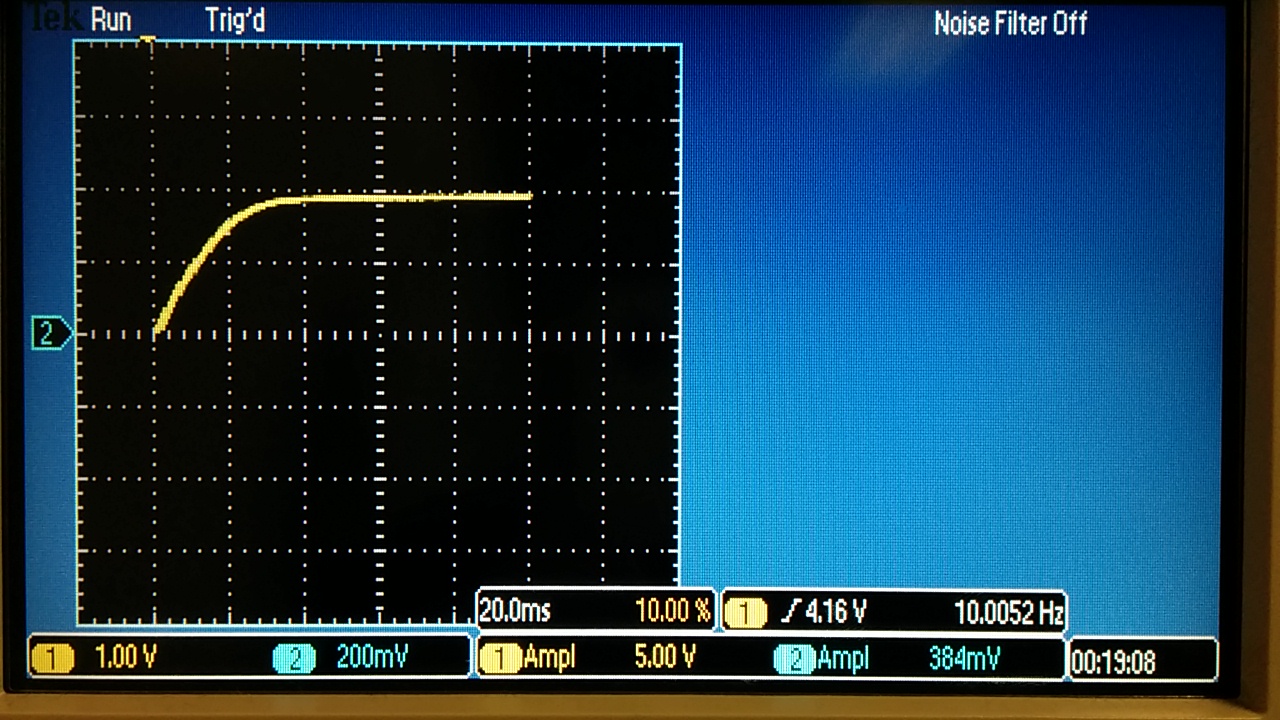

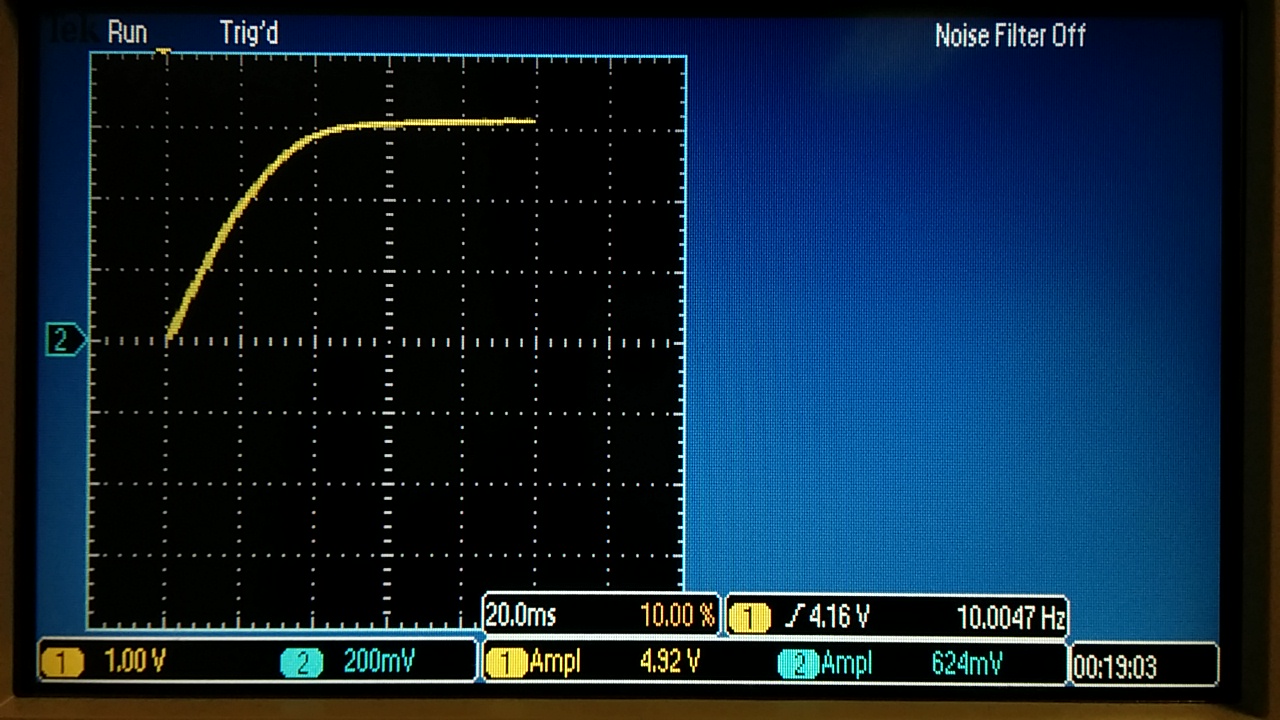

Experiment 3:

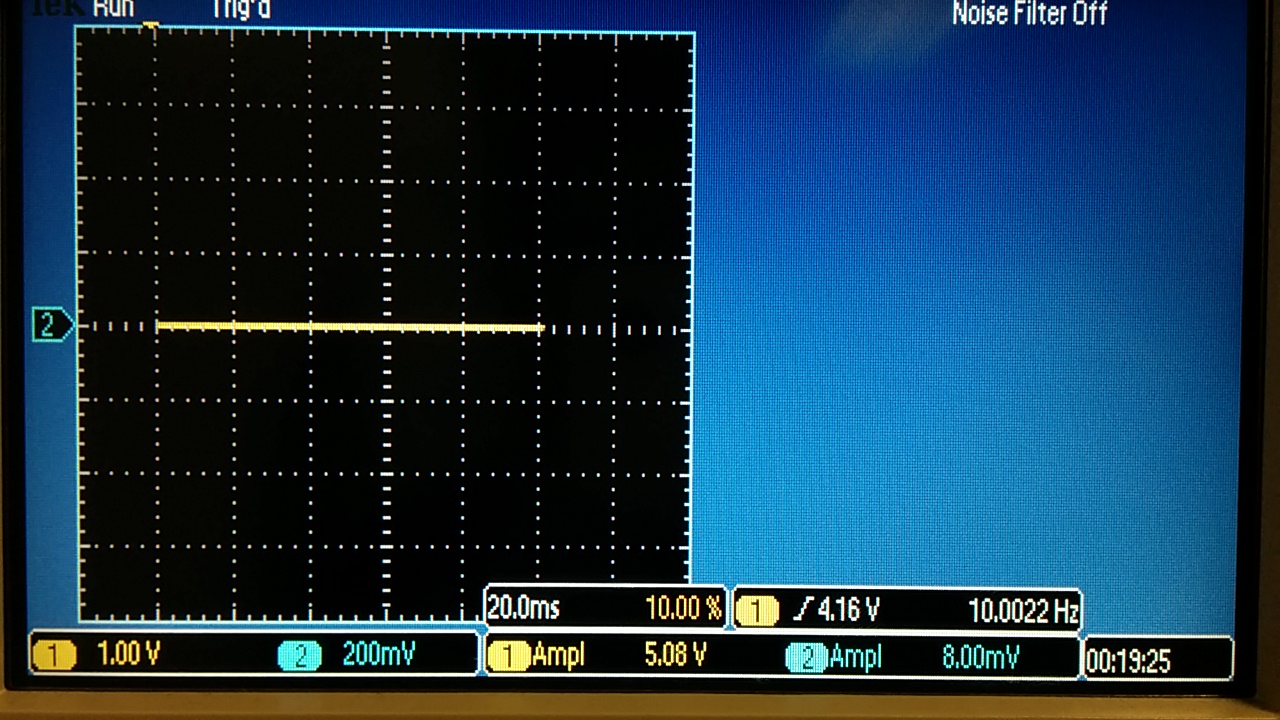

PMOS

Experiment

1: sample

resistor = 200 Ohm

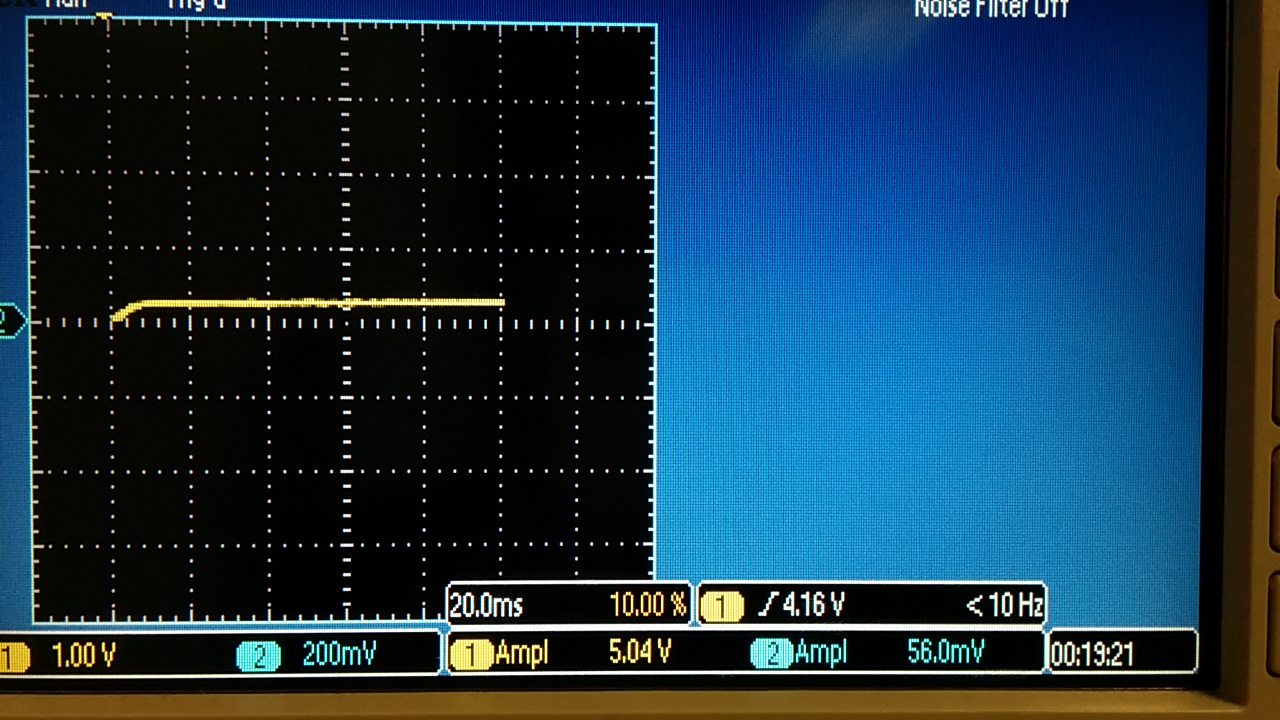

Experiment 2:

Experiment 3:

Hand Calculations

Basic Level = 1 MOSFET Model before

modifications

After comparing my simulations to the experimental results, I observed

that the simulations

current 'Id' was off by a factor of about 1.5 for the NMOS and that the

bias voltage sim did

not completely match. I compensated for this error in the KP and Gamma

value for NMOS. Similarly,

I changed the values of the PMOS KP to better match my experimental

data. The new modified model

is provided here.

Sim Experiment 1 NMOS

Sim Experiment 2 NMOS

Sim Experiment 3 NMOS

Sim Experiment 1 PMOS

Sim Experiment 2 PMOS

Sim Experiment 3 PMOS

Inverter

Return

to EE 420 Labs